#### **Purpose**

Eon Silicon Solution Inc. (hereinafter called "Eon") is going to provide its products' top marking on ICs with < cFeon > from January 1st, 2009, and without any change of the part number and the compositions of the ICs. Eon is still keeping the promise of quality for all the products with the same as that of Eon delivered before. Please be advised with the change and appreciate your kindly cooperation and fully support Eon's product family.

#### **Eon products' New Top Marking**

#### cFeon Top Marking Example:

## cFeon

Part Number: XXXX-XXX

Lot Number: XXXXX

Date Code: XXXXX

## **Continuity of Specifications**

There is no change to this data sheet as a result of offering the device as an Eon product. Any changes that have been made are the result of normal data sheet improvement and are noted in the document revision summary, where supported. Future routine revisions will occur when appropriate, and changes will be noted in a revision summary.

## **Continuity of Ordering Part Numbers**

Eon continues to support existing part numbers beginning with "Eon" and "cFeon" top marking. To order these products, during the transition please specify "Eon top marking" or "cFeon top marking" on your purchasing orders.

#### For More Information

Please contact your local sales office for additional information about Eon memory solutions.

#### **EN71GL128 Base MCP**

Stacked Multi-Chip Product (MCP) Flash Memory and RAM 128 Megabit (8M x 16-bit) CMOS 3.0 Volt-only Page Mode Flash Memory and 32 Megabit (2M x 16-bit) Pseudo Static RAM

# Distinctive Characteristics MCP Features

- Power supply voltage of 2.7 V to 3.3V

- High performance

- 70 ns

- Package

- 7 x 9 x 1.2mm 56 ball FBGA

- Operating Temperature

- 25°C to +85°C

### **General Description**

The EN71GL series is a product line of stacked Multi-Chip Product (MCP) packages and consists of:

- EN29GL128 (Page mode) Flash memory with lowest address sector protected.

- Pseudo SRAM.

For detailed specifications, please refer to the individual datasheets listed in the following table.

| Device      | Document  |

|-------------|-----------|

| NOR Flash   | EN29GL128 |

| Pseudo SRAM | ENPSL32   |

#### **Product Selector Guide**

#### 128Mb Flash Memory

| Device-Model#         | EN71GL128B0 | pSRAM density               | 32M pSRAM |

|-----------------------|-------------|-----------------------------|-----------|

| Flash Access time     | 70ns        | pSRAM Access time           | 70ns      |

| Page read Access time | IZOUS       | pSRAM Page read Access time | 25ns      |

| Package               | 56 FBGA     |                             |           |

This Data Sheet may be revised by subsequent versions or modifications due to changes in technical specifications.

©2004 Eon Silicon Solution, Inc., www.eonssi.com

Rev. B, Issue Date: 2009/11/23

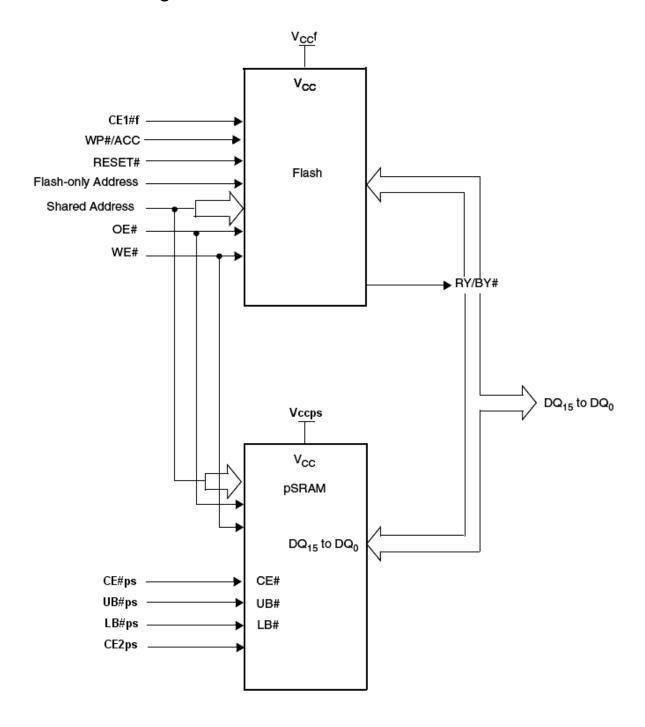

## **MCP Block Diagram**

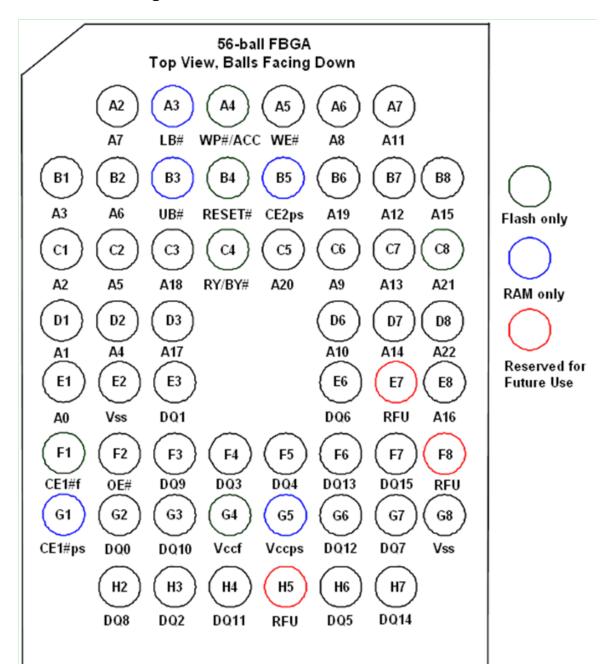

## **Connection Diagram**

| MCP         | Flash-only Addresses | Shared Addresses |

|-------------|----------------------|------------------|

| EN71GL128B0 | A22, A21             | A20 – A0         |

## **Pin Description**

| Signal             | Description                                     |

|--------------------|-------------------------------------------------|

| A22-A0             | 23 Address Inputs (Common)                      |

| DQ15-DQ0           | 16 Data Inputs/Outputs (Common)                 |

| CE1#f              | Chip Enable 1 (Flash)                           |

| CE1#ps             | Chip Enable 1 (pSRAM)                           |

| CE2ps              | Chip Enable 2 (pSRAM)                           |

| OE#                | Output Enable (Common)                          |

| WE#                | Write Enable (Common)                           |

| RY/BY#             | Ready/Busy Output (Flash)                       |

| UB#                | Upper Byte Control (pSRAM)                      |

| LB#                | Lower Byte Control (pSRAM)                      |

| RESET#             | Hardware Reset Pin, Active Low (Flash)          |

| WP#/ACC            | Hardware Write Protect/Acceleration Pin (Flash) |

| V <sub>CC</sub> f  | Flash 3.0 volt-only single power supply         |

| V <sub>CC</sub> ps | pSRAM Power Supply                              |

| V <sub>SS</sub>    | Device Ground (Common)                          |

| NC                 | Pin Not Connected Internally                    |

## Logic Symbol

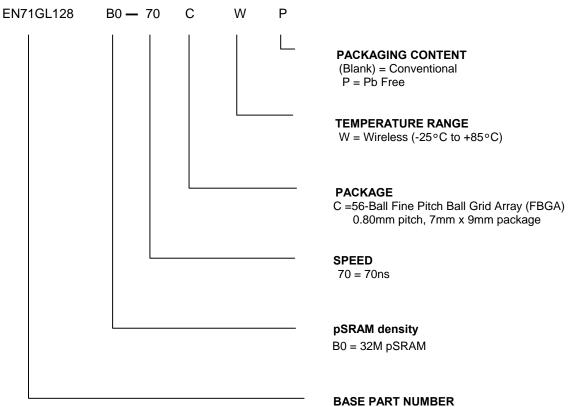

#### **ORDERING INFORMATION**

EN = Eon Silicon Solution Inc. 71GL = Multi-chip Product (MCP)

3.0V Page Mode Flash Memory and RAM 128 = 128 Megabit (8M x 16)

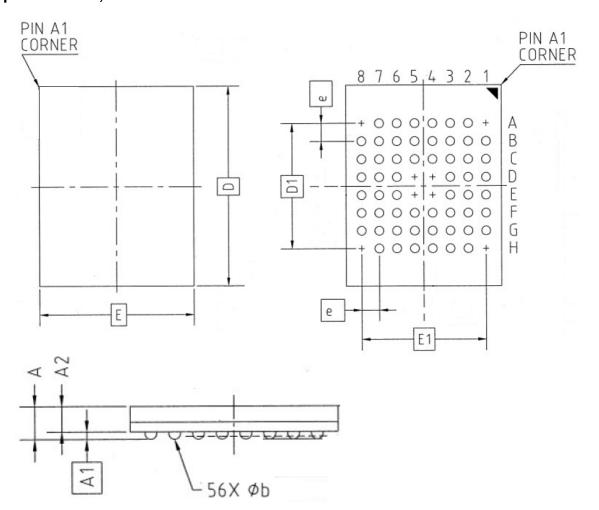

#### **PACKAGE MECHANICAL**

56-ball Fine-Pitch Ball Grid Array (FBGA) 7 x 9 mm Package, pitch: 0.8mm, ball: 0.4mm

| SYMBOL     | DI   | MENSION IN | ММ   |

|------------|------|------------|------|

|            | MIN. | NOR        | MAX  |

| Α          |      |            | 1.20 |

| <b>A</b> 1 | 0.25 | 0.30       | 0.35 |

| A2         | 0.80 |            | 0.95 |

| D          | 8.95 | 9.00       | 9.05 |

| E          | 6.95 | 7.00       | 7.05 |

| D1         |      | 5.60       |      |

| E1         |      | 5.60       |      |

| е          |      | 0.80       |      |

| b          | 0.35 | 0.40       | 0.45 |

Note: Controlling dimensions are in millimeters (mm).

This Data Sheet may be revised by subsequent versions or modifications due to changes in technical specifications.

©2004 Eon Silicon Solution, Inc., www.eonssi.com

#### **Revisions List**

| Revision No | Description                                                                               | Date       |

|-------------|-------------------------------------------------------------------------------------------|------------|

| Α           |                                                                                           | 2009/05/27 |

| В           | Update EN29GL128 (Page mode) Flash memory with lowest address sector protected on page 2. | 2009/11/23 |

Rev. B, Issue Date: 2009/11/23