## Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor

#### Datasheet

## **Product Features**

For a complete list of product features, see "Product Features" on page 10.

# The following features *do not* require enabling software:

- Intel XScale<sup>®</sup> Processor Up to 533 MHz

- PCI Interface

- USB v1.1 Device Controller

- SDRAM Interface

- High-Speed UART

- Console UART

- Internal Bus Performance Monitoring Unit

- 16 GPIOs

- Four Internal Timers

- Packaging

- 492-pin PBGA

- Commercial/Extended Temperature

### **Typical Applications**

- High-Performance DSL Modem

- High-Performance Cable Modem

- Residential Gateway

- SME Router

- Network Printers

## The following features *do* require enabling software:

- Encryption/Authentication (AES, DES, 3DES, SHA-1, MD5)

- Two High-Speed, Serial Interfaces

- Three Network Processor Engines

- Up to two MII Interfaces

- One UTOPIA Level 2 Interface

- Multi-Channel HDLC

- **Note:** Refer to the *Intel<sup>®</sup> IXP400 Software Programmer's Guide* for information on which features are currently enabled.

- Control Plane

- Integrated Access Device (IAD)

- Set-Top Box

- Access Points (802.11a/b/g)

- Industrial Controllers

INFORMATION IN THIS DOCUMENT IS PROVIDED IN CONNECTION WITH INTEL<sup>®</sup> PRODUCTS. NO LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IS GRANTED BY THIS DOCUMENT. EXCEPT AS PROVIDED IN INTEL'S TERMS AND CONDITIONS OF SALE FOR SUCH PRODUCTS, INTEL ASSUMES NO LIABILITY WHATSOEVER, AND INTEL DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY, RELATING TO SALE AND/OR USE OF INTEL PRODUCTS INCLUDING LIABILITY OR WARRANTIES RELATING TO FITNESS FOR A PARTICULAR PURPOSE, MERCHANTABILITY, OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT. Intel products are not intended for use in medical, life saving, life sustaining, critical control or safety systems, or in nuclear facility applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Intel Corporation may have patents or pending patent applications, trademarks, copyrights, or other intellectual property rights that relate to the presented subject matter. The furnishing of documents and other materials and information does not provide any license, express or implied, by estoppel or otherwise, to any such patents, trademarks, copyrights, or other intellectual property rights.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

Intel processor numbers are not a measure of performance. Processor numbers differentiate features within each processor family, not across different processor families. See <a href="http://www.intel.com/products/processor\_number">http://www.intel.com/products/processor\_number</a> for details.

The Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an order number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

BunnyPeople, Celeron, Celeron Inside, Centrino, Centrino logo, Core Inside, FlashFile, i960, InstantIP, Intel, Intel logo, Intel386, Intel486, Intel740, IntelDX2, IntelDX4, IntelSX2, Intel Core, Intel Inside, Intel Inside logo, Intel. Leap ahead., Intel. Leap ahead. logo, Intel NetBurst, Intel NetMerge, Intel NetStructure, Intel SingleDriver, Intel SpeedStep, Intel StrataFlash, Intel Viiv, Intel vPro, Intel XScale, Itanium, Itanium Inside, MCS, MMX, Oplus, OverDrive, PDCharm, Pentium, Pentium, Inside, skoool, Sound Mark, The Journey Inside, VTune, Xeon, and Xeon Inside are trademarks of Intel Corporation in the U.S. and other countries.

\*Other names and brands may be claimed as the property of others.

Copyright © 2007, Intel Corporation. All Rights Reserved.

## Contents

| 1.0 | Intro | duction          | 1                                                                                 | 9   |

|-----|-------|------------------|-----------------------------------------------------------------------------------|-----|

|     | 1.1   | About t          | his Document                                                                      | 9   |

|     | 1.2   | Product          | t Features                                                                        | 10  |

|     |       | 1.2.1            | Product Line Features                                                             | 10  |

|     |       | 1.2.2            | Processor Features                                                                | 13  |

| 2.0 | Funct | tional O         | verview                                                                           | 14  |

|     | 2.1   |                  | nal Units                                                                         |     |

|     | 2     | 2.1.1            | Network Processor Engines (NPEs)                                                  |     |

|     |       | 2.1.2            | Internal Bus                                                                      |     |

|     |       |                  | 2.1.2.1 North AHB                                                                 |     |

|     |       |                  | 2.1.2.2 South AHB                                                                 |     |

|     |       |                  | 2.1.2.3 APB Bus                                                                   |     |

|     |       | 2.1.3            | MII Interfaces                                                                    |     |

|     |       | 2.1.4            | UTOPIA Level 2                                                                    |     |

|     |       | 2.1.5            | USB Interface                                                                     |     |

|     |       | 2.1.6            | PCI Controller                                                                    |     |

|     |       | 2.1.7            | SDRAM Controller                                                                  |     |

|     |       | 2.1.8            | Expansion Bus                                                                     |     |

|     |       | 2.1.9            | High-Speed, Serial Interfaces.                                                    |     |

|     |       |                  | High-Speed and Console UARTs                                                      |     |

|     |       |                  | GPIO                                                                              |     |

|     |       | 2.1.12<br>2.1.12 | Internal Bus Performance Monitoring Unit (IBPMU)<br>Interrupt Controller          | 23  |

|     |       |                  | Timers                                                                            |     |

|     |       |                  | AHB Queue Manager                                                                 |     |

|     | 2.2   |                  | Scale <sup>®</sup> Processor                                                      |     |

|     | 2.2   | 2.2.1            | Super Pipeline                                                                    |     |

|     |       | 2.2.2            | Branch Target Buffer (BTB)                                                        |     |

|     |       | 2.2.3            | Instruction Memory Management Unit (IMMU)                                         |     |

|     |       | 2.2.4            | Data Memory Management Unit (DMMU)                                                |     |

|     |       | 2.2.5            | Instruction Cache (I-Cache)                                                       |     |

|     |       | 2.2.6            | Data Cache (D-Cache)                                                              |     |

|     |       | 2.2.7            | Mini-Data Cache                                                                   | 28  |

|     |       | 2.2.8            | Fill Buffer (FB) and Pend Buffer (PB)                                             |     |

|     |       | 2.2.9            | Write Buffer (WB)                                                                 |     |

|     |       |                  | Multiply-Accumulate Coprocessor (CP0)                                             |     |

|     |       |                  | Performance Monitoring Unit (PMU)                                                 |     |

|     |       | 2.2.12           | Debug Unit                                                                        | 30  |

| 3.0 | Funct | tional S         | ignal Descriptions                                                                | 30  |

|     | 3.1   | Pin Des          | cription Tables                                                                   | 32  |

| 4.0 | Packa | age and          | Pinout Information                                                                | 47  |

|     | 4.1   | -                | e Description                                                                     |     |

|     | 4.2   |                  | Pin Descriptions                                                                  |     |

|     | 4.3   |                  | e Thermal Specifications                                                          |     |

|     |       | 4.3.1            | Commercial Temperature                                                            |     |

|     |       | 4.3.2            | Extended Temperature                                                              |     |

| 5.0 | Flect | rical Sn         | ecifications                                                                      |     |

| 5.0 | 5.1   | •                | e Maximum Ratings                                                                 |     |

|     | 5.2   | Voobur           | , V <sub>CCPLL2</sub> , V <sub>CCOSCP</sub> , V <sub>CCOSC</sub> Pin Requirements | 78  |

|     | J     | * CCPLL'I        |                                                                                   | , 0 |

6.0

|      | 5.2.1               | V <sub>CCPLL1</sub> Requirement              |

|------|---------------------|----------------------------------------------|

|      | 5.2.2               | V <sub>CCPLL2</sub> Requirement              |

|      | 5.2.3               | V <sub>CCOSCP</sub> Requirement              |

|      | 5.2.4               | V <sub>CCOSC</sub> Requirement               |

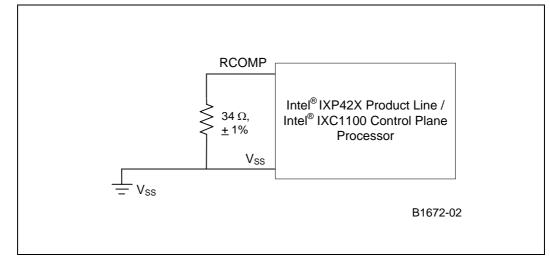

| 5.3  | RCOMF               | Pin Requirements                             |

| 5.4  | DC Spe              | cifications                                  |

|      | 5.4.1               | Operating Conditions                         |

|      | 5.4.2               | PCI DC Parameters                            |

|      | 5.4.3               | USB DC Parameters                            |

|      | 5.4.4               | UTOPIA Level 2 DC Parameters                 |

|      | 5.4.5               | MII DC Parameters                            |

|      | 5.4.6               | MDIO DC Parameters                           |

|      | 5.4.7               | SDRAM Bus DC Parameters                      |

|      | 5.4.8               | Expansion Bus DC Parameters                  |

|      | 5.4.9               | High-Speed, Serial Interface 0 DC Parameters |

|      | 5.4.10              | High-Speed, Serial Interface 1 DC Parameters |

|      | 5.4.11              | High-Speed and Console UART DC Parameters    |

|      | 5.4.12              | GPIO DC Parameters                           |

|      |                     | JTAG AND PLL_LOCK DC Parameters85            |

|      |                     | Reset DC Parameters                          |

| 5.5  | AC Spe              | cifications                                  |

|      | 5.5.1               | Clock Signal Timings                         |

|      |                     | 5.5.1.1 Processor Clock Timings              |

|      |                     | 5.5.1.2 PCI Clock Timings                    |

|      |                     | 5.5.1.3 MII Clock Timings                    |

|      |                     | 5.5.1.4 UTOPIA Level 2 Clock Timings         |

|      |                     | 5.5.1.5 Expansion Bus Clock Timings          |

|      | 5.5.2               | Bus Signal Timings                           |

|      |                     | 5.5.2.1 PCI                                  |

|      |                     | 5.5.2.2 USB Interface                        |

|      |                     | 5.5.2.3 UTOPIA Level 2 (33 MHz)              |

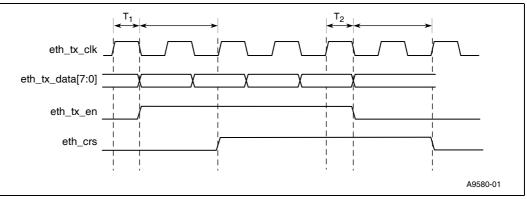

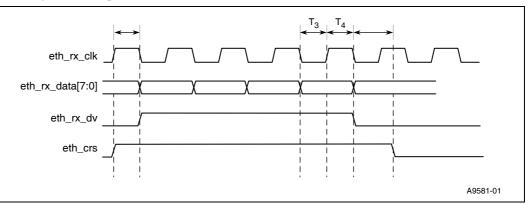

|      |                     | 5.5.2.4 MIT                                  |

|      |                     | 5.5.2.6 SDRAM Bus                            |

|      |                     | 5.5.2.7 Expansion Bus                        |

|      |                     | 5.5.2.8 High-Speed, Serial Interfaces        |

|      |                     | 5.5.2.9 JTĂG                                 |

|      | 5.5.3               | Reset Timings                                |

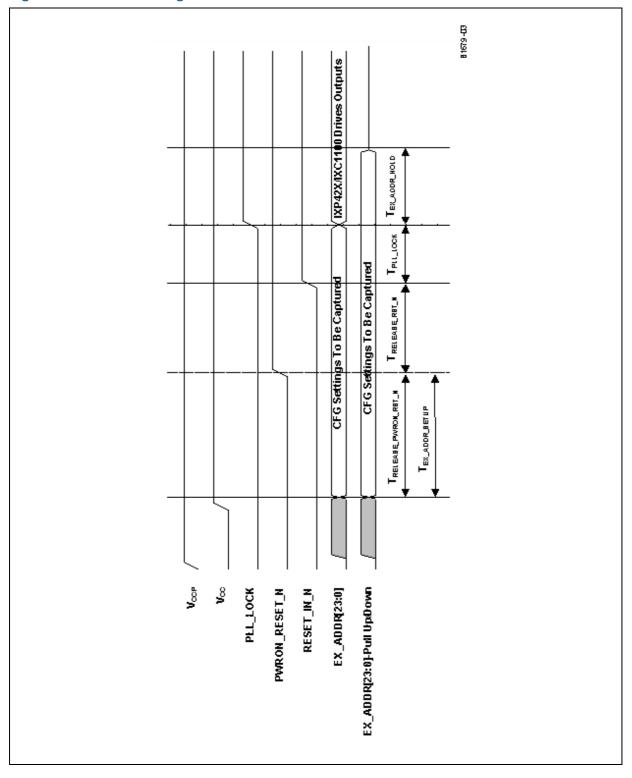

|      |                     | 5.5.3.1 Cold Reset                           |

|      |                     | 5.5.3.2 Hardware Warm Reset                  |

|      |                     | 5.5.3.3 Soft Reset                           |

| - /  |                     | 5.5.3.4 Reset Timings                        |

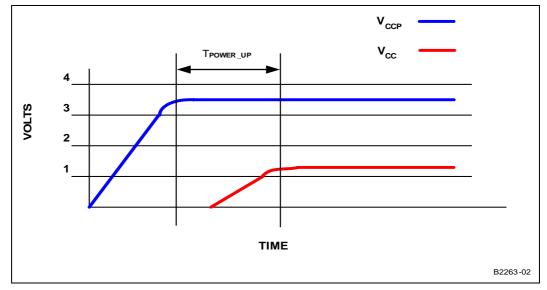

| 5.6  |                     | Sequence                                     |

| 5.7  | I <sub>CC</sub> and | Total Average Power                          |

| Orde | ring Inf            | ormation                                     |

## Figures

| 1  | Intel <sup>®</sup> IXP425 Network Processor Block Diagram | 15   |

|----|-----------------------------------------------------------|------|

| 2  | Intel <sup>®</sup> IXP423 Network Processor Block Diagram | . 16 |

| 3  | Intel® IXP422 Network Processor Block Diagram             | . 17 |

| 4  | Intel <sup>®</sup> IXP421 Network Processor Block Diagram | . 17 |

| 5  | Intel <sup>®</sup> IXP420 Network Processor Block Diagram | 18   |

| 6  | Intel XScale <sup>®</sup> Technology Block Diagram        |      |

| 7  | 492-Pin Lead PBGA Package                                 | . 47 |

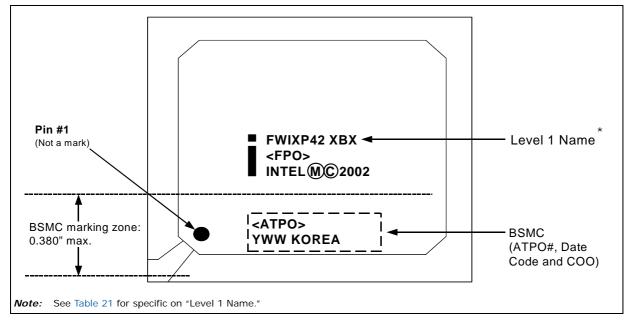

| 8  | Package Markings                                          | . 48 |

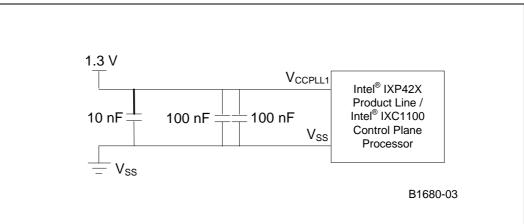

| 9  | V <sub>CCPLL1</sub> Power Filtering Diagram               |      |

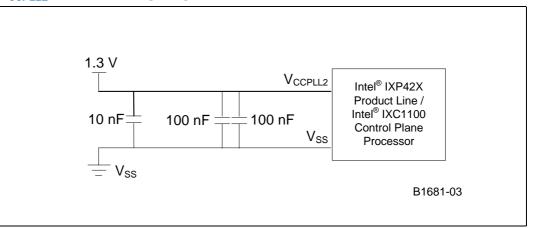

| 10 | V <sub>CCPLL2</sub> Power Filtering Diagram               |      |

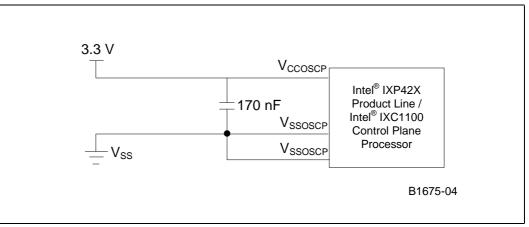

| 11 | V <sub>CCOSCP</sub> Power Filtering Diagram               |      |

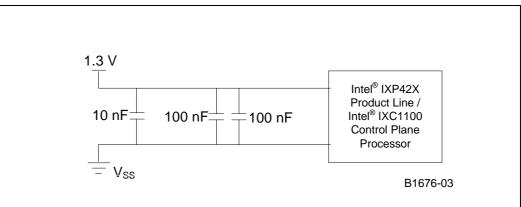

| 12 | V <sub>CCOSC</sub> Power Filtering Diagram                |      |

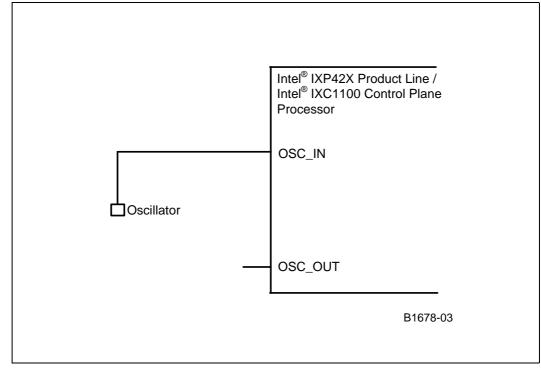

| 13 | RCOMP Pin External Resistor Requirements                  |      |

| 14 | Typical Connection to an Oscillator                       |      |

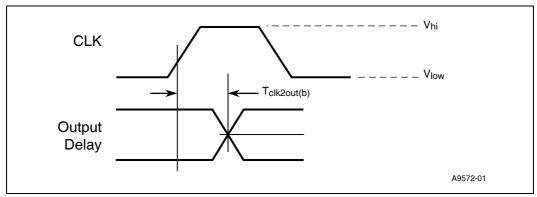

| 15 | PCI Output Timing                                         |      |

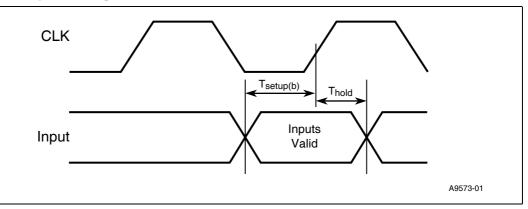

| 16 | PCI Input Timing                                          |      |

| 17 | UTOPIA Level 2 Input Timings                              |      |

| 18 | UTOPIA Level 2 Output Timings                             |      |

| 19 | MII Output Timings                                        |      |

| 20 | MII Input Timings                                         |      |

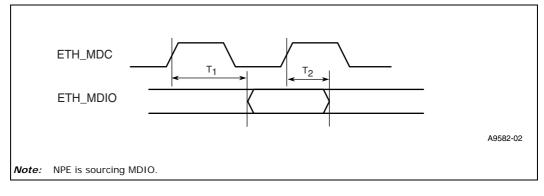

| 21 | MDIO Output Timings                                       |      |

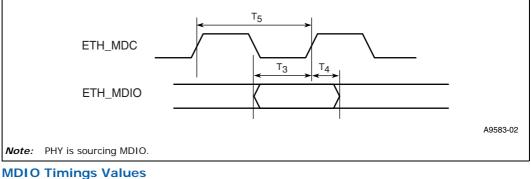

| 22 | MDIO Input Timings                                        |      |

| 23 | SDRAM Input Timings                                       | 93   |

| 24 | SDRAM Output Timings                                      | 94   |

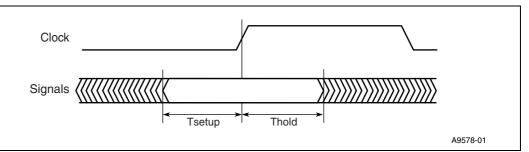

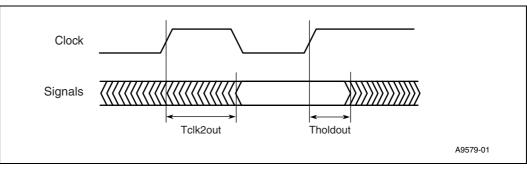

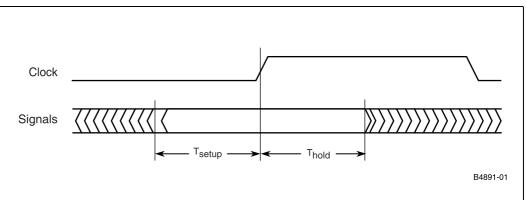

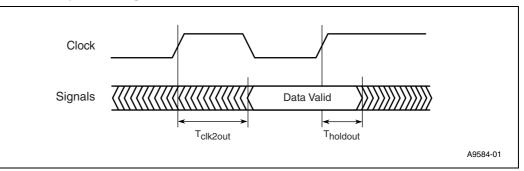

| 25 | Signal Timing With Respect to Clock Rising Edge           | 95   |

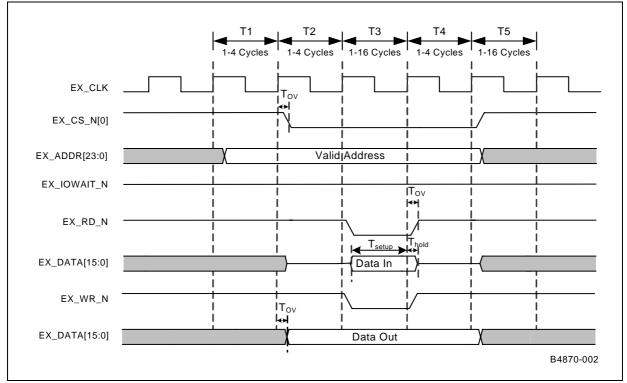

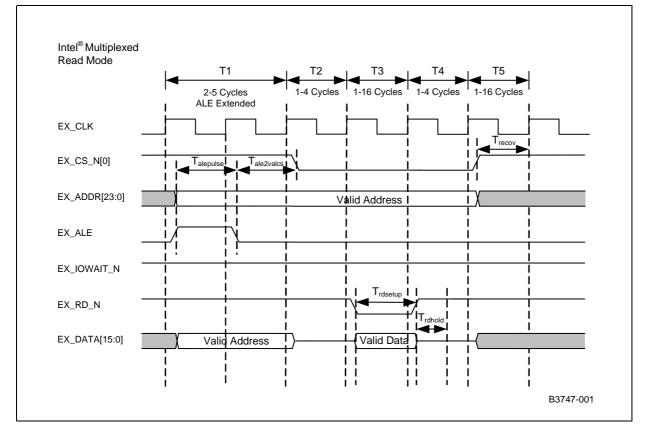

| 26 | Intel <sup>®</sup> Multiplexed Read Mode                  | 96   |

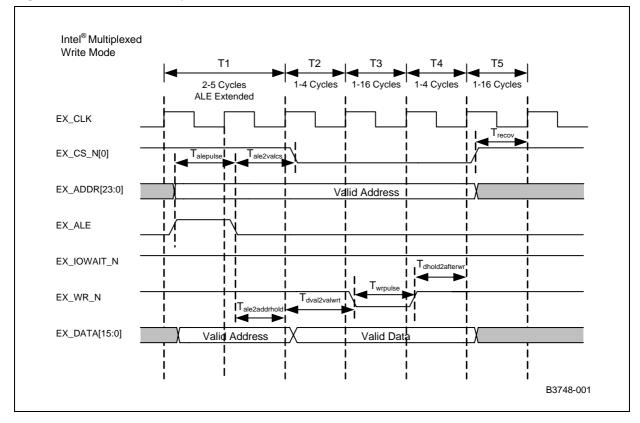

| 27 | Intel <sup>®</sup> Multiplexed Write Mode                 |      |

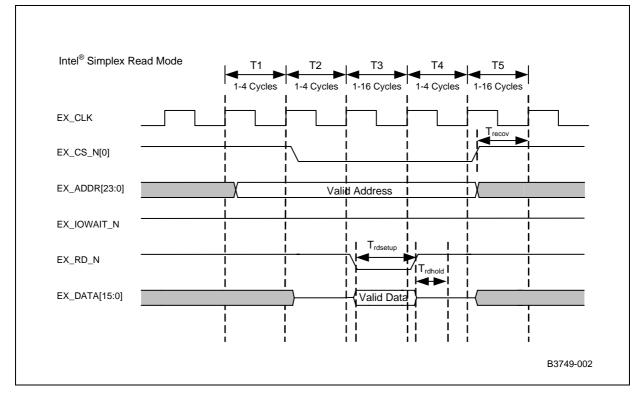

| 28 | Intel <sup>®</sup> Simplex Read Mode                      | 99   |

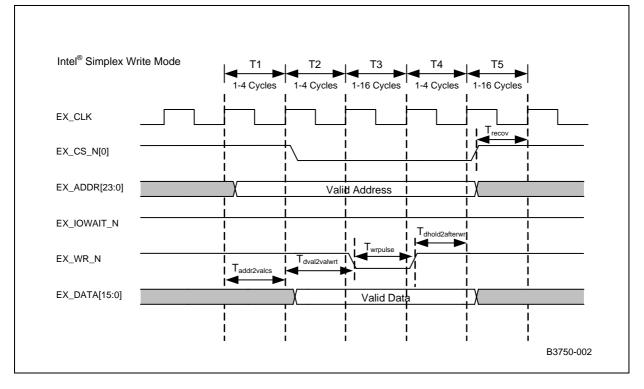

| 29 | Intel <sup>®</sup> Simplex Write Mode                     | 100  |

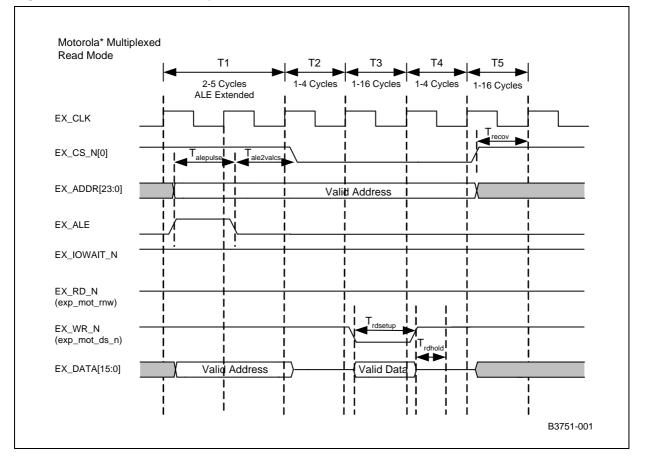

| 30 | Motorola* Multiplexed Read Mode 1                         | 102  |

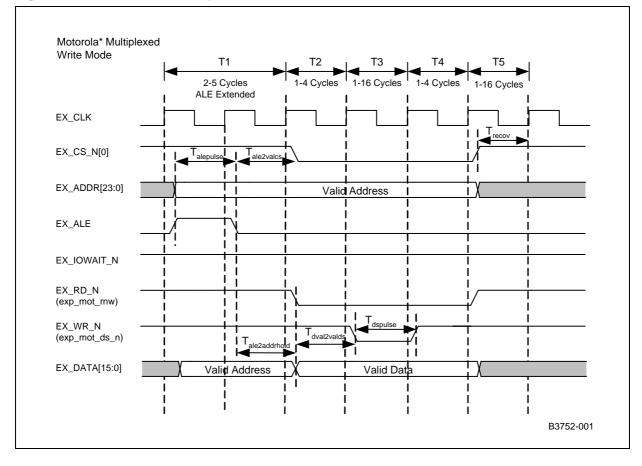

| 31 | Motorola* Multiplexed Write Mode 1                        |      |

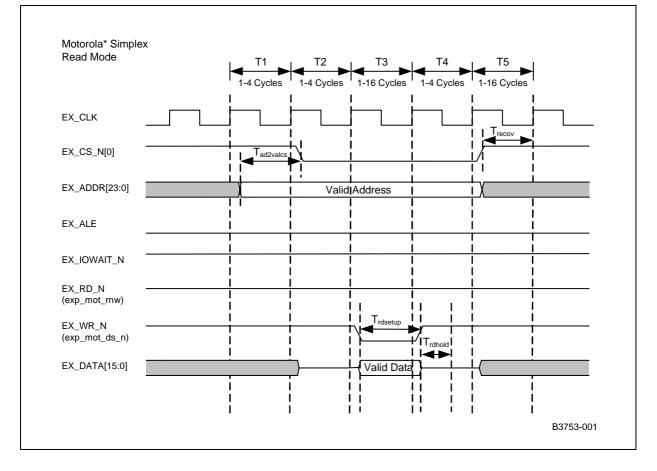

| 32 | Motorola* Simplex Read Mode 1                             | 104  |

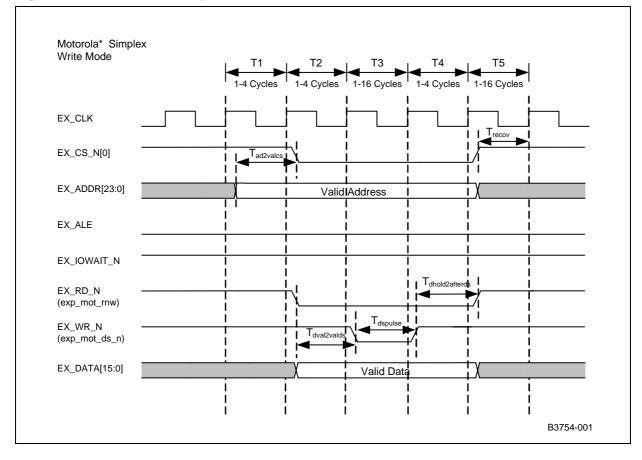

| 33 | Motorola* Simplex Write Mode 1                            |      |

| 34 | HPI-8 Mode Read Accesses                                  |      |

| 35 | HPI-8 Mode Write Accesses                                 |      |

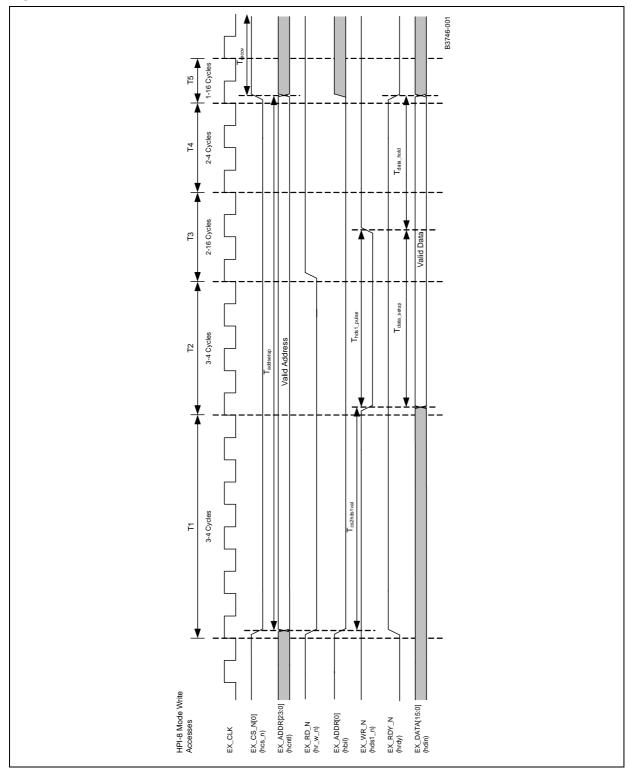

| 36 | HPI-16 Multiplexed Write Mode 1                           |      |

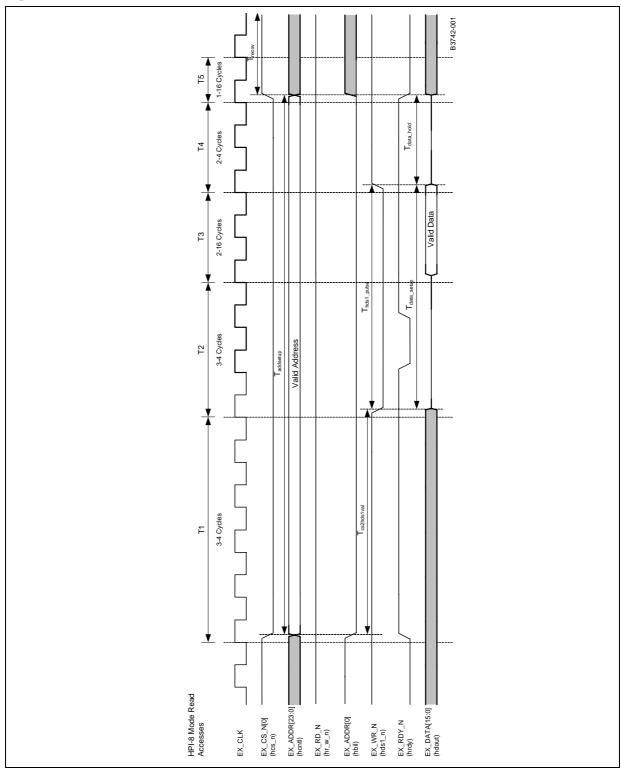

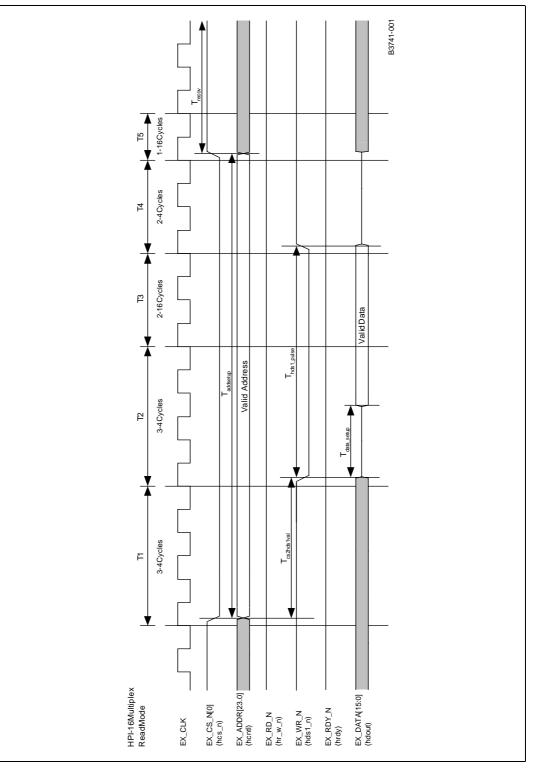

| 37 | HPI-16 Multiplex Read Mode 1                              |      |

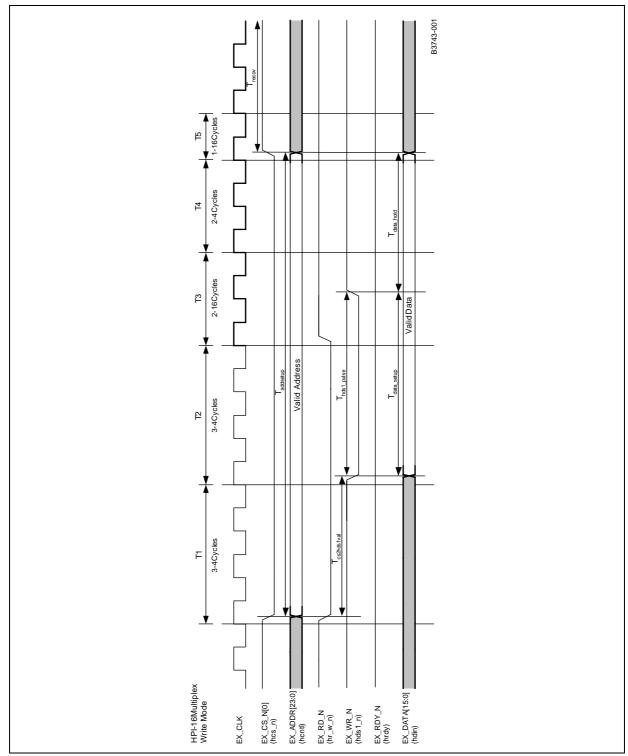

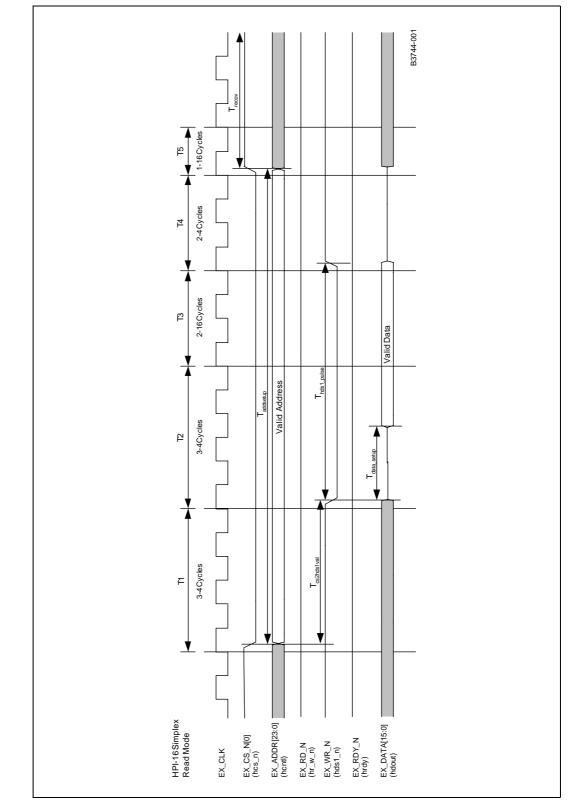

| 38 | HPI-16 Simplex Read Mode                                  |      |

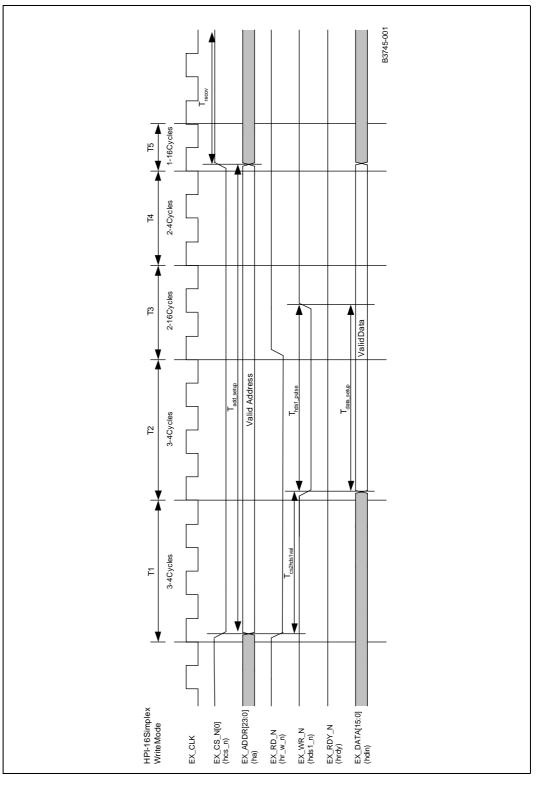

| 39 | HPI-16 Simplex Write Mode                                 |      |

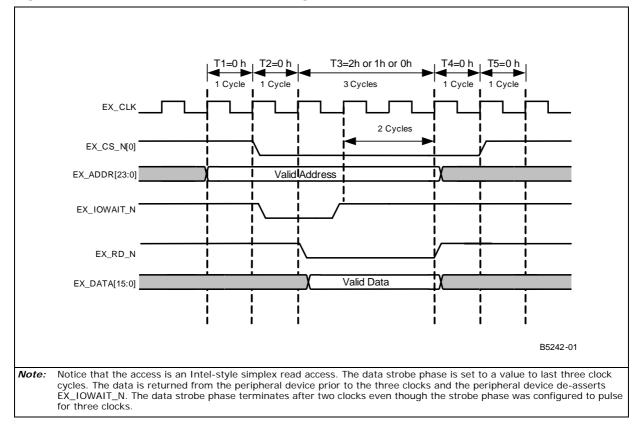

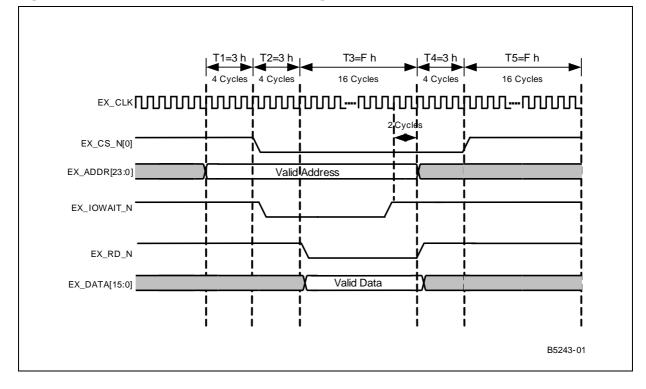

| 40 | I/O Wait Normal Phase Timing                              |      |

| 41 | I/O Wait Extended Phase Timing                            |      |

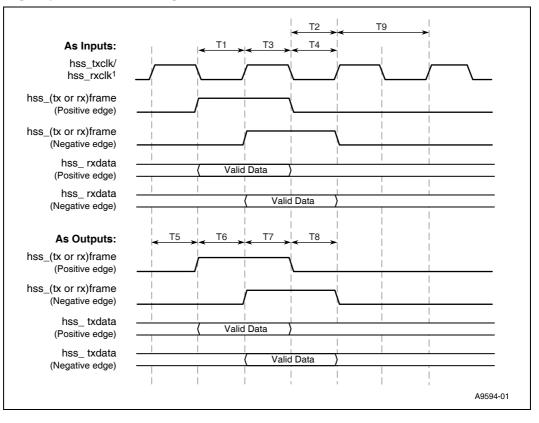

| 42 | High-Speed, Serial Timings                                |      |

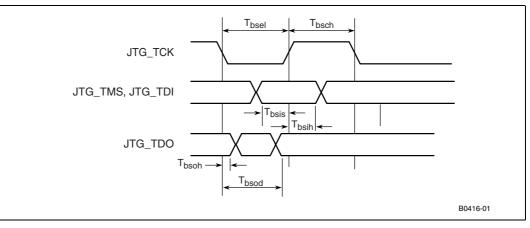

| 43 | Boundary-Scan General Timings                             |      |

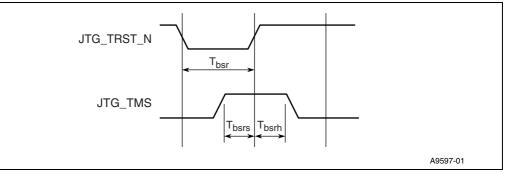

| 44 | Boundary-Scan Reset Timings                               |      |

| 45 | Reset Timings                                             |      |

| 46 | Power-Up Sequence Timing 1                                | 126  |

| Т | a | b | le | S |

|---|---|---|----|---|

|   |   |   |    |   |

| 1                    | Related Documents                                                                                                                                                                                          |                            |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 2                    | Terminology and Acronyms                                                                                                                                                                                   |                            |

| 3                    | Processor Features                                                                                                                                                                                         | 13                         |

| 4                    | Processor Functions                                                                                                                                                                                        | 19                         |

| 5                    | Signal Type Definitions                                                                                                                                                                                    |                            |

| 6                    | Processors' Signal Interface Summary Table                                                                                                                                                                 | 31                         |

| 7                    | SDRAM Interface                                                                                                                                                                                            |                            |

| 8                    | PCI Controller                                                                                                                                                                                             |                            |

| 9                    | High-Speed, Serial Interface 0                                                                                                                                                                             |                            |

| 10                   |                                                                                                                                                                                                            |                            |

| 11                   |                                                                                                                                                                                                            |                            |

| 12                   |                                                                                                                                                                                                            |                            |

| 13                   |                                                                                                                                                                                                            |                            |

| 14                   | •                                                                                                                                                                                                          |                            |

| 15                   |                                                                                                                                                                                                            |                            |

|                      |                                                                                                                                                                                                            |                            |

| 17                   |                                                                                                                                                                                                            |                            |

| 16                   |                                                                                                                                                                                                            |                            |

| 18                   |                                                                                                                                                                                                            |                            |

| 19                   |                                                                                                                                                                                                            |                            |

| 20                   |                                                                                                                                                                                                            |                            |

| 21                   |                                                                                                                                                                                                            |                            |

| 22                   |                                                                                                                                                                                                            |                            |

| 23                   |                                                                                                                                                                                                            | 56                         |

| 24                   |                                                                                                                                                                                                            |                            |

| 25                   |                                                                                                                                                                                                            |                            |

|                      | Plane Processor                                                                                                                                                                                            |                            |

| 26                   |                                                                                                                                                                                                            |                            |

| 27                   | PCI DC Parameters                                                                                                                                                                                          | 81                         |

| 28                   | USB v1.1 DC Parameters                                                                                                                                                                                     | 81                         |

| 29                   | UTOPIA Level 2 DC Parameters                                                                                                                                                                               | 82                         |

| 30                   | MII DC Parameters                                                                                                                                                                                          | 82                         |

| 31                   | MDIO DC Parameters                                                                                                                                                                                         | 82                         |

| 32                   |                                                                                                                                                                                                            |                            |

| 33                   |                                                                                                                                                                                                            |                            |

| 34                   | •                                                                                                                                                                                                          |                            |

| 35                   |                                                                                                                                                                                                            |                            |

| 36                   |                                                                                                                                                                                                            |                            |

| 37                   |                                                                                                                                                                                                            |                            |

| 38                   |                                                                                                                                                                                                            |                            |

| 39                   | —                                                                                                                                                                                                          |                            |

| 40                   |                                                                                                                                                                                                            |                            |

|                      |                                                                                                                                                                                                            |                            |

| 41                   |                                                                                                                                                                                                            |                            |

| 42                   | 5 1 1                                                                                                                                                                                                      |                            |

| 43                   | 5                                                                                                                                                                                                          |                            |

| 44                   | 5                                                                                                                                                                                                          |                            |

| 45                   | UTOPIA Level 2 Clock Timings                                                                                                                                                                               | 88                         |

| 46                   |                                                                                                                                                                                                            | ~ ~                        |

|                      | 1 5                                                                                                                                                                                                        |                            |

| 47                   | PCI Bus Signal Timings                                                                                                                                                                                     | 89                         |

| 48                   | PCI Bus Signal Timings<br>UTOPIA Level 2 Input Timings Values                                                                                                                                              | 89<br>90                   |

| 48<br>49             | PCI Bus Signal Timings<br>UTOPIA Level 2 Input Timings Values<br>UTOPIA Level 2 Output Timings Values                                                                                                      | 89<br>90<br>91             |

| 48<br>49<br>50       | PCI Bus Signal Timings<br>UTOPIA Level 2 Input Timings Values<br>UTOPIA Level 2 Output Timings Values<br>MII Output Timings Values                                                                         | 89<br>90<br>91<br>91       |

| 48<br>49<br>50<br>51 | <ul> <li>PCI Bus Signal Timings</li> <li>UTOPIA Level 2 Input Timings Values</li> <li>UTOPIA Level 2 Output Timings Values</li> <li>MII Output Timings Values</li> <li>MII Input Timings Values</li> </ul> | 89<br>90<br>91<br>91<br>92 |

| 48<br>49<br>50       | <ul> <li>PCI Bus Signal Timings</li> <li>UTOPIA Level 2 Input Timings Values</li> <li>UTOPIA Level 2 Output Timings Values</li> <li>MII Output Timings Values</li> <li>MII Input Timings Values</li> </ul> | 89<br>90<br>91<br>91<br>92 |

| 53 | SDRAM Input Timings Values                                             | 93  |

|----|------------------------------------------------------------------------|-----|

| 54 | SDRAM Output Timings Values                                            | 94  |

| 55 | Signal Timing With Respect to Clock Rising Edge                        | 95  |

| 56 | Intel <sup>®</sup> Multiplexed Mode Values                             | 98  |

| 57 | Intel Simplex Mode Values                                              | 101 |

| 58 | Motorola* Multiplexed Mode Values                                      | 103 |

| 59 | Motorola* Simplex Mode Values                                          |     |

| 60 | HPI Timing Symbol Description                                          | 109 |

| 61 | HPI-8 Mode Write Access Values                                         | 109 |

| 62 | HPI-16 Multiplexed Write Accesses Values                               | 110 |

| 63 | HPI-16 Multiplexed Read Accesses Values                                | 112 |

| 64 | HPI-16 Simplex Read Accesses Values                                    |     |

| 65 | HPI-16 Simplex Write Accesses Values                                   | 116 |

| 66 | High-Speed, Serial Timing Values                                       |     |

| 67 | Boundary-Scan Interface Timings Values                                 |     |

| 68 | Reset Timings Table Parameters                                         |     |

| 69 | I <sub>CC</sub> and Total Average Power – Commercial Temperature Range |     |

| 70 | I <sub>CC</sub> and Total Average Power – Extended Temperature Range   | 127 |

I

## **Revision History**

| Date        | Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| June 2007   | 007      | 1. Added B-1 stepping information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| August 2006 | 006      | <ol> <li>Table 3, Table 21: Added the FWIXP423BD, 533 MHz IXP423</li> <li>Clarified GPIO functions in Section 2.1.11</li> <li>Updated Pin Types in Table 11 and Table 12</li> <li>Added Section 3.1 to help explain the tables outlined in Table 6</li> <li>Modified some signals in Table 8 through Table 17 to be pulled up when<br/>unused in new designs. No change to existing designs.</li> <li>Updated Power on Reset or Sys Reset column values in Table 17 and<br/>Table 19</li> <li>Table 21: Removed the IXC1100</li> <li>Corrected the maximum Talepulse value in Table 55</li> <li>Clarified ordering information in Section 6.0</li> <li>Updated Intel<sup>®</sup> product branding. References to Intel XScale core were<br/>updated to Intel XScale Processor.</li> <li>Incorporated specification changes, specification clarifications and documen<br/>changes from the Intel<sup>®</sup> IXP4XX Product Line of Network Processors<br/>Specification Update (306428-004)</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| March 2005  | 005      | <ol> <li>Rearranged product features lists in Section 1.2, "Product Features"</li> <li>Added two new columns to Table 3 to indicate Software Enable/Disable, an<br/>IXP423 network processor features</li> <li>Replaced network processor block diagrams: Figure 1, Figure 2, Figure 3,<br/>Figure 4, and Figure 5</li> <li>Added new row for the IXP423 network processor to Table 4, "Processor<br/>Functions"</li> <li>Corrected the PCI_IDSEL definition in Table 8, "PCI Controller"</li> <li>Added pull-up resistor requirement for the ETH_MDIO pin in Table 11, "MI<br/>Interfaces"</li> <li>Added footnote to Table 19, "System Interface11" regarding system level<br/>reset</li> <li>Added part number for IXP423 on Table 21, "Part Numbers for the Intel<sup>®</sup><br/>IXP42X Product Line of Network Processors"</li> <li>Changed VIH "Minimum" parameter to 2.0 in Table 28, "USB v1.1 DC<br/>Parameters" (see the Intel<sup>®</sup> IXP4XX Product Line of Network Processors<br/>Specification Update (306428)); added note 2</li> <li>Added footnote regarding PLL operation at the lowest slew rate to Table 47<br/>"Devices' Clock Timings (Oscillator Reference)"</li> <li>Added footnote to Table 51, "Signal Timing With Respect to Clock Rising Edge"</li> <li>Inserted new Figure 25, "Signal Timing With Respect to Clock Rising Edge"</li> <li>Updated Table 55, "Signal Timing With Respect to Clock Rising Edge"</li> <li>Updated Table 55, "Signal Timing With Respect to Clock Rising Edge"</li> <li>Updated Table 55, "Signal Timing With Respect to Clock Rising Edge"</li> <li>Added footnotes to Table 63, "HPI-16 Multiplexed Read Accesses Values"</li> <li>Added footnotes to Table 63, "HPI-16 Multiplexed Read Accesses Values"</li> <li>Added footnotes to Table 63, "HPI-16 Multiplexed Read Accesses Values"</li> </ol> |

| June 2004   | 004      | Updated Intel <sup>®</sup> product branding. Change bars are retained from the previous release of this document (-003).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| April 2004  | 003      | Incorporated specification changes, specification clarifications and document changes from the Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Specification Update (252702-003).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| May 2003    | 002      | Incorporated specification changes, specification clarifications and document changes from the Intel <sup>®</sup> IXP42X Product Line of Network Processors Specification Update (252702-001).<br>Incorporated information for the Intel <sup>®</sup> IXC1100 Control Plane Processor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 001      | Initial release of this document. Document reissued, without "Confidential" markin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

§§

## 1.0 Introduction

#### 1.1 About this Document

This datasheet contains a functional overview of the Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor, mechanical data (package signal locations and simulated thermal characteristics), targeted electrical specifications, and some bus functional wave forms for the device. Detailed functional descriptions other than parametric performance are published in the *Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Developer's Manual.*

Other related documents are shown in Table 1.

#### Table 1. Related Documents

| Document Title                                                                                                              | Document # |

|-----------------------------------------------------------------------------------------------------------------------------|------------|

| Intel <sup>®</sup> IXP4XX Product Line of Network Processors Specification Update                                           | 306428     |

| Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Developer's Manual         | 252480     |

| Intel <sup>®</sup> IXP400 Software Programmer's Guide                                                                       | 252539     |

| Intel <sup>®</sup> IXP400 Software Specification Update                                                                     | 273795     |

| Intel XScale® Core Developer's Manual                                                                                       | 273473     |

| Intel <sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Hardware Design Guidelines | 252817     |

| Intel XScale <sup>®</sup> Microarchitecture Technical Summary                                                               | —          |

| PCI Local Bus Specification, Rev. 2.2                                                                                       | —          |

| Universal Serial Bus Specification, Revision 1.1                                                                            | —          |

#### Table 2.Terminology and Acronyms

| Acronym/<br>Terminology | Description                                      |  |  |  |

|-------------------------|--------------------------------------------------|--|--|--|

| AAL                     | ATM Adaptation Layers                            |  |  |  |

| AES                     | Advanced Encryption Standard                     |  |  |  |

| AHB                     | Advanced High-Performance Bus                    |  |  |  |

| APB                     | Advanced Peripheral Bus                          |  |  |  |

| API                     | Application Program Interface                    |  |  |  |

| Assert                  | The logically active value of a signal or bit.   |  |  |  |

| ATM                     | ATM Asynchronous Transmission Mode               |  |  |  |

| AQM                     | AHB Queue Manager                                |  |  |  |

| BTB                     | Branch Target Buffer                             |  |  |  |

| CRC                     | Cyclical Redundancy Check                        |  |  |  |

| Deassert                | The logically inactive value of a signal or bit. |  |  |  |

| DDR                     | Double Data Rate                                 |  |  |  |

| DES                     | Data-Encryption Standard                         |  |  |  |

| DMA                     | Direct Memory Access                             |  |  |  |

| DSP                     | Digital Signal Processor                         |  |  |  |

#### Table 2.Terminology and Acronyms (Continued)

| Acronym/<br>Terminology | Description                                                                                                                           |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| E1                      | Euro 1 trunk line                                                                                                                     |

| FIFO                    | First In First Out                                                                                                                    |

| GCI                     | General Circuit Interface                                                                                                             |

| GPIO                    | General-purpose input/output                                                                                                          |

| HDLC                    | High-level Data Link Control                                                                                                          |

| HPI                     | (Texas Instruments*) Host Port Interfaces                                                                                             |

| HSS                     | High-Speed Serial (port)                                                                                                              |

| LSb                     | Least-Significant bit                                                                                                                 |

| LSB                     | Least-Significant Byte                                                                                                                |

| MAC                     | Media Access Controller                                                                                                               |

| MDIO                    | Management Data Input/Output                                                                                                          |

| MH                      | Media-Independent Interface                                                                                                           |

| MMU                     | Memory Management Unit                                                                                                                |

| MSb                     | Most-Significant bit                                                                                                                  |

| MSB                     | Most-Significant Byte                                                                                                                 |

| NPE                     | Network Processor Engine                                                                                                              |

| PCI                     | Peripheral Component Interconnect                                                                                                     |

| PHY                     | Physical Layer (Layer 1) Interface                                                                                                    |

| Reserved                | A field that may be used by an implementation. Software should not modify reserved fields or depend on any values in reserved fields. |

| RX                      | Receive (HSS is receiving from off-chip)                                                                                              |

| SRAM                    | Static Random Access Memory                                                                                                           |

| SDRAM                   | Synchronous Dynamic Random Access Memory                                                                                              |

| T1                      | Type 1 trunk line                                                                                                                     |

| TX                      | Transmit (HSS is transmitting off-chip)                                                                                               |

| UART                    | Universal Asynchronous Receiver-Transmitter                                                                                           |

| USB                     | Universal Serial Bus                                                                                                                  |

| UTOPIA                  | Universal Test and Operations PHY Interface for ATM                                                                                   |

| WAN                     | Wide Area Network                                                                                                                     |

#### 1.2 **Product Features**

#### 1.2.1 Product Line Features

This section outlines the features that apply to the Intel^ $^{\textcircled{B}}$  IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor.

Some of the features described in this document require enablement by software delivered by Intel. Some features may not be enabled with current software releases.

The features that require software are identified below. Refer to the *Intel<sup>®</sup> IXP400 Software Programmer's Guide* for information on features that are currently enabled.

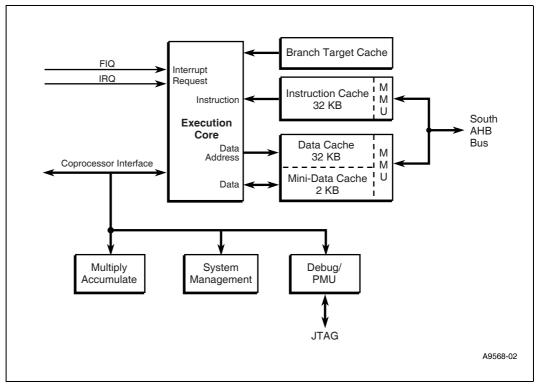

- Intel XScale<sup>®</sup> Processor (compliant with ARM<sup>\*</sup> architecture)

- High-performance processor based on Intel XScale<sup>®</sup> Microarchitecture

- Seven/eight-stage Intel<sup>®</sup> Super-Pipelined RISC Technology

- Management unit

- 32-entry, data memory management unit

- 32-entry, instruction memory management unit

- 32-Kbyte, 32-way, set associative instruction cache

- 32-Kbyte, 32-way, set associative data cache

- · 2-Kbyte, two-way, set associative mini-data cache

- 128-entry, branch target buffer

- Eight-entry write buffer

- · Four-entry fill and pend buffers

- Clock speeds:

- 266 MHz

- 400 MHz

- 533 MHz

- ARM<sup>\*</sup> Version V5TE Compliant

- Intel<sup>®</sup> Media Processing Technology Multiply-accumulate coprocessor

- Debug unit Accessible through JTAG port

- PCI interface

- 32-bit interface

- Selectable clock

- 33 MHz clock output derived from either GPIO14 or GPIO15

- 33 and 66 MHz clock input

- PCI Local Bus Specification, Rev. 2.2 compatible

- PCI arbiter supporting up to four external PCI devices (four REQ/GNT pairs)

- Host/option capable

- Master/target capable

- Two DMA channels

- USB v 1.1 device controller

- Full-speed capable

- Embedded transceiver

- 16 endpoints

- SDRAM interface

- 32-bit data

- 13-bit address

- 133 MHz

- Up to eight open pages simultaneously maintained

- Programmable auto-refresh

- Programmable CAS/data delay

- Support for 8 MB, minimum, up to 256 MB maximum

- Expansion interface

- 24-bit address

- 16-bit data

- Eight programmable chip selects

- Supports Intel/Motorola\* microprocessors

- Multiplexed-style bus cycles

- Simplex-style bus cycles

- DSP support for:

- Texas Instruments\* DSPs supporting HPI-8 bus cycles

- Texas Instruments DSPs supporting HPI-16 bus cycles

- High-speed/Console UARTs

- 1,200 baud to 921 Kbaud

- 16550 compliant

- 64-byte Tx and Rx FIFOs

- CTS and RTS modem control signals

- · Internal bus performance monitoring unit

- Seven 27-bit event counters

- Monitoring of internal bus occurrences and duration events

- 16 GPIOs

- Four internal timers

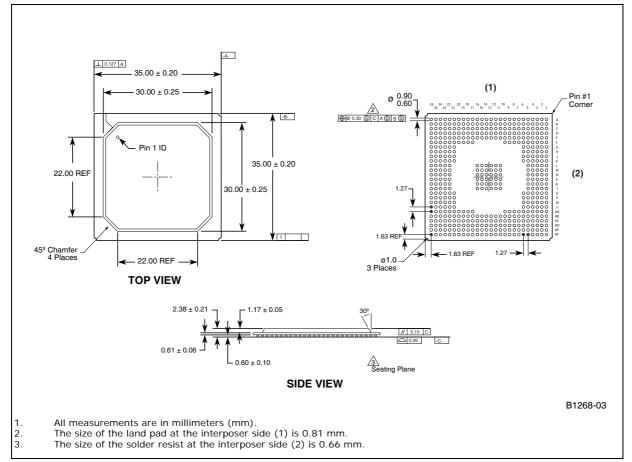

- Packaging

- 492-pin PBGA

- Commercial temperature (0° to +70° C)

- Extended temperature (-40° to +85° C)

The remaining features described in the product line features list require software in order for these features to be functional. To determine if the feature is enabled, see the *Intel<sup>®</sup> IXP400 Software Programmer's Guide*.

- Three network processor engines (NPEs) Note 1 Used to offload typical Layer-2 networking functions such as:

- Ethernet filtering

- ATM SARing

- HDLC

- Encryption/Authentication/Hashing Note 1

- DES

- Triple-DES (3DES)

- AES 128-bit and 256-bit

- ARC4/WEP-CRC

- SHA-1

- MD5

- Two MII interfaces Note 1

- 802.3 MII interfaces

- Single MDIO interface to control both MII interfaces

- UTOPIA Level 2 Interface Note 1

- Eight-bit interface

- Up to 33 MHz clock speed

- Five transmit and five receive address lines

- Two high-speed, serial interfaces Note 1

- Six-wire

- Supports speeds up to 8.192 MHz

- Supports connection to T1/E1 framers

- Supports connection to CODEC/SLICs

- Eight HDLC Channels

- This feature requires Intel supplied software. To determine if this feature is enabled by a particular software release, see the  $Intel^{@}$  IXP400 Software Programmer's Guide. Note:

#### 1.2.2 **Processor Features**

Table 3 on page 13 describes the features that apply to the Intel® IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor.

| Feature                   | Requires<br>Enabling<br>Software<br>(Note 1) | Intel <sup>®</sup><br>IXP425<br>Network<br>Processor | Intel <sup>®</sup><br>IXP423<br>Network<br>Processor | Intel <sup>®</sup><br>IXP422<br>Network<br>Processor | Intel <sup>®</sup><br>IXP421<br>Network<br>Processor | Intel <sup>®</sup><br>IXP420<br>Network<br>Processor | Intel <sup>®</sup><br>IXC1100<br>Control<br>Plane<br>Processor |

|---------------------------|----------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|----------------------------------------------------------------|

| Processor<br>Speed (MHz)  |                                              | 266/400/533                                          | 266/533                                              | 266                                                  | 266                                                  | 266/400/533                                          | 266/400/533                                                    |

| UTOPIA 2                  | Yes                                          | Х                                                    | Х                                                    |                                                      | Х                                                    |                                                      |                                                                |

| GPIO                      |                                              | Х                                                    | Х                                                    | Х                                                    | Х                                                    | х                                                    | Х                                                              |

| UART 0/1                  |                                              | х                                                    | х                                                    | х                                                    | х                                                    | х                                                    | х                                                              |

| HSS 0                     | Yes                                          | х                                                    | х                                                    |                                                      | Х                                                    |                                                      |                                                                |

| HSS 1                     | Yes                                          | х                                                    | х                                                    |                                                      | х                                                    |                                                      |                                                                |

| MII O                     | Yes                                          | х                                                    | х                                                    | х                                                    | Х                                                    | х                                                    | х                                                              |

| MII 1                     | Yes                                          | х                                                    | х                                                    | х                                                    |                                                      | Х                                                    | Х                                                              |

| USB                       |                                              | х                                                    | х                                                    | х                                                    | х                                                    | х                                                    | х                                                              |

| PCI                       |                                              | х                                                    | х                                                    | х                                                    | Х                                                    | х                                                    | х                                                              |

| Expansion<br>Bus          |                                              | 16-bit, 66 MHz                                                 |

| SDRAM                     |                                              | 32-bit, 133<br>MHz                                             |

| AES / DES /<br>3DES       | Yes                                          | х                                                    |                                                      | х                                                    |                                                      |                                                      |                                                                |

| Multi-<br>Channel<br>HDLC | Yes                                          | 8                                                    | 8                                                    |                                                      | 8                                                    |                                                      |                                                                |

| Notes:                    |                                              | <u> </u>                                             | <u> </u>                                             | <u> </u>                                             |                                                      |                                                      |                                                                |

#### Table 3. Processor Features (Sheet 1 of 2)

The features marked "Yes" require enabling software. Refer to the Intel® IXP400 Software Programmer's Guide to 1. determine if the feature is enabled.

2. Only the 266 MHz version of the Intel<sup>®</sup> IXP420 Network Processor supports extended temperature.

| Feature                   | Requires<br>Enabling<br>Software<br>(Note 1) | Intel <sup>®</sup><br>IXP425<br>Network<br>Processor | Intel <sup>®</sup><br>IXP423<br>Network<br>Processor | Intel <sup>®</sup><br>IXP422<br>Network<br>Processor | Intel <sup>®</sup><br>IXP421<br>Network<br>Processor | Intel <sup>®</sup><br>IXP420<br>Network<br>Processor | Intel®<br>IXC1100<br>Control<br>Plane<br>Processor |

|---------------------------|----------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|----------------------------------------------------|

| SHA-1 /<br>MD-5           | Yes                                          | Х                                                    |                                                      | х                                                    |                                                      |                                                      |                                                    |

| Commercial<br>Temperature |                                              | Х                                                    | Х                                                    | х                                                    | х                                                    | Х                                                    | х                                                  |

| Extended<br>Temperature   |                                              | х                                                    |                                                      |                                                      |                                                      | X (Note 2)                                           | х                                                  |

#### Table 3.Processor Features (Sheet 2 of 2)

Notes:

1. The features marked "Yes" require enabling software. Refer to the Intel<sup>®</sup> IXP400 Software Programmer's Guide to determine if the feature is enabled.

Only the 266 MHz version of the Intel<sup>®</sup> IXP420 Network Processor supports extended temperature.

## 2.0 Functional Overview

The Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor are compliant with the ARM<sup>\*</sup> Version 5TE instruction-set architecture (ISA). The Intel<sup>®</sup> IXP42X product line and IXC1100 control plane processors are designed with Intel 0.18-micron production semiconductor process technology. This process technology — along with the compactness of the Intel XScale<sup>®</sup> processor, the ability to simultaneously process up to three integrated network processing engines (NPEs), and numerous dedicated-function peripheral interfaces — enables the IXP42X product line and IXC1100 control plane processors to operate over a wide range of low-cost networking applications, with industry-leading performance.

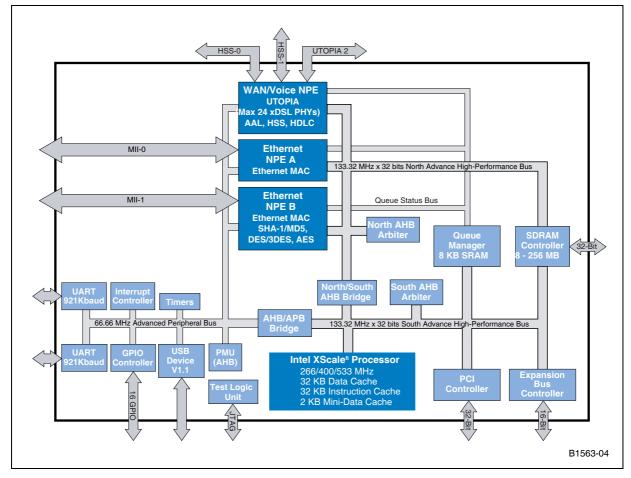

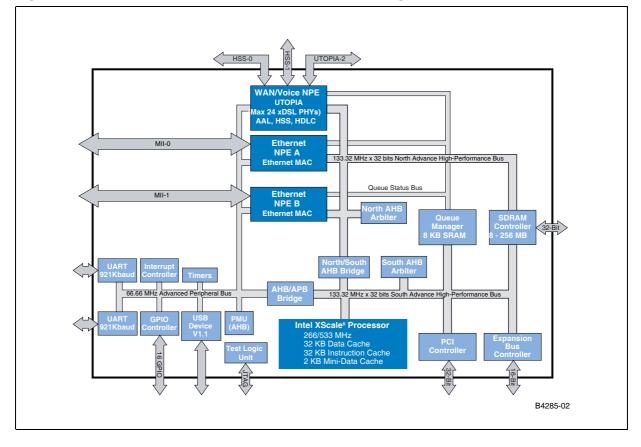

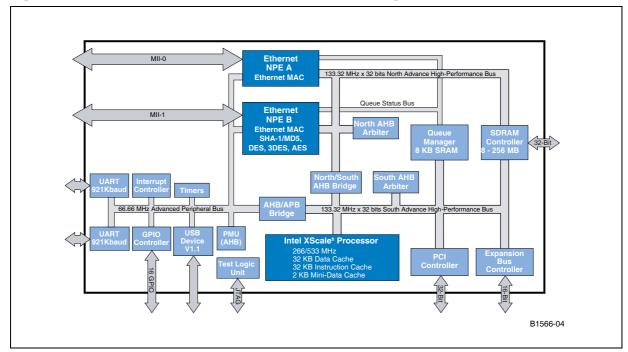

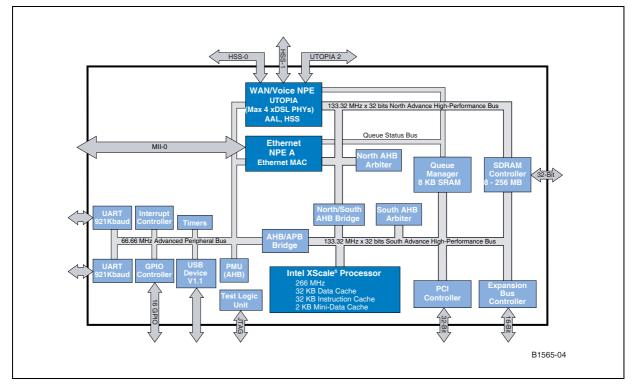

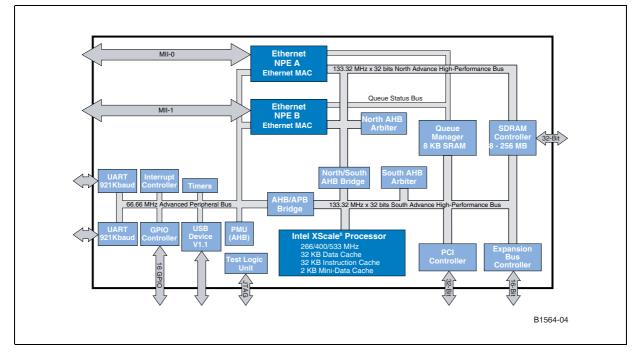

As indicated in Figure 1 through Figure 5, the Intel<sup>®</sup> IXP42X product line and IXC1100 control plane processors combine many features with the Intel XScale<sup>®</sup> Processor to create a highly integrated processor applicable to LAN/WAN-based networking applications in addition to other embedded networking applications.

This section briefly describes the main features of the product. For detailed functional descriptions, see the *Intel<sup>®</sup> IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Developer's Manual.*

#### Figure 1. Intel<sup>®</sup> IXP425 Network Processor Block Diagram

#### Figure 2. Intel<sup>®</sup> IXP423 Network Processor Block Diagram

#### Figure 3. Intel<sup>®</sup> IXP422 Network Processor Block Diagram

#### Figure 4. Intel<sup>®</sup> IXP421 Network Processor Block Diagram

#### Figure 5. Intel<sup>®</sup> IXP420 Network Processor Block Diagram

#### 2.1 Functional Units

The following sections briefly the functional units and their interaction in the system. For more detailed information, refer to the *Intel® IXP42X Product Line of Network Processors and IXC1100 Control Plane Processor Developer's Manual.*

Unless otherwise specified, the functional descriptions apply to all processors in the IXP42X product line and IXC1100 control plane processors. Refer to Table 3 on page 13 and Figure 1 on page 15 through Figure 5 for specific information on supported interfaces.

#### 2.1.1 Network Processor Engines (NPEs)

The network processor engines (NPEs) are dedicated-function processors containing hardware coprocessors integrated into the IXP42X product line and IXC1100 control plane processors. The NPEs are used to off-load processing functions required by the Intel XScale<sup>®</sup> processor.

These NPEs are high-performance, hardware-multi-threaded processors with additional local-hardware-assist functionality used to off-load highly processor-intensive functions such as MII (MAC), CRC checking/generation, AAL segmentation and re-assembly, AES, DES, 3DES, SHA-1, and MD5. All instruction code for the NPEs are stored locally with a dedicated instruction memory bus and dedicated data memory bus.

These NPEs support processing of the dedicated peripherals that can include:

- A Universal Test and Operation PHY Interface for ATM (UTOPIA) 2 interface

- Two High-Speed Serial (HSS) interfaces

- Two Media-Independent Interfaces (MII)

Table 4 specifies which devices, in the IXP42X product line and IXC1100 control plane processors, have which of these capabilities.

#### Table 4. Processor Functions

| Device                                                   | υτορία | HSS | ΜΠΟ | MII 1 | AES / DES<br>/ 3DES | Multi-Channel HDLC | SHA-1 /<br>MD-5 |

|----------------------------------------------------------|--------|-----|-----|-------|---------------------|--------------------|-----------------|

| Intel <sup>®</sup> IXP425 Network<br>Processor           | Х      | х   | х   | х     | х                   | 8                  | х               |

| Intel <sup>®</sup> IXP423 Network<br>Processor           | х      | х   | х   | х     |                     | 8                  |                 |

| Intel <sup>®</sup> IXP422 Network<br>Processor           |        |     | х   | х     | х                   |                    | х               |

| Intel <sup>®</sup> IXP421 Network<br>Processor           | Х      | х   | х   |       |                     | 8                  |                 |

| Intel <sup>®</sup> IXP420 Network<br>Processor           |        |     | х   | х     |                     |                    |                 |