# 16 V 5 + 1-Channel Operational Amplifier

**ADD8706**

## **FEATURES**

Single-supply operation: 4.5 V to 16.5 V Upper/lower buffers swing to V<sub>s</sub>/GND Continuous output current: 35 mA V<sub>COM</sub> peak output current: 250 mA

Offset voltage: 15 mV Slew rate: 6 V/µs

Unity gain stable with large capacitive loads

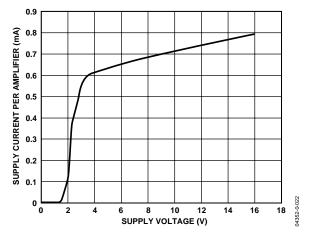

Supply current: 750 µA per amplifier

#### **APPLICATIONS**

TFT LCD monitor panels

TFT LCD notebook panels

Communications equipment

Portable instrumentation

Electronic games

ADC/DAC buffer

### **GENERAL DESCRIPTION**

The ADD8706 is a single-supply, 5-channel buffer with a separate  $V_{\text{COM}}$  amplifier that has been optimized for today's low cost TFT LCD notebook and monitor panels. The top and bottom channels swing to the top/bottom rails, respectively, and can be used as end-point gamma references. The middle channels are ideal for midpoint gamma references. The  $V_{\text{COM}}$  amplifier provides very high continuous and peak currents. All channels have excellent transient response as well as high slew rate and capacitive load drive capability. The ADD8706 is specified over the  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$  temperature range. The ADD8706 is available in a 16-lead TSSOP package.

**Table 1. Input Output Characteristics**

| Channel | V <sub>IH</sub>        | VIL         | lo (mA) | Isc (mA) |

|---------|------------------------|-------------|---------|----------|

| Α       | Vs                     | GND + 1.7 V | 15      | 150      |

| В       | V <sub>s</sub> – 1.7 V | GND         | 15      | 150      |

| C       | V <sub>s</sub> – 1.7 V | GND         | 15      | 150      |

| D       | V <sub>s</sub> – 1.7 V | GND         | 15      | 150      |

| E       | V <sub>s</sub> – 1.7 V | GND         | 15      | 150      |

| F       | V <sub>S</sub> – 1.7 V | GND         | 35      | 250      |

## **PIN CONFIGURATION**

Figure 1. 16-Lead TSSOP

# **ADD8706**

# **TABLE OF CONTENTS**

| Electrical Characteristics          | Theory |

|-------------------------------------|--------|

| Absolute Maximum Ratings 5          | ,      |

| ESD Caution                         |        |

| Typical Performance Characteristics | 1      |

| Application Information             |        |

## **REVISION HISTORY**

Revision 0: Initial Version

Rev. 0 | Page 2 of 12

# **ELECTRICAL CHARACTERISTICS**

Table 2.  $V_S$  = 16 V,  $V_{CM}$  =  $V_S/2$ ,  $T_A$  @ 25 °C, unless otherwise noted

| Parameter                          | Symbol                   | Condition                                                                                 | Min   | Тур    | Max   | Unit  |

|------------------------------------|--------------------------|-------------------------------------------------------------------------------------------|-------|--------|-------|-------|

| SUPPLY CHARACTERISTICS             |                          |                                                                                           |       |        |       |       |

| Supply Voltage                     | Vs                       |                                                                                           | 4.5   |        | 16    | V     |

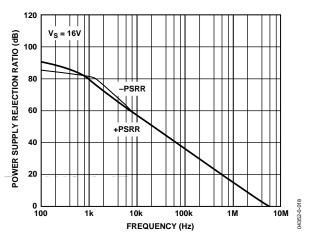

| Power Supply Rejection Ratio       | PSRR                     | $V_S = 4 \text{ V to } 17 \text{ V}, -40^{\circ}\text{C} \le T_A \le +85^{\circ}\text{C}$ | 70    | 90     |       | dB    |

| Total Supply Current               | Isy                      | $V_0 = V_s/2$ , No Load                                                                   |       | 4.5    | 5.4   | mA    |

|                                    |                          | $-40$ °C $\leq T_A \leq +85$ °C                                                           |       |        | 6     | mA    |

| INPUT CHARACTERISTICS              |                          |                                                                                           |       |        |       |       |

| Offset Voltage                     | Vos                      |                                                                                           |       | 2      | 15    | mV    |

| Offset Voltage Drift               | $\Delta V_{OS}/\Delta T$ | $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                   |       | 10     |       | μV/°C |

| Input Bias Current                 | I <sub>B</sub>           |                                                                                           |       | 400    | 1100  | nA    |

|                                    |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                     |       |        | 1500  | nA    |

| Input Offset Current               | los                      |                                                                                           |       | 10     | 100   | nA    |

| Amplifier F                        |                          | $-40^{\circ}\text{C} \le \text{T}_{A} \le +85^{\circ}\text{C}$                            |       |        | 250   | nA    |

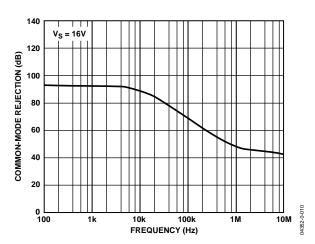

| Common-Mode Rejection Ratio        | CMRR                     | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                     |       |        |       |       |

| Amplifier F                        |                          | $V_{CM} = 0$ to $(V_S - 1.7 \text{ V})$                                                   | 54    | 95     |       | dB    |

| Input Impedance                    | Z <sub>IN</sub>          |                                                                                           |       | 400    |       | kΩ    |

| Input Capacitance                  | C <sub>IN</sub>          |                                                                                           |       | 1      |       | pF    |

| OUTPUT CHARACTERISTICS             |                          |                                                                                           |       |        |       | '     |

| Output Voltage High (A)            | V <sub>OH</sub>          | $V_{IN} = 16 \text{ V}, I_L = 100 \mu\text{A}$                                            |       | 15.99  |       | V     |

| Optimized for High Swing           | 10                       | $V_{IN} = 16 \text{ V}, I_L = 5 \text{ mA}$                                               | 15.75 | 15.85  |       | V     |

|                                    |                          | $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                   | 15.65 |        |       | V     |

| Output Voltage High (B to D)       | $V_{OH}$                 | $V_{IN} = 14 \text{ V}, I_L = 100  \mu\text{A}$                                           | 10.00 | 14     |       | V     |

| Optimized for Midrange             | 1011                     | $V_{IN} = 14 \text{ V}, I_L = 5 \text{ mA}$                                               | 13.90 | 13.985 |       | V     |

| opzea ioi iiiaiai.ge               |                          | $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                   | 13.85 |        |       | V     |

| Output Voltage High (E)            | V <sub>OH</sub> —        | $V_{IN} = 14 \text{ V}, I_L = 100  \mu\text{A}$                                           | -     | 14     |       | V     |

| Optimized for Low Swing            |                          | $V_{IN} = 14 \text{ V}, I_L = 5 \text{ mA}$                                               | 13.9  | 13.99  |       | V     |

| ,                                  |                          | $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                   | 13.85 |        |       | V     |

| Output Voltage High (F)            | V <sub>OH</sub>          | $V_{IN} = 16 \text{ V}, I_L = 100 \mu\text{A}$                                            |       | 15.995 |       | V     |

| Optimized for V <sub>COM</sub>     | J.,                      | $V_{IN} = 16 \text{ V}, I_L = 5 \text{ mA}$                                               | 15.8  | 15.9   |       | V     |

| 22                                 |                          | $-40^{\circ}\text{C} \le \text{T}_{\text{A}} \le +85^{\circ}\text{C}$                     | 15.75 |        |       | V     |

| Output Voltage Low (A)             | V <sub>OL</sub>          | $V_{IN} = 1.7 \text{ V}, I_L = 100 \mu\text{A}$                                           |       | 1.70   |       | V     |

| Optimized for High Swing           | 102                      | $V_{IN} = 1.7 \text{ V}, I_L = 5 \text{ mA}$                                              |       | 1.71   | 1.730 | V     |

|                                    |                          | $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                   |       |        | 1.725 | V     |

| Output Voltage Low (B–D)           | V <sub>OL</sub>          | $V_{IN} = 0 \text{ V, } I_L = 100  \mu\text{A}$                                           |       | 5      | 5     | mV    |

| Optimized for Midrange             | 102                      | $V_{IN} = 0 \text{ V, } I_L = 5 \text{ mA}$                                               |       | 200    | 300   | mV    |

| op200                              |                          | $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                   |       |        | 350   | mV    |

| Output Voltage Low (E)             | V <sub>OL</sub>          | $V_{IN} = 0 \text{ V, } I_L = 100  \mu\text{A}$                                           |       | 5      |       | mV    |

| Optimized for Low Swing            | 102                      | $V_{IN} = 0 \text{ V, } I_L = 5 \text{ mA}$                                               |       | 80     | 200   | mV    |

| opg                                |                          | $-40^{\circ}\text{C} \le T_{A} \le +85^{\circ}\text{C}$                                   |       |        | 300   | mV    |

| Output Voltage Low (F)             | V <sub>OL</sub>          | $V_{IN} = 0 \text{ V, } I_L = 100  \mu\text{A}$                                           |       | 5      |       | mV    |

| Optimized for V <sub>COM</sub>     | 1 02                     | $V_{IN} = 0 \text{ V, } I_L = 5 \text{ mA}$                                               |       | 50     | 150   | mV    |

| - p22                              |                          | $-40^{\circ}\text{C} \le \text{T}_{A} \le +85^{\circ}\text{C}$                            |       |        | 250   | mV    |

| Continuous Output Current (A to E) | Іоит                     | V <sub>S</sub> = 16 V                                                                     |       | 15     |       | mA    |

| Continuous Output Current (F)      | lout                     | V <sub>S</sub> = 16 V                                                                     |       | 35     |       | mA    |

| Peak Output Current (A to E)       | I <sub>PK</sub>          | V <sub>S</sub> = 16 V                                                                     |       | 50     |       | mA    |

| Peak Output Current (F)            | I <sub>PK</sub>          | V <sub>S</sub> = 16 V                                                                     |       | 200    |       | mA    |

# **ADD8706**

| Parameter                | Symbol         | Condition                                                       | Min   | Тур    | Max   | Unit    |

|--------------------------|----------------|-----------------------------------------------------------------|-------|--------|-------|---------|

| TRANSFER CHARACTERISTICS |                |                                                                 |       |        |       |         |

| Amplifier Gain           | Avo            | $R_L = 2 k\Omega$ , $V_O = 0.5 \text{ to } (V_S - 2 \text{ V})$ | 1     | 10     |       | V/mV    |

| Buffer Gain              | Avcl           | $R_L = 2 k\Omega$                                               | 0.995 | 0.9985 | 1.005 | V/V     |

|                          |                | $-40$ °C $\leq T_A \leq +85$ °C                                 | 0.995 | 0.9980 | 1.005 | V/V     |

| Buffer Gain Linearity    | NL             | $R_L = 2k\Omega$ , $V_O = 0.5$ to $(V_S - 0.5 V)$               |       | 0.01   |       | %       |

| DYNAMIC PERFORMANCE      |                |                                                                 |       |        |       |         |

| Slew Rate                | SR             | $R_L = 2 k\Omega$ , $C_L = 200 pF$                              | 4     | 6      |       | V/µs    |

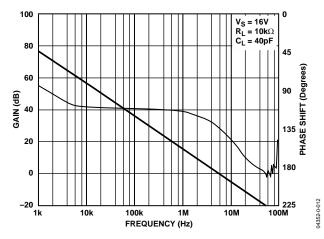

| Bandwidth                | BW             | $-3 \text{ dB, R}_L = 2 \text{ k}\Omega, C_L = 40 \text{ pF}$   |       | 6      |       | MHz     |

| Phase Margin             | Øo             | $R_L = 2 k\Omega$ , $C_L = 40 pF$                               |       | 55     |       | Degrees |

| Channel Separation       |                |                                                                 |       | 75     |       | dB      |

| NOISE PERFORMANCE        |                |                                                                 |       |        |       |         |

| Voltage Noise Density    | e <sub>n</sub> | f = 1  kHz                                                      |       | 26     |       | nV/√Hz  |

|                          |                | f = 10 kHz                                                      |       | 25     |       | nV/√Hz  |

| Current Noise Density    | in             | f = 10 kHz                                                      |       | 8.0    |       | pA/√Hz  |

Rev. 0 | Page 4 of 12

# **ABSOLUTE MAXIMUM RATINGS**

Table 3. ADD8706 Stress Ratings\*

| 1 1010 01 112 2 0 7 00 011 000 11111111190 |                                                  |  |  |  |  |

|--------------------------------------------|--------------------------------------------------|--|--|--|--|

| Parameter                                  | Rating                                           |  |  |  |  |

| Supply Voltage (V <sub>s</sub> )           | 18 V                                             |  |  |  |  |

| Input Voltage                              | $-0.5 \text{ V to V}_{\text{S}} + 0.5 \text{ V}$ |  |  |  |  |

| Differential Input Voltage                 | V <sub>s</sub>                                   |  |  |  |  |

| Storage Temperature Range                  | −65°C to +150°C                                  |  |  |  |  |

| Operating Temperature Range                | –40°C to +85°C                                   |  |  |  |  |

| Junction Temperature Range                 | −65°C to +150°C                                  |  |  |  |  |

| Lead Temperature Range                     | 300°C                                            |  |  |  |  |

| ESD Tolerance (HBM)                        | ±1500 V                                          |  |  |  |  |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

**Table 4. Package Characteristics**

| Package Type       | $\theta_{JA}^1$ | θις | Unit |

|--------------------|-----------------|-----|------|

| 16-Lead TSSOP (RU) | 180             | 35  | °C/W |

$^1\theta_{JA}$  is specified for worst-case conditions, i.e.,  $\theta_{JA}$  is specified for devices soldered onto a circuit board for surface-mount packages.

## **ESD CAUTION**

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although this product features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

# TYPICAL PERFORMANCE CHARACTERISTICS

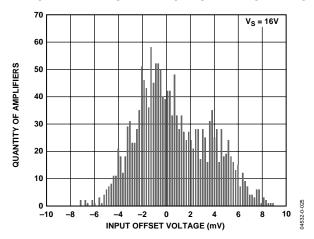

Figure 2. Input Offset Voltage,  $V_S = 16 V$

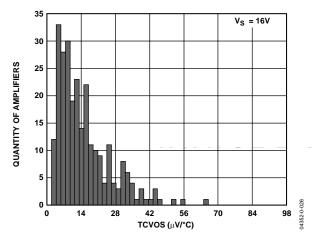

Figure 3. Input Offset Voltage Drift,  $V_S = 16 V$

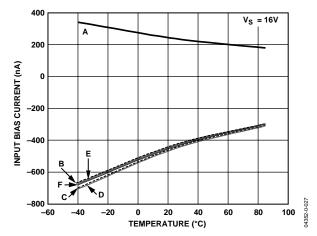

Figure 4. Input Bias Current vs. Temperature

Figure 5. Input Offset Current vs. Temperature

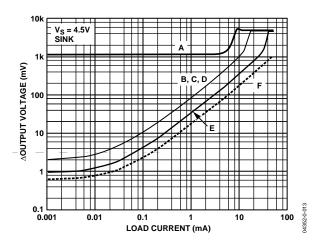

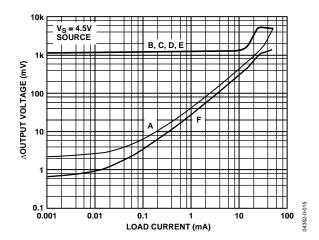

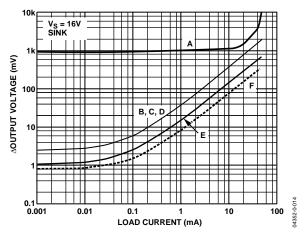

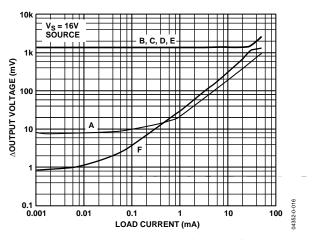

Figure 6. Output Sink Voltage vs. Load Current, All Channels

Figure 7. Output Source Voltage vs. Load Current, All Channels

Figure 8. Output Sink Voltage vs. Load Current, All Channels

Figure 9. Output Source Voltage vs. Load Current, All Channels

Figure 10. Supply Current vs. Supply Voltage

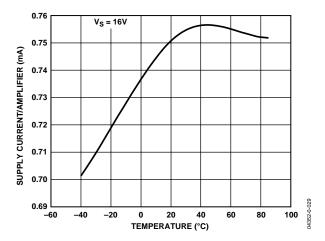

Figure 11. Supply Current vs. Temperature

Figure 12. PSRR vs. Frequency

Figure 13. CMRR vs. Frequency

# **ADD8706**

Figure 14. Frequency vs. Gain and Shift

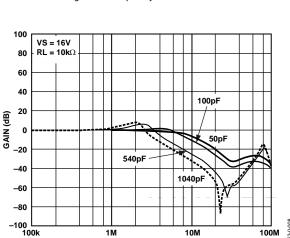

FREQUENCY (Hz) Figure 15. Gain vs. Capacitive Load

100M

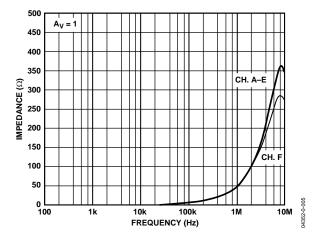

Figure 16. Impedance vs. Frequency

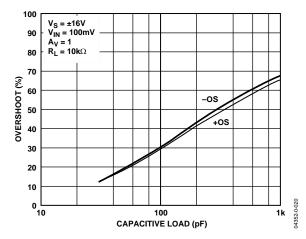

Figure 17. Overshoot vs. Capacitive Load

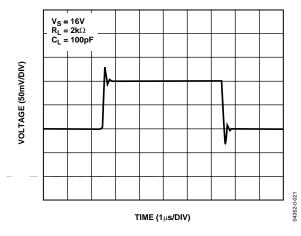

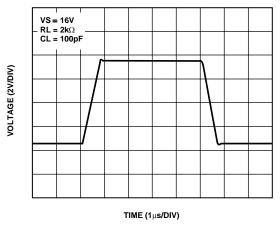

Figure 18. Small-Signal Transient Response

Figure 19. Large Signal Transient Response

# APPLICATION INFORMATION

#### **THEORY**

The ADD8706 is designed for use in LCD gamma correction circuits. This is an ideal on-chip solution for low-end panels. It provides five gamma voltages and a  $V_{\text{COM}}$  output. These gamma voltages provide the reference voltages for the column driver RDACs. Due to the capacitive nature of LCD panels, it is necessary for these drivers to provide high capacitive load drive.

The  $V_{\text{COM}}$  output is the center voltage common to all the LCD pixels. The  $V_{\text{COM}}$  circuit is common to all the pixels in the panel. This requires the  $V_{\text{COM}}$  driver to supply continuous currents up to 35 mA.

#### INPUT/OUTPUT CHARACTERISTICS

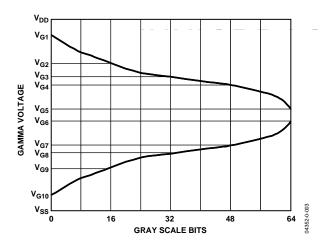

The ADD8706 has five buffers specifically designed for the needs of an LCD panel. Figure 20 shows a typical gamma correction curve for a normally white twisted nematic LCD panel. The symmetric curve comes from the need to reverse the polarity on the LC pixels to avoid "burning" in the image. Therefore, the application requires gamma voltages that come close to both supply rails. To accommodate this transfer function, the five ADD8706 buffers have been designed with three different buffer designs in one package.

Figure 20. LCD Gamma Correction Curve

The nature of LCD panels introduces a large amount of parasitic capacitance from the column drivers as well as the capacitance associated with the liquid crystals via the common plane. This makes capacitive drive capability an important factor when designing the gamma correction circuit.

The outputs of the buffers and amplifier have been designed to match the performance needs of the gamma correction and  $V_{\text{COM}}$  circuits. All have rail-to-rail outputs, but the current drive capabilities differ. The difference in current drive and input voltage range determine the buffer and amplifier use.

Buffer A has an NPN emitter-follower input stage, which provides an input range that includes the top rail, but is limited to 1.7 V away from the bottom rail. It is designed to source 15 mA of continuous current, making this buffer ideal for providing the top voltage on the RDAC string.

Buffers B, C, and D use a single-supply PNP input stage with an intermediate common-mode voltage range. The output was designed to sink or source up to 15 mA of continuous current. The limited input range and equivalent sink and source current make these buffers suitable for the middle voltage ranges on the RDAC string.

Buffer E also uses a single-supply PNP input stage, but the output is designed to sink only up to 15 mA of continuous current. This buffer is designed for the RDAC's lower range.

Amplifier F is designed with an input range limited to midscale applications. It is capable of delivering 35 mA of continuous current. These qualities make Amplifier F suitable for  $V_{\text{COM}}$  applications.

#### **IMPORTANT NOTE**

Because of the asymmetric nature of Buffers A and E, care must be taken to connect an input that forces the amplifiers to operate in their most productive output states. Buffer A has very limited sink capabilities, while Buffer E does not source well. Set the Buffer A input to enable the amplifier output to source current and set the Buffer E input to force a sinking output current. This means making sure the input is above the midpoint of the common-mode input range for Buffer A and below the midpoint for Buffer E. Mathematically speaking, make sure  $V_{\rm IN} > V_{\rm S}/2$  for Buffer A and  $V_{\rm IN} < V_{\rm S}/2$  for Buffer E.

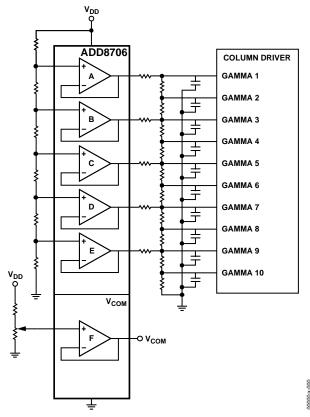

Figure 21 shows an application using the ADD8706 to generate 10 gamma outputs. Note that the five outputs are routed through another resistor network to generate the extra five output voltages, which feed into the column driver.

Figure 21. ADD8706 Application Circuit

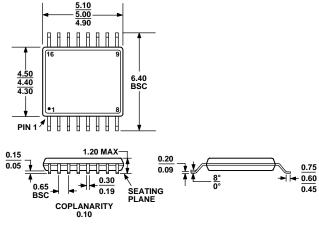

# **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MO-153AB

Figure 22. 16-Lead Thin Shrink Small Outline Package [TSSOP] (RU)

Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description | Package Option |

|--------------------|-------------------|---------------------|----------------|

| ADD8706ARUZ        | −40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

| ADD8706ARUZ-REEL   | -40°C to +85°C    | 16-Lead TSSOP       | RU-16          |

$<sup>^{1}</sup>$  Z = Pb-free part.

| ADD8706 |  |  |  |  |

|---------|--|--|--|--|

|---------|--|--|--|--|

**NOTES**