### 5 Port 10/100 Hardware NAT/NAPT Router

#### Features

| Ethernet Switch                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 32-bit CPU and Peripheral                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Built in 6 MAC and 5 PHY</li> <li>Support 10Base-T and 100Base-T on LAN ports</li> <li>Support 10Base-T, 100Base-TX and 100Base-FX on WAN port</li> <li>Up to 2K MAC addresses</li> <li>Broadcast storm protection</li> <li>Auto MDI-MDIX</li> <li>Layer2-4 Multi-Field classifier</li> <li>Support 8-MultiField entry</li> <li>Support 8-MultiField filter</li> <li>Support traffic policy</li> <li>Support trap to CPU port</li> <li>Class of Service</li> <li>Port based, MAC address, 802.1p, IPv4 ToS, IPv6 DSCP,TCP/UDP logical port and Multi-Field</li> <li>Support 4-level priority queues per port</li> <li>WRR/WFQ/SP</li> <li>Support 16 VLAN (IEEE Std 802.1q)</li> <li>Port-based/tagged-based VLAN</li> <li>Shared VLAN Learning/Independent VLAN Learning (SVL/IVL)</li> <li>Support STP, RSTP and MSTP</li> <li>Support STP, RSTP and MSTP</li> <li>Support bandwidth control</li> <li>Traffic Policy</li> <li>Support double tag header</li> <li>Provide per port LED</li> </ul> | <ul> <li>Provide 16-bit SDRAM (up to 32MB) with selectable clock speed.</li> <li>Optional serial/parallel bus Flash memory (up to 16MB)</li> <li>1 simplified UART</li> <li>15 multi-function pins</li> <li>1 interrupt input pin</li> <li>2 general purpose timers and 1 watchdog timer</li> <li>Selectable CPU clock rates: 125, 150, 175 MHz</li> <li>4K I-Cache, 4K D-Cache, 8K I-MEM, and 4K D-MEM</li> <li>Routing Engine</li> <li>Support IPoE, PPPoE, TCP/UDP, GRE/PPTP, UDP/L2TP auto-routing</li> <li>Hardware based layer 3/layer 4 NAT/NAPT routing to offload CPU computing power</li> <li>Support virtual server to maximize the network throughput</li> <li>4K entries for routing table</li> <li>Support Application Level Gateway (ALG) tables</li> </ul> |

#### **General Description**

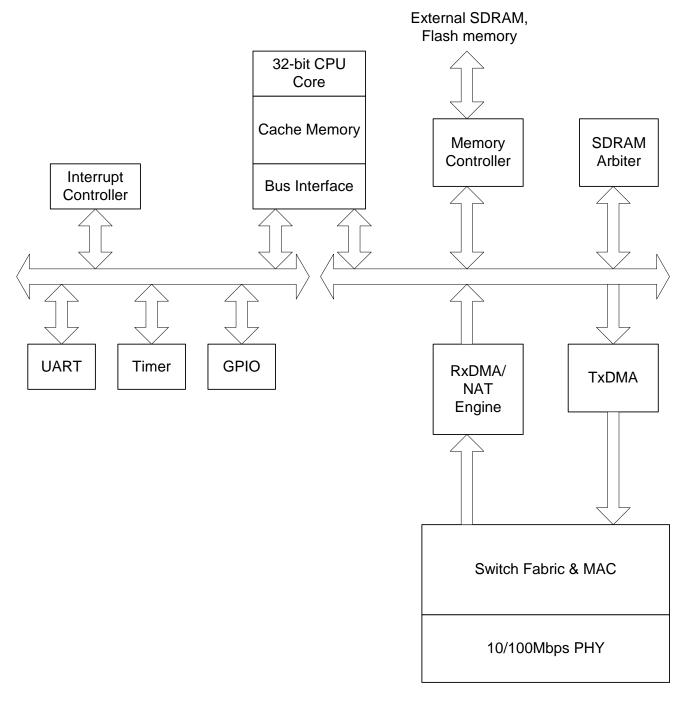

Integrating CPU, 5-port Ethernet switch and packet buffer, IP3210A provides the most cost-effect solution for IP sharing router. Among these Ethernet ports, four ports are used as LAN ports and one as WAN port. There are six MACs and the associated layer 3, 4 router and layer 2 switch engines in the SoC.

Supporting layer 2, layer 3 and layer 4 traffic classification, the switch engine can meet triple play applications. Hardware based IGMP snooping can support the real-time multimedia application without the intervention of CPU. The switch engine provides rich functions to meet the requirement of future applications.

The build-in hardware layer 3, 4 NAT/NAPT engine effectively supports the WAN-to-LAN and LAN-to-WAN auto-routing for IPoE, PPPoE, TCP/UDP, GRE/PPTP and UDP/L2TP packets. The hardware based NAT/NAPT routing engine accelerates the packet routing performance by inspecting the packet header and forwarding either to the CPU or to a destination port. The protocol ID, MAC address, IP address and port number of an incoming packet is checked and auto-routing is executed accordingly. For packets with recognized packet types, the NAT/NAPT engine routes the packet directly to the destination port. For unrecognized packets, the engine redirects the packet to CPU for further process before being sent to the destination port. This architecture greatly offloads the CPU computing power, featuring a high throughput NAT/NAPT router.

The embedded high performance 32-bit RISC core can be programmed to operate at selectable clock frequencies at 125, 150 or 175 MHz. The 7-stage pipelined architecture, together with build-in 4K I-Cache, 4K D-Cache, 8K I-MEM, and 4K D-MEM, increase the RISC instruction execution efficiency. With the aid of MMU, IP3210A can greatly reduce the memory management task for some OS. Two general-purpose timers and one watchdog timer are provided for programmer's convenience. Convenient firmware program debugging is also supported via the UART and JTAG interfaces.

External flash memory is used to store the firmware code for CPU and external SDRAM is used for both code execution and data storage. For greater flexibility of flash memory selection, both serial and parallel flash interface are supported and configurable through a pin strapping option. The industrial standard 16-pin interface is supported for the external SDRAM. The maximum capacity for flash memory and SDRAM are 16MB and 32MB, respectively. Effective DMA engines are designed to move incoming and outgoing packets directly between the MAC and SDRAM without the need of CPU involvement.

### **Revision History**

| Revision #     | Change Description |

|----------------|--------------------|

| IP3210A-DS-R00 | Initial release    |

#### Disclaimer

This document probably contains the inaccurate data or typographic error. In order to keep this document correct, IC Plus reserves the right to change or improve the content of this document.

### **Table of Contents**

| Disc | laimer  |           |                                     | 3    |

|------|---------|-----------|-------------------------------------|------|

|      |         |           |                                     |      |

|      |         |           |                                     |      |

| 2. P | in Diag | ram       |                                     | 7    |

| 3. P |         |           |                                     |      |

| 4.   | Funct   | tional De | scription                           | . 11 |

|      | 4.1     | Etherne   | et Switch Engine                    | . 11 |

|      | 4.      | 1.1       | Switch Register                     | . 11 |

|      | 4.      | 1.2       | Flow Control                        |      |

|      | 4.      | 1.3       | Quality of Service (QoS)            | . 11 |

|      | 4.      | 1.4       | Traffic Policy                      | . 11 |

|      | 4.      | 1.5       | Priority Classification             | . 11 |

|      | 4.      | 1.6       | Output Queue Scheduling             | .14  |

|      | 4.      | 1.7       | IGMP Snooping                       | .14  |

|      | 4.      | 1.8       | Security Filtering                  | .14  |

|      | 4.      | 1.9       | Physical Port Filtering             | .15  |

|      | 4.      | 1.10      | MAC Address Filtering               | .15  |

|      | 4.      | 1.11      | Logical Port Filtering              |      |

|      | 4.      | 1.12      | Layer 2-4 Multi-Field Filtering     |      |

|      | 4.      | 1.13      | Spanning Tree                       | .15  |

|      | 4.      | 1.14      | Special Tag                         | .16  |

|      | 4.2     | Router    | Engine                              | .18  |

|      | 4.      | 2.1       | HNAPT Architecture                  |      |

|      | 4.      | 2.2       | MAC Addresses and VLAN ID           |      |

|      | 4.      | 2.4       | MAC Addresses and VLAN ID           | .20  |

|      | 4.      | 2.5       | Statistical Counters                | .20  |

|      | 4.      | 2.6       | CPU and Peripheral Interface        | .20  |

|      | 4.      | 2.7       | CPU Core                            | .20  |

|      | 4.      | 2.8       | UART 21                             |      |

|      | 4.      | 2.9       | Timers                              | .21  |

|      | 4.      | 2.10      | Interrupt                           | .22  |

|      | 4.      | 2.11      | Memory Interface                    |      |

|      |         | 2.12      | Memory Map                          | .24  |

|      | 4.      | 2.13      | GPIO/LED/JTAG Control               | .24  |

| 5.   | Regis   |           | ription                             |      |

|      | 5.1     | Router    | and Peripheral                      |      |

|      |         | 1.1       | Flash Memory/SDRAM Control          | .25  |

|      |         | 1.2       | Timer 27                            |      |

|      | -       | 1.3       | UART 28                             |      |

|      |         | 1.4       | SMI control/Router Control Register |      |

|      |         | 1.5       | Interrupt controller                | .30  |

|      | 5.      | 1.6       | GPIO 31                             |      |

|      | 5.2     | MII Reg   | gisters of PHY0~4                   | .32  |

|      | 5.3     |           | Control/Status Register             |      |

| 6.   | Elect   |           | racteristics                        |      |

|      | 6.1     |           | e Maximum Rating                    |      |

|      | 6.2     |           | aracteristics                       |      |

|      | 6.3     |           | aracteristics                       |      |

|      | 6.4     |           | I Parameters                        |      |

| 7.   | Orde    | r Informa | tion                                | .79  |

4/80

*July 18 2012* Rev. 00

### 1. Block Diagram

Figure 1 IP3210A 5-port 10/100 NAT/NAPT router block diagram

IP3210A Data sheet

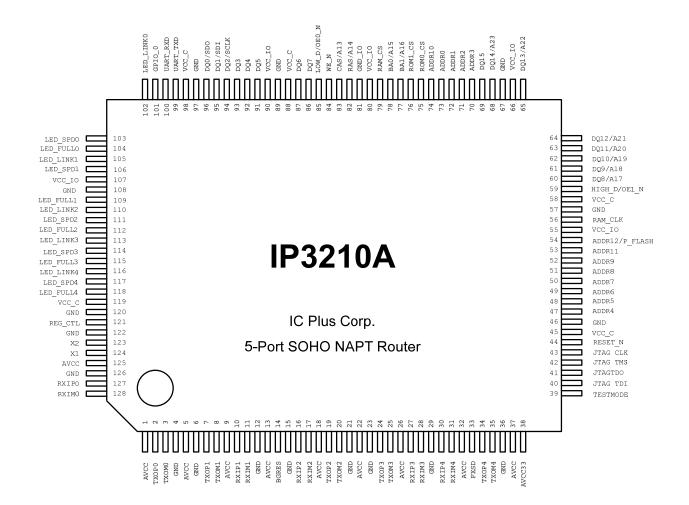

### 2. Pin Diagram

### 3. Pin Description

| Туре | Description                                |

|------|--------------------------------------------|

| I    | Input pin                                  |

| 0    | Output pin                                 |

| IPL  | Input pin with internal pull low 140K ohm  |

| IPH  | Input pin with internal pull high 222K ohm |

| Туре | Description |

|------|-------------|

| А    | Analog pin  |

| Р    | Power pin   |

| G    | Ground pin  |

| Pin No.                        | Label                              | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|--------------------------------|------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SDRAM Bus and Flash Memory Bus |                                    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 91~96, 87,<br>86               | DQ0~DQ7                            | I/Ō  | Shared data bus for Flash memory and SDRAM.<br>During SDRAM access cycle, these pins function as data bus,<br>DQ0~DQ7.<br>During flash memory access cycle, these pins function as data bus,<br>DQ0~DQ7.<br>If serial flash memory is selected, DQ0~DQ2 are used as the following<br>functions.<br>DQ[2] : Serial Flash Clock output<br>DQ[1] : Data output to Serial Flash memory. Connect this pin to DI of<br>the serial flash memory.<br>DQ[0] : Data input from Serial Flash memory. Connect this pin to DO<br>of the serial flash memory. |  |  |  |

| 69                             | DQ8/A17~DQ14/A<br>23,<br>DQ15/ A-1 | I/O  | During SDRAM access cycle, these pins function as data bus,<br>DQ15~DQ8.<br>During flash memory access cycle, these pins function as address<br>bus.<br>A-1 is the LSB of the parallel flash memory address bus.                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 47~53                          | ADDR4 ~ ADDR11                     | 0    | Address bus for SDRAM and parallel Flash memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 54                             | ADDR12//P_FLAS<br>H                | I/O  | IP3210A will latch the state of this pin upon reset.<br>"1": Parallel bus flash memory.<br>"0": Serial bus flash memory.<br>This pin is used as address A12 for SDRAM or flash memory.                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| 59                             | HIGH_D/OE1_N                       | 0    | DQ15~DQ8 enable for SDRAM during the SDRAM access cycle.<br>Byte output enable during Flash memory access cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 85                             | Low_D/OE0_N                        | 0    | DQ7~DQ0 enable for SDRAM during the SDRAM access cycle.<br>Byte output enable during Flash memory access cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 82                             | RAS/A14                            | 0    | RAS for SDRAM access cycle. A14 address for Flash memory cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

|                                |                                    | 0    | CAS for SDRAM access cycle. A13 address for Flash memory cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 56                             | RAM_CLK                            | 0    | Clock for SD RAM access cycle.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|                                | ROM0_CS,<br>ROM1_CS                | 0    | Chip selection for flash memory 0 and flash memory 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 78, 77                         | BA0/A15, BA1/A16                   | 0    | During SDRAM access cycle, it functions as the bank selection.<br>During flash memory access cycle, it functions as the memory address<br>bus.                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| 79                             | RAM_CS                             | 0    | Active low output. SDRAM chip selection.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| 84                             | WE_N                               | 0    | Active low output. Write enable for SDRAM or parallel flash memory.                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

#### Pin description (continued)

|                                                                                            | Label                                                                        | Туре | Description                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LED pin                                                                                    |                                                                              |      |                                                                                                                                                                                                                                                                                                                                                                                        |

| 102~104,<br>103~118                                                                        | LED0_LINK0~LED<br>_SPD1,<br>LED_FULL1~LED<br>_FULL4                          | 0    | Active low LED driving pins.<br>LINK/ACT: Active when the cable is linked up or TX , RX ongoing.<br>SPD: Active when the cable is linked at 100MBps speed.<br>FULL: Active when the cable is operating in full duplex mode.                                                                                                                                                            |

| MDI                                                                                        |                                                                              |      |                                                                                                                                                                                                                                                                                                                                                                                        |

| 25, 34, 35                                                                                 | TXOP1,TXOM1<br>TXOP2,TXOM2<br>TXOP3,TXOM3<br>TXOP4,TXOM4                     | I/O  | These pins are directly connected to the TX pair of the transformer.<br>TXOP0 and TXOM0 represent the positive polarity of port 0 and<br>negative polarity of port 0 respectively.<br>TXOP4 and TXOM4 are connected port 4.<br>TXOP4 and TXOM4 are also configured as the Fiber SerDes output,<br>please refer to the paragraph "DC Characteristics" for more detail<br>information.   |

| 10, 11, 16,<br>17, 27, 28,<br>30, 31                                                       | RXIP0, RXIM0<br>RXIP1, RXIM1<br>RXIP2, RXIM2<br>RXIP3, RXIM3<br>RXIP4, RXIM4 | I/O  | These pins are directly connected to the RX pair of the transformer.<br>RXOP0 and RXOM0 represent the positive polarity of port 0 and<br>negative polarity of port 0 respectively.<br>RXOP4 and RXOM4 are connected to port 4.<br>RXOP4 and RXOM4 are also configured as the Fiber SerDes input,<br>please refer to the paragraph "DC Characteristics" for more detail<br>information. |

| Power Sup                                                                                  | ply                                                                          |      |                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                            | AVCC                                                                         | Ρ    | Analog circuit power supply. These pins should be connected to 1.95V power source.                                                                                                                                                                                                                                                                                                     |

| 38                                                                                         | VCC33                                                                        | Р    | Analog 3.3V power source. This pin should be separated with the IO power source with a ferrite bead.                                                                                                                                                                                                                                                                                   |

| 88,119, 98                                                                                 | VCC_C                                                                        | Ρ    | Digital core power supply. These pins should be connected to 1.95V power source.                                                                                                                                                                                                                                                                                                       |

| 55, 66, 80,<br>90 ,107                                                                     |                                                                              | Ρ    | I/O signal power supply. These pins should be connected to 3.3V power source.                                                                                                                                                                                                                                                                                                          |

| 4, 6, 12,<br>15, 21, 23,<br>29, 36, 46,<br>57, 67, 89,<br>97, 120,<br>122, 126,<br>108, 81 | GND                                                                          | G    | These pins should be connected to ground plane.                                                                                                                                                                                                                                                                                                                                        |

### Pin description (continued)

| Pin No.   | Label                                                                      | Туре   | Description                                                                                                                                                           |

|-----------|----------------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Miscellar | eous Pins                                                                  |        |                                                                                                                                                                       |

| 14        | BGRES                                                                      | A      | This pin sets the band gap reference voltage for the internal circuit.<br>Should be connected to GND through a 6.19K ohm resistor.                                    |

| 39        | TEST MODE                                                                  | I, IPL | This pin sets the testing mode upon reset. Leave it unconnected<br>during the normal operation.<br>TEST_MODE = 0: Normal operation mode;<br>TEST_MODE = 1: Test mode; |

| 40 ~ 43   | JTAGTDI/GPIO16<br>JTAGTDO/GPIO1<br>3,JTAGTMS/GPIO<br>15,JTAGCLK/GPI<br>O14 |        | During test mode, these pins are used for JTAG test.<br>During normal operation mode, these pins are used as GPIO.                                                    |

| 44        | RESET_N                                                                    | I      | Low active reset input.                                                                                                                                               |

| 99        | UART_TX/GPIO17                                                             | 0      | UART TX signal or GPIO 17                                                                                                                                             |

| 100       | UART_RX/GPIO1<br>8                                                         | I      | UART RX Signal or GPIO 18                                                                                                                                             |

| 101       | GPIO0/INT                                                                  | I/O    | General purpose I/O signal or level sensitive Interrupt input                                                                                                         |

| 121       | REG_CTL                                                                    | A      | This pin controls the base of a PNP transistor. The collector of the PNP transistor is 1.95V which is supplied to the power source of VCC_C.                          |

| 124       | X1                                                                         | I      | Connected to the 25MHz clock or crystal input                                                                                                                         |

| 123       | X2                                                                         | 0      | Connected to the other side of 25MHz crystal.                                                                                                                         |

| 33        | FXSD                                                                       | I      | Tie this pin to GND when port 4 is connected to TP cable<br>Please refer to the paragraph "DC Characteristics" for more detail<br>information.                        |

#### 4. Functional Description

#### 4.1 Ethernet Switch Engine

#### 4.1.1 Switch Register

All the PHY and Switch registers are accessible in IP3210A through the "SMI for switch configuration" register (0x AF003000). To read/write these PHY/Switch registers, the firmware on IP3210A should write the PHY/Switch ID, register location and read/write command to the proper bit fields in SMI control register and trigger bit31 with an '1'. Table 4-1 shows the PHY/Switch register location defined for the Ethernet Switch Engine.

| PHY part         |        | Switch part      |         |  |

|------------------|--------|------------------|---------|--|

| PHY ID           | 00 ~04 | Switch ID        | 20 ~ 26 |  |

| Register Address | 0 ~ 06 | Register Address | 0 ~ 31  |  |

#### Table 4-1 PHY/Switch register location for Ethernet Switch Engine

#### 4.1.2 Flow Control

IP3210A supports two flow control mechanism configurable by firmware. For the fast path receiving, the firmware can program the hardware to turn on flow control function if the number of available RX packet buffers is less than a pre-specified threshold and to turn off flow control function if the number of available RX packet buffers is greater than a pre-specified threshold. The threshold values for tuning off/on low control are programmed through the FL\_OFF\_TH field and the FL\_ON\_TH field of FLOWCNTRL1 (0xAF003050) register. Alternatively, the firmware can manually turn on the flow control function by writing '1' to the FLM\_ON field of FLOWCNTRL2 (0xAF003054) register and turn off the flow control function by writing '1' to the FLM\_OFF field of FLOWCNTRL2 (0xAF003054) register. This manual control mechanism is enabled by setting '1' to the FL\_Manual field of FLOWCNTRL2 (0xAF003054) register.

#### 4.1.3 Quality of Service (QoS)

IP3210A utilizes a combination of traffic policy, priority classification and output queue scheduling to achieve policy-based QoS to meet the requirement of internet services, such as file transfer, email, video, voice and Web. Traffic policy can aggregate traffic flow and police against its traffic profile. This mechanism can effectively manipulate the traffics entering the switch. Finally, packets will be placed into appropriate output queue based on priority classification.

#### 4.1.4 Traffic Policy

IP3210A traffic policy is maintained by the combination of classifier, meter and dropper. The classifier separates received packets into different traffic streams based on the pre-defined condition. IP3210A provides 8 Multi-Field entries, where each entry is a combination of one or more layer 2-4 headers. Multi-Field classification can classify packets into traffic classes and traffic flows. For instance, an end-to-end flow is recognized by using five tuples. Each Multi-Field contains a meter for measuring the traffic. The meter passes the in-profile packets for forwarding and put out-of-profile packets into dropper for dropping. The designer can configure the parameters of traffic policy from MII register 26.0-23.

Each entry associated with Multi-Field counter is used to monitor the traffic rate. The counter value is represented in byte unit. The CPU can monitor the traffic rate to periodically read the value of multi-field counter through MII register.

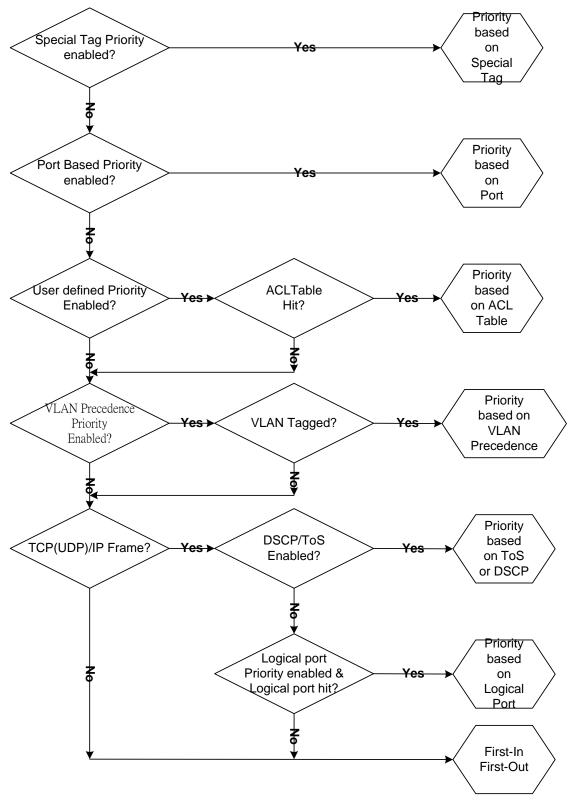

#### 4.1.5 Priority Classification

The priority classification is used to separate packets into four priority levels. In IP3210A, packet classification can categorize packets based on port-based classification and packet-based classification. Port-based classification, packets coming from the same port have a fixed priority level. Packet-based classification is based on one header filed or a combination of more header fields. Packet-based classification has a flexible packet classification to

Copyright © 2012, IC Plus Corp.

*July 18 2012* Rev. 00

### www.BDTIC.com/ICplus

classify priority level designated by the following header fields:

- Special tag

- Source MAC address

- Destination MAC address

- VID

- VLAN priority

- IPv4 ToS/IPv6 DSCP

- TCP/UDP logical port

- Layer 2-4 Multi-Field

Figure 2 illustrates the priority classification flow chart.

Figure 2 IP3210A Traffic Classification Rule

Copyright© 2012, IC Plus Corp. WWW.BDTIC.com/ICplus *July 18 2012* Rev. 00

#### 4.1.6 Output Queue Scheduling

IP3210A supports four scheduling modes at Table 4-2.

| Mode # | Q3  | Q2  | Q1  | Q0      |

|--------|-----|-----|-----|---------|

| Mode 0 | WRR | WRR | WRR | WRR     |

| Mode 1 | WFQ | WFQ | WFQ | WFQ(BE) |

| Mode 2 | SP  | WFQ | WFQ | BE      |

| Mode 3 | SP  | SP  | SP  | SP      |

#### Table 4-2 Four Scheduling Modes

SP: Strictly Priority; WRR: Weight Round Robin; WFQ: Weight Fair Queuing; BE: Best Effort

#### SP:

In strict priority mode, the packets stored in the highest priority queue will be sent until it is empty. The second highest priority queue is then activated with all its packets being sent. This procedure repeats with packets in queues with descending order until packets in the lowest priority queue are sent.

#### WRR:

The designer can control the number of packets transmitted on an output queue by setting its weight. **WFQ:**

The designer can allocate a bandwidth on an output queue by setting its rate. Configuring WFQ bandwidth can be through the internal register.

#### 4.1.7 IGMP Snooping

IP3210A supports IGMP v1 and v2 snooping specified in RFC 1112 and RFC 2236 respectively. Because IGMP is used between hosts and neighboring multicast routers, IP3210A listens to the IGMP message communication between router and host to establish multicast group membership. Based on the group membership information, IP3210A forwards IP multicast data to its members which are registered in the group table. This mechanism is referred to as the "hardware based IGMP snooping". The timeout mechanism is necessary, so that the host can silently leave a specific multicast group. "Silently Leave" means that a host does not respond to the query message when it intends to leave a multicast group. In addition to the hardware based IGMP snooping, IP3210A also supports pure firmware based IGMP snooping and IGMP snooping with CPU assistance mode. The firmware based IGMP snooping implies that the firmware must handle IP multicast traffic which includes multicast data packets and IP multicast table and then the multicast data packet is forwarded to the destination ports according to this table. In IGMP snooping with CPU assistance mode, the IP data packet is forwarded by the internal switch engine and the multicast membership table is maintained by CPU. In hardware based IGMP snooping, all multicast packets are handled by the hardware without the intervention of CPU once the IGMP function is enabled.

IP3210A supports not only IGMP snooping but also MLD snooping. The difference between these two mechanisms is that there is no option for hardware based MLD snooping. It only supports firmware MLD snooping mode and MLD snooping with CPU assistance. For MLD snooping with CPU assistance, IP3210A traps MLD control packets to CPU for further building multicast table and the multicast data packet is forwarded based on this table. For firmware MLD snooping, IP3210A traps all IPv6 multicast packet to CPU and CPU should process these packets and forward to the proper ports.

#### 4.1.8 Security Filtering

IP3210A provides flexible security configuration to protect against attacks and filter suspicious traffics. These packets can be dropped or forwarded to CPU for further process. IP3210A provides packet filtering based on physical port, MAC address, logical port and layer 2-4 Multi-Field packet headers.

Copyright© 2012, IC Plus Corp. WWW.BDTIC.com/ICplus

14/80

*July 18 2012* Rev. 00

#### 4.1.9 Physical Port Filtering

The forwarding and learning ability of a port can be disabled respectively. The security rule is that any user shall be authenticated by an authenticating server or the administrator when accessing to the network. Administrator (or CPU) can disable forwarding and learning ability on a given port, if a host is in the unauthorized state.

#### 4.1.10 MAC Address Filtering

The feature of MAC address filtering can be configured in two modes: The negative list mode and positive list mode. The negative list mode allows IP3210A to drop packets based on the list of either specific source MAC address or specific destination MAC address. The negative list mode can also drop packet on per VLAN group base. Configuring contexts of the negative list MAC address is through "Address Table Access Register". The positive list mode only accepts those packets registered in SMAC (source MAC address) table.

#### 4.1.11 Logical Port Filtering

IP3210A can discard packets based on the layer 4 logical port. The logical port can define a particular port number or a range of port numbers. If the source's logical port or the destination's logical port in the incoming packet matches any of the pre-defined logical ports, the incoming packet will be discarded.

#### 4.1.12 Layer 2-4 Multi-Field Filtering

In addition to supporting simple layer 2 to layer 4 filtering rule, IP3210A can also filter packets based on a combination of layer 2-4 Multi-Field packet headers.

#### 4.1.13 Spanning Tree

The spanning tree protocol can be implemented through the cooperation of both firmware and hardware. In software implementation, CPU must process BPDU packet and configure each port. In hardware implementation, the switch traps BPDU to CPU and either forwards or drops packet according to the register settings. The Table 4-2 describes how to configure the state of each port in IP3210A.

| State      |            | Fwd BPDU packet<br>to each port |   | Fwd all packets<br>normally | Forwarding,<br>Learning <sup>1</sup> |

|------------|------------|---------------------------------|---|-----------------------------|--------------------------------------|

| Disable    | X (note 2) | X (note 2)                      | Х | Х                           | Х, Х                                 |

| Blocking   | 0          | X (note 3)                      | Х | Х                           | Х, Х                                 |

| Listening  | 0          | 0                               | Х | Х                           | Х, Х                                 |

| Learning   | 0          | 0                               | 0 | Х                           | Х, О                                 |

| Forwarding | 0          | 0                               | 0 | 0                           | O, O                                 |

#### Table 4-2 BPDU packet state

Note1: O: enabled, X: disabled

**Note2:** CPU should not send packets to the switch and should discard packets coming from the switch. **Note3:** CPU should not send packets to the switch.

IP3210A supports fast aging function for RSTP by programming registers 20.14[6:5] and 20.14[4:0]. The designer can configure the parameters from MII register.

#### 4.1.14 Special Tag

The purposes of special tag are:

- To allow a packet coming from the switch to carry the ingress port number and violation event before it is sent to the CPU.

- To allow a packet sent from CPU to indicate the egress port and output queue number in special tag header.

The special tag is inserted right behind the Source MAC Address. Unlike the type ID of 802.1Q represented by 8100 in hexadecimal, the special tag is represented by 81xx in hexadecimal, where "xx" means a number other than "00".

| SourceDestinatMACMACAddressAddress | 81xx | Tag<br>Information | Payload | CRC |

|------------------------------------|------|--------------------|---------|-----|

|------------------------------------|------|--------------------|---------|-----|

#### **Special tag format**

There are two formats of special tag, depending on the frame direction. The special tag format is defined as follows:

#### Special Tag added to the received packet (From switch side to CPU side)

The special tag information consists of ingress port number and violation event. Ingress port number indicates where the packet comes from. The violation event is an event vector consisting of security violation, VLAN violation and miss address table.

Security violation: IP3210A supports unknown SMAC filtering and the designer can enable it by register setting. Unknown SMAC means source MAC address of the received packet that is not found in the pre-defined address table. When this function is enabled, the received frames with unknown SMAC are marked as "illegal SMAC" and will not be forwarded to the destination. Instead, this packet is forwarded to the CPU so that the CPU can take the following action:

(a) VLAN violation: If a VLAN ID is found, this bit is set.

(b) Miss address table: If the searching result of the address table misses, this bit is set.

| Special Tag Information | Description                                   |

|-------------------------|-----------------------------------------------|

| Bit 7-3                 | Packet Information                            |

|                         | - bit 4: Reserved                             |

|                         | - bit 3: Reserved                             |

|                         | <ul> <li>bit 2: Miss address table</li> </ul> |

|                         | <ul> <li>bit 1: Security violation</li> </ul> |

|                         | - bit 0: VLAN violation                       |

| Bit 2-0                 | Ingress Port number                           |

|                         | - 3'b000: Disabled                            |

|                         | - 3'b001: Port 0                              |

|                         | - 3'b010: Port 1                              |

|                         | - 3'b011: Port 2                              |

|                         | - 3'b100: Port 3                              |

|                         | - 3'b101: Port 4                              |

|                         | - Other: Reserved                             |

#### Special Tag added to Transmitted Packet (From CPU side to switch side)

This function provides for forwarding decision, priority assignment and disabling physical port. The parameters embedded in the special tag header can be set by CPU.

| Special Tagged Information | Description                     |

|----------------------------|---------------------------------|

| Bit 7                      | 0: Enable MAC address learning  |

|                            | 1: Disable MAC address learning |

| Bit 6-5                    | Priority Assignment             |

|                            | - 2'b00: Disabled               |

|                            | - 2'b01: Queue 1                |

|                            | - 2'b10: Queue 2                |

|                            | - 2'b11: Queue 3                |

| Bit 4-0                    | Output Port Mask.               |

|                            | 1: Forward to this port.        |

|                            | 0: Do not forward to this port. |

|                            | - bit 4: port 4                 |

|                            | - bit 3: port 3                 |

|                            | - bit 2: port 2                 |

|                            | - bit 1: port 1                 |

|                            | - bit 0: port 0                 |

#### 4.2 Router Engine

#### 4.2.1 HNAPT Architecture

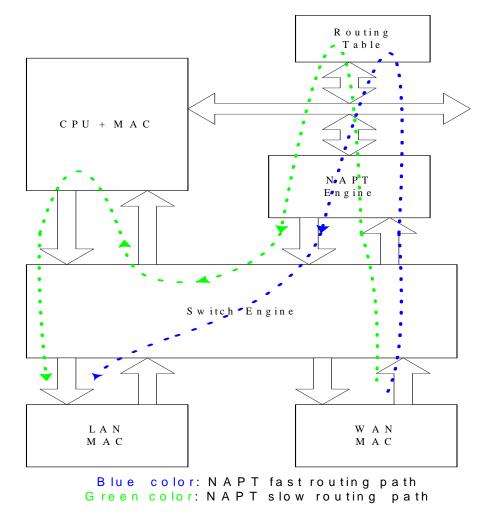

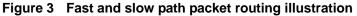

Figure 3 illustrates the fast and slow packet routing paths for a packet incoming from the WLAN port and outgoing to a LAN port. For the fast path, the switch engine forwards the packet to the NATP engine for Layer 3, 4 header parsing. The HNATP engine recognizes the packet and replaces the proper fields in Layer 3, 4 by routing table look-up. The resulting packet is then sent to the destination LAN port directly. For the slow path, the HNATP engine does not recognize the packet or the routing table does not contain proper substitution information. The packet is forwarded to the CPU for further process. The firmware running at CPU checks the incoming packet and performs proper routing substitution on the packet before directing it to the destination LAN port. The firmware may also extract proper fields from the packet to construct routing table entry so that the subsequent packets from the same source will become recognizable by the HNAPT engine and be forwarded to the destination LAN port directly through fast path. Similar routing procedures are performed for packets incoming from a LAN port and outgoing to the WLAN port. By default, the packet types that are currently supported by HNAPT engine include IPoE, PPPoE, TCP/UDP, GRE/PPTP, and UDP/L2TP. The firmware can disable the support of any of these protocols by programming the corresponding bit field in PROTOCOL Register (0xAF003080)

For some special applications, it may be desirable to process all incoming packets by firmware even when the

Copyright© 2012, IC Plus Corp. WWW.BDTIC.com/ICplus July 18 2012 Rev. 00

HNAPT engine can recognize the packets. There are two special modes built in IP3210A that can be used to disable the HNAPT function completely or to direct the HNAPT processed packets to CPU instead of the destination port. The HNAPT function can be disabled by setting Nat\_en field of ROUTERCNTRL (0xAF003004) register to 0, and all packets processed by HHNAPT can be directed to CPU by setting the AllToCpu field of ROUTERCNTRL to 1.

The firmware support for HNAPT is provided by a set of API modules to facilitate the programming effort when the HNAPT function is turned on. Detailed descriptions of these API modules and the programming of the HNAPT function is given in Application Notes for HNAPT firmware programming guide.

#### 4.2.2 MAC Addresses and VLAN ID

IP3210A supports two 48-bit router source MAC addresses programmable through SA0ADDRL/ SA0ADDRH (0xAF00303C, 0xAF003040) and SA1ADDRL/ SA1ADDRH (0xAF003044, 0xAF003048) registers, respectively. Up to eight VLAN IDs can also be programmed through VLANID01, VLANID23, VLANID45, VLANID67 registers (0xAF00301C, 0xAF003020, 0xAF003024, and 0xAF003028). Each VLAN ID is 4-byte and is automatically inserted to packets between a selected pair of WAN and LAN ports with either inbound (WAN-to-LAN) or outbound (LAN-to-WAN) direction as indicated by one bit field (InBoundx) in the corresponding VLAN ID register.

#### 4.2.3 RX/TX Queue Buffer Management

The RX and TX buffer management is accomplished by link lists established by the firmware. Buffer descriptor scheme with distinguished ownership bit for firmware and HNAPT/DMA engine is used to ensure non-conflicting access by them. For a RX or TX queue, the associated buffer descriptors are tabulated in consecutive memory locations. Registers RXSWDSCBASEADDR (0xA3003008), TXSWDSCBASEADDR (0xA3003064) and HWDSCBASEADDR (0xA300300C) are used to identify the base addresses of the tabulated descriptors for the slow path RX queue, slow path TX queue and fast path RX queue, respectively. Note that since RX packets in the fast path are directly forwarded to the destination port, there is no need to define TX queue for the fast path. At initialization, the firmware on IP3210A allocates proper memory segments for these descriptor tables and fills the three base address registers with the corresponding memory addresses.

The packet buffers for the various RX and TX queues are also allocated and linked by the firmware. At initialization, the firmware allocates a fixed number of available packet buffers and link them into a buffer queue with the first buffer address specified in FIRSTBUFBASEADDR (0xA3003010) and the last buffer address in LASTBUFBASEADDR (0xA3003004) registers, respectively. This buffer queue is frequently updated during the normal packet receiving and transmitting operations. When a buffer is needed by RXDMA engine for storing an incoming packet, the first buffer in the queue is easily fetched as its address is readily given by FIRSTBUFBASEADDR register and, after the fetching, the RXDMA engine automatically maintains the integrity of the buffer queue by overwriting the FIRSTBUFBASEADDR register with the address of the second buffer in the queue. On the other hand, when a new buffer is allocated for the buffer queue by the firmware or when an existing buffer of a transmitted packet is ready for releasing back to the buffer queue by the TXMDA engine, this unused buffer is inserted into the queue by linking its address to the last buffer in the queue and overwriting the LASTBUFBASEADDR register with its address.

The total number of buffers allocated for the fast path RX queue is programmed by the firmware in the TotalBuffer field of FLOWCNTRL1 (0xA3003050) register. Since the packet buffers in both slow and fast path RX queues are fetched from the same buffer queue, the TotalBuffer field of FLOWCNTRL1 (0xA3003050) register must be specified with a value less than the number of buffers allocated for the buffer queue at initialization.

For power saving, the hardware ceases checking the ownership bit of the TX descriptors once the slow path TX queue becomes empty. As a result, the firmware has to program the TxSW\_Trig field of SWPKTTRIG (0xA30030C0) register to 1 to trigger the hardware to start the transmission loop again if it en-queues new transmit packets into the TX queue under empty status. It is also possible to encounter the condition that all RX descriptors

Copyright© 2012, IC Plus Corp. WWW.BDTIC.com/ICplus

19/80

for the slow path RX queue are occupied. The hardware ceases the checking on available RX descriptors to save power and the firmware has to trigger the hardware to start RX descriptor fetching for RX queue by writing the HasSWDsc field of RXDMACNTRL (0xA300304C) register to 1 when it allocates new RX descriptors for the RX queue.

To assist firmware in processing RX packets efficiently, the RX packets with recognized protocols can be placed in packet buffers such that the starting point of the L3 portion of a RX packet occurs at a fixed offset from the beginning of the packet buffer. This fixed offset is programmable by the firmware through the IPFixPos field of RXDMACFG (0xA3003014) register with a value no greater than 100. The firmware shall not set this offset value smaller than the total expected L2 length to avoid insufficient space to store the L2 portion of the packet in the buffer.

#### 4.2.4 MAC Addresses and VLAN ID

IP3210A supports two 48-bit router source MAC addresses programmable through SA0ADDRL/SA0ADDRH (0xA300303C, 0xA3003040) and SA1ADDRL/SA1ADDRH (0xA3003044, 0xA3003048) registers, respectively. Up to eight VLAN IDs can also be programmed through VLANID01, VLANID23, VLANID45 and VLANID67 registers (0xA300301C, 0xA3003020, 0xA3003024, 0xA3003028). Each VLAN ID is 4-byte in length and is automatically inserted to packets between a selected pair of WAN and LAN ports with either inbound (WAN-to-LAN) or outbound (LAN-to-WAN) direction as indicated by one bit field (InBoundx) in the corresponding VLAN ID register.

#### 4.2.5 Statistical Counters

The SWITCHRXCOUNTER (0xAF003210) register counts the number of packets received by the HNAPT engine from the switch engine. The RXPKTCOUNTER (0xAF003200) register consists of two counters, one for the total number of packets being received by HNAPT engine and the other for the number of packets forwarded to CPU. The TXPKTCOUNTER (0xAF003204) register also consists of two counters, one for the number of packets transmitted from the slow path TX queue and the other for the number of packets directly sent from the RX queue of the HNAPT engine. Each of these statistical counter is 16-bit and the counter wraps around to zero when overflow.

#### 4.2.6 CPU and Peripheral Interface

IP3210A incorporates a 32-bit RISC CPU with DMA control and supports peripherals including UART, timers, interrupts, JTAG, serial/parallel flash memory and SDRAM. Register control is provided to configure the CPU speed and the features of these supported peripherals. The description of the CPU and the peripheral interfaces are given in the following.

#### 4.2.7 CPU Core

The CPU core is a high-performance RISC with 7-stage pipeline architecture and 4 internal cache memory types (I-Cache, D-Cache, I-RAM, D-RAM). The CPU supports native big endian mode. To enhance the CPU performance, the CPU contains a Branch Target Buffer to reduce the instruction branch penalty. Incorporating write-back or write through cache controller, the CPU can drive the execution efficiency to an extreme state. A compromise between the power consumption and the system performance can be achieved by setting the CPU clock. IP3210A provides various speeds at 125, 150 and 175 MHz for system optimization and can be easily programmed by selecting the desired setting for the CPU SPEED register (0xAF005018). For high speed arithmetic computation, a multiply-and-accumulator unit that can achieve a 1-cycle 16x16 or 2-cycle 32x32 multiply and accumulate operation is built in with the CPU core. The CPU also has a memory management unit (MMU), providing a 4-Kbyte-page size and 16-entry joint translation look-aside buffer (TLB). Convenient firmware debugging is supported through the JTAG and UART interfaces.

#### 4.2.8 UART

The UART has an external interface through two pin-outs, UART\_TXD and UART\_RXD, for transmit serial bit out and receive serial bit in, respectively. When the UART function is not turned on, both of these two pins can be used as GPIO pins where the UART\_TXD pin is designated as GPIO[17] and UART\_RXD as GPIO[18].

The UART can be configured to support various baud rates, ranging from 2400bps to 119200bps by setting bit31-16 of the UART control/status (UCS) register (0xAF002004). An interrupt to CPU can be generated after a number of bytes being received at the UART interface by programming RxThreshold and RIE fields in the UCS register. On the other hand, when TIE bit is set to 1, an interrupt to CPU is generated whenever all available TX bytes in the hardware are transmitted out of the UART interface. The no-parity, even-parity and odd-parity data format is selectable by the Parity\_en and Even\_Odd fields in the UCS register. The 1 or 2 stop-bit mode can also be set by the Stop\_bit field. The current RX byte parity is indicated in the Parity field. RX data error conditions are reported in the UCS register through the Parity\_err and Framing\_err fields. TX buffer empty and TX data ongoing are read-only status from the UCS register. An Internal loopback test mode for the UART transceiver is also supported by setting the loopback field of the UCS register.

With the UCS register properly set, the UART TX operations can be performed by writing bytewise data to bit31-24 of the UART buffer (UBF) register (0xAF002000) and the RX operations by reading bytewise data from bit31-24 of the UBF register. Note that a write to bit31-24 of UBF for TX byte operation will not corrupt any RX bytes that are ready for read since the read and write data ports are physically separated although they are only logically defined at the same bit fields of UBF. On-chip 16-byte RX and TX buffers are employed to ensure the read/write performance of the UART transceiver. The buffering operation is handled by hardware and is transparent to the control register interface. For each transmit burst, the TX buffer can be filled up to 16 bytes. To prevent TX overrun condition from occurring, the next transmit burst can only start after the TX empty status bit (bit2) of UCS is set to 1 for the current transmit burst. For receiving data bytes, the RX\_STATUS bit (bit23) of UBF is set to 1 by hardware whenever there is an available RX byte ready for read back by firmware. The RX\_STATUS bit is automatically cleared by the hardware if no more RX byte is available. The RX overrun condition will occur if the available RX byte is not read while more than 16 bytes of data have been received. This error condition is not reported in the register and may result in unknown RX data corruption behavior. Since the maximum baud rate of the UART is relatively slow, this RX overrun condition can be easily avoided by a well-designed firmware code.

#### 4.2.9 Timers

There are two general-purpose timers (Timer1 and Timer2) and one watchdog timer (WDTimer) in IP3210A. The general-purpose timers are programmable and used to facilitate the need of time unit used for programming purposes. The watchdog timer is used to detected conditions that may result in CPU unexpectedly hanged in an unknown state. During normal operation, the watchdog timer is periodically set by the firmware running on CPU to keep it from expiring. When a catastrophic system breakdown happens that causes a CPU halt, the firmware code that updates the watchdog timer no longer functions correctly and consequently the watchdog timer does not get updated which eventually leads to timer expires that triggers a watchdog timer interrupt. This interrupt is hardwired to trigger a CPU reboot process to rescue the breakdown.

Each of the three timers is configurable through a set of 5 registers. The three sets of registers for Timer1, Timer2 and WDTimer are (TIM1L, TIM1H, Prescaler1, Timer1C, TIS1), (TIM2L, TIM2H, Prescaler2, Timer2C, TIS2) and (TIMWDL, TIMWDH, PrescalerWD, TimerWDC, TISWD), respectively. The time scale of the three timers is controlled by their respective set of TIMnL, TIMnH and Prescalern (n = 1, 2 or WD) registers and the time unit is given by the formula below:

Timern = SDRAM\_CLK rate \* Prescalern value \* [TIMnH-TIMnL+1] value

Where SDRAM\_CLK rate is the operating frequency of the SDRAM (can be selected as 125 or 150 MHz), Prescalen value is specified by 24-bit in Prescalen register and [TIMnH-TIMnL+1] is the difference between TIMnH and TIMnL registers when the timer starts.

Timern gets started by setting TimernGo bit in TimernC register to 1. To control the proper response when timer expires, IME\_Timerx bit is set to 1 to generate timer interrupt and TxAIM is set to 1 if automatic restart of the timer is desired or set to 0 if the halt of the timer is desired. The timer interrupt status is indicated by intr\_timern in TISn register and is clear when it is written by a '1'. In contract to Timer1 and Timer2, TimerWD has one additional control bit, WDMode, in TISWD register. When this WDMode is programmed to 0, the watchdog timer acts as a regular timer in that it does not trigger a CPU/System reset when the timer expires. When WDMode is set to 1, the watchdog function is turned on to trigger a CPU/System reset when the timer expires.

#### 4.2.10 Interrupt

The interrupt controller supports a number of hardware interrupt sources that are configurable through the setting of STMSK (0xAF004000), CPOL (0xAF004004), IntS1 (0xAF004008) and IntS2 (0xAF00400C) registers. The selection of interrupt sources is programmable by setting IntS1 and IntS2 with a total of up to 14 sources where Source 15 to Source 8 are specified by IntS1 and Source 7 to Source 2 by bit31-8 in IntS2. Each source field in IntS1 and IntS2 should be filled with a 4-bit number that identifies the corresponding selected source. For the router/switch application in IP3210A, 7 hardware interrupt sources are provided with each of them associated with a source number as shown in Table 4-3.

| Hardware Interrupt Source | Interrupt Source Number |

|---------------------------|-------------------------|

| Timer 1                   | 15                      |

| Timer 2                   | 14                      |

| Router (NAPT Engine)      | 13                      |

| UART                      | 9                       |

| Timer (WatchDog)          | 8                       |

| GPIO0                     | 7                       |

| Switch Engine             | 6                       |

#### Table 4-3 Hardware interrupts source number assignment

The 7 interrupts consist of three timers, one UART, one GPIO, one router and one switch hardware interrupt sources, which can be programmed to generate interrupt events to CPU. The three timer interrupts are Timer1, Timer2 and WatchDog Timer; the UART interrupt is the UART TX/RX interrupt; the GPIO0 interrupt is the external interrupt driven by GPIO pin0; the router interrupt is the interrupt generated by NATP engine and the switch interrupt is the interrupt generated by the switch engine.

Each of these interrupts can be enabled by writing an "1" to the corresponding bit of Interrupt Mask fields in the STMSK register (0xAF00400). The interrupt event of each source is maintained in the interrupt status field of the CPOL register (0xAF004004). The polarity field of the CPOL register can also be set to indicate whether the corresponding source is a high-level sensitive or low-level sensitive interrupt. An additional "CAUSE" field in STMSK register is used to reflect the interrupt source instantaneous status that can be checked at any desirable time by polling the corresponding "CAUSE" field for this interrupt source. This can be useful when it is desired to clear the interrupt source status by firmware.

Once the interrupt sources are properly programmed in IntS1/IntS2 registers and the respective fields in STMSK and CPOL registers, the occurrence of an interrupt event will trigger the CPU to enter the interrupt service routine (ISR). The firmware is responsible to clear the corresponding interrupt status after the interrupt event is served. The priority of the interrupt source goes from high to low for source15 to source2 in IntS1 and IntS2. For interrupt source15 to source8, direct interrupt vector access functionality is

Copyright© 2012, IC Plus Corp.

22/80

*July 18 2012* Rev. 00

www.BDTIC.com/ICplus

supported for the respective ISRs. When the direct interrupt vector access is utilized, the firmware is responsible to program the locations of these ISRs into a set of interrupt vectors on the CPU. More detailed ISR programming methodology and examples for IP3210A can be referred to Document???

#### 4.2.11 Memory Interface

IP3210A supports one SDRAM controller and up to two generic static memory controllers. The required functional pins for these three memory interfaces are shared and managed by hardware in order to keep low pin count for IP3210A while minimizing the impact to firmware complexity.

With address lines A[0]-A[12], CAS\_N, RAS\_N, BA[0]-BA[1], the SDRAM controller can support an external SDRAM up to 32M bytes of range with memory mapping from 0x0000000 to 0x01FFFFFFF. The external data bus for SDRAM is 16-bit wide given by DQ[0]-DQ[15]. The SDRAM\_CLK is the clock output to SDRAM, which is 125 MHz when the CPU speed is 125 or 175 MHz and is 150 MHz when the CPU speed is 150 MHz. The chip select pin, SDRAM\_CS\_N, for SDRAM is used to assert the SDRAM device when the SRAM memory region is accessed. The write-enable pin is WE\_N and the low- and high-byte read-enable pins are LDQ\_L and LDQ\_H, respectively. For greater flexibility in SDRAM support, the controller is parameterized by SDRCR register. The setting of this register is SDRAM devices dependent and the best matching value for a particular device should be selected according to the guidelines provided in Applications Notes for IP3210A Memory Controller Setting. The

The two static internal memory controllers share the same address lines A[-1], A[13]-A[16] (shared pins with CAS\_N, RAS\_N, BA[0]-BA[1]), A[17]-A[23] (shared pins with DQ[8]-DQ[15]). Controller 1 supports up to 4M bytes of range with memory mapping from 0x1FFC0000 to 0x1FFFFFFF and controller 2 supports 12M bytes of range with memory mapping from 0x1F000000 to 0x1FFBFFFF, respectively. The chip selects pins ROM\_CS\_1\_N and ROM\_CS\_2\_N are used to assert external memory 1 and 2, respectively. And for the corresponding memory region 0x1FFC0000 to 0x1FFFFFF is accessed.

The two generic static memory controllers can be individually programmed to operate in either parallel or serial mode depending upon the configuration in SROMEN register. Since generic static memory controller 1 is designed to support external flash device for firmware code storage, the parallel or serial mode is decided for this controller during the system boot-up process. In particular, the controller enters parallel mode if A[12] is pulled high when power-on reset is asserted; otherwise, it enters serial mode. The resulting mode is reported as 1 for parallel and 0 for serial in pfboot field (bit0) of SROMEN. On the other hand, the parallel or serial mode for generic static memory is programmed by firmware via the pflash field (bit1) of SROMEN with a value '1' for parallel and '0' for serial.

In parallel mode, the external memory access is achieved by execute any normal RISC supported memory read/write instructions to the corresponding external memory map region without the need of special commands. The parameters of the control registers, ROM1CR and ROM2CR, can be set according to the timing characteristics of the external memories connected to controller 1 and controller 2, respectively. The detailed description of the selection of these parameters can be found in Applications Notes for IP3210A Memory Controller Setting.

In serial mode, external memory access for controller 1 is achieved through the issue of command on SROM1CR with the read/write address location specified in SROM1Addr and the read/write data available in SROM1Data. Similarly, external memory access for controller 2 is achieved through SROM2CR, SROM2Addr and SROM2Data. Applications Notes for IP3210A Serial Flash Controller provides the detailed description of the serial mode operation.

#### 4.2.12 Memory Map

The physical address for the control/status register, flash memory and the SDRAM is listed in Table 4-4.

| Physical Address Range            | Devices                           |

|-----------------------------------|-----------------------------------|

| 0x0000-0000 - 0x01FF-FFFF (32 MB) | External SDRAM                    |

| 0x0000-0000 - 0x0000-2FFF (8 KB)  | Embedded CPU SRAM (I memory)      |

| 0x0020-0000 - 0x0020-0FFF (4 KB)  | Embedded CPU SRAM (D memory)      |

| 0x0200-0000 - 0x02FF-FFFF         | Reserved                          |

| 0x0300-0000 - 0x03FFF-FFFF        | System Control Registers          |

| 0x0F00-0000 - 0x0FFFF-FFFF        | Reserved                          |

| 0x0400-0000 - 0x0BFF-FFFF         | Reserved                          |

| 0x0C00-0000 - 0x0EFF-FFFF         | Reserved                          |

| 0x0F00-0000 - 0x1CFF-FFFF         | Reserved                          |

| 0x1F00-0000 - 0x1FFF-FFFF (16MB)  | ROM/Flash (Static Memory 1 and 2) |

#### Table 4-4 Reigsters and memory physical address mapping

#### 4.2.13 GPIO/LED/JTAG Control

The only dedicated GPIO pin is GPIO[0]. This can serve as an external interrupt source if desirable. Other GPIO pins, GPIO[1]-GPIO[19], are shared pins with other functional pins such as the LED control, the UART, the JTAG pins. The GPIOSEL register (0xAF005010) is used to assign each of the GPIO pin as in GPIO function mode or the normal function mode. In addition, each GPIO pin can be configured as either an input or output pin by the GPIOD register (0xAF00500C). To provide more flexibility for coding convenient, the output of the GPIO pins can be controlled by firmware via two mechanisms. For the first mechanism, the firmware can write '1' and '0' to the corresponding field in GPIO register (0xAF005000) to pull a particular GPIO high and low, respectively. Alternatively, a particular GPIO pin can be pulled high by writing an '1' to the corresponding bit field in GPIOS register (0xAF005004) and can be pulled low by writing an '1' to the corresponding bit field in GPIOC register (0xAF005008).

A total of 15 LED control pins divided into 5 equivalent sets in which each set has 3 pins, LED\_Link, LED\_SPEED, LED\_FULL. All LED functions are controlled by hardware and no firmware configuration is needed.

Four-wired standard JTAG interface is supported. No firmware configuration of the JTAG interface is needed.

#### 5. Register Description

The symbols used in the following tables are listed below.

R/W: Read/Write attributes.

SC: Self-cleared after read.

PHY: PHY ID which should be included in a frame of Serial Management Interface.

MII: MII register address which should be included in a frame of Serial Management Interface.

#### 5.1 Router and Peripheral

Note: The address of the router and peripheral shown in the following table is the virtual address. In the following tables, the register address is byte oriented and the lower address maps to the least significant byte.

| Register<br>Address | Bit<br>Location | R/W | Function                                                         | Default Value        |

|---------------------|-----------------|-----|------------------------------------------------------------------|----------------------|

| AF000004            |                 | R/W | Polarity of ready signal,                                        | 32'hFFFFFFF          |

|                     |                 |     | 0: rdy_busy_n =1 means "ready";                                  | -Suggested<br>value: |

|                     |                 |     | 1: rdy_busy_n =0 means "ready"                                   | 32'hf008010a         |

|                     | 30              | R/W | Mask off busy signal.                                            |                      |

|                     |                 |     | 1: ignore ready/busy signal. 0: Do not ignore ready signal.      |                      |

|                     | 29:25           | R/W | OEW: Output enables width.                                       |                      |

|                     |                 |     | Actual time period=(OEW + 1) * SDRAM clock cycle time            |                      |

|                     | 24:23           | R/W | OEH: Out enable High Hold time.                                  |                      |

|                     |                 |     | Actual time period= OEH * SDRAM clock cycle time                 |                      |

|                     | 22:20           | R/W | AVOEL: Address valid to OE Low.                                  |                      |

|                     |                 |     | Actual time period= (AVOEL+1) * SDRAM clock cycle time           |                      |

|                     | 19:15           | R/W | WEW: WE width                                                    |                      |

|                     |                 |     | Actual time period= (WEW+1) * SDRAM clock cycle time             |                      |

|                     | 14:13           | R/W | WE High Hold time                                                |                      |

|                     | 12:10           | R/W | AVWEL: Address valid to WE Low.                                  |                      |

|                     |                 |     | Actual time period= (AVWEL+1) * SDRAM clock cycle time           |                      |

|                     | 9:5             | R/W | CSW: Chip select width.                                          |                      |

|                     |                 |     | Actual time period= CSW * SDRAM clock cycle time                 |                      |

|                     | 4:3             | R/W | CSH: CS High Hold time                                           |                      |

|                     |                 |     | Actual time period=CSH * SDRAM clock cycle time                  |                      |

|                     | 2:0             | R/W | AVCSL: Address valid to CS Low.                                  |                      |

|                     |                 |     | Actual time period= (AVCSL+2) * SDRAM clock cycle time           |                      |

| 0xAF0000            | 1               | R/W | 1:ROM2 is parallel flash, 0: ROM2 is serial flash                | 32'h000000000        |