## Flash Programmable System Devices with 8032 MCU with USB and Programmable Logic

#### FEATURES SUMMARY

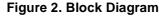

- FAST 8-BIT 8032 MCU

- 40MHz at 5.0V, 24MHz at 3.3V

- Core, 12-clocks per instruction

- DUAL FLASH MEMORIES WITH MEMORY MANAGEMENT

- Place either memory into 8032 program address space or data address space

- READ-while-WRITE operation for In-Application Programming and EEPROM emulation

- Single voltage program and erase

- 100K minimum erase cycles, 15-year retention

- CLOCK, RESET, AND SUPPLY MANAGEMENT

- SRAM is Battery Backup capable

- Normal, Idle, and Fower Dwn Mode Power-on and Lov Voltage ros at supervisor

- Programmable Watchdog Timer PROGRAMMABLE LOGIC, GENERAL

- PURPOSE

- 16 macrocells

- Implements state machines, glue-logic, and so forth

- COMMUNICATION INTERFACES

- I<sup>2</sup>C Master/Slave bus controller

- Two UARTs with independent baud rate

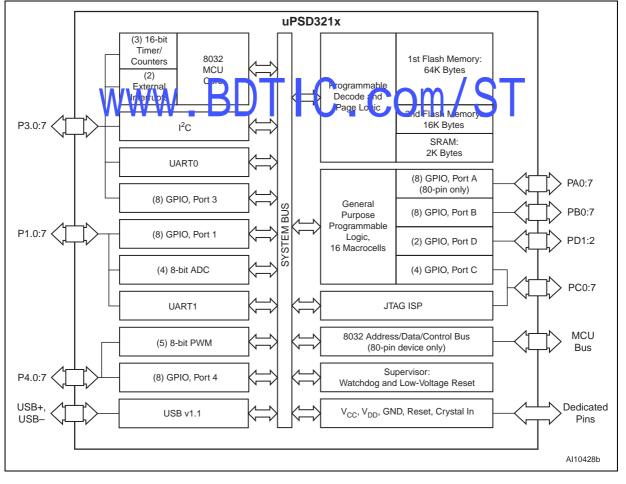

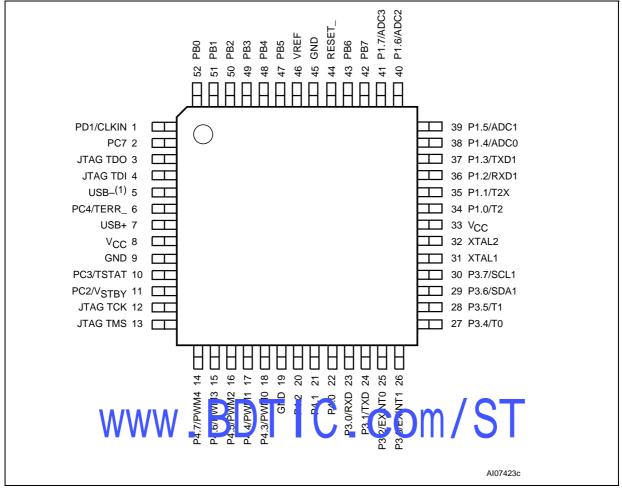

- Six I/O ports with up to 46 I/O pins

- 8032 Address/Data bus available on TQFP80 package

- 5 PWM outputs, 8-bit resolution

- USB v1.1, low-speed 1.5Mbps, 3 endpoints (uPSD3212A only)

#### Figure 1. Packages

- JTAG IN-SYSTEM PROGRAMMING

- Program the entire device in as little as 10 seconds

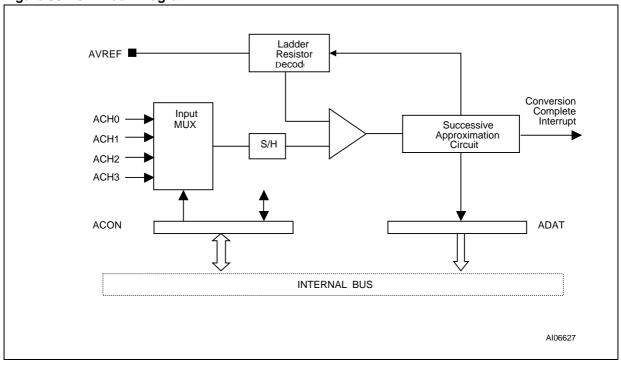

- A/D CONVERTER

- Four channels, 8-bit resolution, 10µs

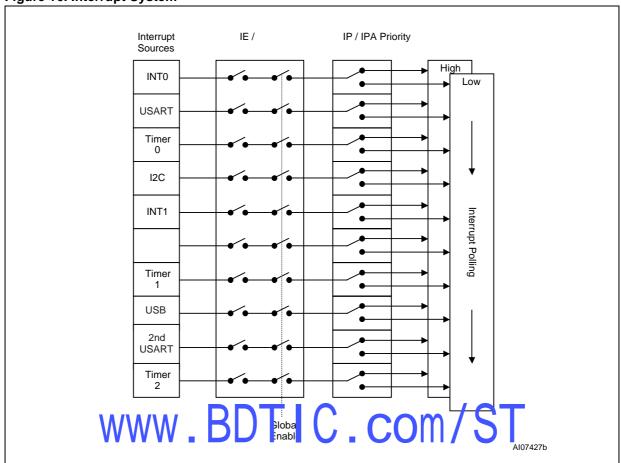

- TIMERS AND INTERRUPTS

- Three 8032 standard 16-bit timers

- 10 Interrupt sources with two external interrupt pins

- Single Supply Voltage

- 4.5 to 5.5V

- 3.0 to 3.6V

| Part Number     | Max<br>Clock<br>(MHz) | 1st<br>Flash<br>(bytes) | 2nd<br>Flash<br>(bytes) | SRAM<br>(bytes) | GPIO | USB | 8032<br>Bus | V <sub>CC</sub><br>(V) | Pkg.   | Temp.         |

|-----------------|-----------------------|-------------------------|-------------------------|-----------------|------|-----|-------------|------------------------|--------|---------------|

| uPSD3212C-40T6  | 40                    | 64K                     | 16K                     | 2K              | 37   | No  | No          | 4.5-5.5                | TQFP52 | -40°C to 85°C |

| uPSD3212CV-24T6 | 24                    | 64K                     | 16K                     | 2K              | 37   | No  | No          | 3.0-3.6                | TQFP52 | -40°C to 85°C |

| uPSD3212C-40U6  | 40                    | 64K                     | 16K                     | 2K              | 46   | No  | Yes         | 4.5-5.5                | TQFP80 | -40°C to 85°C |

| uPSD3212CV-24U6 | 24                    | 64K                     | 16K                     | 2K              | 46   | No  | Yes         | 3.0-3.6                | TQFP80 | -40°C to 85°C |

| uPSD3212A-40T6  | 40                    | 64K                     | 16K                     | 2K              | 37   | Yes | No          | 4.5-5.5                | TQFP52 | –40°C to 85°C |

| uPSD3212A-40U6  | 40                    | 64K                     | 16K                     | 2K              | 46   | Yes | Yes         | 4.5-5.5                | TQFP80 | -40°C to 85°C |

#### **Table 1. Device Summary**

# www.BDTIC.com/ST

### TABLE OF CONTENTS

| FEATURES SUMMARY                                                                                                                                                                                                                                                                                                                                               | 1                                                                                                        |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

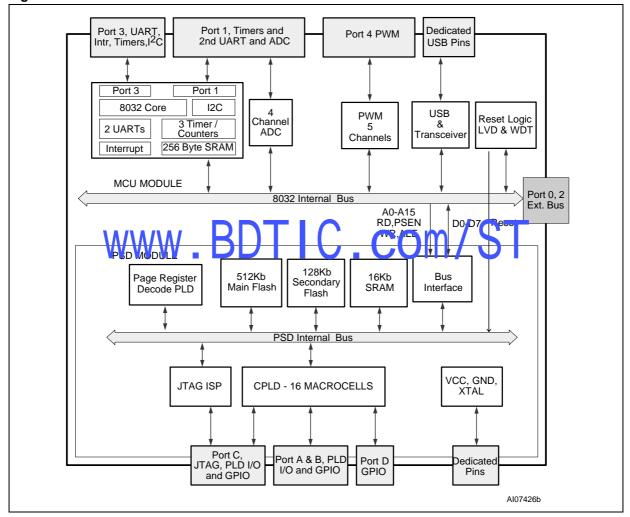

| SUMMARY DESCRIPTION                                                                                                                                                                                                                                                                                                                                            | 7                                                                                                        |

| 52-PIN PACKAGE I/O PORT                                                                                                                                                                                                                                                                                                                                        | 12                                                                                                       |

| ARCHITECTURE OVERVIEW                                                                                                                                                                                                                                                                                                                                          |                                                                                                          |

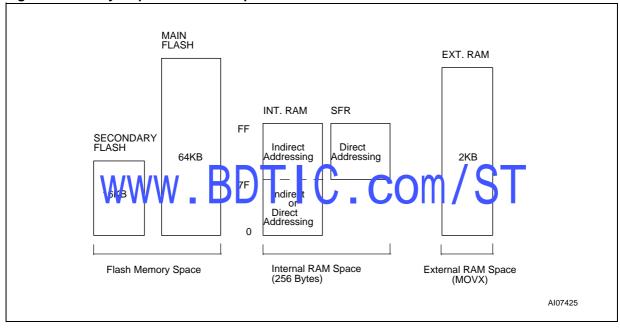

| Memory Organization                                                                                                                                                                                                                                                                                                                                            | 13                                                                                                       |

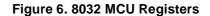

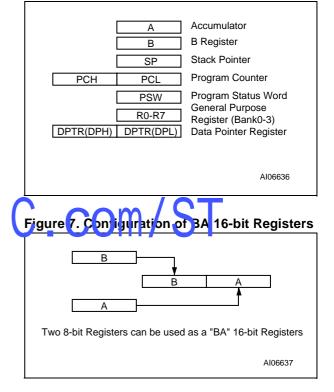

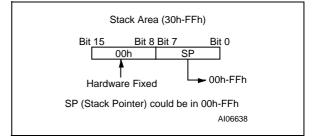

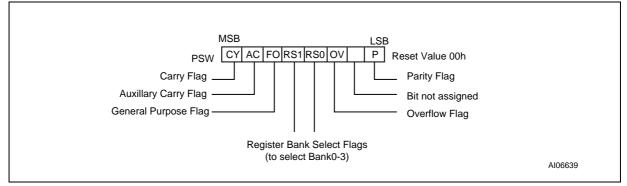

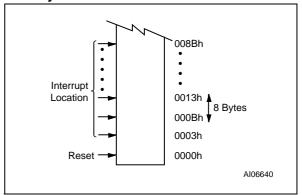

| Registers                                                                                                                                                                                                                                                                                                                                                      |                                                                                                          |

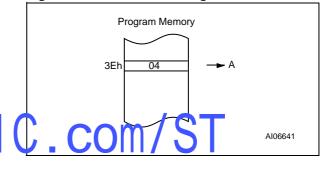

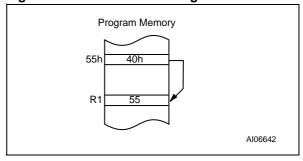

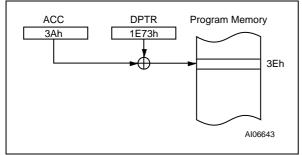

| Program Memory                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |

| Data memory                                                                                                                                                                                                                                                                                                                                                    |                                                                                                          |

| RAM                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |

| XRAM-PSD                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                        |

| SFR                                                                                                                                                                                                                                                                                                                                                            |                                                                                                          |

| Addressing Modes                                                                                                                                                                                                                                                                                                                                               |                                                                                                          |

| Arithmetic Instructions                                                                                                                                                                                                                                                                                                                                        |                                                                                                          |

| Logical Instructions                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |

| Boolean Instructions                                                                                                                                                                                                                                                                                                                                           |                                                                                                          |

| Relative Offset                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

| Jump Instructions                                                                                                                                                                                                                                                                                                                                              |                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                | -                                                                                                        |

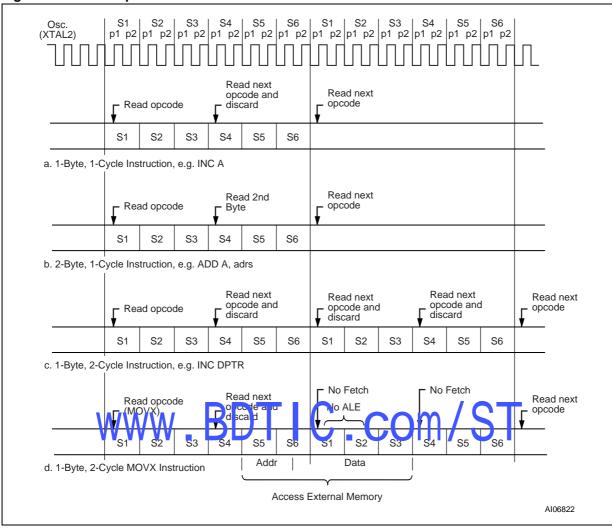

| Machine Cycles                                                                                                                                                                                                                                                                                                                                                 |                                                                                                          |

| UPSD3200 HARDWARE DESCRIPTION                                                                                                                                                                                                                                                                                                                                  |                                                                                                          |

|                                                                                                                                                                                                                                                                                                                                                                |                                                                                                          |

| MCU MODULE DISCRIPTION                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |

| MCU MODULE DISCRIPTION<br>Special Function Registers<br>INTERRUPT SYSTEM                                                                                                                                                                                                                                                                                       |                                                                                                          |

| MCU MODULE DISCRIPTION                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |

| MCU MODULE DISCRIPTION<br>Special Function Registers<br>INTERRUPT SYSTEM                                                                                                                                                                                                                                                                                       |                                                                                                          |

| MCU MODULE DISCRIPTION                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |

| MCU MODULE DISCRIPTION                                                                                                                                                                                                                                                                                                                                         |                                                                                                          |

| MCU MODULE DISCRIPTION<br>Special Function Registers<br>INTERRUPT SYSTEM.<br>External Int0.<br>Timer 0 and 1 Interrupts<br>Timer 2 Interrupt<br>I <sup>2</sup> C Interrupt                                                                                                                                                                                     |                                                                                                          |

| MCU MODULE DISCRIPTION<br>Special Function Registers<br>INTERRUPT SYSTEM.<br>External Int0.<br>Timer 0 and 1 Interrupts<br>Timer 2 Interrupt<br>I <sup>2</sup> C Interrupt<br>External Int1.<br>USB Interrupt<br>USART Interrupt                                                                                                                               |                                                                                                          |

| MCU MODULE DISCRIPTION<br>Special Function Registers<br>INTERRUPT SYSTEM.<br>External Int0.<br>Timer 0 and 1 Interrupts<br>Timer 2 Interrupt<br>I <sup>2</sup> C Interrupt<br>External Int1.<br>USB Interrupt<br>USART Interrupt<br>Interrupt Structure.                                                                                                       | 28<br>28<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34                   |

| MCU MODULE DISCRIPTION<br>Special Function Registers<br>INTERRUPT SYSTEM.<br>External Int0.<br>Timer 0 and 1 Interrupts<br>Timer 2 Interrupt<br>I <sup>2</sup> C Interrupt<br>External Int1.<br>USB Interrupt<br>USART Interrupt<br>Interrupt Structure<br>Interrupt Senable Structure                                                                         | 28<br>28<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>36<br>36<br>36<br>36 |

| MCU MODULE DISCRIPTION<br>Special Function Registers<br>INTERRUPT SYSTEM.<br>External Int0.<br>Timer 0 and 1 Interrupts<br>Timer 2 Interrupt<br>I <sup>2</sup> C Interrupt<br>External Int1.<br>USB Interrupt<br>USART Interrupt<br>Interrupt Structure.                                                                                                       | 28<br>28<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>36<br>36<br>36<br>36 |

| MCU MODULE DISCRIPTION<br>Special Function Registers<br>INTERRUPT SYSTEM.<br>External Int0.<br>Timer 0 and 1 Interrupts<br>Timer 2 Interrupt<br>I <sup>2</sup> C Interrupt<br>External Int1.<br>USB Interrupt<br>USART Interrupt<br>Interrupt Structure<br>Interrupt Senable Structure                                                                         | 28<br>28<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34                   |

| MCU MODULE DISCRIPTION<br>Special Function Registers<br>INTERRUPT SYSTEM.<br>External Int0.<br>Timer 0 and 1 Interrupts<br>Timer 2 Interrupt<br>I <sup>2</sup> C Interrupt<br>External Int1.<br>USB Interrupt<br>USART Interrupt<br>Interrupt Priority Structure<br>Interrupt Senable Structure<br>How Interrupts are Handled                                  | 28<br>28<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34                   |

| MCU MODULE DISCRIPTION .<br>Special Function Registers .<br>INTERRUPT SYSTEM.<br>External Int0.<br>Timer 0 and 1 Interrupts .<br>Timer 2 Interrupt .<br>I <sup>2</sup> C Interrupt .<br>External Int1.<br>USB Interrupt .<br>USART Interrupt .<br>Interrupt Structure .<br>Interrupts Enable Structure .<br>How Interrupts are Handled .<br>POWER-SAVING MODE. | 28<br>28<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34<br>34                   |

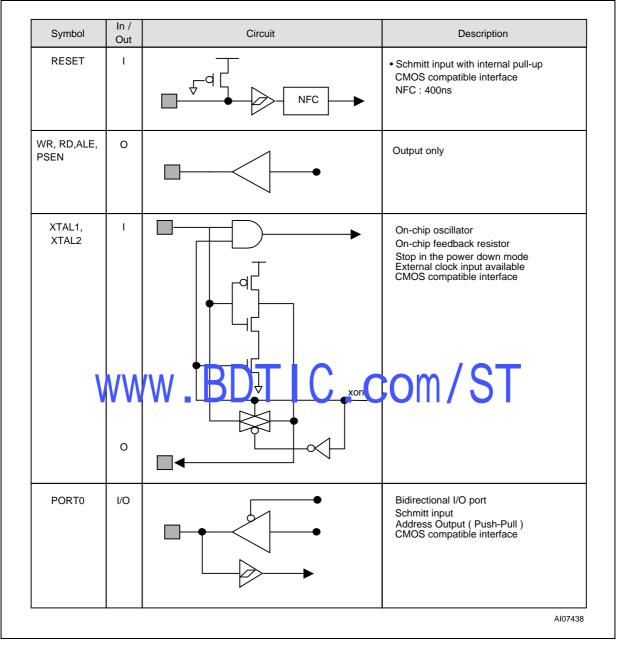

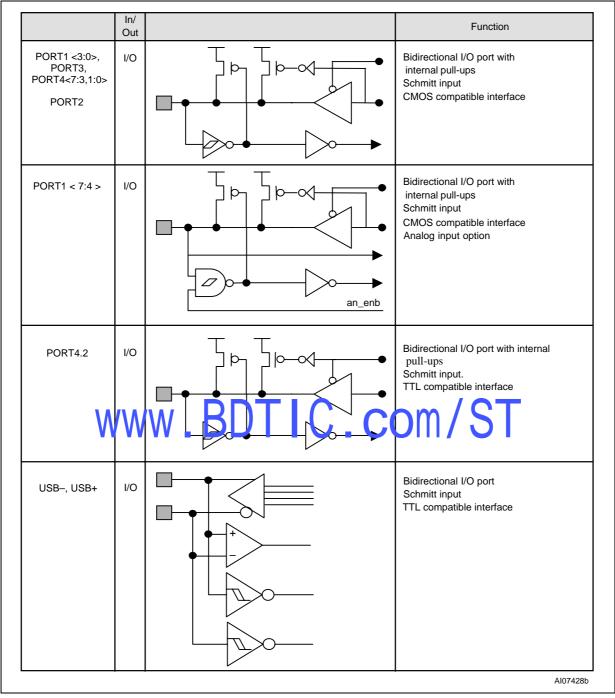

| VO PORTS (MCU Module)       40         PORT Type and Description       42         OSCILLATOR       44         SUPERVISORY       45         External Reset       45         Low VpD Voltage Reset       45         Watchdog Timer Overflow       45         USB Reset       45         WATCHDOG TIMER       46         TIMER/COUNTERS (TIMER 0, TIMER 1 AND TIMER 2)       48         Timer 0 and Timer 1.       48         Timer 2       51         STANDARD SERIAL INTERFACE (UART)       55         Multiprocessor Communications.       55         Serial Port Control Register       56         ADC Interrupt       65         PULSE WIDTH MODULATION (PWM)       67         4-channel PVM Unit (PWM 0-3)       67         Programmable Period 8-bit PVM.       70         PVWM 4 Channel Operation       71         1 <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT)       74         Address Register (S2DAT)       74         Address Register (S2DAT)       76         USB HARDWARE       76         USB Palated registers       76 <t< th=""><th>Idle Mode</th><th></th></t<>                                                 | Idle Mode                                      |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------|

| OSCILLATOR       44         SUPERVISORY       45         External Reset       45         Low Vop Voltage Reset       45         Watchdog Timer Overflow       45         USB Reset       45         WATCHDOG TIMER       46         TIMER/COUNTERS (TIMER 0, TIMER 1 AND TIMER 2)       48         Timer 0 and Timer 1       48         Timer 2       51         STANDARD SERIAL INTERFACE (UART)       55         Multiprocessor Communications       55         Serial Port Control Register       56         ANALOG-TO-DISTALCOVERTOR ADC       65         ADC Interrupt       65         PULSE WIDTH MODULATION (PWM)       67         4-channel PWM Unit (PWM 0-3)       67         Programmable Period 8-bit PWM       70         PWM 4 Channel Operation       71         1 <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT)       74         Address Register (S2DAT)       74         Address Register (S2DAT)       75         USB HARDWARE       76         USB Pollact registers       76         USB Pollact registers       76 <td< td=""><td>I/O PORTS (MCU Module)</td><td>0</td></td<>                                  | I/O PORTS (MCU Module)                         | 0        |

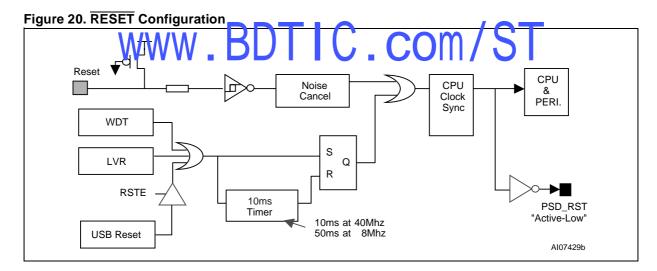

| SUPERVISORY       45         External Reset       45         Low V <sub>DD</sub> Voltage Reset       45         Low V <sub>DD</sub> Voltage Reset       45         USB Reset       45         WATCHDOG TIMER       46         TIMER/COUNTERS (TIMER 0, TIMER 1 AND TIMER 2)       48         Timer 0 and Timer 1.       48         Timer 0 and Timer 1.       48         Timer 2       51         STANDARD SERIAL INTERFACE (UART)       55         Multiprocessor Communications.       55         Serial Port Control Register       56         ADC Interrupt.       65         PULSE WIDTH MODULATION (PWM)       67         4-channel PWM Unit (PWM 0-3)       67         Programmable Period 8-bit PWM       70         PWM 4 Channel Operation       71         I <sup>2</sup> C INTERFACE       72         Serial Status Register (S2DAT)       74         Data Shift Register (S2DAT)       74         DAta Shift Register (S2DAT)       75         USB HARDWARE       76         VDSB related registers       76         VDSB related registers       76         VDSB related registers       76         VDSB related registers       76 <t< td=""><td>PORT Type and Description</td><td>2</td></t<> | PORT Type and Description                      | 2        |

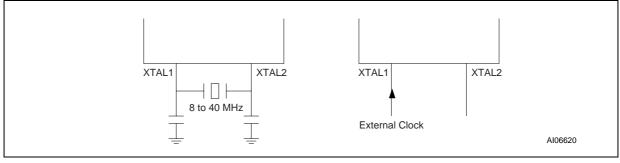

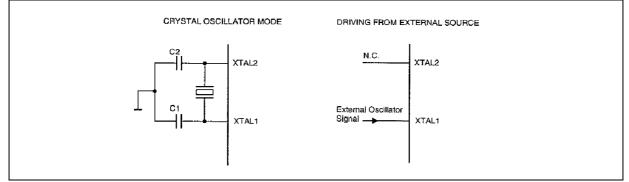

| External Reset       45         Low V <sub>DD</sub> Voltage Reset       45         Watchdog Timer Overflow       45         USB Reset       45         WATCHDOG TIMER       46         TIMER/COUNTERS (TIMER 0, TIMER 1 AND TIMER 2)       48         Timer 0 and Timer 1.       48         Timer 0 and Timer 1.       48         Timer 2       51         STANDARD SERIAL INTERFACE (UART)       55         Multiprocessor Communications       55         Serial Port Control Register       56         ANALOG-TO-DISTANCOVER       ADC       C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | OSCILLATOR                                     | 4        |

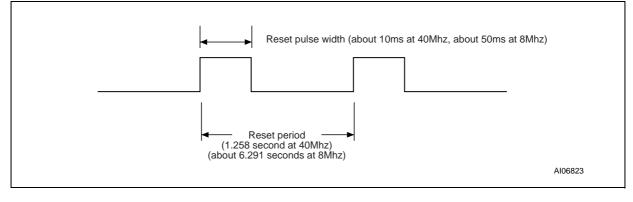

| Low V <sub>DD</sub> Voltage Reset       45         Watchdog Timer Overflow       45         USB Reset       45         WATCHDOG TIMER       46         TIMER/COUNTERS (TIMER 0, TIMER 1 AND TIMER 2)       48         Timer 0 and Timer 1.       48         Timer 2       51         STANDARD SERIAL INTERFACE (UART)       55         Multiprocessor Communications.       55         Serial Port Control Register       56         ANALOG-TO-DIMPACOVERT DADC       COM/.ST         ADC Interrupt.       65         PULSE WIDTH MODULATION (PWM).       67         4-channel PWM Unit (PWM 0-3)       67         Programmable Period 8-bit PWM.       70         PWM 4 Channel Operation       71         I <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT).       74         Address Register (S2DAT).       74         Address Register (S2ADR).       75         USB HARDWARE       76         USB related registers       76         Transceiver       83         Receiver Characteristics.       85         PSD MODULE.       88                                                                                                 | SUPERVISORY4                                   | 5        |

| TIMER/COUNTERS (TIMER 0, TIMER 1 AND TIMER 2).       48         Timer 0 and Timer 1.       48         Timer 2       51         STANDARD SERIAL INTERFACE (UART)       55         Multiprocessor Communications.       55         Serial Port Control Register       56         ANALOG-TO-DISTALCOVVERTOR OF COMMENTS       55         ADC Interrupt.       65         PULSE WIDTH MODULATION (PWM).       67         4-channel PWM Unit (PWM 0-3).       67         Programmable Period 8-bit PWM.       70         PWM 4 Channel Operation       71         I <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2ADR).       75         USB HARDWARE.       76         USB related registers       76         Transceiver       83         Receiver Characteristics.       85         External USB Pull-Up Resistor.       86         PSD MODULE.       88                                                                                                                                                                                                                                                                                     | Low V <sub>DD</sub> Voltage Reset              | 5<br>5   |

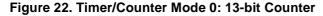

| Timer 0 and Timer 1.       48         Timer 2       51         STANDARD SERIAL INTERFACE (UART)       55         Multiprocessor Communications       55         Serial Port Control Register       66         ANALOG-TO-DISTRALCOVERTOR ACC.       COM./SIT         ADC Interrupt       65         PULSE WIDTH MODULATION (PWM)       67         4-channel PWM Unit (PWM 0-3)       67         Programmable Period 8-bit PWM       70         PWM 4 Channel Operation       71         I <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT)       74         Address Register (S2ADR)       75         USB HARDWARE       76         USB related registers       76         Status Rugister (S2DAT)       83         Receiver Characteristics       83         Receiver Characteristics       85         External USB Pull-Up Resistor       86         PSD MODULE       88                                                                                                                                                                                                                                                                | WATCHDOG TIMER                                 | 6        |

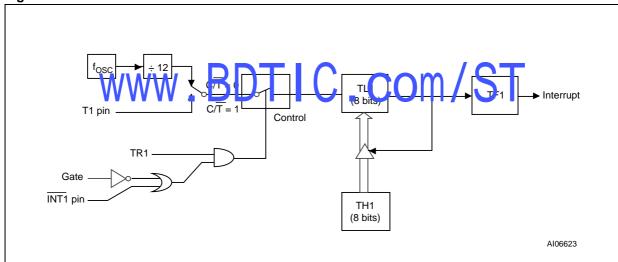

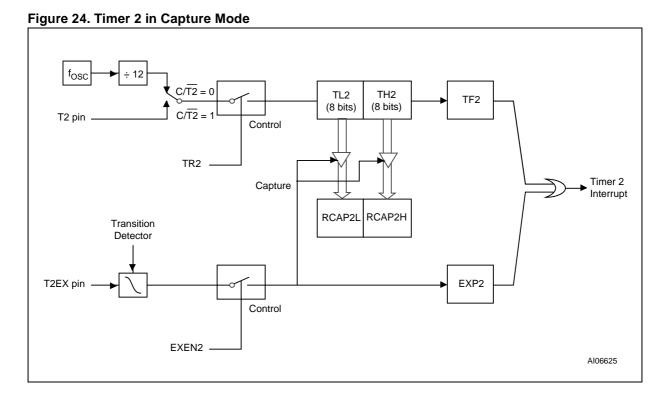

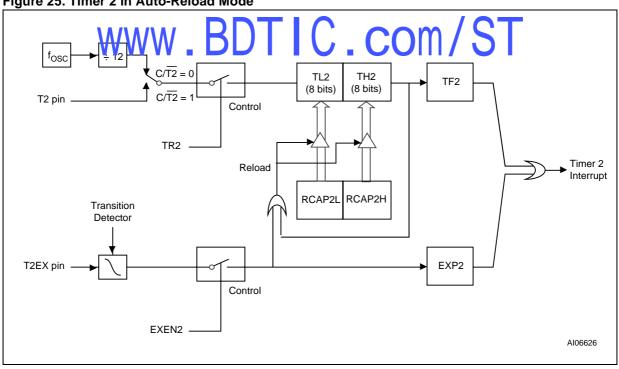

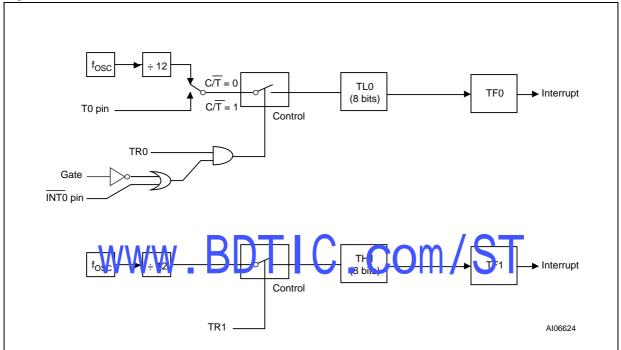

| Timer 2       51         STANDARD SERIAL INTERFACE (UART)       55         Multiprocessor Communications       55         Serial Port Control Register       56         ANALOG-TO-DIGITALCOVVERTOR ACC       COM         ANALOG-TO-DIGITALCOVVERTOR ACC       65         ADC Interrupt       65         PULSE WIDTH MODULATION (PWM)       67         4-channel PWM Unit (PWM 0-3)       67         Programmable Period 8-bit PWM       70         PWM 4 Channel Operation       71         1 <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT)       74         Address Register (S2ADR)       76         USB HARDWARE       76         USB related registers       76         Transceiver       83         Receiver Characteristics       85         PSD MODULE       88                                                                                                                                                                                                                                                                                                                                                                | TIMER/COUNTERS (TIMER 0, TIMER 1 AND TIMER 2)4 | 8        |

| Multiprocessor Communications.       55         Serial Port Control Register       56         ANALOG-TO-DISTALCOVVERTOR ADC       COM./ST         ADC Interrupt.       65         PULSE WIDTH MODULATION (PWM).       67         4-channel PWM Unit (PWM 0-3)       67         Programmable Period 8-bit PWM.       70         PWM 4 Channel Operation       71         I <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT)       74         Address Register (S2ADR)       75         USB HARDWARE       76         USB related registers       76         Transceiver       83         Receiver Characteristics.       85         External USB Pull-Up Resistor       86                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                | -        |

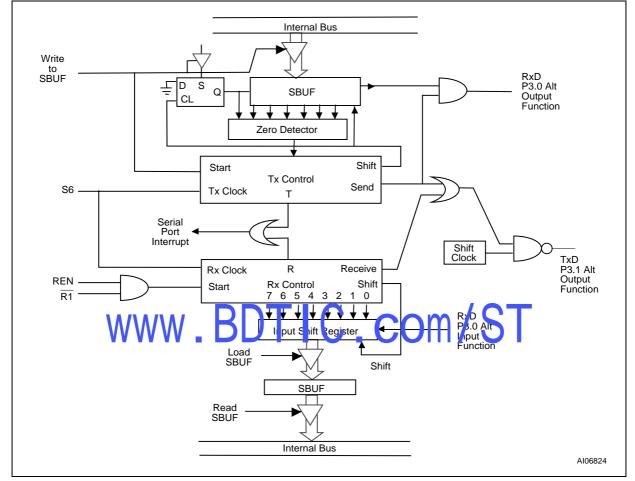

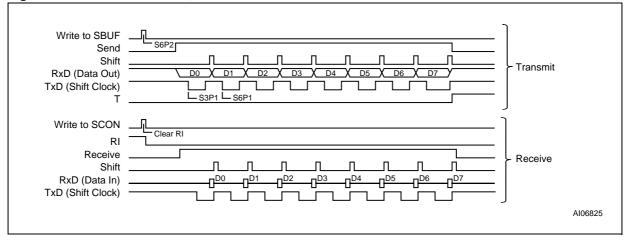

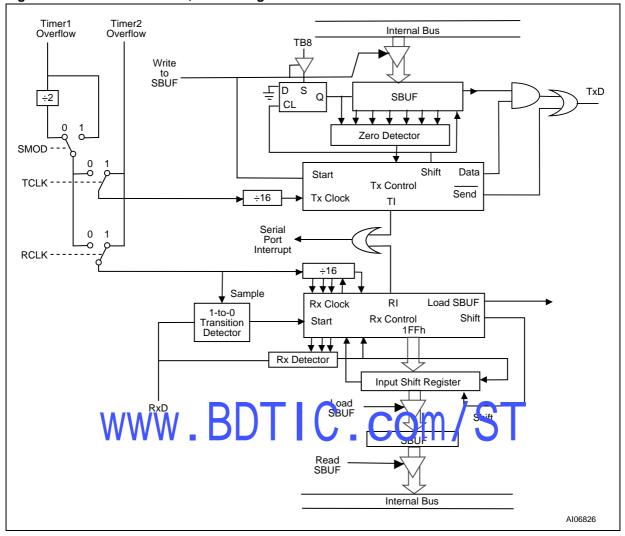

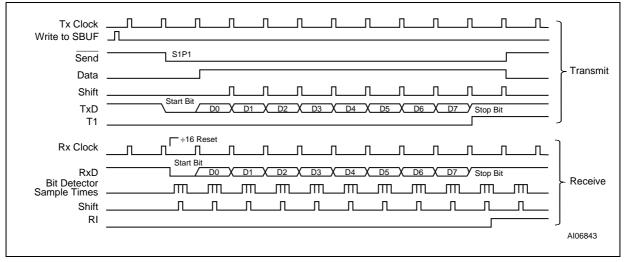

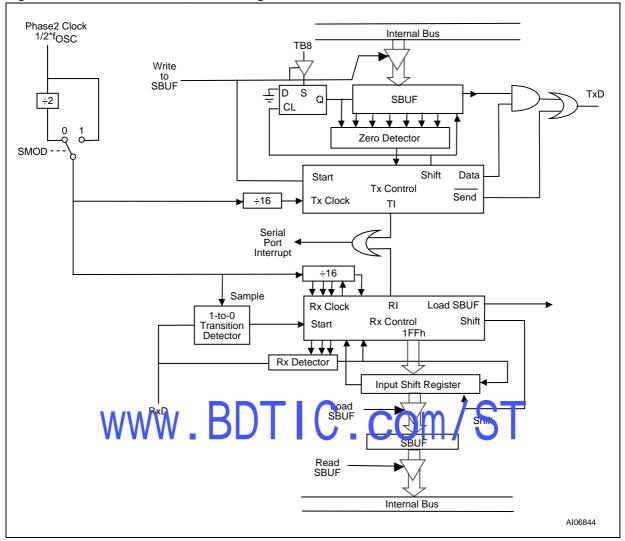

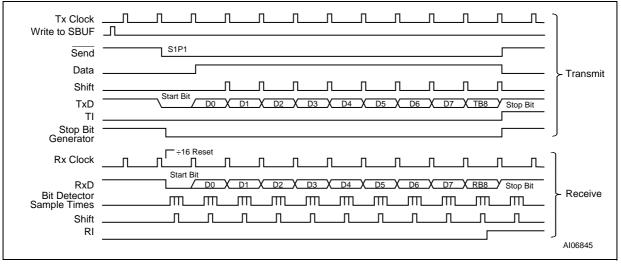

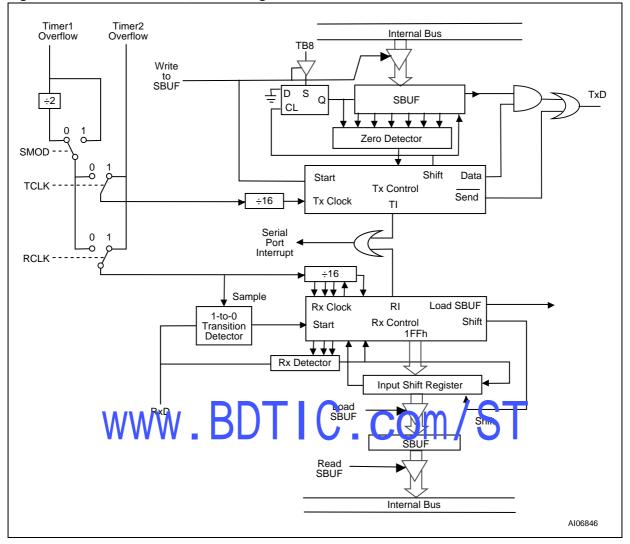

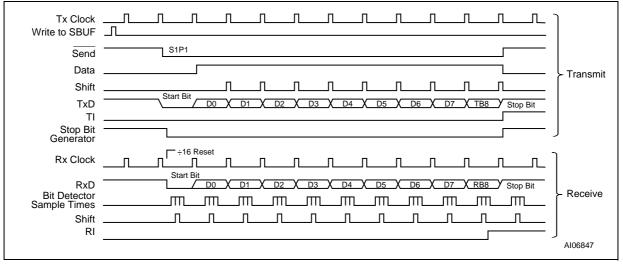

| Serial Port Control Register 56<br>ANALOG-TO-DIGITAL COVVERTOR ADCT C. COM / S.T. 65<br>ADC Interrupt. 65<br>PULSE WIDTH MODULATION (PWM). 67<br>4-channel PWM Unit (PWM 0-3). 67<br>Programmable Period 8-bit PWM. 70<br>PWM 4 Channel Operation 71<br>I <sup>2</sup> C INTERFACE 72<br>Serial Status Register (S2STA) 74<br>Data Shift Register (S2DAT) 74<br>Address Register (S2ADR). 75<br>USB HARDWARE 76<br>USB related registers 76<br>Transceiver 83<br>Receiver Characteristics 85<br>External USB Pull-Up Resistor. 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | STANDARD SERIAL INTERFACE (UART)               | 5        |

| ADC Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | •                                              |          |

| PULSE WIDTH MODULATION (PWM).       67         4-channel PWM Unit (PWM 0-3)       67         Programmable Period 8-bit PWM.       70         PWM 4 Channel Operation       71         I <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT)       74         Address Register (S2ADR)       75         USB HARDWARE       76         USB related registers       76         Transceiver       83         Receiver Characteristics       85         External USB Pull-Up Resistor       86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                |          |

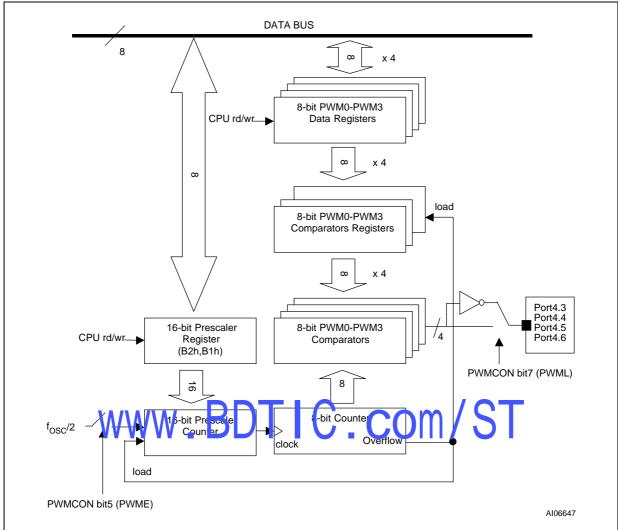

| 4-channel PWM Unit (PWM 0-3)       67         Programmable Period 8-bit PWM       70         PWM 4 Channel Operation       71         I <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT)       74         Address Register (S2ADR)       75         USB HARDWARE       76         USB related registers       76         Transceiver       83         Receiver Characteristics       85         External USB Pull-Up Resistor       86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ADC Interrupt                                  | 5        |

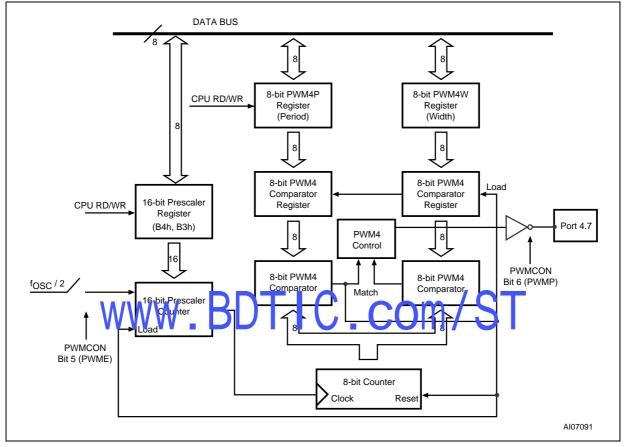

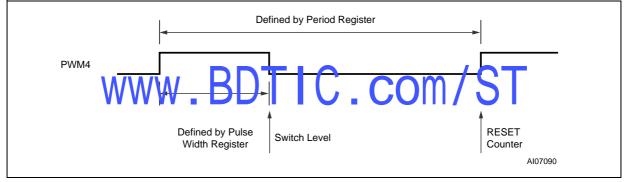

| Programmable Period 8-bit PWM.       70         PWM 4 Channel Operation       71         I <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT)       74         Address Register (S2ADR)       75         USB HARDWARE       76         USB related registers       76         Transceiver       83         Receiver Characteristics       85         External USB Pull-Up Resistor       86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PULSE WIDTH MODULATION (PWM)6                  | 7        |

| PWM 4 Channel Operation       71         I <sup>2</sup> C INTERFACE       72         Serial Status Register (S2STA)       74         Data Shift Register (S2DAT)       74         Address Register (S2ADR)       75         USB HARDWARE       76         USB related registers       76         Transceiver       83         Receiver Characteristics       85         External USB Pull-Up Resistor       86                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |          |

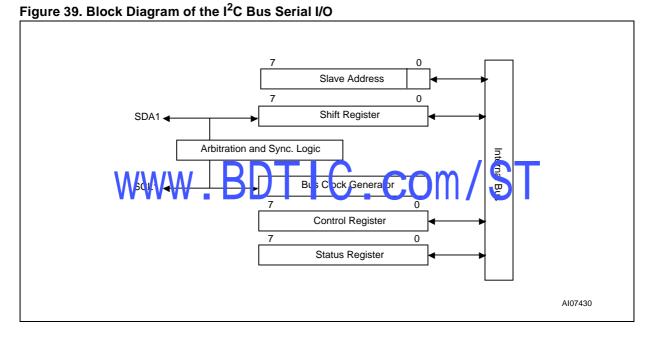

| Serial Status Register (S2STA)74Data Shift Register (S2DAT)74Address Register (S2ADR)75USB HARDWARE76USB related registers76Transceiver83Receiver Characteristics85External USB Pull-Up Resistor86PSD MODULE88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |          |

| Serial Status Register (S2STA)74Data Shift Register (S2DAT)74Address Register (S2ADR)75USB HARDWARE76USB related registers76Transceiver83Receiver Characteristics85External USB Pull-Up Resistor86PSD MODULE88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                | <u>י</u> |

| Data Shift Register (S2DAT)74Address Register (S2ADR)75USB HARDWARE76USB related registers76Transceiver83Receiver Characteristics85External USB Pull-Up Resistor86PSD MODULE88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                |          |

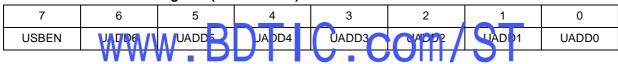

| USB HARDWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                |          |

| USB related registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Address Register (S2ADR)                       | 5        |

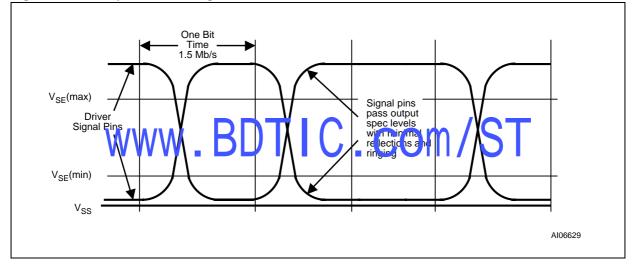

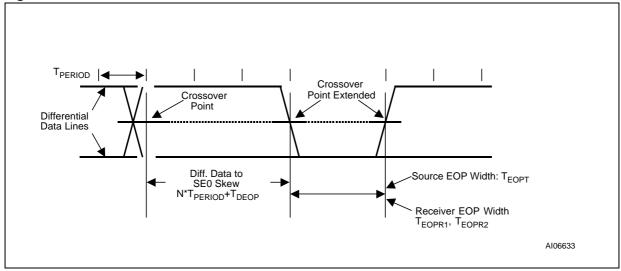

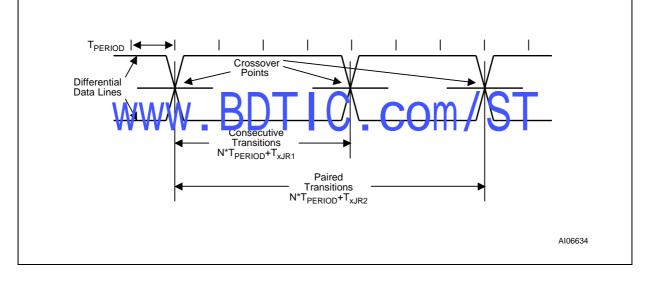

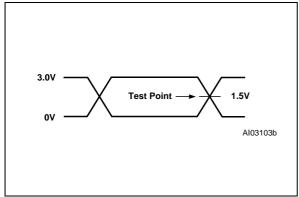

| Transceiver    83      Receiver Characteristics.    85      External USB Pull-Up Resistor.    86      PSD MODULE.    88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | USB HARDWARE                                   | 6        |

| Receiver Characteristics.    85      External USB Pull-Up Resistor.    86      PSD MODULE.    88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                |          |

| External USB Pull-Up Resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                |          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                | -        |

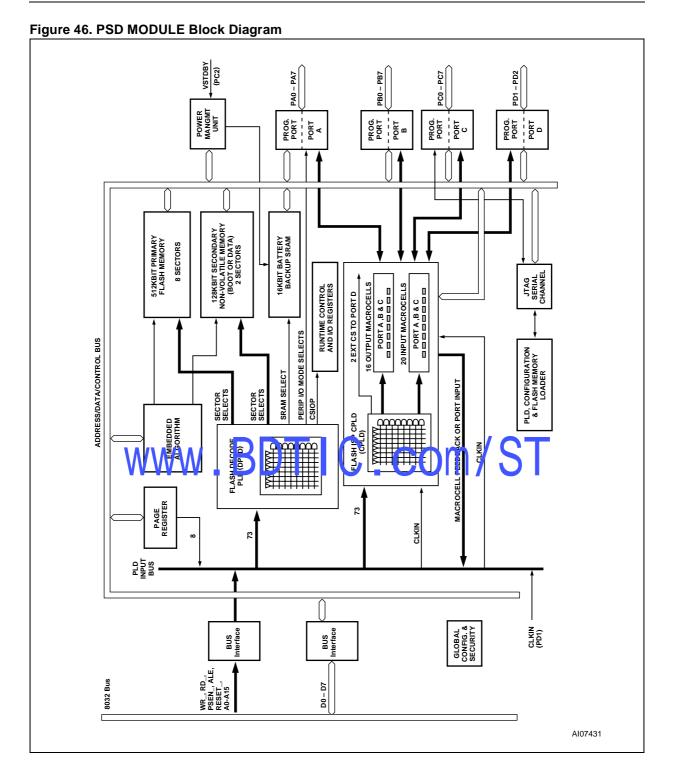

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PSD MODULE                                     | 8        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                |          |

**\\\**

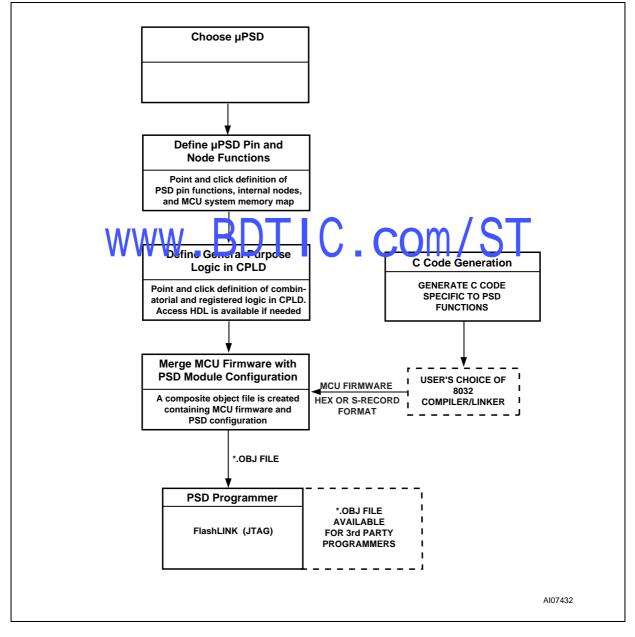

| In-System Programming (ISP)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 90                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

| DEVELOPMENT SYSTEM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 91                                                                                                                                |

| PSD MODULE REGISTER DESCRIPTION AND ADDRESS OFFSET                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 92                                                                                                                                |

| PSD MODULE DETAILED OPERATION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93                                                                                                                                |

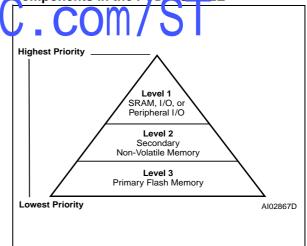

| MEMORY BLOCKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 93                                                                                                                                |

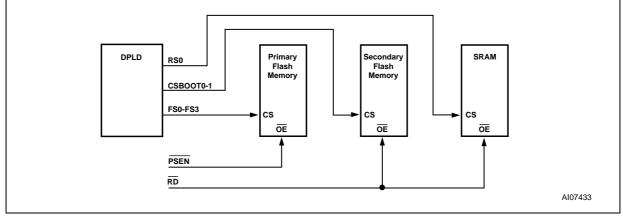

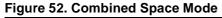

| Primary Flash Memory and Secondary Flash memory Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| Memory Block Select Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                   |

| Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                   |

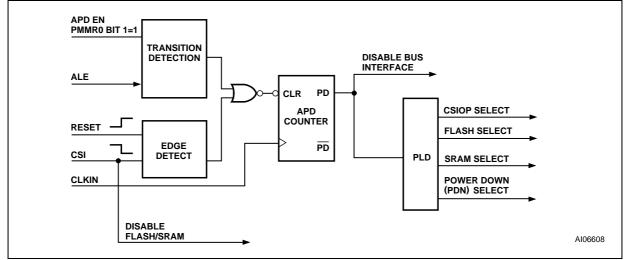

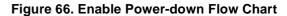

| Power-down Instruction and Power-up Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

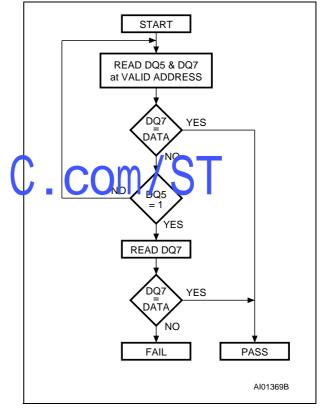

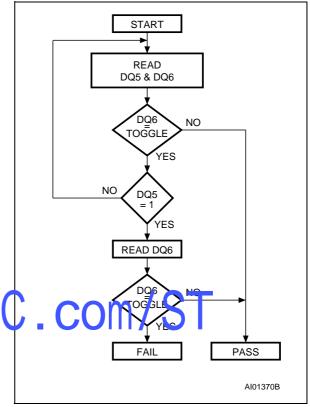

| Programming Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                   |

| Erasing Flash Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                   |

| Specific Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

| SRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                                                                                                                 |

| Sector Select and SRAM Select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                   |

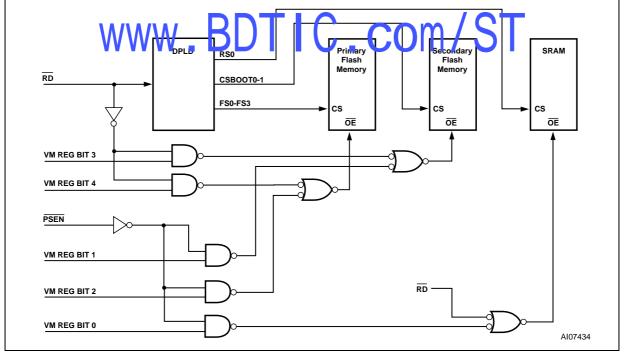

| Page Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 105                                                                                                                               |

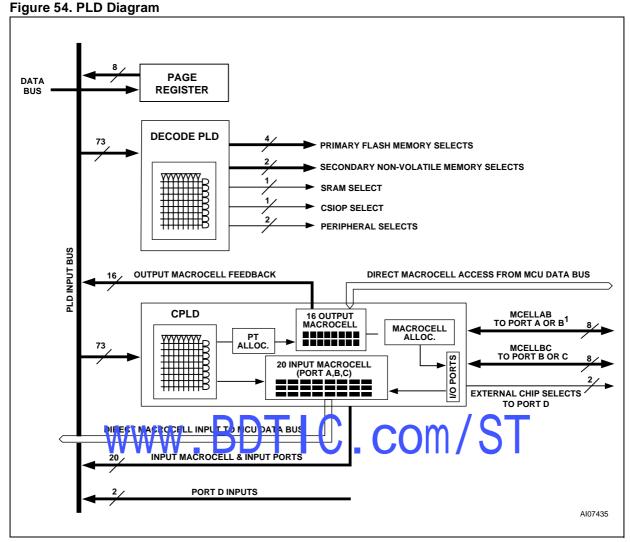

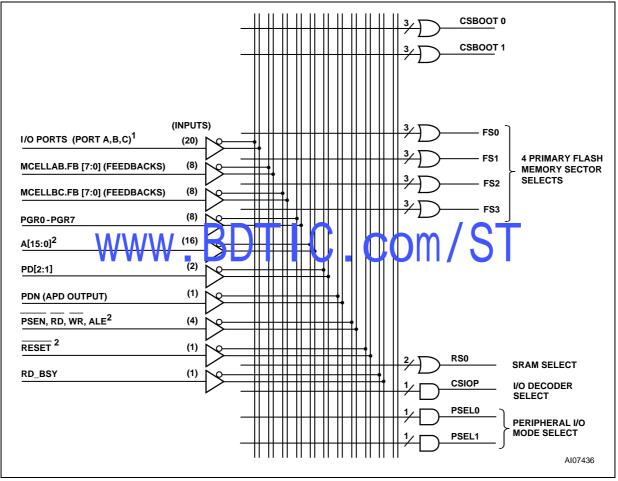

| PLDs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 106                                                                                                                               |

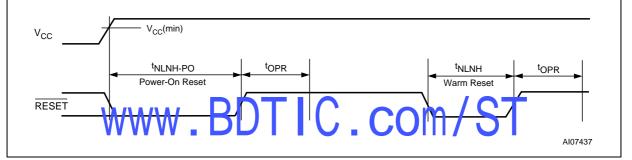

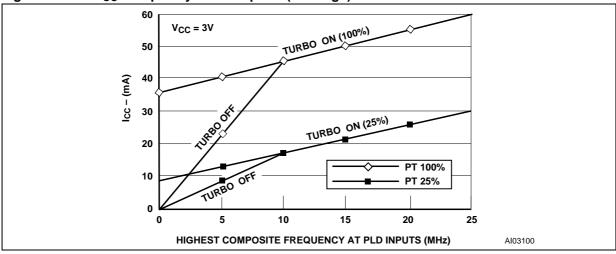

| The Turbo Bit in PSD MODULE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 106                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 108                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 108                                                                                                                               |

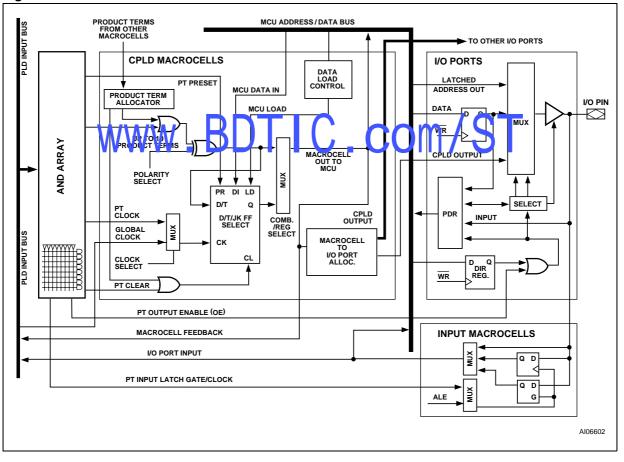

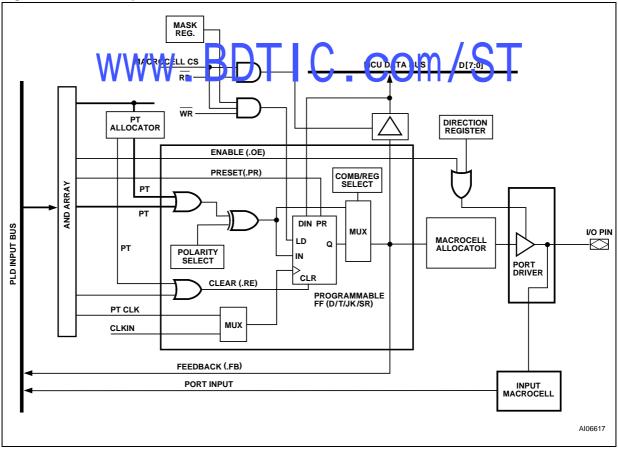

| Decode PLD (DPLD)<br>Complex PLD (dPLD)<br>Output Macrocell (OMC)                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                   |

| Product Term Allocator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 111                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 111                                                                                                                               |

| Product Term Allocator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 110<br>111<br>112                                                                                                                 |

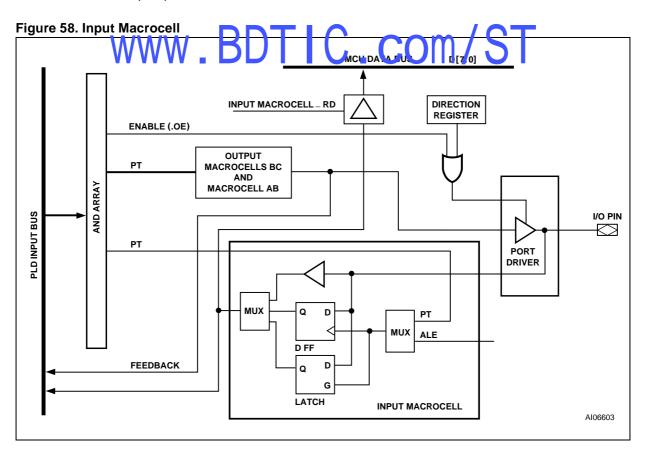

| Product Term Allocator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 110<br>111<br>112<br>113                                                                                                          |

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         I/O PORTS (PSD MODULE)                                                                                                                                                                                                                                                                                                                                                                                                          | 110<br>111<br>112<br>113<br>113                                                                                                   |

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         I/O PORTS (PSD MODULE)         General Port Architecture.                                                                                                                                                                                                                                                                                                                                                                       | 110<br>111<br>112<br>113<br>113<br>114                                                                                            |

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         I/O PORTS (PSD MODULE)         General Port Architecture.         Port Operating Modes.         MCU I/O Mode         PLD I/O Mode                                                                                                                                                                                                                                                                                               | 110<br>111<br>112<br>113<br>113<br>114<br>114<br>114                                                                              |

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         Input Macrocells (IMC)         General Port Operating Modes.         Port Operating Modes.         MCU I/O Mode         PLD I/O Mode.         Address Out Mode.                                                                                                                                                                                                                                                                 | 110<br>111<br>112<br>113<br>113<br>113<br>114<br>114<br>114<br>114                                                                |

| Violation       Product Term Allocator.         Input Macrocells (IMC)       Input Macrocells (IMC)         VO PORTS (PSD MODULE)       General Port Architecture.         Port Operating Modes.       MCU I/O Mode         PLD I/O Mode.       Address Out Mode.         Peripheral I/O Mode.       Peripheral I/O Mode.                                                                                                                                                                                                     | 110<br>111<br>112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>114                                                         |

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         I/O PORTS (PSD MODULE)         General Port Architecture.         Port Operating Modes.         MCU I/O Mode         PLD I/O Mode.         Address Out Mode.         Peripheral I/O Mode.         JTAG In-System Programming (ISP).                                                                                                                                                                                             | 110<br>111<br>112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>114<br>114<br>114                                           |

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         IvO PORTS (PSD MODULE).         General Port Architecture.         Port Operating Modes.         MCU I/O Mode         PLD I/O Mode.         Address Out Mode.         Peripheral I/O Mode.         JTAG In-System Programming (ISP)         Port Configuration Registers (PCR)                                                                                                                                                  | 110<br>111<br>112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>114<br>114<br>114<br>116                                    |

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         Input Macrocells (IMC)         VO PORTS (PSD MODULE)         General Port Architecture.         Port Operating Modes.         MCU I/O Mode         PLD I/O Mode.         Peripheral I/O Mode.         JTAG In-System Programming (ISP).         Port Configuration Registers (PCR)         Port Data Registers.                                                                                                                 | 110<br>111<br>112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>114<br>114<br>116<br>117                                    |

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         IvO PORTS (PSD MODULE).         General Port Architecture.         Port Operating Modes.         MCU I/O Mode         PLD I/O Mode.         Address Out Mode.         Peripheral I/O Mode.         JTAG In-System Programming (ISP)         Port Configuration Registers (PCR)                                                                                                                                                  | 110<br>111<br>112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>114<br>114<br>114<br>116<br>117<br>118                      |

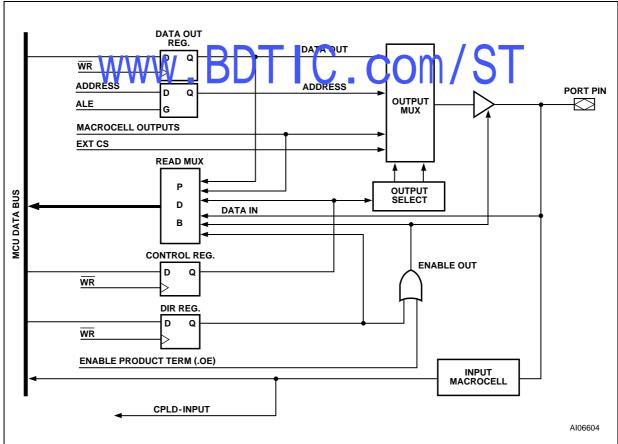

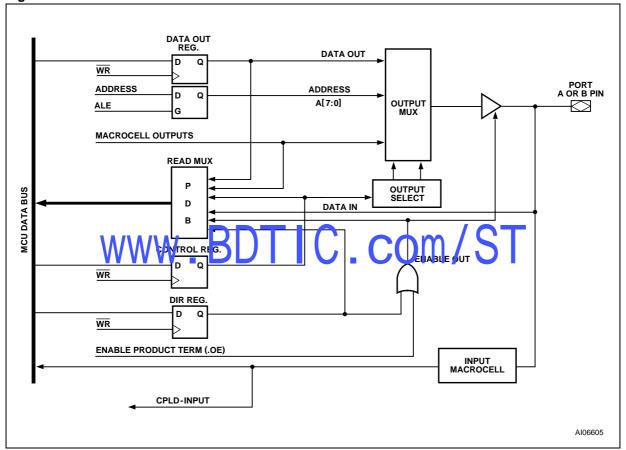

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         I/O PORTS (PSD MODULE).         General Port Architecture.         Port Operating Modes.         MCU I/O Mode         PLD I/O Mode.         Address Out Mode.         Peripheral I/O Mode.         JTAG In-System Programming (ISP).         Port Configuration Registers (PCR)         Port Data Registers.         Ports A and B – Functionality and Structure                                                                | 110<br>111<br>112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>114<br>114<br>114<br>116<br>117<br>118<br>119               |

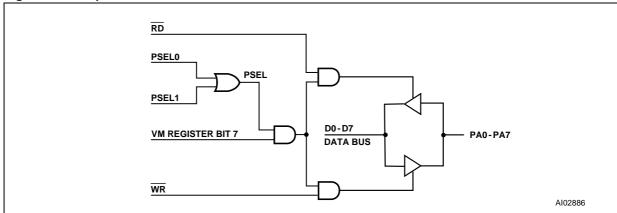

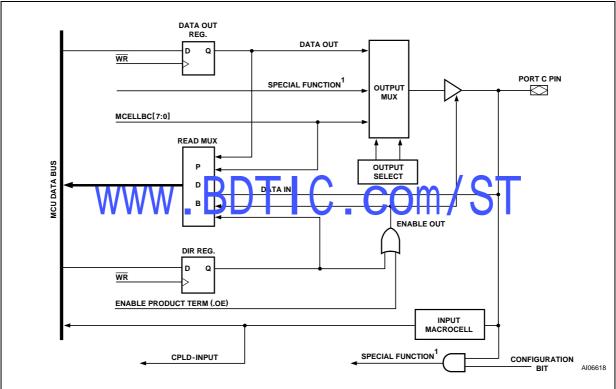

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         I/O PORTS (PSD MODULE).         General Port Architecture.         Port Operating Modes.         MCU I/O Mode         PLD I/O Mode.         Address Out Mode.         Peripheral I/O Mode.         JTAG In-System Programming (ISP).         Port Configuration Registers (PCR)         Port Data Registers.         Ports A and B – Functionality and Structure         Port C – Functionality and Structure.                  | 110<br>111<br>112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>114<br>114<br>114<br>116<br>117<br>118<br>119<br>120        |

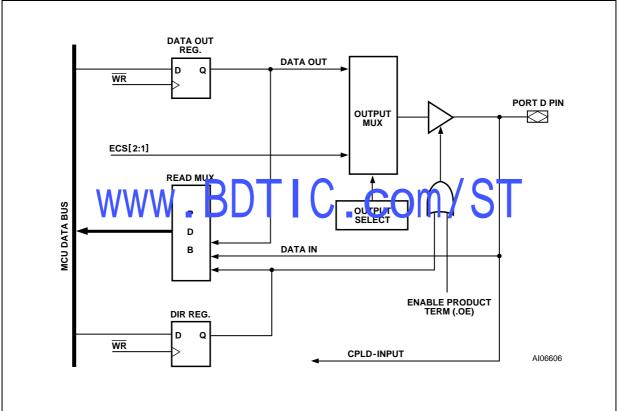

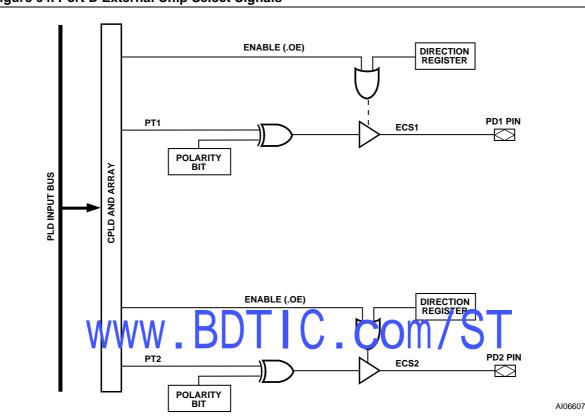

| Output Macrocell (OMC)         Product Term Allocator.         Input Macrocells (IMC)         I/O PORTS (PSD MODULE).         General Port Architecture.         Port Operating Modes.         MCU I/O Mode         PLD I/O Mode.         Address Out Mode.         Peripheral I/O Mode.         JTAG In-System Programming (ISP).         Port Configuration Registers (PCR)         Ports A and B – Functionality and Structure         Port C – Functionality and Structure.         Port D – Functionality and Structure. | 110<br>111<br>112<br>113<br>113<br>113<br>114<br>114<br>114<br>114<br>114<br>114<br>114<br>116<br>117<br>118<br>119<br>120<br>121 |

| PSD Chip Select Input (CSI, PD2)                       |     |

|--------------------------------------------------------|-----|

| Input Control Signals                                  |     |

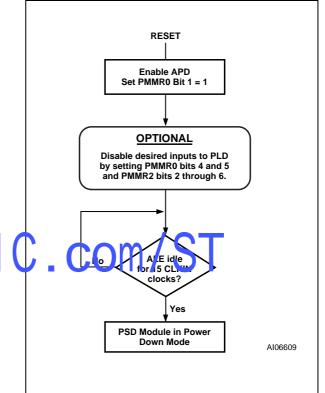

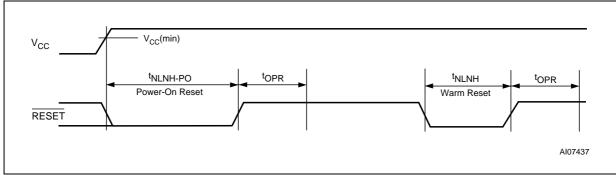

| RESET TIMING AND DEVICE STATUS AT RESET                | 126 |

| Warm RESET                                             | 126 |

| I/O Pin, Register and PLD Status at RESET              | 126 |

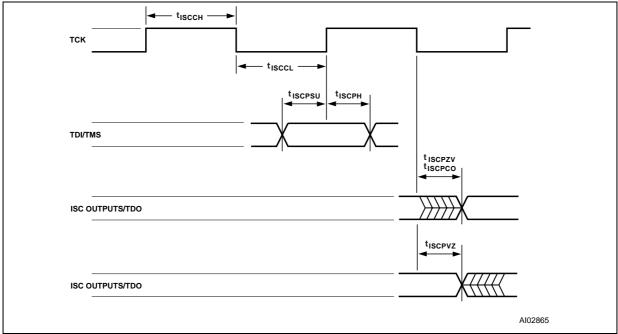

| PROGRAMMING IN-CIRCUIT USING THE JTAG SERIAL INTERFACE | 127 |

| Standard JTAG Signals                                  | 127 |

| JTAG Extensions                                        | 127 |

| Security and Flash memory Protection                   | 127 |

| INITIAL DELIVERY STATE                                 | 127 |

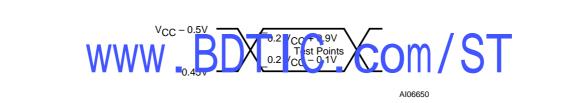

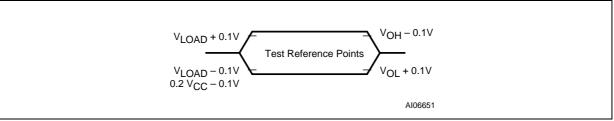

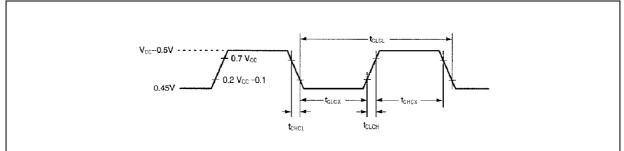

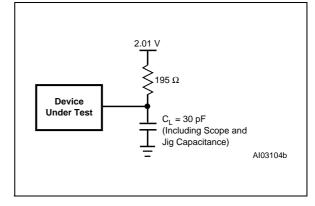

| AC/DC PARAMETERS                                       | 128 |

| MAXIMUM RATING                                         | 130 |

| EMC CHARACTERISTICS                                    | 131 |

| Functional EMS (Electromagnetic Susceptibility)        | 131 |

| Designing Hardened Software To Avoid Noise Problems    | 131 |

| Absolute Maximum Ratings (Electrical Sensitivity)      | 131 |

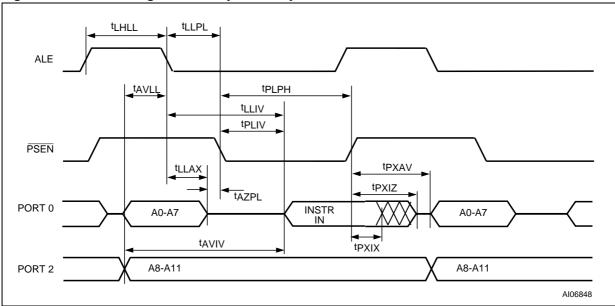

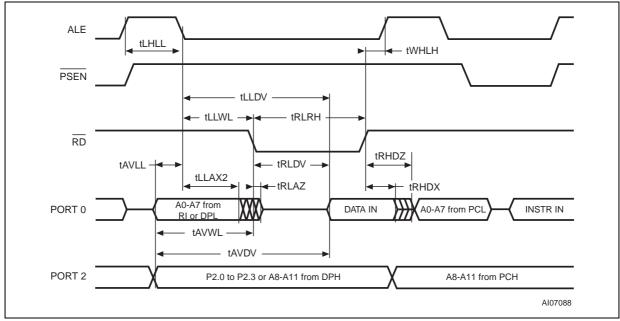

| DC AND AC PARAMETERS                                   | 133 |

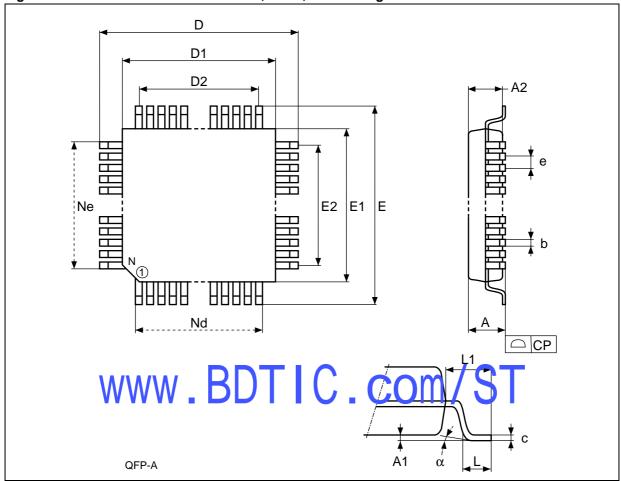

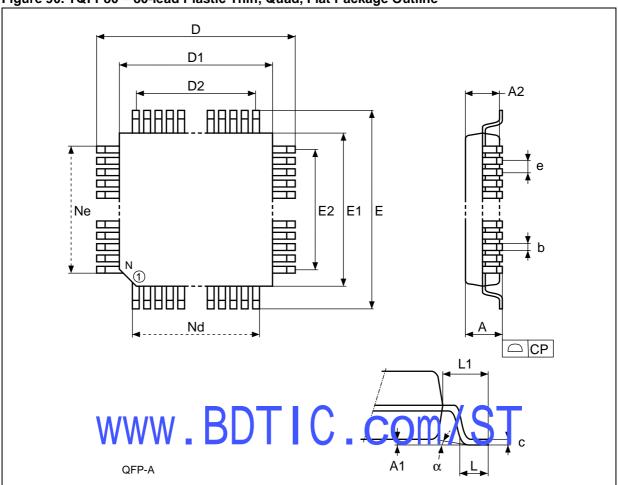

| PACKAGE MECHANICAL INFORMATION                         |     |