#### **General Description**

The MAX3950 deserializer is ideal for converting 10Gbps serial data to 16-bit-wide, 622Mbps parallel data in SDH/SONET and DWDM applications. Operating from a single +3.3V supply, this device accepts CML serial clock and data inputs and delivers low-voltage differential-signal (LVDS) clock and data outputs for interfacing with high-speed digital circuitry.

The MAX3950 is available in the extended temperature range (-40°C to +85°C) in a 68-pin QFN package. The typical power dissipation is 900mW.

#### **Applications**

SONET/OC-192 SDH/STM-64 Transmission Systems Add/Drop Multiplexers **Broadband Digital Cross-Connects**

#### Features

- ♦ Supports Serial Data Rates Up to 10.7Gbps

- ♦ 10Gbps/10.7Gbps Serial to 622Mbps/667Mbps **Parallel Conversion**

- ♦ Single +3.3V Supply

- 900mW Operating Power

- ♦ CML Serial Clock and Data Inputs

- **♦ LVDS Parallel Clock and Data Outputs**

- ◆ -40°C to +85°C Operating Temperature

#### **Ordering Information**

| PART       | TEMP RANGE     | PIN-PACKAGE |  |

|------------|----------------|-------------|--|

| MAX3950EGK | -40°C to +85°C | 68 QFN      |  |

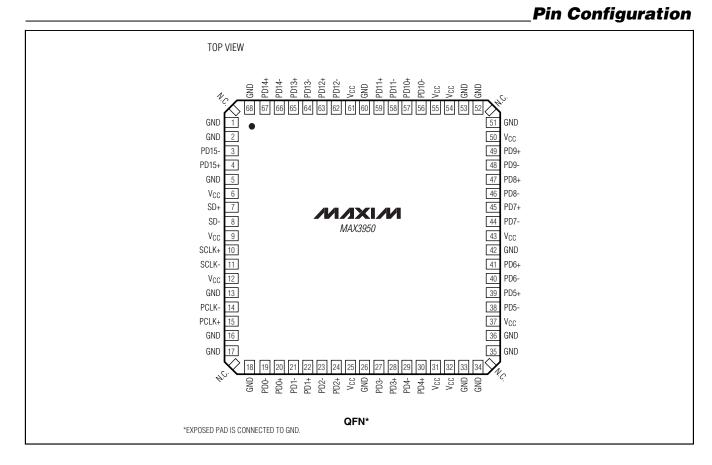

Pin Configuration appears at the end of data sheet.

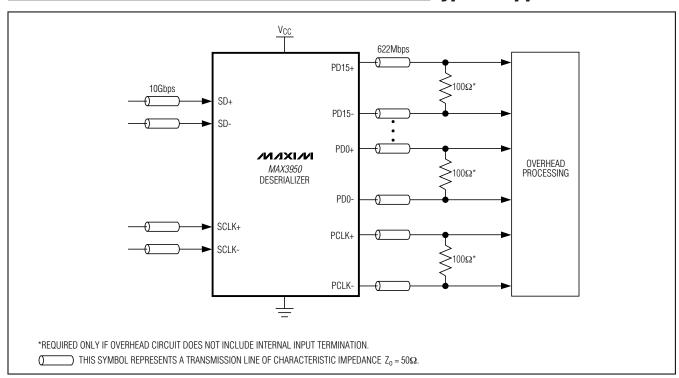

#### **Typical Application Circuit**

#### MIXIM

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

#### **ABSOLUTE MAXIMUM RATINGS**

| Positive Supply Voltage (VCC)0.5V to +5.0V                                  | Ο  |

|-----------------------------------------------------------------------------|----|

| CML Input Voltage Level(V <sub>CC</sub> - 0.8V) to (V <sub>CC</sub> + 0.5V) | St |

| LVDS Output Voltage Level0.5V to (V <sub>CC</sub> + 0.5V)                   | Le |

| Continuous Power Dissipation (T <sub>A</sub> = +85°C)                       |    |

| 68-Lead QFN (derate 43.5mW/°C above +85°C)2800mW                            |    |

| Operating Temperature Range       | 40°C to +85°C  |

|-----------------------------------|----------------|

| Storage Temperature Range         | 55°C to +150°C |

| Lead Temperature (soldering, 10s) |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### DC ELECTRICAL CHARACTERISTICS

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, \text{ differential loads} = 100\Omega \pm 1\%, T_A = -40 ^{\circ}\text{C to } +85 ^{\circ}\text{C}, \text{ unless otherwise noted. Typical values are at } V_{CC} = +3.3 \text{V}, T_A = +25 ^{\circ}\text{C}.)$

| PARAMETER                                                                   | SYMBOL            | CONDITIONS      | MIN                   | TYP | MAX                   | UNITS             |  |

|-----------------------------------------------------------------------------|-------------------|-----------------|-----------------------|-----|-----------------------|-------------------|--|

| Supply Current                                                              | Icc               |                 |                       | 270 | 350                   | mA                |  |

| CML INPUTS (SD±, SCLK±)                                                     |                   |                 |                       |     |                       |                   |  |

| Differential Input Voltage Swing                                            | V <sub>ID</sub>   |                 | 400                   |     | 1200                  | mV <sub>P-P</sub> |  |

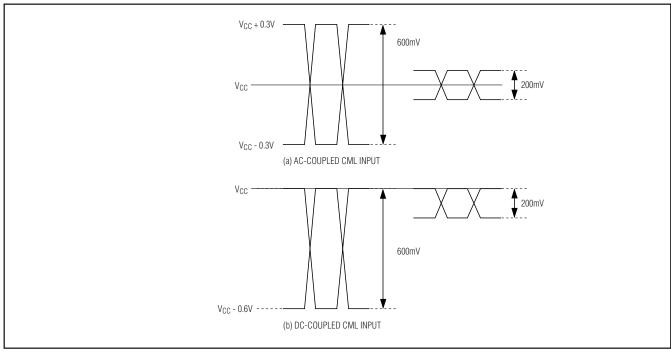

| Single-Ended Input Voltage<br>Range                                         | VIS               | Figure 1        | V <sub>CC</sub> - 0.6 |     | V <sub>CC</sub> + 0.3 | V                 |  |

| Input Termination to V <sub>CC</sub>                                        | RIN               |                 | 42.5                  | 50  | 57.5                  | Ω                 |  |

| LVDS OUTPUT SPECIFICATION                                                   | (PD[15.0] ±,      | , PCLK±)        |                       |     |                       |                   |  |

| Output High Voltage                                                         | VoH               |                 |                       |     | 1.375                 | V                 |  |

| Output Low Voltage                                                          | V <sub>OL</sub>   |                 | 1.025                 |     |                       | V                 |  |

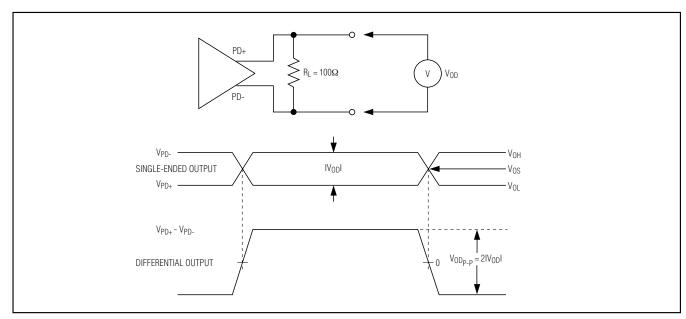

| Differential Output Voltage                                                 | V <sub>OD</sub>   | Figure 2        | 150                   |     | 250                   | mV                |  |

| Change in Magnitude of<br>Differential Output for<br>Complementary States   | Δ V <sub>OD</sub> |                 |                       |     | 25                    | mV                |  |

| Offset Output Voltage                                                       |                   |                 | 1.15                  |     | 1.25                  | V                 |  |

| Change in Magnitude of<br>Output Offset Voltage for<br>Complementary States | Δ V <sub>OS</sub> |                 |                       |     | 25                    | mV                |  |

| Differential Output Impedance                                               |                   |                 | 80                    |     | 120                   | Ω                 |  |

| 0. 1. 1. 0                                                                  |                   | Short together  |                       |     | 12                    | νοο Λ             |  |

| Output Current                                                              |                   | Short to ground |                       |     | 24                    | - mA              |  |

#### **AC ELECTRICAL CHARACTERISTICS**

$(V_{CC} = +3.0 \text{V to } +3.6 \text{V}, \text{ differential loads} = 100\Omega \pm 1\%, T_A = -40^{\circ}\text{C to } +85^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $V_{CC} = +3.3 \text{V}, T_A = +25^{\circ}\text{C}.)$  (Note 1)

| PARAMETER                       | SYMBOL          | CONDITIONS            | MIN  | TYP | MAX  | UNITS |

|---------------------------------|-----------------|-----------------------|------|-----|------|-------|

| Serial Input Data Rate          |                 |                       |      | 10  |      | Gbps  |

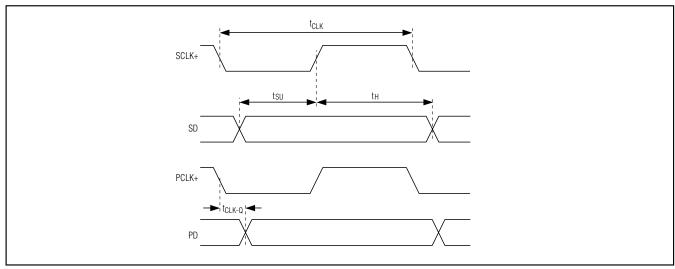

| Serial Data Setup Time          | tsu             |                       | 25   |     |      | ps    |

| Serial Data Hold Time           | tH              |                       | 25   |     |      | ps    |

| Parallel Output Data Rate       |                 |                       |      | 622 |      | Mbps  |

| Parallel Output Clock Frequency |                 |                       |      | 622 |      | MHz   |

| Parallel Clock-to-Q Delay       | tCLK-Q          | (Note 2)              | -200 |     | +200 | ps    |

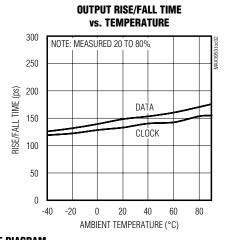

| LVDS Output Rise/Fall Time      |                 | 20% to 80%            |      |     | 300  | ps    |

| LVDS Differential Skew          | tskew1          | Any differential pair |      |     | 65   | ps    |

| LVDS Channel-to-Channel Skew    | tskew2          | PD[150]±              |      | 200 |      | ps    |

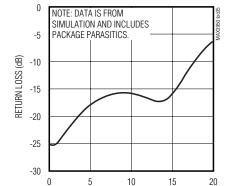

|                                 |                 | 100kHz ≤ f ≤ 5GHz     |      | 17  |      |       |

| Input Return Loss               | S <sub>11</sub> | 5GHz ≤ f ≤ 10GHz      |      | 14  |      | dB    |

|                                 |                 | 10GHz ≤ f ≤ 15GHz     |      | 11  |      |       |

Note 1: AC specifications are guaranteed by design and characterization.

Note 2: Relative to the falling edge of PCLK+. See Figure 3.

Figure 1. Input Amplitude

Figure 2. Driver Output Levels

Figure 3. Timing Parameters

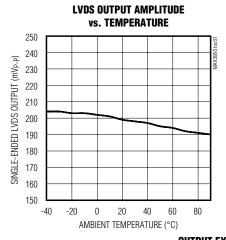

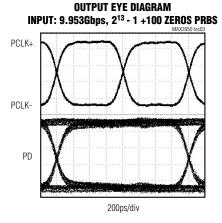

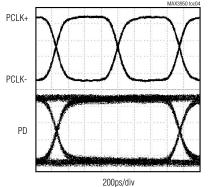

#### **Typical Operating Characteristics**

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

## OUTPUT EYE DIAGRAM INPUT: 10.7Gbps, 2<sup>13</sup> - 1 +100 ZEROS PRBS

FREQUENCY (GHz)

**INPUT RETURN LOSS**

#### **Pin Description**

| PIN                                                        | NAME  | FUNCTION                                                |  |

|------------------------------------------------------------|-------|---------------------------------------------------------|--|

| 1, 2, 5, 13, 16, 17, 18, 26, 33–36, 42, 51, 52, 53, 60, 68 | GND   | Ground                                                  |  |

| 6, 9, 12, 25, 31, 32, 37, 43, 50, 54, 55, 61               | Vcc   | Positive Power Supply                                   |  |

| 7                                                          | SD+   | Positive Data Input. 9.953Gbps serial data stream, CML. |  |

| 8                                                          | SD-   | Negative Data Input. 9.953Gbps serial data stream, CML. |  |

| 10                                                         | SCLK+ | Positive Serial Clock Input. 9.953GHz, CML.             |  |

| 11                                                         | SCLK- | Negative Serial Clock Input. 9.953GHz, CML.             |  |

| 14                                                         | PCLK- | Negative Parallel Clock Output, 622.08MHz, LVDS.        |  |

MIXIM

#### Pin Description (continued)

| PIN                                                                 | NAME             | FUNCTION                                                                                                                                  |

|---------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 15                                                                  | PCLK+            | Positive Parallel Clock Output, 622.08MHz, LVDS.                                                                                          |

| 19, 21, 23, 27, 29, 38, 40, 44, 46, 48, 56, 58, 62, 64, 66, 3       | PD0- to<br>PD15- | Negative Parallel Data Output, 622.08Mbps, LVDS.                                                                                          |

| 20, 22, 24, 28, 30, 39,<br>41, 45, 47, 49, 57, 59,<br>63, 65, 67, 4 | PD0+ to<br>PD15+ | Positive Parallel Data Output, 622.08Mbps, LVDS.                                                                                          |

| EP                                                                  | Exposed<br>Pad   | Ground. This must be soldered to the circuit board ground for proper thermal and electrical operation. See <i>Layout Considerations</i> . |

| СР                                                                  | Corner<br>Pins   | N.C. Not Connected. Ensure that the solder mask is located below them so that unintentional connections do not occur.                     |

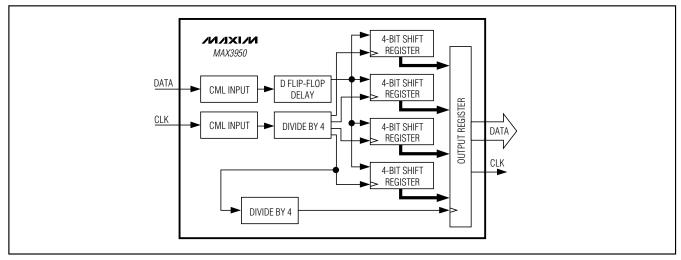

Figure 4. Functional Block Diagram

#### Detailed Description

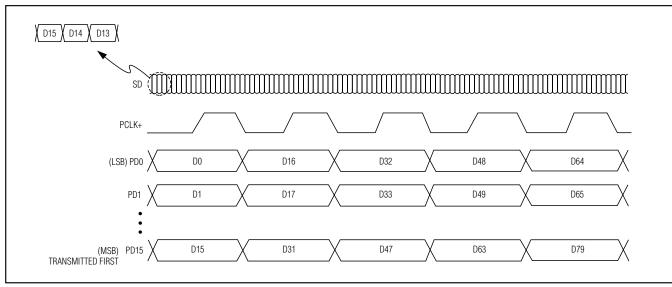

The MAX3950 deserializer implements a shift-register-based demultiplexer to convert 9.953Gbps serial data to 16-bit-wide, 622.08Mbps parallel data (Figure 4). The allocation of the serial input bits to the parallel LVDS outputs is displayed in Figure 5.

#### \_Applications Information

## Low-Voltage Differential-Signal Outputs

The MAX3950 features LVDS outputs for interfacing with high-speed digital circuitry. This LVDS implementation is based on the IEEE 1596.3 LVDS reduced-range link specification and is compatible with OIF 1999.102.

Note that the PCLK polarity on the MAX3950 is inverted relative to OIF 1999.102, so that PCLK+ is equivalent to RXCLK\_N and PCLK- is equivalent to RXCLK\_P.

The MAX3950 uses 300mVp-p to 500mVp-p differential low-voltage swings to achieve fast transition times, minimize power dissipation, and improve noise immunity. The parallel clock and data LVDS outputs (PCLK+, PCLK-, PD\_+, PD\_-) require 100 $\Omega$  differential DC termination between the inverting and noninverting outputs for proper operation. Do not terminate these outputs to ground. For more information on interfacing with the LVDS outputs, refer to Maxim Application Note  $\it{HFAN-1.0:}$  Interfacing Between CML, PECL, and LVDS.

Figure 5. Timing Diagram

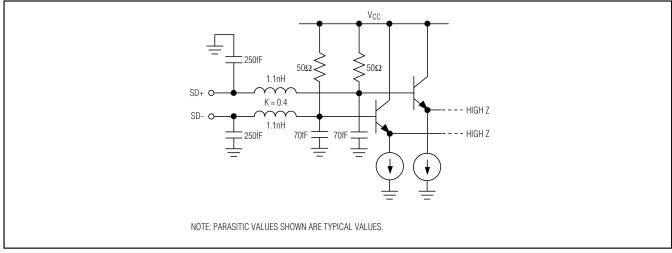

Figure 6. CML Input Model

#### **Current Mode Logic (CML) Inputs**

The differential serial inputs to the MAX3950 are CML and have an input impedance of  $50\Omega$  on each of the complementary inputs. For more information on interfacing with the CML inputs, refer to Maxim Application Note *HFAN-1.0: Interfacing Between CML, PECL, and LVDS.*

#### **Interface Models**

Figures 6 and 7 show the typical input/output models for the MAX3950 deserializer.

#### **Layout Considerations**

For best performance, use good high-frequency layout techniques. Filter voltage supplies, keep ground connections short, and use multiple vias where possible. Use controlled-impedance transmission lines to interface with the MAX3950's high-speed inputs and outputs. Place power-supply decoupling as close to  $V_{\rm CC}$  as possible. To reduce feedthrough, isolate the input signals from the output signals.

# V<sub>CC</sub> PD\_+ PD\_PD\_MAX3950

Figure 7. LVDS Output Model

#### **Chip Information**

TRANSISTOR COUNT: 4800

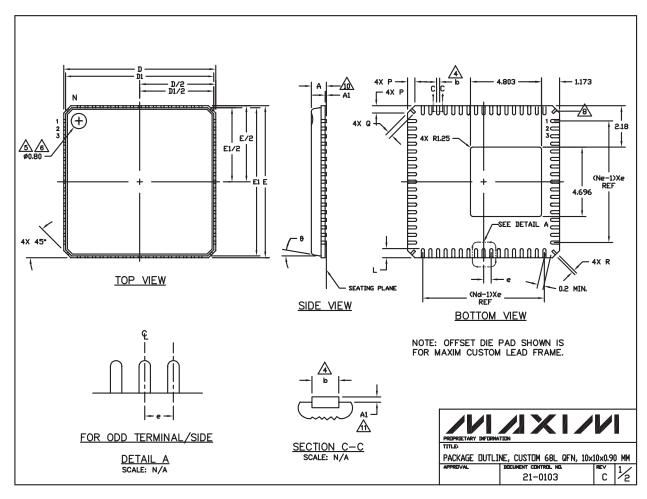

#### Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

MIXIM

#### **Package Information (continued)**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

#### NOTES:

- 1. DIE THICKNESS ALLOWABLE IS .012 INCHES MAXIMUM.

- 2. DIMENSIONING & TOLERANCES CONFORM TO ASME Y14.5M. 1994.

N IS THE NUMBER OF TERMINALS.

No IS THE NUMBER OF TERMINALS IN X-DIRECTION &

No IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

4. DIMENSION 6 APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20mm AND 0.25mm FROM TERMINAL.

THE PIN #1 IDENTIFIER MUST BE LOCATED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR OTHER FEATURE OF PACKAGE BODY.

6. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

7. ALL DIMENSIONS ARE IN MILLIMETERS.

8. THE SHAPES SHOWN AT FOUR CORNERS ARE CONNECTED TO DIE PAD.

9. PACKAGE WARPAGE MAX 0.10mm.

APPLIED FOR EXPOSED PAD AND TERMINALS.

11 APPLIED ONLY FOR TERMINALS.

12. CUSTOM LEAD FRAME WITH OFFSET DIE PAD: REFER TO MAXIM 24-0718 (G6800-1F).

| S<br>Y | COMMON     |                |      | ш                |  |  |

|--------|------------|----------------|------|------------------|--|--|

| M H    | DIMENSIONS |                |      | No.              |  |  |

| ">BBOL | MIN.       | NOM.           | MAX. | No <sub>TE</sub> |  |  |

| Α      | _          | 0.90           | 1.00 | Ш                |  |  |

| A1     | 0.00       | 0.01           | 0.05 | 11               |  |  |

| ь      | 0.18       | 0.23           | 0.30 | 4                |  |  |

| D      |            | 10.00BSC       |      |                  |  |  |

| D1     |            | 9.75BSC        |      |                  |  |  |

| Ε      |            | 10.00BSC       |      |                  |  |  |

| E1     |            | 9.75BSC        |      |                  |  |  |

| N      | 68         |                |      |                  |  |  |

| Nd     |            | 17             |      |                  |  |  |

| Ne     |            | 17             |      |                  |  |  |

| е      | 0.50 BSC   |                |      |                  |  |  |

| L      | 0.50       | 0.50 0.60 0.75 |      |                  |  |  |

| θ      |            |                |      |                  |  |  |

| Р      | 0.24       | 0.42           | 0.60 |                  |  |  |

| Q      | 0.30       | 0.30 0.40 0.65 |      |                  |  |  |

| R      | 0.13       |                |      |                  |  |  |

#### **Revision History**

Rev 0; 11/00: Initial data sheet release.

Rev 1; 12/02: Page 6, Pin Configuration: Corner Pins changed from Ground to N.C.; page 8, Pin Configuration:

Changed GND corner pins to N.C.

Rev 2; 7/06: Page 1: Removed future products from

Typical Application Circuit.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

10 \_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2006 Maxim Integrated Products

is a registered trademark of Maxim Integrated Products.