## BDTIC www.bdtic.com/ATMEL

## **Features**

- Serial Peripheral Interface (SPI) Compatible

- Supports SPI Modes 0 (0,0) and 3 (1,1)

- Data Sheet Describes Mode 0 Operation

- Low-voltage Operation

- 1.8 (V<sub>cc</sub> = 1.8V to 5.5V)

- 20 MHz Clock Rate (4.5 5.5V)

- 128-byte Page Mode and Byte Write Operation Supported

- Block Write Protection

- Protect 1/4, 1/2, or Entire Array

- Write Protect (WP) Pin and Write Disable Instructions for Both Hardware and Software Data Protection

- Self-timed Write Cycle (5 ms Max)

- High-reliability

- Endurance: 1 Million Write Cycles

- Data Retention: >40 Years

- Lead-free/Halogen-free Devices

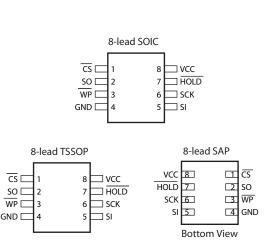

- 8-lead JEDEC SOIC, 8-lead TSSOP and 8-lead SAP Packages

- Die Sales: Wafer Form, Waffle Pack, and Bumped Die

## Description

Table 0-1.

The AT25512 provides 524,288 bits of serial electrically-erasable programmable read only memory (EEPROM) organized as 65,536 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The devices are available in space saving 8-lead JEDEC SOIC, 8-lead TSSOP and 8-lead SAP packages. In addition, the entire family is available in 1.8V (1.8V to 5.5V) versions.

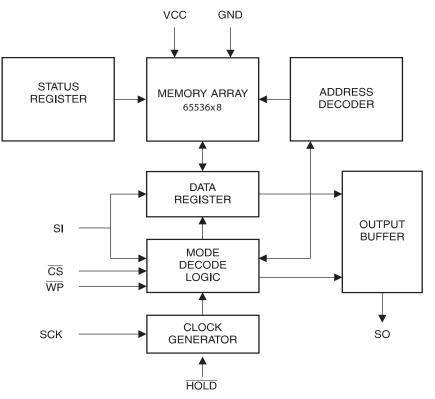

The AT25512 is enabled through the Chip Select pin  $(\overline{CS})$  and accessed via a 3-wire interface consisting of Serial Data Input (SI), Serial Data Output (SO), and Serial Clock (SCK). All programming cycles are completely self-timed, and no separate Erase cycle is required before Write.

| Pin Name | Function              |

|----------|-----------------------|

| CS       | Chip Select           |

| SCK      | Serial Data Clock     |

| SI       | Serial Data Input     |

| SO       | Serial Data Output    |

| GND      | Ground                |

| VCC      | Power Supply          |

| WP       | Write Protect         |

| HOLD     | Suspends Serial Input |

| NC       | No Connect            |

Pin Configurations

http://www.]

DTIC.com/ATM

# SPI Serial EEPROM

512K (65,536 x 8)

# AT25512

Block Write protection is enabled by programming the status register with top ¼, top ½ or entire array of write protection. Separate Program Enable and Program Disable instructions are provided for additional data protection. Hardware data protection is provided via the WP pin to protect against inadvertent write attempts to the status register. The HOLD pin may be used to suspend any serial communication without resetting the serial sequence.

## 1. Absolute Maximum Ratings\*

| Operating Temperature55°C to +125°C                        | * |

|------------------------------------------------------------|---|

| Storage Temperature65°C to +150°C                          |   |

| Voltage on Any Pin<br>with Respect to Ground–1.0V to +7.0V |   |

| Maximum Operating Voltage 6.25V                            |   |

| DC Output Current 5.0 mA                                   |   |

\*NOTICE: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Figure 1-1. Block Diagram

http://www.BDTIC.com/AT

AT25512

2

### Table 1-1.Pin Capacitance<sup>(1)</sup>

Applicable over recommended operating range from  $T_A = 25^{\circ}C$ , f = 1.0 MHz,  $V_{CC} = +5.0V$  (unless otherwise noted)

| Symbol           | Test Conditions                           | Max | Units | Conditions            |

|------------------|-------------------------------------------|-----|-------|-----------------------|

| C <sub>OUT</sub> | Output Capacitance (SO)                   | 8   | pF    | V <sub>OUT</sub> = 0V |

| C <sub>IN</sub>  | Input Capacitance (CS, SCK, SI, WP, HOLD) | 6   | pF    | $V_{IN} = 0V$         |

Note: 1. This parameter is characterized and is not 100% tested.

### Table 1-2. DC Characteristics

Applicable over recommended operating range from  $T_{AI} = -40^{\circ}C$  to +85°C,  $V_{CC} = +1.8V$  to +5.5V,  $V_{CC} = +1.8V$  to +5.5V(unless otherwise noted)

| Symbol                         | Parameter           | Test Condition                                        |                                                            | Min                  | Тур | Max                   | Units |

|--------------------------------|---------------------|-------------------------------------------------------|------------------------------------------------------------|----------------------|-----|-----------------------|-------|

| V <sub>CC1</sub>               | Supply Voltage      |                                                       |                                                            | 1.8                  |     | 5.5                   | V     |

| V <sub>CC2</sub>               | Supply Voltage      |                                                       |                                                            | 2.7                  |     | 5.5                   | V     |

| V <sub>CC3</sub>               | Supply Voltage      |                                                       |                                                            | 4.5                  |     | 5.5                   | V     |

| I <sub>CC1</sub>               | Supply Current      | V <sub>CC</sub> = 5.0V at 20 MI<br>Read               | Hz, SO = Open,                                             |                      | 9.0 | 10.0                  | mA    |

| I <sub>CC2</sub>               | Supply Current      | V <sub>CC</sub> = 5.0V at 10 MI<br>SO = Open, Read, V |                                                            |                      | 5.0 | 7.0                   | mA    |

| I <sub>CC3</sub>               | Supply Current      |                                                       | V <sub>CC</sub> = 5.0V at 1 MHz,<br>SO = Open, Read, Write |                      |     | 3.5                   | mA    |

| I <sub>SB1</sub>               | Standby Current     | $V_{CC} = 1.8V, \overline{CS} = V_{CC}$               | $V_{CC}$ = 1.8V, $\overline{CS}$ = $V_{CC}$                |                      |     | 3.0                   | μA    |

| I <sub>SB2</sub>               | Standby Current     | $V_{CC} = 2.7V, \overline{CS} = V_{CC}$               |                                                            | 0.5                  | 3.0 | μA                    |       |

| I <sub>SB3</sub>               | Standby Current     | $V_{CC} = 5.0V, \overline{CS} = V_{CC}$               | $V_{CC} = 5.0V, \overline{CS} = V_{CC}$                    |                      | 2.0 | 5.0                   | μA    |

| I <sub>IL</sub>                | Input Leakage       | $V_{IN}$ = 0V to $V_{CC}$                             |                                                            | -3.0                 |     | 3.0                   | μA    |

| I <sub>OL</sub>                | Output Leakage      | $V_{IN} = 0V$ to $V_{CC}$ , $T_{AC}$                  | c = 0.C to $70.C$                                          | -3.0                 |     | 3.0                   | μA    |

| V <sub>IL</sub> <sup>(1)</sup> | Input Low-voltage   |                                                       |                                                            | -1.0                 |     | V <sub>CC</sub> x 0.3 | V     |

| V <sub>IH</sub> <sup>(1)</sup> | Input High-voltage  |                                                       |                                                            |                      |     | V <sub>CC</sub> + 0.5 | V     |

| V <sub>OL1</sub>               | Output Low-voltage  |                                                       | I <sub>OL</sub> = 3.0 mA                                   |                      |     | 0.4                   | V     |

| V <sub>OH1</sub>               | Output High-voltage | $3.6 \le V_{CC} \le 5.5V$                             | I <sub>OH</sub> = -1.6 mA                                  | V <sub>CC</sub> –0.8 |     |                       | V     |

| V <sub>OL2</sub>               | Output Low-voltage  |                                                       | I <sub>OL</sub> = 0.15 mA                                  |                      |     | 0.2                   | V     |

| V <sub>OH2</sub>               | Output High-voltage | $1.8V \le V_{CC} \le 3.6V$                            | I <sub>OH</sub> = -100 μA                                  | V <sub>CC</sub> –0.2 |     |                       | V     |

p://www.BDTIC.com/ATMEL

Note: 1.  $V_{IL}$  min and  $V_{IH}$  max are reference only and are not tested.

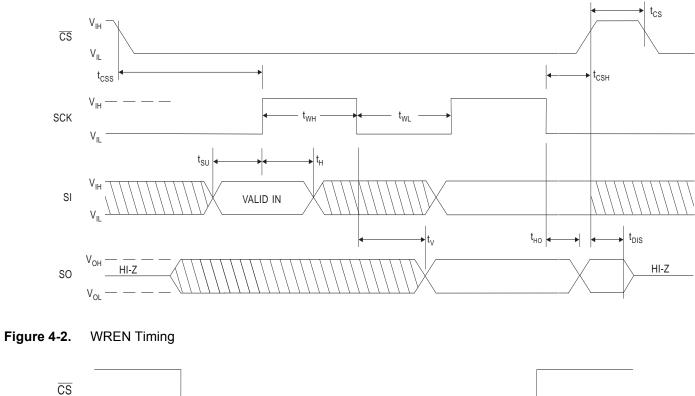

### Table 1-3. AC Characteristics

Applicable over recommended operating range from  $T_{AI} = -40 \cdot C$  to + 85·C,  $V_{CC}$  = As Specified, CL = 1 TTL Gate and 30 pF (unless otherwise noted)

| Symbol           | Parameter            | Voltage                       | Min               | Max             | Units |

|------------------|----------------------|-------------------------------|-------------------|-----------------|-------|

| f <sub>SCK</sub> | SCK Clock Frequency  | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 0<br>0<br>0       | 20<br>10<br>5   | MHz   |

| t <sub>RI</sub>  | Input Rise Time      | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 |                   | 2<br>2<br>2     | μs    |

| t <sub>FI</sub>  | Input Fall Time      | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 |                   | 2<br>2<br>2     | μs    |

| t <sub>wH</sub>  | SCK High Time        | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 20<br>40<br>80    |                 | ns    |

| t <sub>wL</sub>  | SCK Low Time         | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 20<br>40<br>80    |                 | ns    |

| t <sub>cs</sub>  | CS High Time         | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 100<br>100<br>200 |                 | ns    |

| t <sub>css</sub> | CS Setup Time        | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 100<br>100<br>200 |                 | ns    |

| t <sub>CSH</sub> | CS Hold Time         | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 100<br>100<br>200 |                 | ns    |

| t <sub>su</sub>  | Data In Setup Time   | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 5<br>10<br>20     |                 | ns    |

| t <sub>H</sub>   | Data In Hold Time    | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 5<br>10<br>20     |                 | ns    |

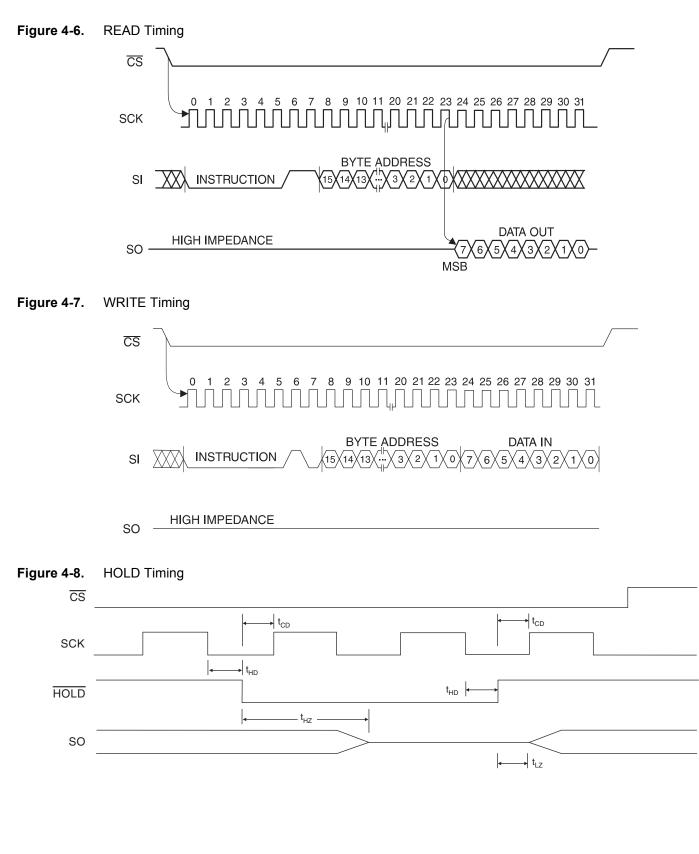

| t <sub>HD</sub>  | Hold Setup Time      | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 5<br>10<br>20     |                 | ns    |

| t <sub>CD</sub>  | Hold Hold Time       | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 5<br>10<br>20     |                 | ns    |

| t <sub>V</sub>   | Output Valid         | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 0<br>0<br>0       | 20<br>40<br>80  | ns    |

| t <sub>HO</sub>  | Output Hold Time     | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 0<br>0<br>0       |                 | ns    |

| t <sub>LZ</sub>  | Hold to Output Low Z | 4.5–5.5<br>2.7–5.5<br>1.8–5.5 | 0<br>0<br>0       | 25<br>50<br>100 | ns    |

AT25512 🛑

4

5165F-SEEPR-3/09

http://www.BDTIC.com/ATMEL

Table 1-3.

AC Characteristics (Continued)

Applicable over recommended operating range from  $T_{AI} = -40 \cdot C$  to + 85·C,  $V_{CC}$  = As Specified, CL = 1 TTL Gate and 30 pF (unless otherwise noted)

| Symbol                   | Parameter             | Voltage | Min | Мах | Units        |

|--------------------------|-----------------------|---------|-----|-----|--------------|

|                          |                       | 4.5-5.5 |     | 25  |              |

| t <sub>HZ</sub>          | Hold to Output High Z | 2.7–5.5 |     | 50  | ns           |

|                          |                       | 1.8–5.5 |     | 100 |              |

|                          |                       | 4.5–5.5 |     | 25  |              |

| t <sub>DIS</sub>         | Output Disable Time   | 2.7–5.5 |     | 50  | ns           |

|                          |                       | 1.8–5.5 |     | 100 |              |

|                          |                       | 4.5–5.5 |     | 5   |              |

| t <sub>wc</sub>          | Write Cycle Time      | 2.7–5.5 |     | 5   | ms           |

|                          | -                     | 1.8–5.5 |     | 5   |              |

| Endurance <sup>(1)</sup> | 5.0V, 25·C, Page Mode |         | 1M  |     | Write Cycles |

Notes: 1. This parameter is characterized and is not 100% tested. Contact Atmel for further information.

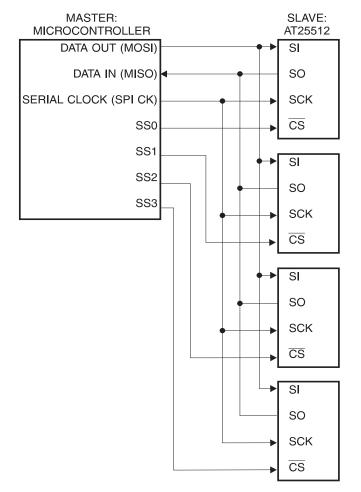

## 2. Serial Interface Description

**MASTER:** The device that generates the serial clock.

**SLAVE:** Because the serial clock pin (SCK) is always an input, the AT25512 always operates as a slave.

**TRANSMITTER/RECEIVER:** The AT25512 has separate pins designated for data transmission (SO) and reception (SI).

MSB: The Most Significant Bit (MSB) is the first bit transmitted and received.

**SERIAL OP-CODE:** After the device is selected with CS going low, the first byte will be received. This byte contains the op-code that defines the operations to be performed.

**INVALID OP-CODE:** If an invalid op-code is received, no data will be shifted into the AT25512, and the serial output pin (SO) will remain in a high impedance state until the falling edge of  $\overline{CS}$  is detected again. This will reinitialize the serial communication.

**CHIP SELECT:** The AT25512 is selected when the  $\overline{CS}$  pin is low. When the device is not selected, data will not be accepted via the SI pin, and the serial output pin (SO) will remain in a high impedance state.

**HOLD**: The HOLD pin is used in conjunction with the  $\overline{CS}$  pin to select the AT25512. When the device is selected and a serial sequence is underway, HOLD can be used to pause the serial communication with the master device without resetting the serial sequence. To pause, the HOLD pin must be brought low while the SCK pin is low. To resume serial communication, the HOLD pin is brought high while the SCK pin is low (SCK may still toggle during HOLD). Inputs to the SI pin will be ignored while the SO pin is in the high impedance state.

**WRITE PROTECT:** The write protect pin ( $\overline{WP}$ ) will allow normal read/write operations when held high. When the  $\overline{WP}$  pin is brought low and WPEN bit is "1", all write operations to the status register are inhibited.  $\overline{WP}$  going low while  $\overline{CS}$  is still low will interrupt a write to the status register. If the internal write cycle has already been initiated,  $\overline{WP}$  going low will have no effect on any write operation to the status register. The  $\overline{WP}$  pin function is blocked when the WPEN bit in the status register is "0". This will allow the user to install the AT25512 in a system with the  $\overline{WP}$  pin tied to

n://www.]

ground and still be able to write to the status register. All  $\overline{\text{WP}}$  pin functions are enabled when the WPEN bit is set to "1".

#### Figure 2-1. SPI Serial Interface

http://www.BDTIC.com/ATM

## 3. Functional Description

The AT25512 is designed to interface directly with the synchronous serial peripheral interface (SPI) of the 6800 type series of microcontrollers.

The AT25512 utilizes an 8-bit instruction register. The list of instructions and their operation codes are contained in see Table 4-3. All instructions, addresses, and data are transferred with the MSB first and start with a high-to-low  $\overline{CS}$  transition.

AT25512

7

| Table 3-1.         Instruction Set for the A125512 |                    |                             |  |  |  |

|----------------------------------------------------|--------------------|-----------------------------|--|--|--|

| Instruction Name                                   | Instruction Format | Operation                   |  |  |  |

| WREN                                               | 0000 X110          | Set Write Enable Latch      |  |  |  |

| WRDI                                               | 0000 X100          | Reset Write Enable Latch    |  |  |  |

| RDSR                                               | 0000 X101          | Read Status Register        |  |  |  |

| WRSR                                               | 0000 X001          | Write Status Register       |  |  |  |

| READ                                               | 0000 X011          | Read Data from Memory Array |  |  |  |

| WRITE                                              | 0000 X010          | Write Data to Memory Array  |  |  |  |

0 - 1 ( - - 1 - -

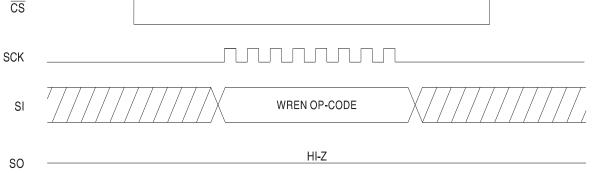

WRITE ENABLE (WREN): The device will power-up in the write disable state when  $V_{\text{CC}}$  is applied. All programming instructions must therefore be preceded by a Write Enable instruction.

WRITE DISABLE (WRDI): To protect the device against inadvertent writes, the Write Disable instruction disables all programming modes. The WRDI instruction is independent of the status of the  $\overline{WP}$  pin.

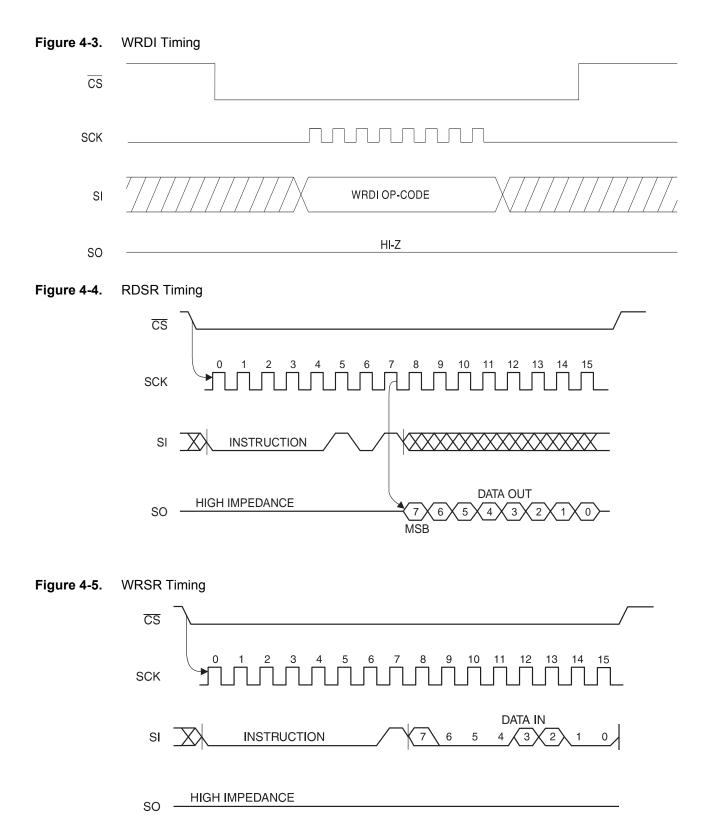

**READ STATUS REGISTER (RDSR):** The Read Status Register instruction provides access to the status register. The Ready/Busy and Write Enable status of the device can be determined by the RDSR instruction. Similarly, the Block Write Protection bits indicate the extent of protection employed. These bits are set by using the WRSR instruction.

Table 3-2. Status Register Format

|       |       | 5     |       |       |       |       |       |

|-------|-------|-------|-------|-------|-------|-------|-------|

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| WPEN  | Х     | Х     | х     | BP1   | BP0   | WEN   | RDY   |

Table 3-3. Read Status Register Bit Definition

| Bit                                                                                                                          | Definition                                                                                                               |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Bit 0 (RDY)                                                                                                                  | Bit 0 = "0" ( $\overline{RDY}$ ) indicates the device is ready.<br>Bit 0 = "1" indicates the write cycle is in progress. |  |  |  |  |

| Bit 1 (WEN)Bit 1 = 0 indicates the device <i>is not</i> write enabled. Bit 1 = "1" indicates<br>the device is write enabled. |                                                                                                                          |  |  |  |  |

| Bit 2 (BP0)                                                                                                                  | See Table 3-4 on page 8.                                                                                                 |  |  |  |  |

| Bit 3 (BP1)                                                                                                                  | Bit 3 (BP1) See Table 3-4 on page 8.                                                                                     |  |  |  |  |

| Bits 4 – 6 are 0s whe                                                                                                        | Bits 4 – 6 are 0s when device is not in an internal write cycle.                                                         |  |  |  |  |

| Bit 7 (WPEN) See Table 3-5 on page 8.                                                                                        |                                                                                                                          |  |  |  |  |

| Bits 0 – 7 are "1"s du                                                                                                       | iring an internal write cycle.                                                                                           |  |  |  |  |

WRITE STATUS REGISTER (WRSR): The WRSR instruction allows the user to select one of four levels of protection. The AT25512 is divided into four array segments. Top quarter (1/4), top half (1/2), or all of the memory segments can be protected. Any of the data within any selected segment will therefore be read only. The block write protection levels and corresponding status register control bits are shown in Table 3-4.

The three bits, BP0, BP1, and WPEN are nonvolatile cells that have the same properties and functions as the regular memory cells (e.g. WREN,  $t_{WC}$ , RDSR).

|        | Status Re | gister Bits | Array Addresses<br>Protected |

|--------|-----------|-------------|------------------------------|

| Level  | BP1       | BP0         | AT25512                      |

| 0      | 0         | 0           | None                         |

| 1(1/4) | 0         | 1           | C000 – FFFF                  |

| 2(1/2) | 1         | 0           | 8000 – FFFF                  |

| 3(All) | 1         | 1           | 0000 – FFFF                  |

Table 3-4. Block Write Protect Bits

The WRSR instruction also allows the user to enable or disable the write protect (WP) pin through the use of the write protect enable (WPEN) bit. Hardware write protection is enabled when the  $\overline{\text{WP}}$  pin is low and the WPEN bit is "1". Hardware write protection is disabled when *either* the  $\overline{\text{WP}}$  pin is high or the WPEN bit is "0". When the device is hardware write protected, writes to the Status Register, including the Block Protect bits and the WPEN bit, and the block-protected sections in the memory array are disabled. Writes are only allowed to sections of the memory which are not block-protected.

**NOTE:** When the WPEN bit is hardware write protected, it cannot be changed back to "0", as long as the  $\overline{WP}$  pin is held low.

| WPEN | WP   | WEN | Protected<br>Blocks | Unprotected<br>Blocks | Status<br>Register |

|------|------|-----|---------------------|-----------------------|--------------------|

| 0    | Х    | 0   | Protected           | Protected             | Protected          |

| 0    | Х    | 1   | Protected           | Writable              | Writable           |

| 1    | Low  | 0   | Protected           | Protected             | Protected          |

| 1    | Low  | 1   | Protected           | Writable              | Protected          |

| Х    | High | 0   | Protected           | Protected             | Protected          |

| Х    | High | 1   | Protected           | Writable              | Writable           |

Table 3-5.WPEN Operation

**READ SEQUENCE** (**READ**): Reading the AT25512 via the SO pin requires the following sequence. After the  $\overline{CS}$  line is pulled low to select a device, the Read op-code is transmitted via the SI line followed by the byte address to be read (see Table 3-6 on page 9). Upon completion, any data on the SI line will be ignored. The data (D7 – D0) at the specified address is then shifted out onto the SO line. If only one byte is to be read, the  $\overline{CS}$  line should be driven high after the data comes out. The read sequence can be continued since the byte address is automatically incremented and data will continue to be shifted out. When the highest address is reached, the address counter will roll over to the lowest address allowing the entire memory to be read in one continuous read cycle.

**WRITE SEQUENCE (WRITE):** In order to program the AT25512, two separate instructions must be executed. First, the device *must be write enabled* via the Write Enable (WREN) Instruction. Then a Write instruction may be executed. Also, the address of the memory location(s) to be programmed must be outside the protected address field location selected by the Block Write

http://www.BDTIC.com/ATM

5165F-SEEPR-3/09

# ı AT25512

Protection Level. During an internal write cycle, all commands will be ignored except the RDSR instruction.

A Write Instruction requires the following sequence. After the  $\overline{CS}$  line is pulled low to select the device, the Write op-code is transmitted via the SI line followed by the byte address and the data (D7 – D0) to be programmed (see Table 3-6). Programming will start after the  $\overline{CS}$  pin is brought high. (The Low-to-High transition of the  $\overline{CS}$  pin must occur during the SCK low time immediately after clocking in the D0 (LSB) data bit.

The Ready/Busy status of the device can be determined by initiating a Read Status Register (RDSR) Instruction. If Bit 0 = 1, the Write cycle is still in progress. If Bit 0 = 0, the Write cycle has ended. Only the Read Status Register instruction is enabled during the Write programming cycle.

The AT25512 is capable of a 128-byte Page Write operation. After each byte of data is received, the seven low order address bits are internally incremented by one; the high order bits of the address will remain constant. If more than 128 bytes of data are transmitted, the address counter will roll over and the previously written data will be overwritten. The AT25512 is automatically returned to the write disable state at the completion of a Write cycle.

**NOTE:** If the device is not write enabled (WREN), the device will ignore the Write instruction and will return to the standby state, when  $\overline{CS}$  is brought high. A new CS falling edge is required to re-initiate the serial communication.

Table 3-6. Address Key

| Address        | AT25512        |

|----------------|----------------|

| A <sub>N</sub> | $A_{15} - A_0$ |

## 4. Timing Diagrams (for SPI Mode 0 (0, 0))

http://www.BDTIC.com/A7

Figure 4-1. Synchronous Data Timing

AT25512 ı

10

EL

TIC.com/ATI

5165F-SEEPR-3/09

hti

://www.

11

FT.

http://www.BDTIC.com/A7

12 AT25512

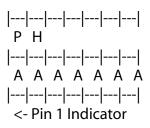

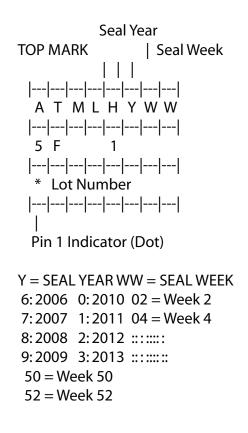

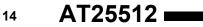

#### Part Marking Scheme 5.

**TOP MARK**

Pin 1 Indicator (Dot)

**BOTTOM MARK**

| Y = SEAL     | YEAR W | W = SEAL WEEK |  |  |  |

|--------------|--------|---------------|--|--|--|

| 6:2006       | 0:2010 | 02 = Week 2   |  |  |  |

| 7:2007       | 1:2011 | 04 = Week 4   |  |  |  |

| 8:2008       | 2:2012 |               |  |  |  |

| 9:2009       | 3:2013 |               |  |  |  |

| 50 = Week 50 |        |               |  |  |  |

52 = Week 52

### AT25512N-SH-B/T

Lot Number to Use ALL Characters in Marking

BOTTOM MARK

http://www.BDTIC.com/ATM

No Bottom Mark

H

AT25512

### AT25512Y7-YH-T

Lot Number to Use ALL Characters in Marking

**BOTTOM MARK**

No Bottom Mark

## 6. AT25512 Ordering Information

| Ordering Code                 | Voltage | Package  | Operation Range        |

|-------------------------------|---------|----------|------------------------|

| AT25512N-SH-B <sup>(1)</sup>  | 1.8     | 8S1      |                        |

| AT25512N-SH-T <sup>(2)</sup>  | 1.8     | 8S1      | Lead-free/Halogen-free |

| AT25512-TH-B <sup>(1)</sup>   | 1.8     | 8A2      | NiPDAu Lead Finish     |

| AT25512-TH-T <sup>(2)</sup>   | 1.8     | 8A2      | Industrial Temperature |

| AT25512Y7-YH-T <sup>(2)</sup> | 1.8     | 8Y7      | (–40°C to 85°C)        |

| AT25512-W-11 <sup>(3)</sup>   | 1.8     | Die Sale | Industrial Temperature |

|                               |         |          | (−40°C to 85°C)        |

Notes: 1. "-B" denotes bulk.

- 2. "-T" denotes tape and reel. SOIC = 4K per reel. TSSOP = 5K per reel. SAP = 3K per reel.

- 3. Available in waffle pack, tape and reel, and wafer form; order as SL788 for inkless wafer form. Bumped die available upon request. Please contact Serial Interface Marketing.

| Package Type |                                                                                                 |  |  |

|--------------|-------------------------------------------------------------------------------------------------|--|--|

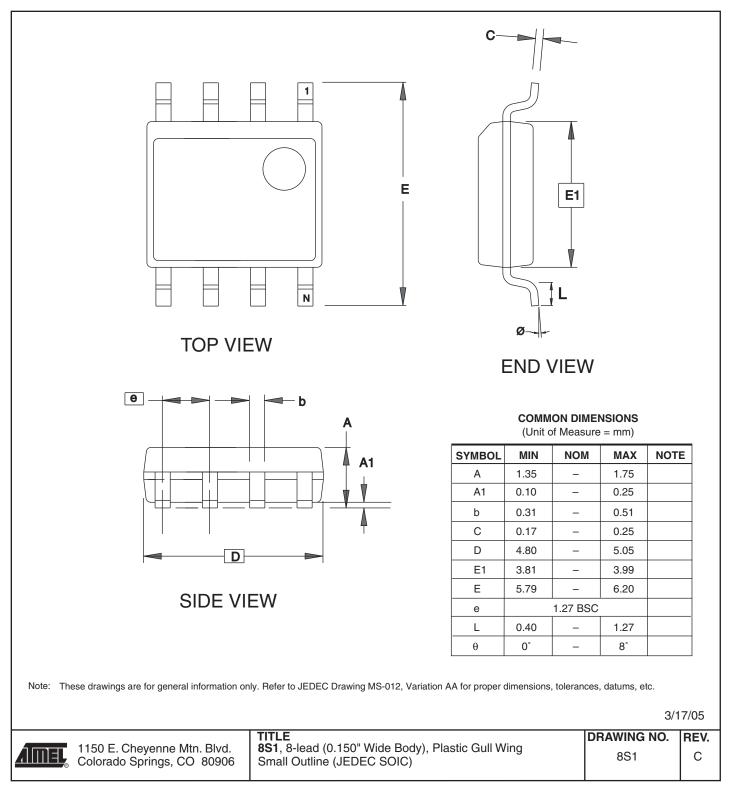

| 8S1          | 8-lead, 0.150" Wide, Plastic Gull Wing Small Outline (JEDEC SOIC)                               |  |  |

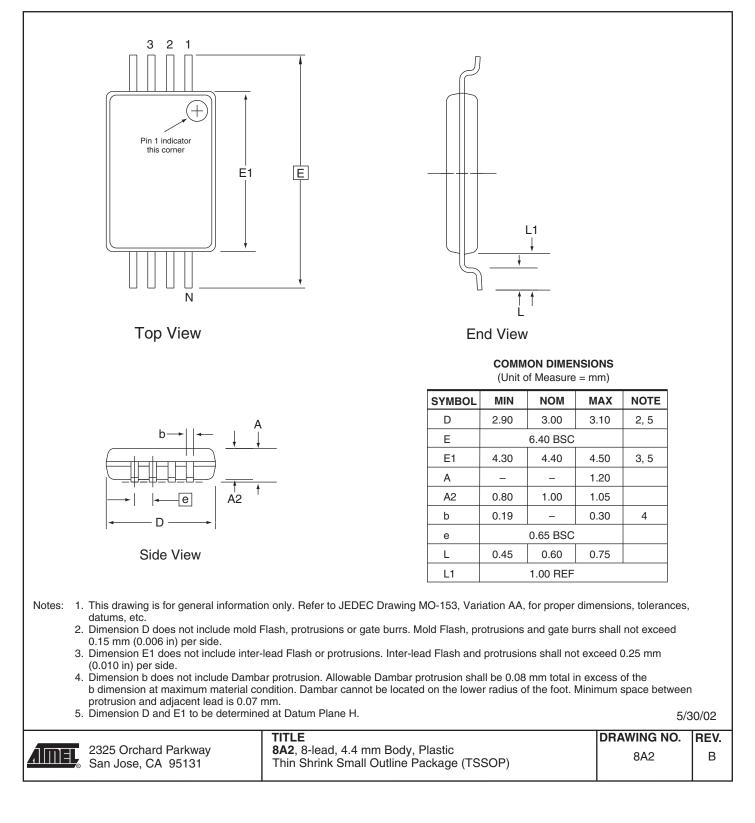

| 8A2          | 8-lead, 4.4 mm Body, Plastic Thin Shrink Small Outline Package (TSSOP)                          |  |  |

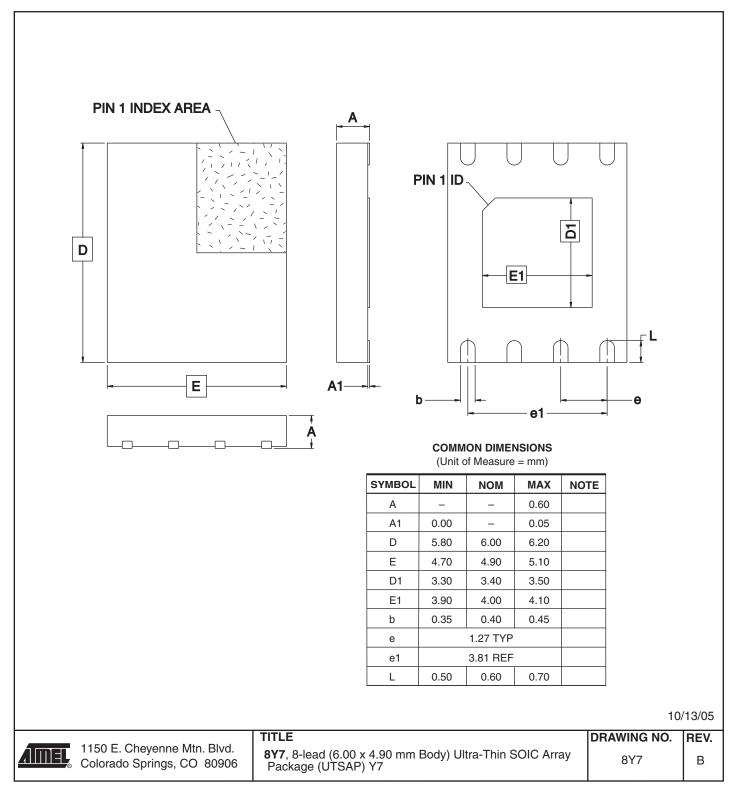

| 8Y7          | 8-lead, 6.00mm x 4.90mm Body, Ultra Thin, Dual Footprint, Non-leaded, Small Array Package (SAP) |  |  |

| Options      |                                                                                                 |  |  |

| -1.8         | Low-voltage (1.8V to 5.5V)                                                                      |  |  |

http://www.BDTIC.com/ATM

16 AT25512

## 7. Packaging Information

## 8S1 – JEDEC SOIC

TIC.com/ATN

5165F-SEEPR-3/09

b://www.

ET.

## 8A2 – TSSOP

http://www.BDTIC.com/AT

18 AT25512

### 8Y7 - SAP

EL

TIC.com/ATM

h

EL

## 8. Revision History

| Doc. Rev. | Date   | Comments                                                                                                          |

|-----------|--------|-------------------------------------------------------------------------------------------------------------------|

| 5165F     | 3/2009 | Changed Maximum Operating Voltage from 4.3V to 6.25V in the Absolute Maximum Ratings Table on page 2              |

| 5165E     | 8/2008 | Updated for 1.8V - 5.5V operation                                                                                 |

| 5165D     | 5/2008 | Added part marking diagram information                                                                            |

| 5165C     | 8/2007 | Changed address bit number to seven on page 9<br>Removed Preliminary status                                       |

| 5165B     | 6/2007 | Changed spacing on table notes<br>Reworked figure 4-8<br>Updated to new template<br>Changed status to Preliminary |

| 5165A     | 1/2007 | Initial document release                                                                                          |