NOVEMBER 2006 REV.1.2.0.

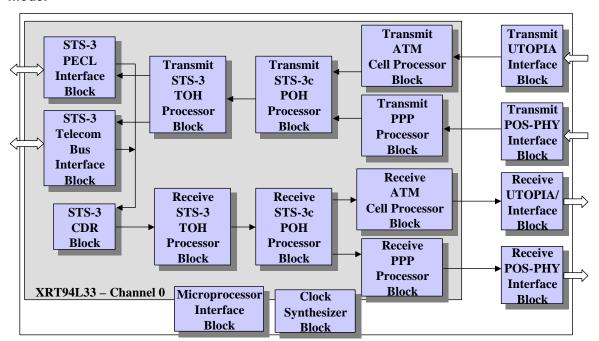

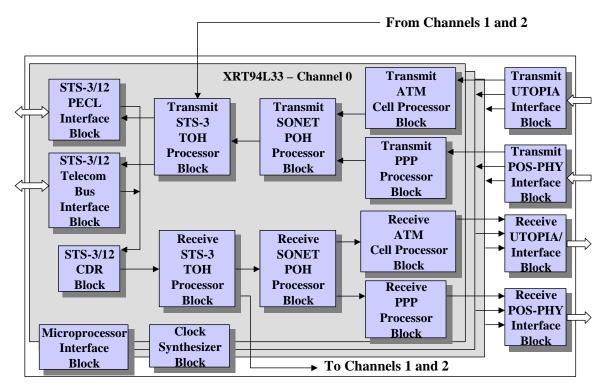

#### **GENERAL DESCRIPTION**

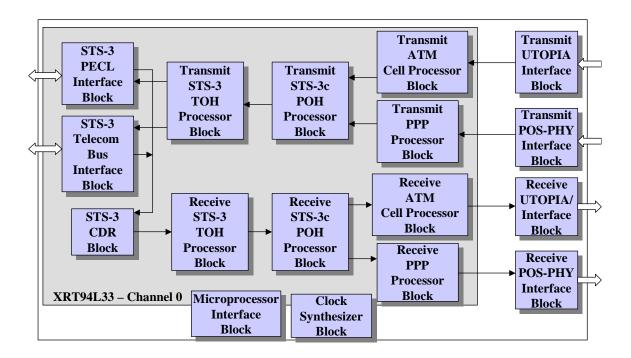

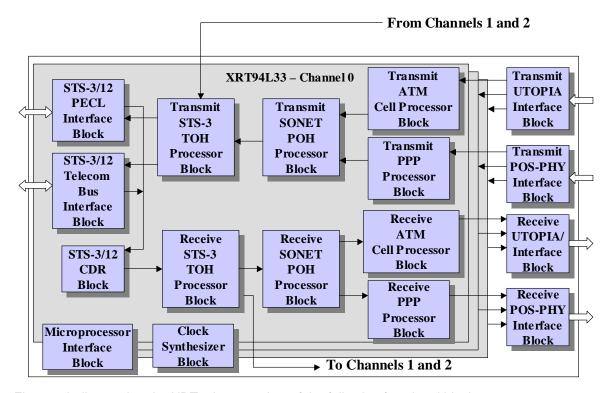

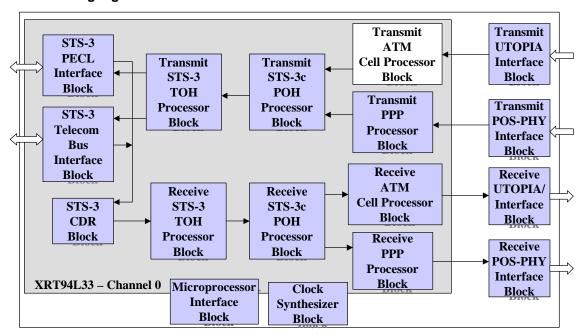

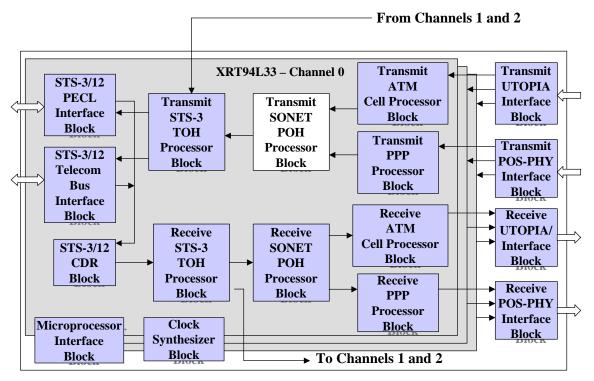

The XRT94L33 is a highly integrated SONET/SDH terminator designed for E3/DS3/STS-1 mapping/de-mapping functions from either the STS-3 or STM-1 data stream. The XRT94L33 interfaces directly to the optical transceiver

The XRT94L33 processes the section, line and path overhead in the SONET/SDH data stream and also performs ATM and PPP PHY-layer processing. The processing of path overhead bytes within the STS-1s or TUG-3s includes 64 bytes for storing the J1 bytes. Path overhead bytes can be accessed through the microprocessor interface or via serial interface.

The XRT94L33 uses the internal E3/DS3 De-Synchronizer circuit with an internal pointer leak algorithm for clock smoothing as well as to remove the jitter due to mapping and pointer movements. These De-Synchronizer circuits do not need any external clock reference for its operation.

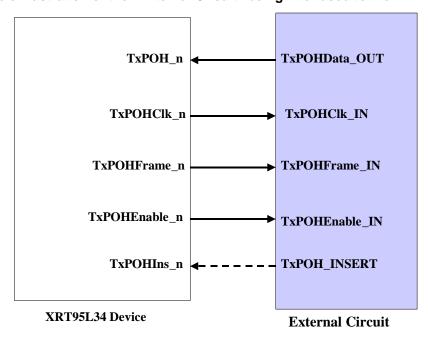

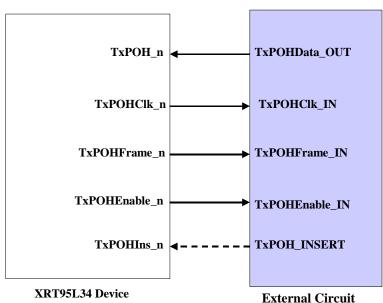

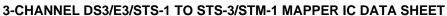

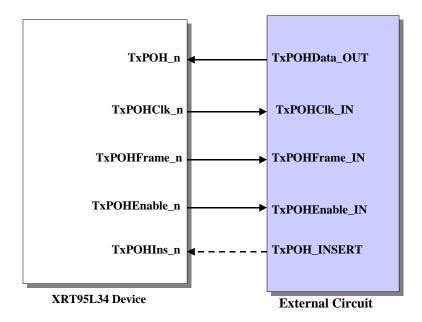

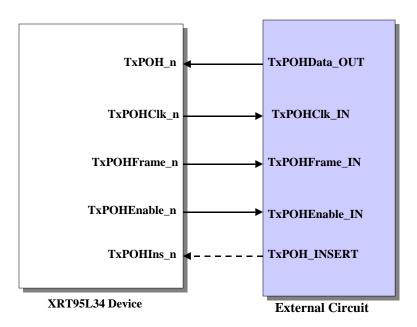

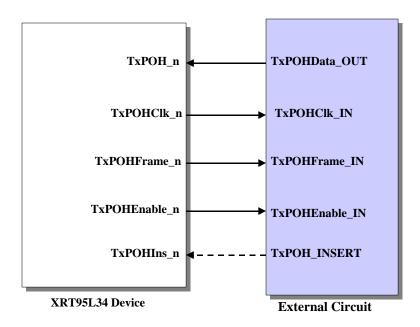

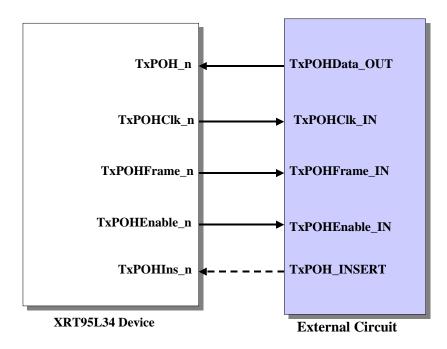

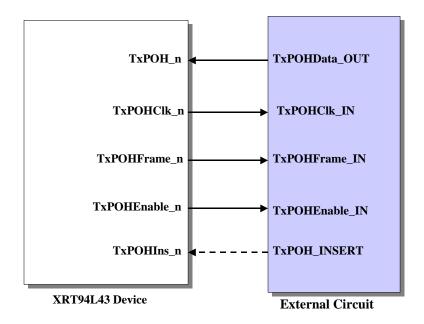

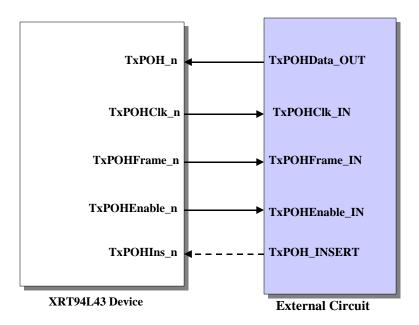

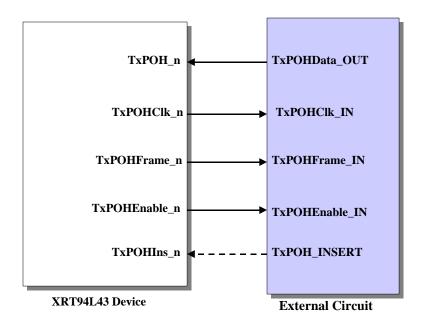

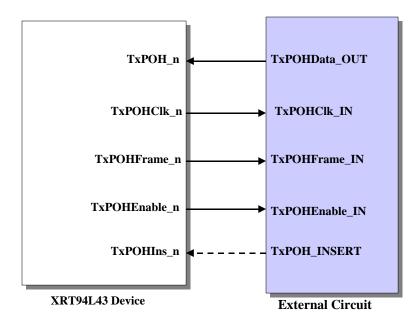

The SONET/SDH transmit blocks allow flexible insertion of TOH and POH bytes through both Hardware and Software. Individual POH bytes for the transmitted SONET/SDH signal are mapped either from the XRT94L33 memory map or from external interface. A1, A2 framing pattern, C1 byte and H1, H2 pointer byte are generated.

The SONET/SDH receive blocks receive SONET STS-3 signal or SDH STM-1 signal and perform the necessary transport and path overhead processing.

The XRT94L33 provides a line side APS (Automatic Protection Switching) interface by offering redundant receive serial interface to be switched at the frame boundary.

The XRT94L33 provides 3 mappers for performing STS-1/VC-3 to STS-1/DS3/E3 mapping function, one for each STS-1/DS3/E3 framers.

A PRBS test pattern generation and detection is implemented to measure the bit-error performance.

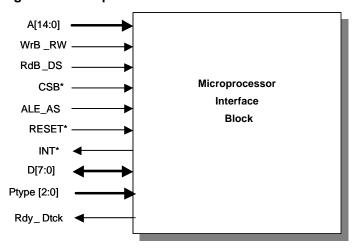

A general-purpose microprocessor interface is included for control, configuration and monitoring.

#### **APPLICATIONS**

- Network switches

- Add/Drop Multiplexer

- W-DCS Digital Cross Connect Systems

#### **FEATURES**

- Provides DS3/ E3 mapping/de-mapping for up to 3 tributaries through SONET STS-1 or SDH AU-3 and/or TUG-3/AU-4 containers

- Generates and terminates SONET/SDH section, line and path layers

- Integrated SERDES with Clock Recovery Circuit

- Provides SONET frame scrambling and descrambling

- Integrated Clock Synthesizer that generates 155 MHz and 77.76 MHz clock from an external 12.96/19.44/77.76 MHz reference clock

- Integrated 3 E3/DS3/STS-1 De-Synchronizer circuit that de-jitter gapped clock to meet 0.05Ulpp jitter requirements

- Access to Line or Section DCC

- Level 2 Performance Monitoring for E3 and DS3

- Supports mixing of STS-1E and DS3 or E3 and DS3 tributaries

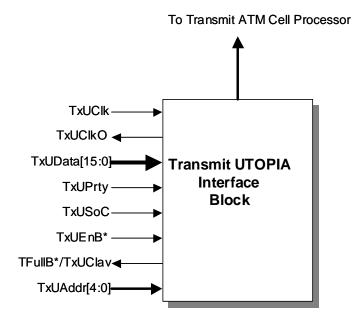

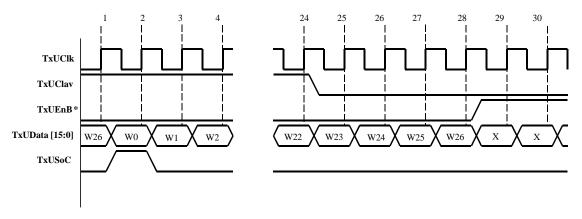

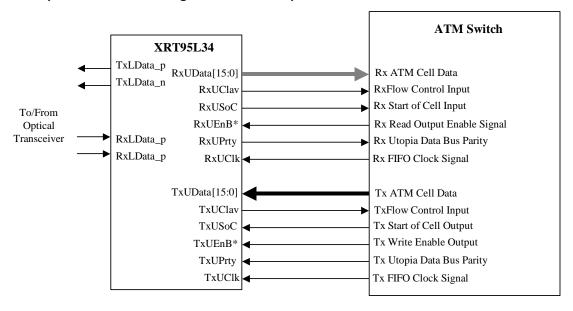

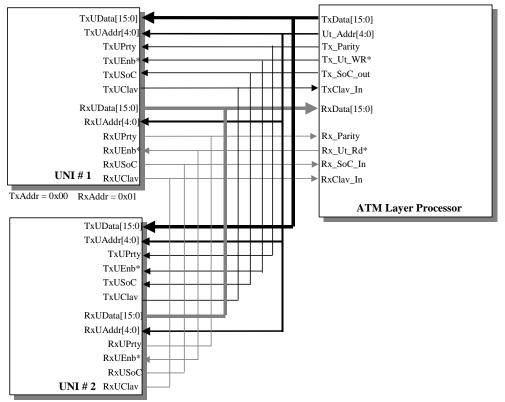

- UTOPIA Level 2 interface for ATM or level 2P for Packets

- E3 and DS3 framers for both Transmit and Receive directions

- Complete Transport/Section Overhead Processing and generation per Telcordia and ITU standards

- Single PHY and Multi-PHY operations supported

- Full line APS support for redundancy applications

- Loopback support for both SONET/SDH as well as E3/DS3/STS-1

- Boundary scan capability with JTAG IEEE 1149

- 8-bit microprocessor interface

- 3.3 V ± 5% Power Supply; 5 V input signal tolerance

- -40°C to +85°C Operating Temperature Range

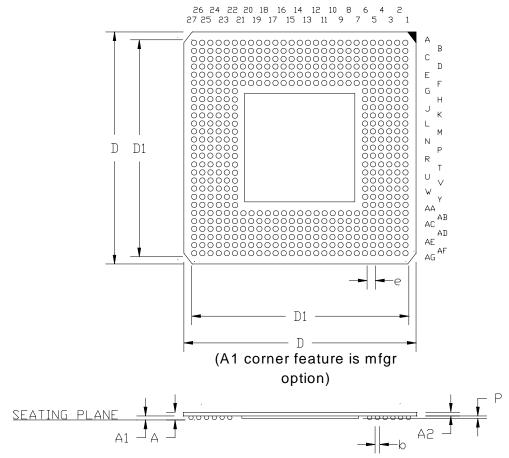

- Available in a 504 Ball TBGA package

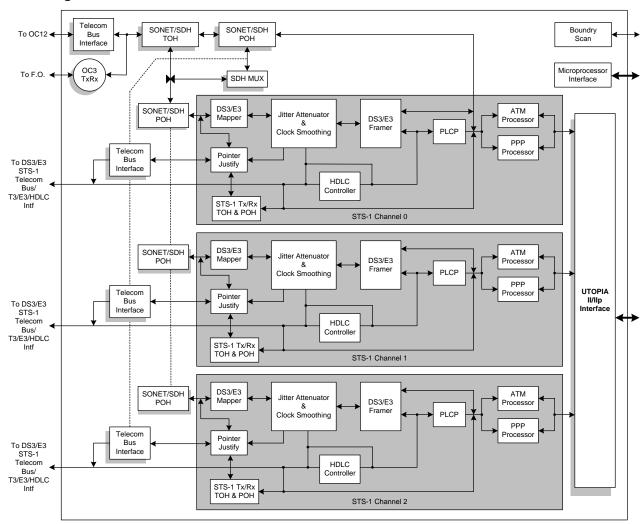

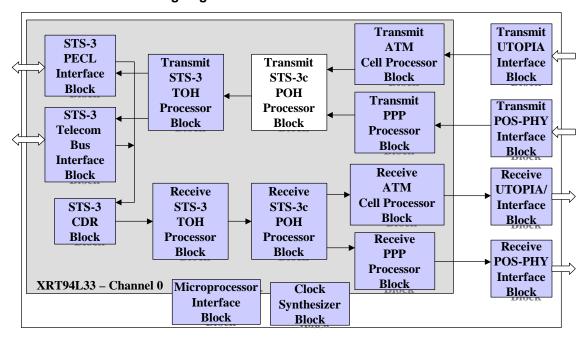

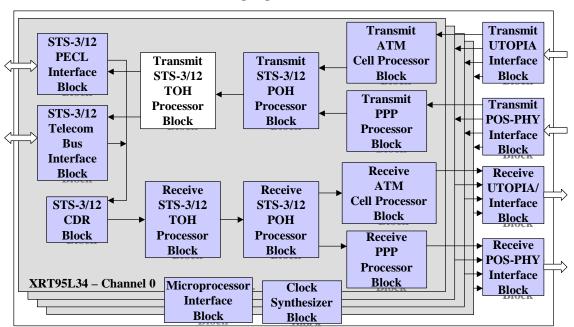

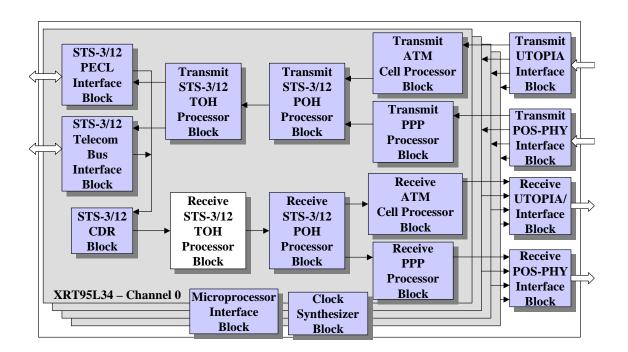

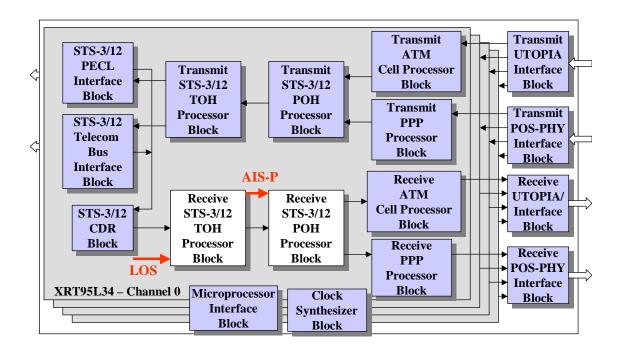

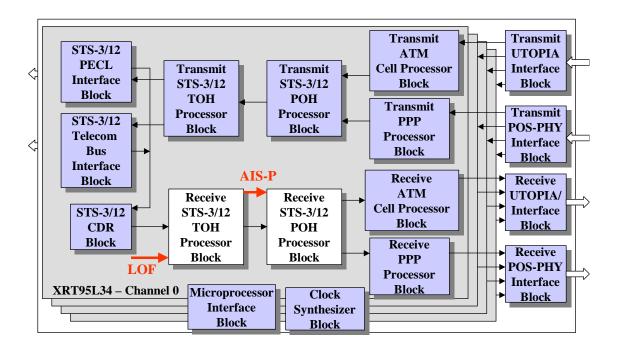

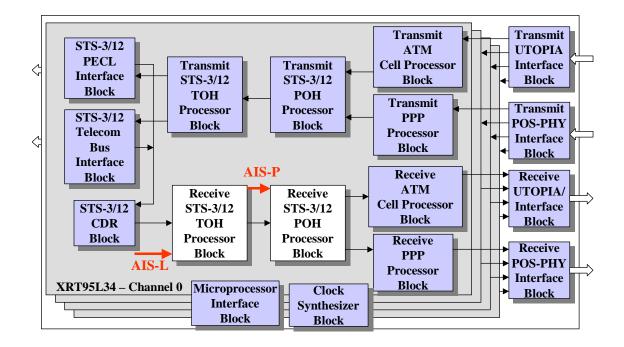

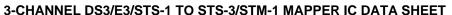

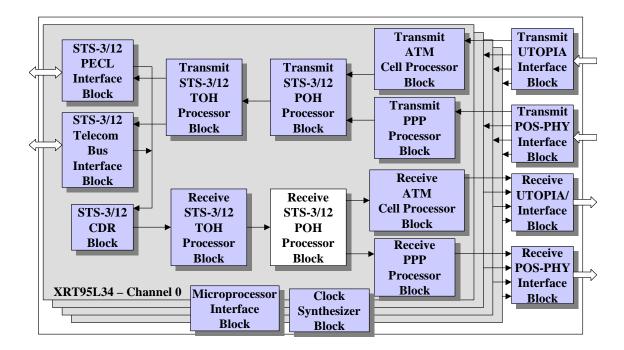

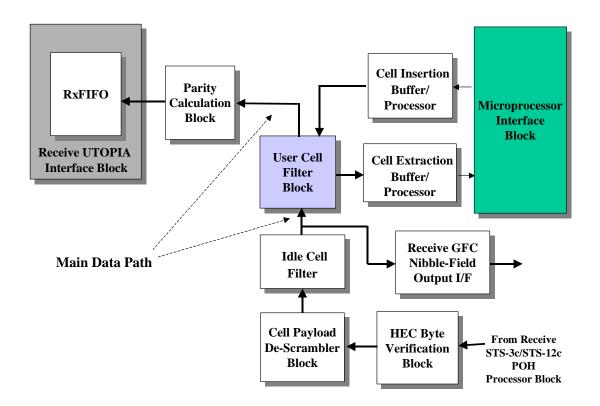

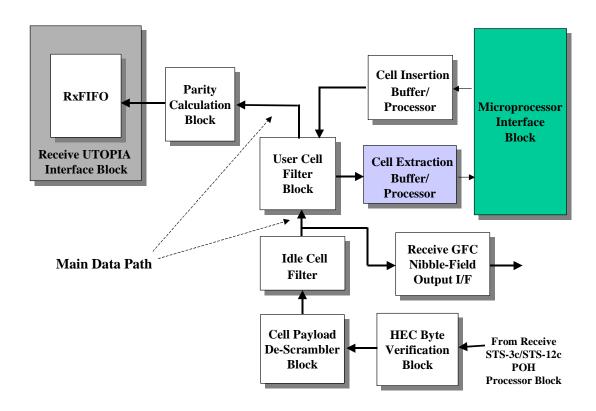

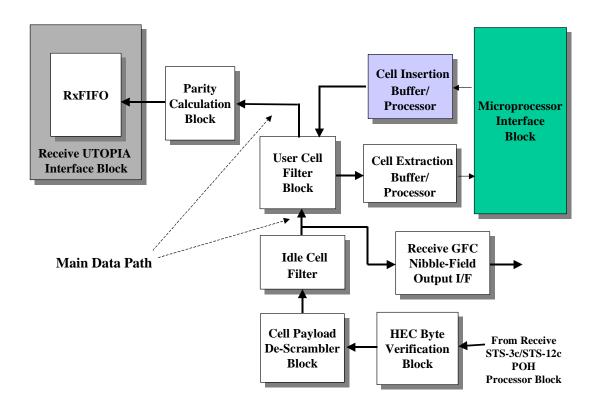

#### **Block Diagram of the XRT94L33**

#### ORDERING INFORMATION

| Part Number | PACKAGE TYPE          | OPERATING TEMPERATURE RANGE |

|-------------|-----------------------|-----------------------------|

| XRT94L33IB  | 27 x 27 504 Lead TBGA | -40°C to +85°C              |

### PIN DESCRIPTION of the XRT94L33 (Rev. B)

| Pin#         | SIGNAL NAME        | I/O                                          | SIGNAL<br>Type | DESCRIPTION                                                                                                                                                                                                                                                                                           |

|--------------|--------------------|----------------------------------------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | <u> </u>           | <u>                                     </u> |                | ROCESSOR INTERFACE                                                                                                                                                                                                                                                                                    |

| Y22          | PCLK               | I                                            | TTL            | Microprocessor Interface Clock Input:                                                                                                                                                                                                                                                                 |

|              |                    |                                              |                | This clock input signal is only used if the Microprocessor Interface has been configured to operate in one of the Synchronous Mode (e.g., Power PC 403 Mode). If the Microprocessor Interface is configured to operate in one of these modes, then it will use this clock signal to do the following. |

|              |                    |                                              |                | • To sample the CS*, WR*/R/W*, A[14:0], D[7:0], RD*/DS* and DBEN input pins, and                                                                                                                                                                                                                      |

|              |                    |                                              |                | To update the state of D[7:0] and the RDY/DTACK output signals.                                                                                                                                                                                                                                       |

|              |                    |                                              |                | NOTES:                                                                                                                                                                                                                                                                                                |

|              |                    |                                              |                | <ol> <li>The Microprocessor Interface can work with μPCLK frequencies ranging up to 33MHz.</li> </ol>                                                                                                                                                                                                 |

|              |                    |                                              |                | <ol> <li>This pin is inactive if the user has configured the<br/>Microprocessor Interface to operate in either the Intel-<br/>Asynchronous or the Motorola-Asynchronousl Modes.<br/>In this case, the user should tie this pin to GND.</li> </ol>                                                     |

| AD25         | PTYPE_0            | I                                            | TTL            | Microprocessor Type Select input:                                                                                                                                                                                                                                                                     |

| AD23<br>AC21 | PTYPE_1<br>PTYPE_2 |                                              |                | These three input pins permit the user to configure the Microprocessor Interface block to readily support a wide variety of Microprocessor Interfaces. The relationship between the settings of these input pins and the corresponding Microprocessor Interface configuration is presented below.     |

|              |                    |                                              |                | PTYPE[2:0] Microprocessor Interface Mode                                                                                                                                                                                                                                                              |

|              |                    |                                              |                | 000 Intel-Asynchronous Mode                                                                                                                                                                                                                                                                           |

|              |                    |                                              |                | 001 Motorola – Asynchronous Mode                                                                                                                                                                                                                                                                      |

|              |                    |                                              |                | 010 Intel X86                                                                                                                                                                                                                                                                                         |

|              |                    |                                              |                | 011 Intel I960                                                                                                                                                                                                                                                                                        |

|              |                    |                                              |                | 100 IDT3051/52 (MIPS)                                                                                                                                                                                                                                                                                 |

|              |                    |                                              |                | 101 Power PC 403 Mode                                                                                                                                                                                                                                                                                 |

|              |                    |                                              |                | 111 Motorola 860                                                                                                                                                                                                                                                                                      |

| Pin# | SIGNAL NAME | I/O | Signal<br>Type | DESCRIPTION                                                 |

|------|-------------|-----|----------------|-------------------------------------------------------------|

| AD27 | PADDR_0     | ı   | TTL            | Address Bus Input pins (Microprocessor Interface):          |

| AB25 | PADDR_1     |     |                | These pins permit the Microprocessor to identify on-chip    |

| W23  | PADDR_2     |     |                | registers and Buffer/Memory locations (within the XRT94L33) |

| Y24  | PADDR_3     |     |                | whenever it performs READ and WRITE operations with the     |

| AD26 | PADDR_4     |     |                | XRT94L33.                                                   |

| AC25 | PADDR_5     |     |                |                                                             |

| AA24 | PADDR_6     |     |                |                                                             |

| Y23  | PADDR_7     |     |                |                                                             |

| AE24 | PADDR_8     |     |                |                                                             |

| AB20 | PADDR_9     |     |                |                                                             |

| AD22 | PADDR_10    |     |                |                                                             |

| AC20 | PADDR_11    |     |                |                                                             |

| AD21 | PADDR_12    |     |                |                                                             |

| AE23 | PADDR_13    |     |                |                                                             |

| AF24 | PADDR_14    |     |                |                                                             |

| AD20 | PDATA_0     | I/O | TTL            | Bi-Directional Data Bus pins (Microprocessor Interface):    |

| AC19 | PDATA_1     |     |                | These pins are used to drive and receive data over the bi-  |

| AE22 | PDATA_2     |     |                | directional data bus, whenever the Microprocessor performs  |

| AG24 | PDATA_3     |     |                | READ and WRITE operations with the Microprocessor Interface |

| AE21 | PDATA_4     |     |                | of the XRT94L33.                                            |

| AD19 | PDATA_5     |     |                |                                                             |

| AF23 | PDATA_6     |     |                |                                                             |

| AE20 | PDATA_7     |     |                |                                                             |

| Pin# | SIGNAL NAME | I/O | Signal<br>Type | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|------|-------------|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AF22 | PWR_L/      | 1   | TTL            | Write Strobe/Read-Write Operation Identifier:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      | R/W*        |     |                | The exact function of this input pin depends upon which mode the Microprocessor Interface has been configured to operate in, as described below.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

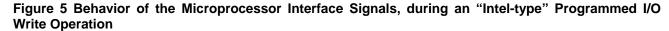

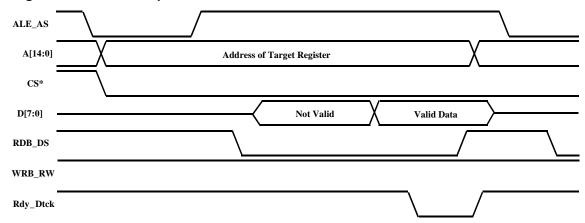

|      |             |     |                | Intel-Asynchronous Mode – WR* - Write Strobe Input:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|      |             |     |                | If the Microprocessor Interface is configured to operate in the Intel-Asynchronous Mode, then this input pin functions as the WR* (Active-Low WRITE Strobe) input signal from the Microprocessor. Once this active-low signal is asserted, then the input buffers (associated with the Bi-Directional Data Bus pins, D[7:0]) will be enabled. The Microprocessor Interface will latch the contents on the Bi-Directional Data Bus (into the "target" register or address location, within the XRT94L33) upon the rising of this input.                                                                                                                                                                                             |

|      |             |     |                | Motorola-Asynchronous Mode - R/W* - Read/Write Operation Identification Input Pin:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |             |     |                | If the Microprocessor Interface is operating in the "Motorola-Asynchronous" Mode, then this pin is functionally equivalent to the "R/W*" input pin. In the Motorola Mode, a "READ" operation occurs if this pin is held at a logic "1", coincident to a falling edge of the RD/DS* (Data Strobe) input pin.                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |             |     |                | PowerPC 403 Mode – R/W* - Read/Write Operation Identification Input:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |             |     |                | If the Microprocessor Interface is configured to operate in the PowerPC 403 Mode, then this input pin will function as the "Read/Write Operation Identification" input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      |             |     |                | Anytime the Microprocessor Interface samples this input signal at a logic "low" (while also sampling the CS* input pin "low") upon the rising edge of PCLK, then the Microprocessor Interface will (upon the very same rising edge of PCLK) latch the contents of the Address Bus (A]14:0]) into the Microprocessor Interface circuitry, in preparation for this forthcoming READ operation. At some point (later in this READ operation) the Microprocessor will also assert the DBEN*/OE* input pin, and the Microprocessor Interface will then place the contents of the "target" register (or address location within the XRT94L33) upon the Bi-Directional Dat Bus pins (D[7:0]), where it can be read by the Microprocessor. |

|      |             |     |                | Anytime the Microprocessor Interface samples this input signal at a logic high (while also sampling the CS* input pin at a logic "low") upon the rising edge of PCLK, then the Microprocessor Interface will (upon the very same rising edge of PCLK) latch the contents of the Address Bus (A[14:0]) into the Microprocessor Interface circuitry, in preparation for the forthcoming WRITE operation. At some point (later in this WRITE operation) the Microprocessor will also assert the RD*/DS*/WE* input pin, and the Microprocessor Interface will then latch the contents of the Bi-Directional Data Bus (D[7:0]) into the contents of the "target" register or buffer location (within the XRT94L33).                     |

| Pin# | SIGNAL NAME | I/O | Signal<br>Type | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------|-------------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AC18 | PRD_L/      | I   | TTL            | READ Strobe /Data Strobe:                                                                                                                                                                                                                                                                                                                                                                                                                        |

|      | DS*/<br>WE* |     |                | The exact function of this input pin depends upon which mode the Microprocessor Interface has been configured to operate in, as described below.                                                                                                                                                                                                                                                                                                 |

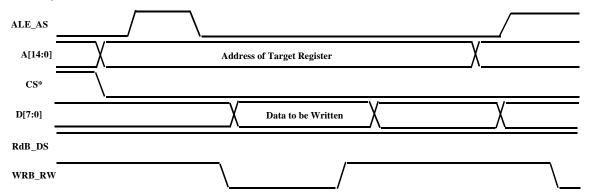

|      |             |     |                | Intel-Asynchronous Mode – RD* - READ Strobe Input:                                                                                                                                                                                                                                                                                                                                                                                               |

|      |             |     |                | If the Microprocessor Interface is operating in the Intel-Asynchronous Mode, then this input pin will function as the RD* (Active Low READ Strobe) input signal from the Microprocessor. Once this active-low signal is asserted, then the XRT94L33 will place the contents of the addressed register (or buffer location) on the Microprocessor Bi-directional Data Bus (D[7:0]). When this signal is negated, the Data Bus will be tri-stated. |

|      |             |     |                | Motorola-Asynchronous (68K) Mode – DS* - Data Strobe Input:                                                                                                                                                                                                                                                                                                                                                                                      |

|      |             |     |                | If the Microprocessor Interface is operating in the Motorola Asynchronous Mode, then this input will function as the DS* (Data Strobe) input signal.                                                                                                                                                                                                                                                                                             |

|      |             |     |                | PowerPC 403 Mode – WE* - Write Enable Input:                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |             |     |                | If the Microprocessor Interface is operating in the PowerPC 403 Mode, then this input pin will function as the WE* (Write Enable) input pin.                                                                                                                                                                                                                                                                                                     |

|      |             |     |                | Anytime the Microprocessor Interface samples this active-low input signal (along with CS* and WR*/R/W*) also being asserted (at a logic level) upon the rising edge of PCLK, then the Microprocessor Interface will (upon the very same rising edge of PCLK) latch the contents on the Bi-Directional Data Bus (D[7:0]) into the "target" on-chip register or buffer location within the XRT94L33.                                               |

| Pin# | SIGNAL NAME | I/O | Signal<br>Type | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                  |

|------|-------------|-----|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AG23 | ALE/        | I   | TTL            | Address Latch Enable/Address Strobe:                                                                                                                                                                                                                                                                                                                         |

|      | AS_L        |     |                | The exact function of this input pin depends upon which mode the Microprocessor Interface has been configured to operate in, as described below.                                                                                                                                                                                                             |

|      |             |     |                | Intel-Asynchronous Mode - ALE                                                                                                                                                                                                                                                                                                                                |

|      |             |     |                | If the Microprocessor Interface (of the XRT94L33) has been configured to operate in the Intel-Asynchronous Mode, then this active-high input pin is used to latch the address (present at the Microprocessor Interface Address Bus input pins (A[14:0]) into the XRT94L33 Microprocessor Interface block and to indicate the start of a READ or WRITE cycle. |

|      |             |     |                | Pulling this input pin "high" enables the input bus drivers for the Address Bus input pins (A[14:0]). The contents of the Address Bus will be latched into the XRT94L33 Microprocessor Interface circuitry, upon the falling edge of this input signal.                                                                                                      |

|      |             |     |                | Motorola-Asynchronous (68K) Mode – AS*                                                                                                                                                                                                                                                                                                                       |

|      |             |     |                | If the Microprocessor Interface has been configured to operate in<br>the Motorola-Asynchronous Mode, then this active-low input pin<br>is used to latch the data (residing on the Address Bus, A[14:0])<br>into the Microprocessor Interface circuitry of the XRT94L33.                                                                                      |

|      |             |     |                | Pulling this input pin "low" enables the input bus drivers for the Address Bus input pins. The contents of the Address Bus will be latched into the Microprocessor Interface circuitry, upon the rising edge of this signal.                                                                                                                                 |

|      |             |     |                | PowerPC 403 Mode – No Function – Tie to GND:                                                                                                                                                                                                                                                                                                                 |

|      |             |     |                | If the MIcroprocessor Interface has been configured to operate in the PowerPC 403 Mode, then this input pin has no role nor function and should be tied to GND.                                                                                                                                                                                              |

| AE19 | PCS_L       | I   | TTL            | Chip Select Input:                                                                                                                                                                                                                                                                                                                                           |

|      |             |     |                | The user must assert this active low signal in order to select the Microprocessor Interface for READ and WRITE operations between the Microprocessor and the XRT94L33 on-chip registers, LAPD and Trace Buffer locations.                                                                                                                                    |

| Pin# | SIGNAL NAME   | I/O | Signal<br>Type | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------|---------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD18 | PRDY_L/       | 0   | CMOS           | READY or DTACK Output:                                                                                                                                                                                                                                                                                                                                                                                                            |

|      | DTACK*<br>RDY |     |                | The exact function of this input pin depends upon wich mode the Microprocessor Interface has been configured to operate in, as described below.                                                                                                                                                                                                                                                                                   |

|      |               |     |                | Intel Asynchronous Mode – RDY* - READY output:                                                                                                                                                                                                                                                                                                                                                                                    |

|      |               |     |                | If the Microprocessor Interface has been configured to operate in<br>the Intel-Asyncrhronous Mode, then this output pin will function<br>as the "active-low" READY output.                                                                                                                                                                                                                                                        |

|      |               |     |                | During a READ or WRITE cycle, the Microprocessor Interface block will toggle this output pin to the logic "low" level ONLY when it (the Microprocessor Interface) is ready to complete or terminate the current READ or WRITE cycle. Once the Microprocessor has determined that this input pin has toggled to the logic "low" level, then it is now safe for it to move on and execute the next READ or WRITE cycle.             |

|      |               |     |                | If (during a READ or WRITE cycle) the Microprocessor Interface block is holding this output pin at a logic "high" level, then the MIcroprocessor is expected to extend this READ or WRITE cycle, until it detect this output pin being toggled to the logic low level.                                                                                                                                                            |

|      |               |     |                | Motorola Mode – DTACK* - Data Transfer Acknowledge Output:                                                                                                                                                                                                                                                                                                                                                                        |

|      |               |     |                | If the Microprocessor Interface has been configured to operate in the Motorola-Asynchronous Mode, then this output pin will function as the "active-low" DTACK* ouytput.                                                                                                                                                                                                                                                          |

|      |               |     |                | During a READ or WRITE cycle, the Microprocessor Interface block will toggle this output pin to the logic low level, ONLY when it (the Microprocessor Interface) is ready to complete or terminate the current READ or WRITE cycle. Once the Microprocessor has determined that this input pin has toggled to the logic "low" leve, then it is now safe for it to move on and execute the next READ or WRITE cycle.               |

|      |               |     |                | If (during a READ or WRITE cycle) the Microprocessor Interface block is holding this output pin at a logic "high" level, then the MIcroprocessor is expected to extend this READ or WRITE cycle, until it detects this output pin being toggled to the logic low level.                                                                                                                                                           |

|      |               |     |                | PowerPC 403 Mode – RDY – Ready Output:                                                                                                                                                                                                                                                                                                                                                                                            |

|      |               |     |                | If the Microprocessor Interface has been configured to operate in<br>the PowerPC 403 Mode, then this output pin will function as the<br>"active-high" READY output.                                                                                                                                                                                                                                                               |

|      |               |     |                | During a READ or WRITE cycle, the Microprocessor Interface block will toggle this output pin to the logic high level, ONLY when it (the Microprocessor Interface) is ready to complete or terminate the current READ or WRITE cycle. Once the Microprocessor has sampled this signal being at a logic "high" level (upon the rising edge of PCLK) then it is now safe for it to move on and execute the next READ or WRITE cycle. |

|      |               |     |                | The Microprocessor Interface will update the state of this output pin upon the rising edge of PCLK.                                                                                                                                                                                                                                                                                                                               |

| Pin# | SIGNAL NAME    | I/O | SIGNAL<br>Type | DESCRIPTION                                                                                                                                                                                                                                             |

|------|----------------|-----|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AF21 | PDBEN_L        | I   | TTL            | Bi-directional Data Bus Enable Input pin:                                                                                                                                                                                                               |

|      |                |     |                | This input pin permits the user to either enable or tri-state the Bi-<br>Directional Data Bus pins (D[7:0]), as described below.                                                                                                                        |

|      |                |     |                | Setting this input pin "low" enables the Bi-directional Data bus. Setting this input "high" tri-states the Bi-directional Data Bus.                                                                                                                     |

| AF20 | PBLAST_L       | I   | TTL            | Last Burst Transfer Indicator input pin:                                                                                                                                                                                                                |

|      |                |     |                | If the Microprocessor Interface is operating in the Intel-I960 Mode, then this input pin is used to indicate (to the Microprocessor Interface block) that the current data transfer is the last data transfer within the current burst operation.       |

|      |                |     |                | The Microprocessor should assert this input pin (by toggling it "Low") in order to denote that the current READ or WRITE operation (within a BURST operation) is the last operation of this BURST operation.                                            |

|      |                |     |                | <b>Note:</b> The user should connect this input pin to GND whenever the Microprocessor Interface has been configured to operate in the Intel-Async, Motorola 68K and IBM PowerPC 403 modes.                                                             |

| AG22 | PINT_L         | 0   | CMOS           | Interrupt Request Output:                                                                                                                                                                                                                               |

|      |                |     |                | This open-drain, active-low output signal will be asserted when the Mapper/Framer device is requesting interrupt service from the Microprocessor. This output pin should typically be connected to the "Interrupt Request" input of the Microprocessor. |

| AB24 | RESET_L        | I   | TTL            | Reset Input:                                                                                                                                                                                                                                            |

|      |                |     |                | When this "active-low" signal is asserted, the XRT94L33 will be asynchronously reset. When this occurs, all outputs will be "tristated" and all on-chip registers will be reset to their "default" values.                                              |

| AE18 | DIRECT_ADD_SEL | I   | TTL            | Address Location Select input pin:                                                                                                                                                                                                                      |

|      |                |     |                | This input pin must be pulled "HIGH" in order to permit normal operation of the Microprocessor Interface.                                                                                                                                               |

|      |                |     | SONET/SDH      | SERIAL LINE INTERFACE PINS                                                                                                                                                                                                                              |

| Т3   | RXLDAT_P       | I   | LVPECL         | Receive STS-3/STM-1 Data – Positive Polarity PECL Input:                                                                                                                                                                                                |

|      |                |     |                | This input pin, along with RXLDAT_N functions as the Recovered Data Input, from the Optical Transceiver or as the Receive Data Input from the system back-plane                                                                                         |

|      |                |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this input pin, along with "RXLDAT_N" functions as the "Primary" STS-3/STM-1 Receive Data Input Port.                                                                                   |

| Pin# | SIGNAL NAME | I/O | Signal<br>Type | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| T2   | RXLDAT_N    | I   | LVPECL         | Receive STS-3/STM-1 Data – Negative Polarity PECL Input:                                                                                                                                                                                                                                                                                                                    |

|      |             |     |                | This input pin, along with RXLDAT_P functions as the Recovered Data Input, from the Optical Transceiver or as the Receive Data Input from the system back-plane.                                                                                                                                                                                                            |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this input pin, along with "RXLDAT_P" functions as the "Primary Receive STS-3/STM-1 Data Input Port"                                                                                                                                                                                                        |

| U2   | RXLDAT_R_P  | I   | LVPECL         | Receive STS-3/STM-1 Data – Positive Polarity PECL Input – Redundant Port:                                                                                                                                                                                                                                                                                                   |

|      |             |     |                | This input pin, along with "RXLDAT_R_N" functions as the Recovered Data Input, from the Optical Transceiver or as the Receive Data Input from the system back-plane.                                                                                                                                                                                                        |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this input pin, along with "RXLDAT_R_N" functions as the "Redundant Receive STS-3/STM-1 Data Input Port".                                                                                                                                                                                                   |

| U1   | RXLDAT_R_N  | I   | LVPECL         | Receive STS-3/STM-1 Data – Negative Polarity PECL Input – Redundant Port:                                                                                                                                                                                                                                                                                                   |

|      |             |     |                | This input pin, along with "RXLDAT_R_P" functions as the Recovered Data Input, from the Optical Transceiver or as the Receive Data Input from the system back-plane.                                                                                                                                                                                                        |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this input pin, along with "RXLDAT_R_N" functions as the "Redundant Receive STS-3/STM-1 Data Input Port".                                                                                                                                                                                                   |

| AE27 | RXCLK_19MHZ | 0   | CMOS           | 19.44MHz Recovered Output Clock:                                                                                                                                                                                                                                                                                                                                            |

|      |             |     |                | This pin outputs a 19.44MHz clock signal that has been derived from the incoming STS-3/STM-1 line signal (via the Receive STS-3/STM-1 Clock and Data Recovery PLL).                                                                                                                                                                                                         |

|      |             |     |                | If the user wishes to operate the STS-3/STM-1 Interface in the "loop-timing" mode, then the user should route this particular signal through a "narrow-band" PLL (in order to attenuate any jitter within this signal) prior to routing it to the REFTTL input pin.                                                                                                         |

| P3   | REFCLK_P    | I   | LVPECL         | Transmit Reference Clock – Positive Polarity PECL Input:                                                                                                                                                                                                                                                                                                                    |

|      |             |     |                | This input pin, along with "REFCLK_N" and "REFTTL" can be configured to function as the timing source for the STS-3/STM-1 Transmit Interface Block.                                                                                                                                                                                                                         |

|      |             |     |                | If the user configures these two input pins to function as the timing source, then the user must apply a 155.52MHz clock signal, in the form of a PECL signal to these input pins. The user can configure these two inputs to function as the timing source by writing the appropriate data into the "Transmit Line Interface Control Register" (Address Location = 0x0383) |

|      |             |     |                | Note: Users should set this pin to "1" if "REFTTL" clock input is used                                                                                                                                                                                                                                                                                                      |

| Pin# | SIGNAL NAME | I/O | Signal<br>Type | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                 |

|------|-------------|-----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P2   | REFCLK_N    | I   | LVPECL         | Transmit Reference Clock – Negative Polarity PECL Input:                                                                                                                                                                                                                                                                                                                    |

|      |             |     |                | This input pin, along with "REFCLK_P" and "REFTTL" can be configured to function as the timing source for the STS-3/STM-1 Transmit Interface Block.                                                                                                                                                                                                                         |

|      |             |     |                | If the user configures these two input pins to function as the timing source, then the user must apply a 155.52MHz clock signal, in the form of a PECL signal to these input pins. The user can configure these two inputs to function as the timing source by writing the appropriate data into the "Transmit Line Interface Control Register" (Address Location = 0x0383) |

|      |             |     |                | Note: Users should set this pin to "0" if "REFTTL" clock input is used                                                                                                                                                                                                                                                                                                      |

| P5   | TXLDATO_P   | 0   | LVPECL         | Transmit STS-3/STM-1 Data - Positive Polarity PECL Output:                                                                                                                                                                                                                                                                                                                  |

|      |             |     |                | This output pin, along with TXLDATO_N functions as the Transmit Data Output, to the Optical Transceiver or to the system back-plane.                                                                                                                                                                                                                                        |

|      |             |     |                | For "High-Speed" Back-Plane Applications, the user should note that data is output from these output pins upon the rising/falling edge of "TXLCLKO_P/TXLCLKO_N".                                                                                                                                                                                                            |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this output pin, along with "TXLDATO_N" functions as the "Primary" Transmit STS-3/STM-1 Data Output Port.                                                                                                                                                                                                   |

| P6   | TXLDATO_N   | 0   | LVPECL         | Transmit STS-3/STM-1 Data – Negative Polarity PECL Output:                                                                                                                                                                                                                                                                                                                  |

|      |             |     |                | This output pin, along with TXLDATO_P functions as the Transmit Data Output, to the Optical Transceiver or to the system back-plane.                                                                                                                                                                                                                                        |

|      |             |     |                | For "High-Speed" Back-Plane Applications, the user should note that data is output from these output pins upon the rising/falling edge of TXLCLKO_P/TXLCLKO_N.                                                                                                                                                                                                              |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this output pin, along with "TXLDATO_P" functions as the "Primary" Transmit STS-3/STM-1 Data Output Port.                                                                                                                                                                                                   |

| M4   | TXLDATO_R_P | 0   | LVPECL         | Transmit STS-3/STM-1 Data - Positive Polarity PECL Output - Redundant Port:                                                                                                                                                                                                                                                                                                 |

|      |             |     |                | This output pin, along with TXLDATO_R_N functions as the Transmit Data Output, to the Optical Transceiver or to the system back-plane.                                                                                                                                                                                                                                      |

|      |             |     |                | For "High-Speed" Back-Plane Applications, the user should note that data is output from these output pins upon the rising/falling edge of "TXLCLKO_R_P/TXLCLKO_R_N").                                                                                                                                                                                                       |

|      |             |     |                | Note: For APS (Automatic Protection Switching) purposes, this output pin, along with "TXLDATO_N" functions as the "Redundant" Transmit STS-3/STM-4 Data Output Port.                                                                                                                                                                                                        |

| Pin# | SIGNAL NAME | I/O | Signal<br>Type | DESCRIPTION                                                                                                                                                                                                                         |

|------|-------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M3   | TXLDATO_R_N | 0   | LVPECL         | Transmit STS-3/STM-1 Data - Negative Polarity PECL Output - Redundant Port:                                                                                                                                                         |

|      |             |     |                | This output pin, along with TXLDATO_R_P functions as the Transmit Data Output, to the Optical Transceiver (for transmission to remote terminal equipment) or to the system back-plane (for transmission to some other System board) |

|      |             |     |                | For "High-Speed" Back-Plane Applications, the user should note that data is output from these output pins upon the rising/falling edge of "TXLCLKO_R_P/TXLCLKO_R_N").                                                               |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this output pin, along with "TXLDATO_R_P" functions as the "Redundant" Transmit STS-3/STM-1 Data Output Port.                                                       |

| N6   | TXLCLKO_P   | 0   | LVPECL         | Transmit STS-3/STM-1 Clock – Positive Polarity PECL Output:                                                                                                                                                                         |

|      |             |     |                | This output pin, along with TXLCLKO_N functions as the Transmit Clock Output signal.                                                                                                                                                |

|      |             |     |                | These output pins are typically used in "High-Speed" Back-Plane Applications. In this case, outbound STS-3/STM-1 data is output via the "TXLDATO_P/TXLDATO_N" output pins upon the rising edge of this clock signal.                |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this output pin, along with "TXLCLKO_N" functions as the "Primary Transmit Output Clock" signal.                                                                    |

| N5   | TXLCLKO_N   | 0   | LVPECL         | Transmit STS-3/STM-1 Clock – Negative Polarity PECL Output:                                                                                                                                                                         |

|      |             |     |                | This output pin, along with TXLCLKO_P functions as the Transmit Clock Output signal.                                                                                                                                                |

|      |             |     |                | These output pins are typically used in "High-Speed" Back-Plane Applications. In this case, outbound STS-3/STM-1 data is output via the "TXLDATO_P/TXLDATO_N" output pins upon the falling edge of this clock signal.               |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this output pin, along with "TXLCLKO_N" functions as the "Primary Transmit Output Clock" signal.                                                                    |

| M1   | TXLCLKO_R_P | 0   | LVPECL         | Transmit STS-3/STM-1 Clock – Positive Polarity PECL Output – Redundant Port:                                                                                                                                                        |

|      |             |     |                | This output pin, along with TXLCLKO_R_N functions as the Transmit Clock Output signal.                                                                                                                                              |

|      |             |     |                | These output pins are typically used in "High-Speed" Back-Plane Applications. In this case, outbound STS-3/STM-1 data is output via the "TXLDATO_R_P/TXLDATO_R_N" output pins upon the rising edge of this clock signal.            |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this output pin, along with "TXLCLKO_R_N" functions as the "Redundant Transmit Output Clock" signal.                                                                |

| Pin# | SIGNAL NAME | I/O | SIGNAL<br>TYPE | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                |

|------|-------------|-----|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M2   | TXLCLKO_R_N | 0   | LVPECL         | Transmit STS-3/STM-1 Clock – Negative Polarity PECL Output – Redundant Port:                                                                                                                                                                                                                                                                                                                               |

|      |             |     |                | This output pin, along with TXLCLKO_R_P functions as the Transmit Clock Output signal.                                                                                                                                                                                                                                                                                                                     |

|      |             |     |                | These output pins are typically used in "High-Speed" Back-Plane Applications. In this case, outbound STS-3/STM-1 data is output via the "TXLDATO_R_P/TXLDATO_R_N" output pins upon the rising edge of this clock signal.                                                                                                                                                                                   |

|      |             |     |                | <b>Note:</b> For APS (Automatic Protection Switching) purposes, this output pin, along with "TXLCLKO_R_P" functions as the "Redundant Transmit Output Clock" signal.                                                                                                                                                                                                                                       |

| P1   | REFTTL      | I   | TTL            | 19.44MHz or 77.76MHz Clock Synthesizer Reference Clock Input Pin:                                                                                                                                                                                                                                                                                                                                          |

|      |             |     |                | The exact function of this input pin depends upon whether the user enables the "Clock Synthesizer" block or not.                                                                                                                                                                                                                                                                                           |

|      |             |     |                | If Clock Synthesizer is Enabled.                                                                                                                                                                                                                                                                                                                                                                           |

|      |             |     |                | If the "Clock Synthesizer" block is enabled, then it will be used to generate the 155.52MHz, 19.44MHz and/or 77.76MHz clock signal for the STS-3/STM-1 block. In this mode, the user should apply a clock signal of either of the following frequencies to this input pin.                                                                                                                                 |

|      |             |     |                | • 19.44 MHz                                                                                                                                                                                                                                                                                                                                                                                                |

|      |             |     |                | • 38.88 MHz                                                                                                                                                                                                                                                                                                                                                                                                |

|      |             |     |                | • 51.84 MHz                                                                                                                                                                                                                                                                                                                                                                                                |

|      |             |     |                | • 77.76 MHz                                                                                                                                                                                                                                                                                                                                                                                                |

|      |             |     |                | Afterwards, the user needs to write the appropriate data into the "Transmit Line Interface Control Register" (Address Location = 0x0383) in order to (1) configure the Clock Synthesizer Block to accept any of the above-mentioned signals and generate a 155.52MHz, 19.44MHz or 77.76MHz clock signal, (2) to configure the Clock Synthesizer to function as the Clock Source for the STS-3/STM-1 block. |

|      |             |     |                | If Clock Synthesizer is NOT Enabled:                                                                                                                                                                                                                                                                                                                                                                       |

|      |             |     |                | If the "Clock Synthesizer" block is NOT enabled, then it will NOT be used to generate the 19.44MHz and/or 77.76MHz clock signal, for the STS-3/STM-1 block. In this configuration seting, the user MUST apply a 19.44MHz clock signal to this input pin.                                                                                                                                                   |

| Pin# | SIGNAL NAME | I/O | Signal<br>Type | DESCRIPTION                                                                                                                                                                                                 |

|------|-------------|-----|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AG3  | LOSTTL      | I   | TTL            | Loss of Optical Carrier Input – Primary:                                                                                                                                                                    |

|      |             |     |                | The user is expected to connect the "Loss of Carrier" output (from the Optical Transceiver) to this input pin.                                                                                              |

|      |             |     |                | If this input pin and the LOSPECL_P pin are pulled "high", or if both of these input pins are pulled "low", tthen the Receive STS-3 TOH Processor block will declare a "Loss of Optical Carrier" condition. |

|      |             |     |                | <b>Note:</b> This input pin is only active if the "Primary Port" is active. This input pin is inactive if the "Redundant Port" is active.                                                                   |

| AG25 | LOSTTL_R    | I   | TTL            | Loss of Optical Carrier Input – Redundant:                                                                                                                                                                  |

|      |             |     |                | The user is expected to connect the "Loss of Carrier" output (from the Optical Transceiver) to this input pin.                                                                                              |

|      |             |     |                | If this input pin and the LOSPECL_R are pulled "high", or if both of these input pins are pulled "low", then the Receive STS-3 TOH Processor block will declare a "Loss of Optical Carrier" condition.      |

|      |             |     |                | <b>Note:</b> This input pin is only active if the "Redundant Port" is active. This input pin is inactive if the "Primary Port" is active.                                                                   |

| L4   | LOSPECL_P   | I   | LVPECL         | Loss of PECL Interface Input – Primary:                                                                                                                                                                     |

|      |             |     |                | If this input pin is pulled "high", then the Receive STS-3 TOH Processor block will declare a "Loss of PECL Interface" condition.                                                                           |

|      |             |     |                | <b>Note:</b> This input pin is only active if the "Primary Port" is active. This input pin is inactive if the "Redundant Port" is active.                                                                   |

| L3   | LOSPECL_R   | I   | LVPECL         | Loss of PECL Interface Input – Redundant:                                                                                                                                                                   |

|      |             |     |                | If this input pin is pulled "high", then the Receive STS-3 TOH Processor block will declare a "Loss of PECL Interface" condition.                                                                           |