## **µP Supervisory Circuits**

## Description

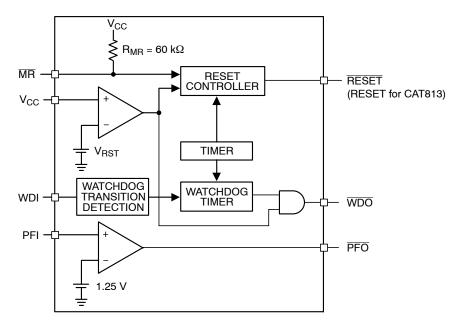

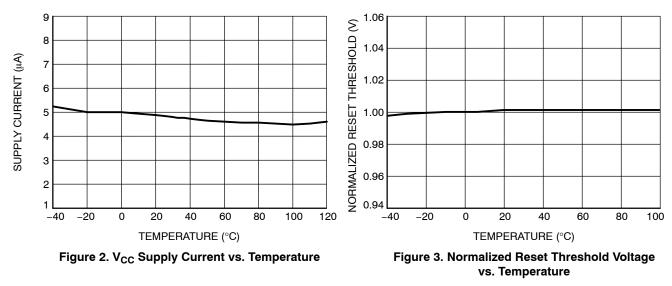

The CAT705, CAT706, and CAT813 provide reset and monitoring functions for the electronic systems. Each device monitors the system voltage and maintains a reset output until that voltage reaches the device's specified trip value and then maintains the reset output active condition until the device's internal timer allows the system power supply to stabilize.

The devices have a watchdog input which can be used to monitor a system signal and causes  $\overline{WDO}$  to go low if the signal fails to change state prior to a timeout condition.

The supervisory circuits provide a  $\overline{MR}$  input which initiates a reset if pulled low. The CAT705 and CAT706 provide an active low RESET output. The CAT813 provides an active high RESET output.

There is a secondary supply monitor (PFI) included for power-fail warning.

### Features

- Reset Guaranteed Valid for 1.0 V V<sub>CC</sub>

- 6 µA Supply Current

- 200 ms Reset Pulse Width

- Watchdog Timer Function 1.6 s Timeout

- Accurate Brownout Detection Reset in 3.0, 3.6, and 5.0 Volt Systems

- Secondary Low Supply Monitoring on PFI Input

- Pin and Function Compatible with the MAX705/MAX706/MAX813L Products

- Operating Range from -40°C to +85°C

- SOIC 8-lead and MSOP 8-lead Packages

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant

### **Typical Applications**

- Microprocessor and Microcontroller Based Systems

- Instrument and Control Systems

- Portable Equipment

## **ON Semiconductor®**

http://onsemi.com

**V SUFFIX** CASE 751BD

L

4

Α

Т

Υ

Μ

**Z SUFFIX** CASE 846AD

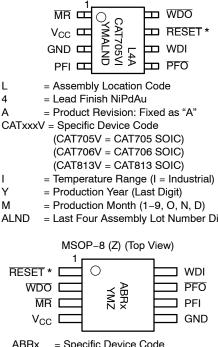

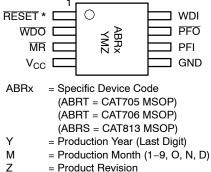

### PIN CONFIGURATIONS AND MARKING DIAGRAMS

SOIC-8 (V) (Top View)

ALND = Last Four Assembly Lot Number Digits

(\* RESET for CAT813)

#### **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

**W.BDTIC.com** © Semiconductor Components Ind April, 2012 - Rev. 7

Publication Order Number: CAT705/D

|  | Figure 1. | Functional | Block Diagram |

|--|-----------|------------|---------------|

|--|-----------|------------|---------------|

| Device | RESET    | RESET    | MR | WDI | WDO | PFI      |

|--------|----------|----------|----|-----|-----|----------|

| CAT705 | @ 4.65 V |          | х  | x   | x   | @ 1.25 V |

| CAT706 | x        |          | х  | x   | x   | @ 1.25 V |

| CAT813 |          | @ 4.65 V | х  | x   | х   | @ 1.25 V |

# www.BDhtp://htemi.comcom/ON/

### **Table 1. PIN FUNCTION DESCRIPTION**

| Pin Name        | Function                                                 |

|-----------------|----------------------------------------------------------|

| MR              | Manual Reset Input                                       |

| V <sub>CC</sub> | Power Supply                                             |

| GND             | Ground                                                   |

| PFI             | Power Fail voltage monitor Input                         |

| PFO             | Power Fail Output                                        |

| WDI             | Watchdog Timer Input                                     |

| RESET           | CMOS Push-Pull Active Low Reset Output (CAT705 & CAT706) |

| RESET           | CMOS Push-Pull Active High Reset Output (CAT813)         |

| WDO             | Watchdog Timer Output                                    |

## Table 2. ABSOLUTE MAXIMUM RATINGS

| Parameters                                                                                                                                         | Ratings                         | Units |

|----------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------|

| Supply Voltage                                                                                                                                     | 6.5                             | V     |

| All other pins                                                                                                                                     | –0.3 to (V <sub>CC</sub> + 0.3) | V     |

| Output Current RESET, RESET, WDO                                                                                                                   | 20                              | mA    |

| Continuous Power Dissipations (T <sub>A</sub> = +70°C)<br>SOIC 8–lead (derate 5.9 mW/°C above +70°C)<br>MSOP 8–lead (derate 4.1 mW/°C above +70°C) | 471<br>330                      | mW    |

| Storage Temperature                                                                                                                                | -65 to 150                      | °C    |

| Lead Soldering (10 seconds max)                                                                                                                    | +300                            | °C    |

| ESD Rating: Human Body Model                                                                                                                       | 2000                            | V     |

| ESD Rating: Machine Model                                                                                                                          | 200                             | V     |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

## Table 3. RECOMMENDED OPERATING CONDITIONS

| Parameter                                  | Rating                          | Unit |

|--------------------------------------------|---------------------------------|------|

| $V_{CC}$ (T <sub>A</sub> = -40°C to +85°C) | 1.0 to 5.5                      | V    |

| All Other Pins                             | –0.1 to (V <sub>CC</sub> + 0.1) | V    |

| Ambient Temperature                        | -40 to +85                      | °C   |

# www.BDhtp://hsemicorcom/ON/

| Table 4. ELECTRICAL OPERATING CHARACTERISTICS (Typical values at T <sub>A</sub> = 25°C and V <sub>CC</sub> = 5 V for CAT705, CAT706 and |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| CAT813 versions. $V_{CC}$ = 3.3 V for the CAT706 T/S versions; $V_{CC}$ = 3.0 V for the CAT706 R version.) (Note 1)                     |

| Parameter                               | Symbol           | Test Conditions                                                                                     | Min                        | Тур  | Max  | Units  |

|-----------------------------------------|------------------|-----------------------------------------------------------------------------------------------------|----------------------------|------|------|--------|

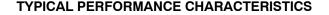

| Supply Current                          | I <sub>CC</sub>  | CAT705, CAT706, CAT813                                                                              |                            | 6    | 17   | μΑ     |

|                                         |                  | CAT706 (R/S/T Versions)                                                                             |                            | 4    | 12   | μΑ     |

| Reset Threshold                         | V <sub>RST</sub> | CAT705 & CAT813 at $-40^{\circ}C \leq T_{A} \leq +85^{\circ}C$                                      | 4.50                       | 4.65 | 4.75 | V      |

|                                         |                  | CAT706 at $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                   | 4.25                       | 4.40 | 4.50 | V      |

|                                         |                  | CAT706T at $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                  | 3.00                       | 3.08 | 3.15 | V      |

|                                         |                  | CAT706S at $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                  | 2.85                       | 2.93 | 3.00 | V      |

|                                         |                  | CAT706R at $-40^{\circ}C \le T_A \le +85^{\circ}C$                                                  | 2.55                       | 2.63 | 2.70 | V      |

| Reset Threshold Tempco (Note 1)         |                  |                                                                                                     |                            | 40   |      | ppm/°C |

| Reset Threshold Hysteresis              |                  | CAT705 & CAT813                                                                                     |                            | 10   |      | mV     |

| (Note 1)                                |                  | CAT706                                                                                              |                            | 5    |      | mV     |

| V <sub>CC</sub> to Reset Delay (Note 2) | t <sub>RD</sub>  | $V_{CC} = V_{TH}$ to ( $V_{TH} - 100$ mV)                                                           |                            | 20   | 1    | μs     |

| Reset Active Timeout Period             | t <sub>RP</sub>  |                                                                                                     | 140                        | 200  | 400  | ms     |

| RESET Output High Voltage               | V <sub>OH</sub>  | CAT705 & CAT706, 4.5 V < V_{CC} < 5.5 V, I_{SOURCE} = –800 $\mu A$                                  | V <sub>CC</sub> –<br>1.5 V |      |      | V      |

|                                         |                  | CAT705 & CAT706, V <sub>RST (max)</sub> <<br>V <sub>CC</sub> < 3.6 V, I <sub>SOURCE</sub> = -500 μA | 0.8 x V <sub>CC</sub>      |      |      |        |

| RESET Output Low Voltage                | V <sub>OL</sub>  | CAT705 & CAT706, 4.5 V < V_{CC} < 5.5 V, I_{SINK} = 3.2 mA                                          |                            |      | 0.4  | V      |

|                                         |                  | CAT705 & CAT706, V <sub>RST (max)</sub> <<br>V <sub>CC</sub> < 3.6 V, I <sub>SINK</sub> = 1.2 mA    |                            |      | 0.3  |        |

|                                         |                  | CAT705 &CAT706, V <sub>CC</sub> = 1 V, $I_{SINK}$ = 100 $\mu$ A                                     |                            |      | 0.3  |        |

| RESET Output High Voltage               | V <sub>OH</sub>  | CAT813, V <sub>CC</sub> = V <sub>RST max</sub> ,<br>I <sub>SOURCE</sub> = -120 μA                   | V <sub>CC</sub> –<br>1.5 V |      |      | V      |

|                                         |                  | CAT813, $V_{CC} = V_{RST max}$ ,<br>I <sub>SOURCE</sub> = -30 $\mu$ A                               | 0.8 x V <sub>CC</sub>      |      |      | 1      |

| RESET Output Low Voltage                | V <sub>OL</sub>  | CAT813, $V_{CC} = V_{RST min}$ , $I_{SINK} = 3.2 \text{ mA}$                                        |                            |      | 0.4  | V      |

|                                         |                  | CAT813, $V_{CC}$ = 1.2 V, $I_{SINK}$ = 100 $\mu$ A                                                  |                            |      | 0.3  |        |

### WATCHDOG INPUT

| Watchdog Timeout Period    | t <sub>WD</sub> |                                             | 1.00                | 1.6 | 2.25                | S  |

|----------------------------|-----------------|---------------------------------------------|---------------------|-----|---------------------|----|

| WDI Pulse Width            | t <sub>WP</sub> | $V_{IL}$ = 0.4 V, $V_{IH}$ = 0.8 x $V_{CC}$ | 50                  |     |                     | ns |

| WDI Input Voltage (Note 3) | VIL             |                                             |                     |     | $0.3 \times V_{CC}$ | V  |

|                            | VIH             |                                             | $0.7 \times V_{CC}$ |     |                     |    |

| WDI Input Current (Note 3) |                 | WDI = V <sub>CC</sub> , Time Average        |                     | 50  | 150                 | μA |

|                            |                 | WDI = 0 V, Time Average                     | -150                | -50 |                     |    |

1. Limits are guaranteed by design and not production tested.

2. The RESET short-circuit current is the maximum pull-up current when reset is driven low by a bidirectional output.

WDI is internally serviced within the watchdog period if WDI is left open.

RESET for CAT705 & CAT706 & RESET for CAT813.

5. Not 100% tested but guaranteed by design.

# www.BDhtp://nemi.com.com/ON/

**Table 4. ELECTRICAL OPERATING CHARACTERISTICS** (Typical values at TA = 25°C and V<sub>CC</sub> = 5 V for CAT705, CAT706 andCAT813 versions. V<sub>CC</sub> = 3.3 V for the CAT706 T/S versions; V<sub>CC</sub> = 3.0 V for the CAT706 R version.) (Note 1)

| Parameter                      | Symbol            | Test Conditions                                                                               | Min                   | Тур                    | Max | Units |

|--------------------------------|-------------------|-----------------------------------------------------------------------------------------------|-----------------------|------------------------|-----|-------|

| WATCHDOG INPUT                 |                   |                                                                                               |                       |                        |     |       |

| WDO Output Voltage             | V <sub>W_OH</sub> | V <sub>RST (max)</sub> < V <sub>CC</sub> < 3.6 V;<br>I <sub>SOURCE</sub> = -500 μA            | 0.8 x V <sub>CC</sub> |                        |     | V     |

|                                |                   | 4.5 V < V <sub>CC</sub> < 5.5 V,<br>I <sub>SOURCE</sub> = -800 μA                             | V <sub>CC</sub> – 1.5 | V <sub>CC</sub> - 0.25 |     |       |

|                                | V <sub>W_OL</sub> | V <sub>RST (max)</sub> < V <sub>CC</sub> < 3.6 V,<br>I <sub>SINK</sub> = +500 μA              |                       |                        | 0.3 |       |

|                                |                   | $4.5 \text{ V} < \text{V}_{CC} < 5.5 \text{ V},$<br>$\text{I}_{\text{SINK}} = 1.2 \text{ mA}$ |                       | 0.1                    | 0.4 |       |

| WDO to WDI setup time (Note 5) | t <sub>WDSU</sub> |                                                                                               | 250                   |                        |     | ns    |

#### MANUAL RESET INPUT

| MR Input Voltage               | VIL               |                 |                     |    | $0.3 \times V_{CC}$ | V  |

|--------------------------------|-------------------|-----------------|---------------------|----|---------------------|----|

|                                | V <sub>IH</sub>   |                 | $0.7 \times V_{CC}$ |    |                     |    |

| MR Pull-up Current             |                   | <u>MR</u> = 0 V | 40                  | 70 | 140                 | μΑ |

| MR Pulse Width                 | t <sub>PB</sub>   |                 | 1                   |    |                     | μs |

| MR Pull-up Resistance          | R <sub>MR</sub>   |                 | 40                  | 60 | 80                  | kΩ |

| MR low to Reset Delay (Note 4) | t <sub>PDLY</sub> |                 |                     |    | 5                   | μs |

### **POWER-FAIL INPUT**

| PFI Input Threshold |                   | $V_{CC} = 5 V$                                                                                                                | 1.2                      | 1.25 | 1.3 | V  |

|---------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|-----|----|

| PFI Input Current   |                   |                                                                                                                               | -25                      | 0.01 | 25  | nA |

| PFO Output Voltage  | V <sub>P_OH</sub> | $\label{eq:VRST(max)} \begin{array}{l} V_{RST(max)} < V_{CC} < 3.6 \text{ V}, \\ I_{SOURCE} = -500 \ \mu\text{A} \end{array}$ | 0.8 x V <sub>CC</sub>    |      |     | V  |

|                     |                   | $4.5 \text{ V} < \text{V}_{CC} < 5.5 \text{ V},$<br>$\text{I}_{SOURCE} = -800 \mu\text{A}$                                    | V <sub>CC</sub> –<br>1.5 |      | 0.4 |    |

|                     | V <sub>P_OL</sub> | $V_{RST (max)} < V_{CC} < 3.6 V,$<br>$I_{SINK} = +1.2 mA$                                                                     |                          |      | 0.3 |    |

|                     |                   | $4.5 \text{ V} < \text{V}_{\text{CC}} < 5.5 \text{ V}, \text{ I}_{\text{SINK}} = 3.2 \text{ mA}$                              |                          |      | 0.4 |    |

Limits are guaranteed by design and not production tested.

The RESET short-circuit current is the maximum pull-up current when reset is driven low by a bidirectional output.

3. WDI is internally serviced within the watchdog period if WDI is left open.

4. RESET for CAT705 & CAT706 & RESET for CAT813.

5. Not 100% tested but guaranteed by design.

# www.BDhr:/hemi.com/ON/

## **FUNCTIONAL DESCRIPTION**

### **Processor Reset**

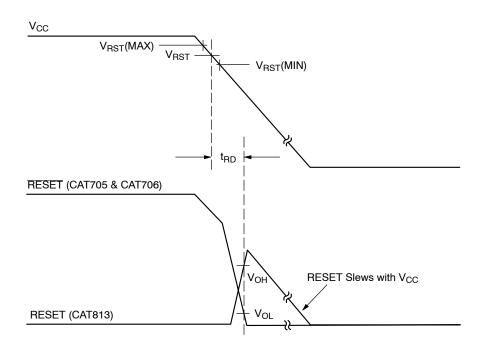

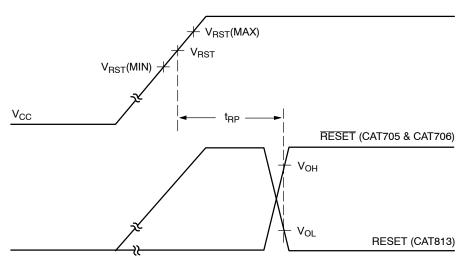

The CAT705, CAT706 & CAT813 detect supply voltage ( $V_{CC}$ ) conditions that are below the specified voltage trip value ( $V_{RST}$ ) and provide a reset output to maintain correct system operation. On power–up, RESET (or RESET for the CAT813) are kept active for a minimum delay  $t_{RP}$  of 140 ms after the supply voltage ( $V_{CC}$ ) rises above  $V_{RST}$  to allow the power supply and processor to stabilize. When  $V_{CC}$  drops below the voltage trip value ( $V_{RST}$ ), the reset output signals RESET (or RESET) are pulled active. RESET (or RESET) is specifically designed to provide the reset input signals for processors. This provides reliable and consistent operation as power is turned on, off or during brownout conditions by maintaining the processor operation in known conditions.

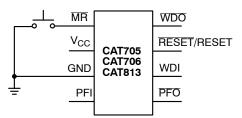

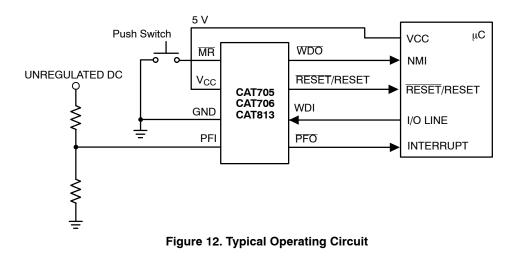

#### Manual Reset

The CAT705, CAT706 & CAT813 each have a Manual Reset ( $\overline{\text{MR}}$ ) input to allow for alternative control of the reset outputs. The  $\overline{\text{MR}}$  input is designed for direct connection to a pushbutton (see Figure 4). The  $\overline{\text{MR}}$  input is internally pulled up by 60 k $\Omega$  resistor and must be pulled low to cause the reset output to go active. Internally, this input is debounced and timed such that  $\overline{\text{RESET}}$  (or RESET) signals of at least 140 ms minimum will be generated. The min 140 ms t<sub>RP</sub> delay commences as the Manual Reset input is released from the low level. (see Figure 5).

Figure 4. Pushbutton RESET

Figure 5. Timing Diagram – Pushbutton RESET

## www.BD<sup>htp://Insemil.com</sup>com/ON/

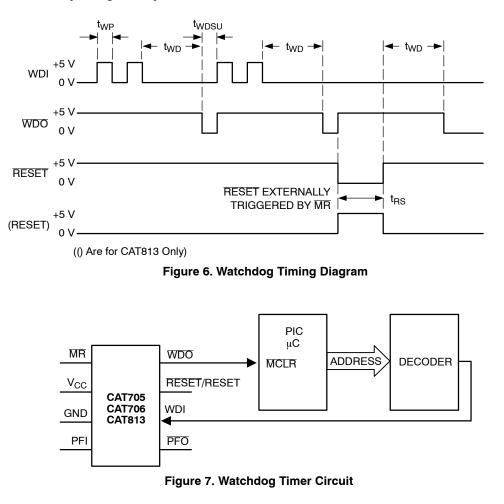

### WATCHDOG TIMER

The CAT705, CAT706, & CAT813 provide a Watchdog input (WDI). The watchdog timer function controls the watchdog output ( $\overline{WDO}$ ) signal and forces the  $\overline{WDO}$  to be low (active) when the WDI input does not have a transition from low-to-high or high-to-low within 1.6 s typical. If a transition occurs on the WDI input pin prior to the watchdog time-out, the watchdog timer is restarted. The timing diagram is shown in Figure 6. The watchdog timer starts as soon as reset condition becomes inactive.

When the  $V_{CC}$  supply drops below the reset threshold, the  $\overline{WDO}$  output becomes active and goes low independently of the watchdog timing stage.

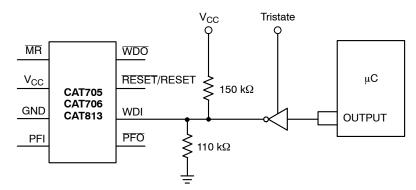

Figure 7 below shows a typical implementation of a watchdog function. Any processor signal that repeats dependant on the normal operation of the processor or directed by the software operating on the processor can be

used to strobe the watchdog input. The most reliable is a dedicated I/O output transitioned by a specific software instruction.

The watchdog can be disabled by floating (or tri–stating) the WDI input (see Figure 8). If the watchdog is disabled the WDI pin will be pulled low for the first  $7/8^{\text{th}}$ 's of the watchdog period ( $t_{WD}$ ) and pulled high for the last  $1/8^{\text{th}}$  of the watchdog period. This pulling low of the WDI input and then high is used to detect an open or tri–state condition and will continue to repeat until the WDI input is driven high or low.

For most efficient operation of devices with the watchdog function the WDI input should be held low the majority of the time and only strobed high as required to reset the watchdog timer.

## www.BDhtp://insemil.com ON/

Figure 10. Timing Diagram – Power Up

# www.BDhtp://htemi.comcom/ON/

## **APPLICATION NOTES**

### µP's with Bidirectional Reset Pins

The RESET output can be pulled low by processors like the 68HC11 allowing for a system reset issued by the processor. The maximum pullup current that can be sourced by the CAT705 & CAT706 1.5 mA (and by the CAT706 T/R/S is 800  $\mu$ A) allowing the processor to pull the output low even when the CAT70x is pulling it high.

### **Power Transients**

Generally short duration negative–going transients of less than 2  $\mu$ s on the power supply at V<sub>RST</sub> minimum will not cause a reset condition. However the lower the voltage of the transient the shorter the required time to cause a reset output.

These issues can usually be remedied by the proper location of bypass capacitance on the circuit board.

## **Output Valid Conditions**

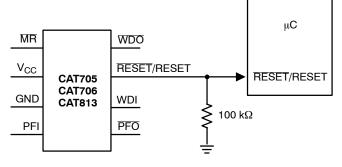

The RESET output uses a push-pull output which can maintain a valid output down to a  $V_{CC}$  of 1.0 volts. To sink current below 0.8 V a resistor can be connected from RESET to Ground (see Figure 11.) This arrangement will maintain a valid value on the RESET output during both power up and down but will draw current when the RESET output is in the high state. A resistor value of about 100 k $\Omega$  should be adequate in most situations to maintain a low condition valid output down to  $V_{CC}$  equal to 1.0 V.

Figure 11. RESET Valid for V<sub>CC</sub> < 1.0 V

## www.BDhtp://hsemi.comcom/ON/

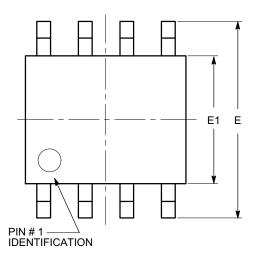

## PACKAGE DIMENSIONS

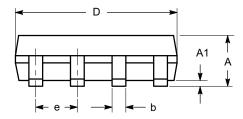

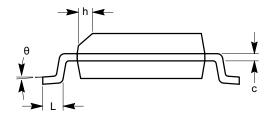

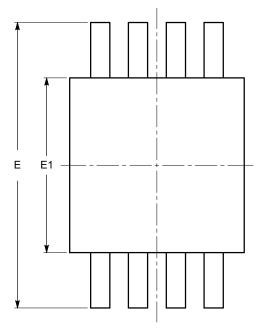

SOIC 8, 150 mils CASE 751BD-01 ISSUE O

| SYMBOL | MIN  | NOM      | MAX  |

|--------|------|----------|------|

| А      | 1.35 |          | 1.75 |

| A1     | 0.10 |          | 0.25 |

| b      | 0.33 |          | 0.51 |

| с      | 0.19 |          | 0.25 |

| D      | 4.80 |          | 5.00 |

| E      | 5.80 |          | 6.20 |

| E1     | 3.80 |          | 4.00 |

| е      |      | 1.27 BSC |      |

| h      | 0.25 |          | 0.50 |

| L      | 0.40 |          | 1.27 |

| θ      | 0°   |          | 8°   |

TOP VIEW

SIDE VIEW

## Notes:

(1) All dimensions are in millimeters. Angles in degrees.

(2) Complies with JEDEC MS-012.

END VIEW

# www.BDhtp://thsemi.comcom/ON/

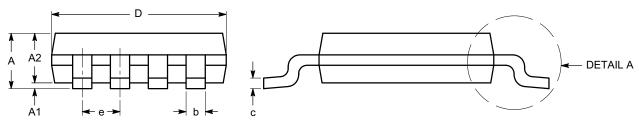

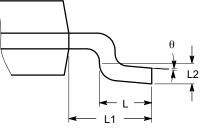

## PACKAGE DIMENSIONS

MSOP 8, 3x3 CASE 846AD-01 ISSUE O

TOP VIEW

| SYMBOL | MIN      | NOM  | МАХ  |  |  |

|--------|----------|------|------|--|--|

| А      |          |      | 1.10 |  |  |

| A1     | 0.05     | 0.10 | 0.15 |  |  |

| A2     | 0.75     | 0.85 | 0.95 |  |  |

| b      | 0.22     |      | 0.38 |  |  |

| с      | 0.13     |      | 0.23 |  |  |

| D      | 2.90     | 3.00 | 3.10 |  |  |

| E      | 4.80     | 4.90 | 5.00 |  |  |

| E1     | 2.90     | 3.00 | 3.10 |  |  |

| е      | 0.65 BSC |      |      |  |  |

| L      | 0.40     | 0.60 | 0.80 |  |  |

| L1     | 0.95 REF |      |      |  |  |

| L2     | 0.25 BSC |      |      |  |  |

| θ      | 0° 6°    |      |      |  |  |

www.BDhtp://fremi.com.com

SIDE VIEW

END VIEW

### Notes:

- (1) All dimensions are in millimeters. Angles in degrees.

- (2) Complies with JEDEC MO-187.

## Example of Ordering Information (Notes 6 - 8)

| Order Number  | Voltage | Top Mark | Manual Reset | Reset Output | Package | Quantity per<br>Reel (Note 9) |

|---------------|---------|----------|--------------|--------------|---------|-------------------------------|

| CAT705VI-GT3  | 4.65    | CAT705V  | Yes          | LOW          | SOIC-8  |                               |

| CAT705ZI-GT3  |         | ABRT     |              |              | MSOP-8  |                               |

|               |         |          |              |              | -       |                               |

| CAT706RVI-GT3 | 0.60    | CAT706V  | Yes          | LOW          | SOIC-8  | 3,000                         |

| CAT706RZI-GT3 | 2.63    | ABRT     | res          |              | MSOP-8  |                               |

| CAT706SVI-GT3 | 0.00    | CAT706V  |              | LOW          | SOIC-8  |                               |

| CAT706SZI-GT3 | 2.93    | ABRT     | Yes          |              | MSOP-8  |                               |

| CAT706TVI-GT3 | 3.08    | CAT706V  |              | LOW          | SOIC-8  |                               |

| CAT706TZI-GT3 |         | ABRT     | Yes          |              | MSOP-8  |                               |

| CAT706VI-GT3  | 4.40    | CAT706V  | No           | LOW          | SOIC-8  |                               |

| CAT706ZI-GT3  |         | ABRT     | Yes          |              | MSOP-8  |                               |

|               |         |          |              |              |         |                               |

| CAT813VI-GT3  | 4.65    | CAT813V  | Yes          | HIGH         | SOIC-8  |                               |

| CAT813ZI-GT3  |         | ABRS     |              |              | MSOP-8  |                               |

6. All packages are RoHS-compliant (Lead-free, Halogen-free).

7. The standard lead finish is NiPdAu.

8. Contact factory for package availability.

9. For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

ON Semiconductor and I are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other application in which the BSCILLC product create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death agsociated with such unintended or unauthorized use, ever if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

#### PUBLICATION ORDERING INFORMATION

### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303–675–2175 or 800–344–3860 Toll Free USA/Canada Fax: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com N. American Technical Support: 800–282–9855 Toll Free USA/Canada Europe, Middle East and Africa Technical Support:

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

www.BDTIC.com/ON/

Phone: 421 33 790 2910

Phone: 81-3-5817-1050

Japan Customer Focus Center