# LV71402RA

Advance Information

**Bi-CMOS LSI**

# 1.5A, 2-Cell Li-ion Battery DC-DC USB Charger

3 Current Modes (500 mA / 900 mA / 1.5 A)

# Overview

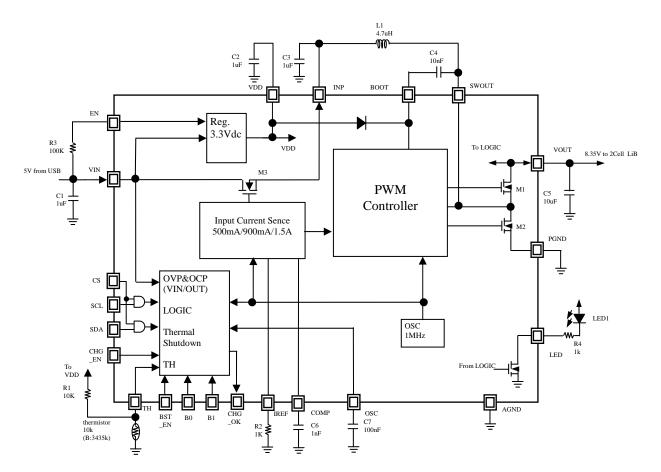

The LV71402RA is a 1ch DC-DC boost converter which is suitable for charge control usage such as charging 2Cell Li-ion battery (e.g. D-SLR, DVC) from USB port. Since it is corresponding to 3 current modes (500mA/900mA/1.5A) from the port, when it determines that there is no current capability on the port, it will automatically set suppliable current mode. By having a variety of internal protection circuits, inrush current generated by connecting/removing USBs or Li-ion batteries can be controlled – Enables safe charging.

LV71402RA also has an internal mode that is not only used as Li-ion battery charger, but also as a VOUT=8.35V Fixed boost converter which will enable set driving without batteries.

#### Function

- 1ch Synchronous boost converter (Internal FET)

- LDO Trickle charge at Low voltage

- 3-mode-compatible USB supply current (500mA/900mA/1.5A)

- USB Supply current capability auto-detection

- Internal Soft start function (Current slope : 10msec)

- Automatic recharging function

- (Recharges when VOUT is below 7.8V after judged as fully-charged )

- Switching frequency 1MHz/2MHz Switching function

- Charge/Boost Mode switching function

- LED Pin/CHG\_OK Pin for Charging condition check

- Input voltage operation range : 4.0 to 6.0V

- Current at Shutdown < 1uA

- Full-charged voltage : 8.35V±0.5%

- High efficiency charge 93%

- Charging inception Anomaly detection

- (2 hours of LDO Trickle charge will set Standby mode)

- I/O over-voltage protection OVP

- I/O over-current protection OCP

- Thermal Shutdown

- Thermistor temperature detection

- Pin control/I<sup>2</sup>C bus control selectable

FLGA32(3.5X3.5)

This document contains information on a new product. Specifications and information herein are subject to change without notice.

\* I<sup>2</sup>C Bus is a trademark of Philips Corporation.

# Specifications

#### Absolute Maximum Ratings at $Ta = 25^{\circ}C$

| PARAMETER                   | SYMBOL   | CONDITION                                                          | RATING       | UNIT |

|-----------------------------|----------|--------------------------------------------------------------------|--------------|------|

| Supply voltage              | VINmax   | VIN                                                                | –0.3 to 9.0  | V    |

|                             | VPINmax1 | B0,B1,CHG_EN,BST_EN,TH,SDA,<br>SCL,CS,VDD,IREF,OSC,COMP,<br>CHG_OK | -0.3 to 4.0  | v    |

| Pin voltage                 | VPINmax2 | EN,LED,INP                                                         | -0.3 to 9.0  | V    |

|                             | VPINmax3 | SWOUT,VOUT                                                         | -0.3 to 10.0 | V    |

|                             | VPINmax4 | BOOT                                                               | -0.3 to 14.0 | V    |

| Allowable power consumption | Pd max   | With a designated board *1                                         | 1.8          | W    |

| Operating temperature       | Topr     |                                                                    | -20 to +85   | °C   |

| Storage temperature         | Tstg     |                                                                    | -40 to +125  | °C   |

| Junction temperature        | Tjmax    |                                                                    | +150         | °C   |

\*1 : Designated board : 60×60×1.6 mm 2S2P\_Glass epoxy

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

#### Recommended Operating Conditions at $Ta = 25^{\circ}C$

| PARAMETER            | SYMBOL | CONDITION | RATING     | UNIT |

|----------------------|--------|-----------|------------|------|

| Supply-voltage range | VIN    |           | 4.0 to 6.0 | V    |

# **Electrical Characteristics** at Ta = 25°C, VIN = 5.0V

| T_EN,                  |

|------------------------|

| · · _ <b>_ · · ·</b> · |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

|                        |

| )                      |

|                        |

| 2)                     |

|                        |

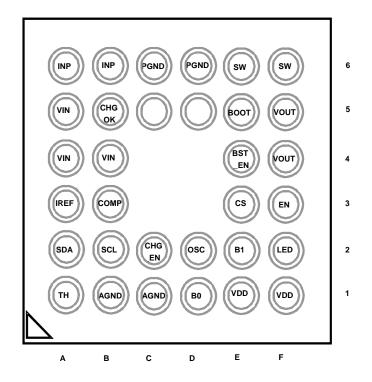

# PIN CONFIGURATION (Top view)

# **PIN FUNCTIONS**

| No.      | PIN NAME | DESCRIPTION                                                                                                                                                                                                                                    |

|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| E1,F1    | VDD      | Regulator output pin. Provides stable voltage of 3.3V from VIN power supply.                                                                                                                                                                   |

| A4,A5,B4 | VIN      | Pin to provide 5V from USB port.                                                                                                                                                                                                               |

| A6,B6    | INP      | Converter power supply pin after Input Current Limit FET (M3).                                                                                                                                                                                 |

| D1       | B0       | Logic input pin to determine the input current limitation.                                                                                                                                                                                     |

| E2       | B1       | Logic input pin to determine the input current limitation.                                                                                                                                                                                     |

| A3       | IREF     | Programmed current of the input current limitation. Connect a resistor in between this pin and GND to determine the input current value.                                                                                                       |

| C2       | CHG_EN   | Charge Enable Input.<br>L = Stop charging operation H = Charging operation                                                                                                                                                                     |

| F3       | EN       | This ICs Enable pin. When EN pin is "H", VDD powers up and I <sup>2</sup> C registers are ready for communication.                                                                                                                             |

| F4,F5    | VOUT     | Boost output pin. Boosted voltage will be generated by the converter operation. Executes charging<br>by connecting a battery in between this pin and PGND. Also Connects 10µF capacitor in parallel with<br>the battery.                       |

| E5       | BOOT     | Hi-side gate voltage driving pin of a converter. Connect capacitor in between SWOUT and BOOT pins.                                                                                                                                             |

| E6,F6    | SWOUT    | Switching operation pin of a converter.                                                                                                                                                                                                        |

| D2       | OSC      | Capacitor connecting pin for timing clock of an internal logic. The clock is set to 32Hz with a 0.1uF ceramic capacitor.                                                                                                                       |

| B3       | COMP     | GM amp phase compensating pin. Phase compensation R embedded.<br>Determines time constant of GM Amp by its external capacity value.                                                                                                            |

| E3       | CS       | I <sup>2</sup> C interface enable input pin. When CS pin is "H", I <sup>2</sup> C_data can be accepted.                                                                                                                                        |

| F2       | LED      | Output pin to light up LED while charging the battery.                                                                                                                                                                                         |

| B1,C1    | AGND     | Analog Ground                                                                                                                                                                                                                                  |

| C6,D6    | PGND     | Power Ground                                                                                                                                                                                                                                   |

| A1       | ТН       | Thermistor input pin. Connect a NTC Thermistor from TH to GND. Connect a $10k\Omega$ resistor from TH to VDD. Charging is suspended when TH $\ge 2.4V$ and TH $\le 0.78V$ .<br>Set externals OPEN when not using temperature sensing function. |

| B5       | CHG OK   | Logic output pin. This will be "H" when fully-charged.                                                                                                                                                                                         |

| A2       | SDA      | I <sup>2</sup> C data input pin.                                                                                                                                                                                                               |

| B2       | SCL      | I <sup>2</sup> C clock input pin.                                                                                                                                                                                                              |

| E4       | BST_EN   | Charging/Boosting mode switching pin.<br>"L" = Charge mode, "H" = Boost mode.                                                                                                                                                                  |

Total : 30PINS

# **BLOCK DIAGRAM**

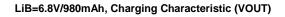

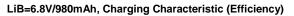

# **TYPICAL CHARACTERISTICS**

(VIN = 5V, CIN = 1 $\mu$ F, CINP = 1 $\mu$ F, CVDD = 1 $\mu$ F, COUT = 10 $\mu$ F, LOUT = 4.7 $\mu$ H, Ta = +25°C)

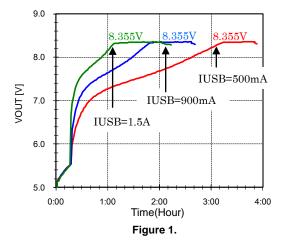

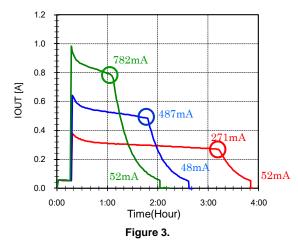

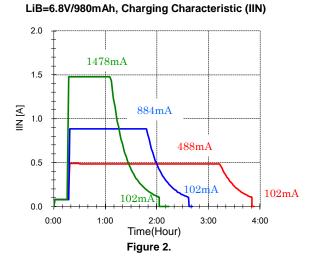

#### LiB=6.8V/980mAh, Charging Characteristic (IOUT)

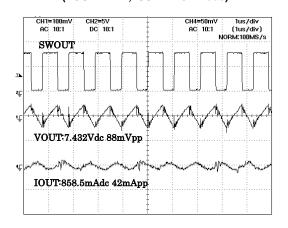

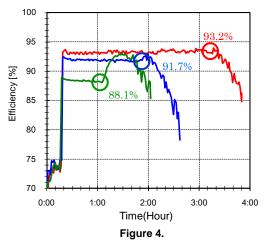

CC Mode Switching Waveform (VOUT = 7.4V, IUSB = 1.5A Mode)

Figure 5.

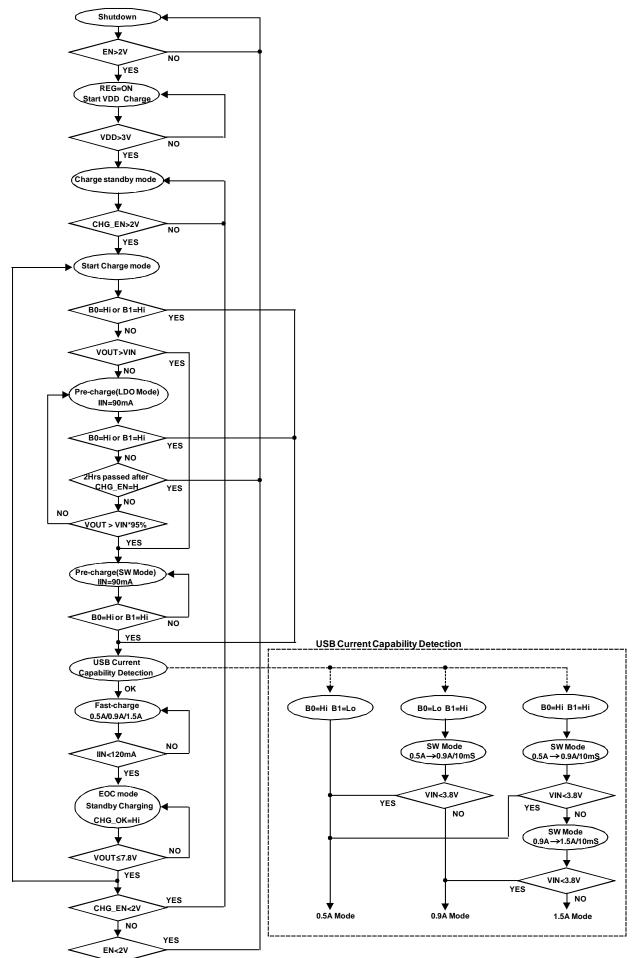

USB Current Capability Detection Waveform (USB Supply Current = 0.7A, IUSB = 0.9A Mode)

Figure 6.

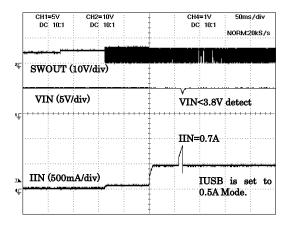

## **FLOW CHART**

# ABOUT I<sup>2</sup>C-BUS

1. A Method of data transfer

This IC has adopted Serial data controlling method (I<sup>2</sup>C-BUS) and controls with SCL and SDA pins, and CS pin for noise suppression. When CS pin is "H", I<sup>2</sup>C interface accepts data transfer of SCL and SDA. When CS pin is "L", I<sup>2</sup>C interface doesn't accept them. If CS pin is not used, it must be pulled up to VDD pin. A Method of data transfer is below. First, set Data transfer start condition (\*1) by using these two pins, then input 8-bit data to SDA pin. This 8-bit data needs to be synchronized to SCL pin clock. It is necessary to start transferring from MSB (Most Significant Bit) side. The 9<sup>th</sup>-bit is going to be the ACK (Data transfer acknowledge) period, and while SCL pin is "H", this IC will "Pull-down" an SDA pin. After transferring necessary data, complete transferring by setting End of data transfer condition (\*2) by using two pins.

\*1) Define by falling SDA while SCL is in "H" period.

\*2) Define by rising SDA while SCL is in "H" period.

#### 2. Data transfer format

After transferring the Start condition, transfer Slave address, followed by sub-address, control data, Ending condition to the SDA pin (See Diagram 1). Since this IC does not have Auto address increment function, Slave address, Sub-address, and Control data must be transferred as a set. The slave-address is configured in 7-bit with having its 8<sup>th</sup>-bit as a READ/WRITE setting bit. Therefore, set "L" at WRITE mode, and set "H" at READ mode.

#### Write Mode

|   | STA                                                       | IC-ADD           | R/W       | Α   | SUB-ADD  | Α         | DATA           | Α        | STO      |  |

|---|-----------------------------------------------------------|------------------|-----------|-----|----------|-----------|----------------|----------|----------|--|

| - | STA : Start Condition STO : Stop Condition A [1Bit] : ACK |                  |           |     |          |           |                |          |          |  |

|   | IC-A                                                      | .DD [7Bit] : Sla | ave addre | SS  | R/V      | V[1Bit]   | : Read/Write(R | lead:1/\ | Nrite:0) |  |

|   | SUB                                                       | -ADD [8Bit] :    | Sub addre | ess | DATA [88 | Bit] : Da | ata Bits       |          |          |  |

|   |                                                           |                  |           |     |          |           |                |          |          |  |

#### • Read Mode

|                               | STA | IC-ADD | R/W | Α | STATUS1 | Α | STATUS2 | Α | STO |

|-------------------------------|-----|--------|-----|---|---------|---|---------|---|-----|

| STATUS1/2[8Bit] : Status Bits |     |        |     |   |         |   |         |   |     |

#### Diagram 1 : Data configuration diagram

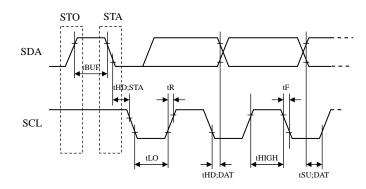

# 3. Input Timing

Transfer Input data in a timing shown in Diagram 2 (See Table 1).

STA : Start Condition STO : Stop Condition

#### Diagram 2 : Input timing

#### Table 1 : Electrical characteristics at Ta = 25 °C

|                                       |         | STAN | DARD | HIGH SPEE    | Ð    |      |

|---------------------------------------|---------|------|------|--------------|------|------|

| PARAMETER                             | SYMBOL  |      | max. | min.         | max. | UNIT |

| SCL Frequency                         | FSCL    | 0    | 100  | 0            | 400  | kHz  |

| BUS free time between stop - start    | tBUF    | 4.7  | -    | 1.3          | -    | μs   |

| HOLD time of start, restart condition | tHD;STA | 4.0  | -    | 0.6          | -    | μs   |

| L time of SCL                         | tLOW    | 4.7  | -    | 1.3          | -    | μs   |

| H time of SCL                         | tHIGH   | 4.0  | -    | 0.6          | -    | μs   |

| Set-up time of restart condition      | tSU;STA | 4.7  | -    | 0.6          | -    | μs   |

| HOLD time of SDA                      | tHD;DAT | 0    | -    | 0            | 0.9  | μs   |

| Set-up time of SDA                    | tSU;DAT | 250  | -    | 100          | -    | ns   |

| Rising time of SDA, SCL               | tR      | -    | 1000 | 20+0.1Cb(*3) | 300  | ns   |

| Falling time of SDA, SCL              | tF      | -    | 300  | 20+0.1Cb(*3) | 300  | ns   |

\*3) Cb : Total capacitance of one BUS line (unit : pF)

# I<sup>2</sup>C-BUS REGISTER MAP

WRITE : IC Address: 10111010

| E.m.e | SUB     | MSB     |                              |         |            |                  |          |           | LSB      |

|-------|---------|---------|------------------------------|---------|------------|------------------|----------|-----------|----------|

| Func. | ADDRESS | [7]     | [6]                          | [5]     | [4]        | [3]              | [2]      | [1]       | [0]      |

| CTL1  | 0       | CHG_BUS | CHG_EN                       | BST_BUS | BST_EN     | PWM_FREQ         | IUSB_BUS | IUSB[1:0] |          |

| CILI  | 0       | 0       | 0                            | 0       | 0          | 0                | 0        | 0         | 0        |

| CTL2  | 1       | VRECH   | IG[1:0]                      | EOC[1   | :0]        | SWPCI            | HG[1:0]  | LDOPO     | CHG[1:0] |

| CILZ  | I       | 1       | 0                            | 0       | 0          | 0                | 0        | 0         | 0        |

| CTL3  | 2       | ERR_L   | ED[1:0]                      |         |            |                  |          |           |          |

| CILS  | 2       | 1       | 0                            | 0       | 0          | 0                | 0        | 0         | 0        |

|       | 3       |         |                              |         |            |                  |          |           |          |

|       | 5       | 0       | 0                            | 0       | 0          | 0                | 0        | 0         | 0        |

| TEST1 | 4       |         | TEST MODE (WRITE prohibited) |         |            |                  |          |           |          |

| TEST2 | 5       |         |                              | TES     | ST MODE (V | VRITE prohibited | d)       |           |          |

| TEST3 | 6       |         |                              | TES     | ST MODE (V | VRITE prohibited | d)       |           |          |

| TEST4 | 7       |         |                              | TES     | ST MODE (V | VRITE prohibited | (t       |           |          |

| TEST5 | 8       |         |                              | TES     | ST MODE (V | VRITE prohibited | (t       |           |          |

| TEST6 | 9       |         | TEST MODE (WRITE prohibited) |         |            |                  |          |           |          |

| TEST7 | 10      |         | TEST MODE (WRITE prohibited) |         |            |                  |          |           |          |

| TEST8 | 11      |         | TEST MODE (WRITE prohibited) |         |            |                  |          |           |          |

| TEST9 | 12      |         | TEST MODE (WRITE prohibited) |         |            |                  |          |           |          |

READ : IC Address: 10111011

| Function | MSB    |     |        |       |          |          |         | LSB   |

|----------|--------|-----|--------|-------|----------|----------|---------|-------|

|          | [7]    | [6] | [5]    | [4]   | [3]      | [2]      | [1]     | [0]   |

| READ1    | CHG_OK | ERR | VIN_LO | UVLO  | VIN_OVP  | VOUT_OVP | VIN_OCP | LDO2H |

| READ2    | TH     | TSD | LDO_PG | SW_PG | BST_MODE | CHG_MODE | IUSB_   | MODE  |

# I<sup>2</sup>C-BUS Registers

WRITE : IC Address: 10111010

| SUB_<br>ADDRESS | Bit                    | Name         | Init                                                                     | DESCRIPTION                                                                                                                  |

|-----------------|------------------------|--------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|

|                 | [7]                    | CHG_BUS      | 0b                                                                       | Pin/I <sup>2</sup> C Control : <b>0b = CHG_EN Pin control</b> , 1b = I <sup>2</sup> C control                                |

|                 | [6]                    | CHG_EN       | 0b                                                                       | Charge Enable (When CHG_BUS = 1b) :<br><b>0b = Charge disable</b> , 1b = Charge enable                                       |

|                 | [5]                    | BST_BUS      | 0b                                                                       | $Pin/I^2C$ Control : <b>0b = BST_EN Pin control</b> , 1b = $I^2C$ control                                                    |

| 0 [CTL1]        | [4]                    | BST_EN       | 0b                                                                       | Boost Mode Enable (When BST_BUS=1b) :<br><b>0b = Charge mode,</b> 1b = Boost mode.                                           |

|                 | [3]PWM_FREQ[2]IUSB_BUS | 0b           | PWM Frequency : <b>0b = 1MHz</b> , 1b = 2MHz                             |                                                                                                                              |

|                 |                        | 0b           | $Pin/l^2C$ Control : <b>0b = B1/B0 Pin control</b> , 1b = $l^2C$ control |                                                                                                                              |

|                 | [1]                    |              | 00b                                                                      | USB Input Current Limit (When IUSB_BUS=1b) :<br>00b = LDOPCHG/SWPCHG Set value                                               |

|                 | [0]                    | IUSB[1:0]    |                                                                          | 01b = 500mA, $10b = 900mA$ , $11b = 1500mA$                                                                                  |

|                 | [7]                    | VRECHG[1:0]  | 10b                                                                      | Battery Recharge Voltage :                                                                                                   |

|                 | [6]                    |              |                                                                          | 00b = 7.0V, 01b = 7.4V, <b>10b = 7.8V</b> , 11b = Not Recharging                                                             |

|                 | [5]                    | EOC[1:0]     | 00b                                                                      | End Of Charge (Input current is detected at IIN)                                                                             |

| 1 [CTL2]        | [4]                    | 200[1.0]     | 000                                                                      | <b>00b = 120mA</b> , 01b = 150mA, 10b = 180mA, 11b = 210mA                                                                   |

|                 | [3]                    | SWPCHG[1:0]  | 00b                                                                      | Pre-Charge Current Limit (SW Mode) :                                                                                         |

|                 | [2]                    |              | 000                                                                      | <b>00b = 90mA</b> , 01b = 120mA, 10b = 150mA, 11b = 180mA                                                                    |

|                 | [1]                    | LDOPCHG[1:0] | 00b                                                                      | Pre-Charge Current Limit (LDO Mode) :                                                                                        |

|                 | [0]                    |              | 000                                                                      | <b>00b = 90mA</b> , 01b = 120mA, 10b = 150mA, 11b = 180mA                                                                    |

| 2 (CTI 2)       | [7]                    |              | 10b                                                                      | LED display at Anomaly detection (Charge suspend)<br>00b = Lights-out, 01b = blinking at 2Hz, <b>10b = blinking at 4Hz</b> , |

| 2 [CTL3]        | [6]                    | ERR_LED[1:0] | 100                                                                      | 11b = Lights-on                                                                                                              |

#### READ : IC Address : 10111011

|       | Bit        | Name      | DESCRIPTION                                                                                                                |

|-------|------------|-----------|----------------------------------------------------------------------------------------------------------------------------|

|       | [7]        | CHG_OK    | End of charge Detection : 0b = Not End of charge, 1b = End of charge                                                       |

|       | [6]        | ERR       | Charge Error : 0b = Not Error, 1b = Error (When protection circuits work)                                                  |

| READ1 | [5]        | VIN_LO    | VIN Low Voltage Detection : 0b = VIN>3.8V, 1b = VIN<3.8V                                                                   |

|       | [4]        | UVLO      | VDD Low Voltage Detection : 0b = VDD>2.8V, 1b = VDD<2.8V                                                                   |

|       | [3]        | VIN_OVP   | VIN Over Voltage Detection : 0b = VIN<6.3V, 1b = VIN>6.3V                                                                  |

|       | [2]        | VOUT_OVP  | VOUT Over Voltage Detection : 0b = VOUT<9V, 1b = VOUT>9V                                                                   |

|       | [1]        | VIN_OCP   | VIN Over Current Detection : 0b = VIN Current< 2A, 1b = VIN Current > 2A                                                   |

|       | [0]        | LDO2H     | LDO Mode Safety Timer Detection : 0b = LDO Mode<2hrs, 1b = LDO Mode>2hrs                                                   |

|       | [7]        | TH        | Thermistor Sense Detection : 0b = Normal Charge, 1b = Thermistor Cold/Hot<br>Temperature                                   |

|       | [6]        | TSD       | Thermal Shutdown Detection : 0b = Tj <140°C, 1b = Tj >160°C                                                                |

|       | [5]        | LDO_PG    | VOUT Voltage Detection 1 : 0b = VOUT <vin*95%, 1b="VOUT">VIN*95%</vin*95%,>                                                |

| READ2 | [4]        | SW_PG     | VOUT Voltage Detection 2 : 0b = VOUT<7.8V, 1b = VOUT>7.8V                                                                  |

|       | [3]        | BST_MODE  | Boost Mode : 0b = Charge Mode, 1b = Boost Mode                                                                             |

|       | [2]        | CHG_MODE  | Charge Mode : 0b = LDO Mode, 1b = SW Mode                                                                                  |

|       | [1]<br>[0] | IUSB_MODE | USB Input Current Limit Condition (Internal Logic Condition) :<br>00b = Pre-Charge, 01b = 500mA, 10b = 900mA, 11b = 1500mA |

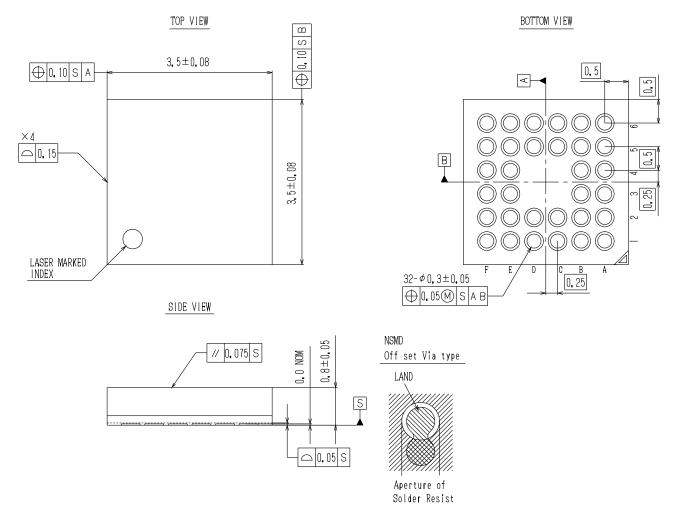

#### **Package Dimension**

FLGA32(3.5X3.5) unit : mm

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemify and hold SCILLC and its officers, employees, subsidiaries, affliates, and feastributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright have and is not for resale in any manner.