# Automotive Grade Non-Synchronous Buck Controller

The NCV885300 is an adjustable-output non-synchronous buck controller which drives an external P-channel MOSFET. The device uses peak current mode control with internal slope compensation. The IC incorporates an internal regulator that supplies charge to the gate driver.

Protection features include internal soft-start, undervoltage lockout, cycle-by-cycle current limit, hiccup-mode overcurrent protection, hiccup-mode short-circuit protection.

Additional features include: power good signal, low quiescent current sleep mode and externally synchronizable switching frequency.

#### **Features**

- Ultra Low Iq Sleep Mode

- Adjustable Output with 800 mV ±2.0% Reference Voltage

- Wide Input of 3.1 to 44 V with Undervoltage Lockout (UVLO)

- Power Good (PG)

- Internal Soft-Start (SS)

- Fixed-Frequency Peak Current Mode Control

- Internal Slope Compensating Artificial Ramp

- Internal High-Side PMOS Gate Driver

- Regulated Gate Driver Current Source

- External Frequency Synchronization (SYNC)

- Programmable Cycle-by-Cycle Current Limit (CL)

- Hiccup Overcurrent Protection (OCP)

- Output Short Circuit Hiccup Protection (SCP)

- Space-Saving 8-PIN SOIC Package

- NCV Prefix for Automotive and Other Applications Requiring Unique Site and Control Change Requirements; AEC-Q100 Qualified and PPAP Capable

1

• These Devices are Pb-Free and are RoHS Compliant

## ON Semiconductor®

http://onsemi.com

### MARKING DIAGRAM

SOIC-8 SUFFIX D CASE 751

V885300 = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

= Pb-Free Package

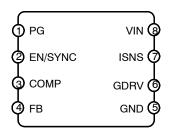

#### **PINOUT DIAGRAM**

#### **ORDERING INFORMATION**

| Device         | Package             | Shipping <sup>†</sup> |

|----------------|---------------------|-----------------------|

| NCV885300D1R2G | SOIC-8<br>(Pb-Free) | 2500/Tape & Reel      |

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specification Brochure, BRD8011/D.

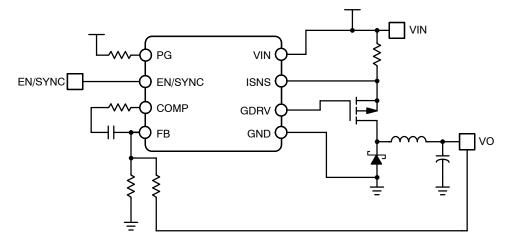

Figure 1. NCV885300 Application Diagram

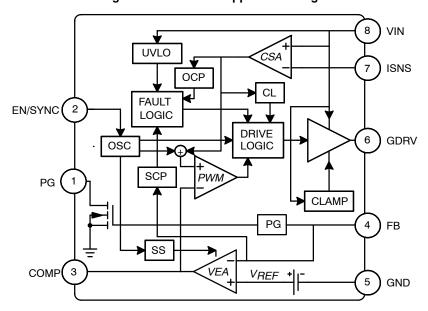

Figure 2. NCV885300 Simple Block Diagram

# **PIN DESCRIPTIONS**

| No | Pin Symbol | Function                                                                                                                                                                                               |

|----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | PG         | Power good output. Use a pull-up resistor to 5.0 V. PG is pulled low when power is not good.                                                                                                           |

| 2  | EN/SYNC    | Enable and synchronization input. The falling edge synchronizes the internal oscillator. The part is disabled into sleep mode when this pin is brought low for longer than the enable time-out period. |

| 3  | COMP       | Output of the voltage error amplifier. An external compensator network from COMP to GND is used to stabilize the converter and tailor transient performance.                                           |

| 4  | FB         | Output voltage feedback. A resistor from the output voltage to FB with another resistor from FB to GND creates a voltage divider for regulation and programming of the output voltage.                 |

| 5  | GND        | Ground reference.                                                                                                                                                                                      |

| 6  | GDRV       | Gate driver output. Connect to gate of the external P-channel MOSFET. A series resistance can be added from GDRV to the gate to tailor EMC performance.                                                |

| 7  | ISNS       | Current sense input. Connect this pin to the source of the external P-channel MOSFET, through a current-sense resistor to VIN to sense the switching current for regulation and current limiting.      |

| 8  | VIN        | Main power input for the IC.                                                                                                                                                                           |

### MAXIMUM RATINGS (Voltages are with respect to GND unless otherwise indicated.)

| Rating                                                                | Value       | Unit |

|-----------------------------------------------------------------------|-------------|------|

| DC Voltage (VIN, ISNS, GDRV)                                          | -0.3 to 44  | V    |

| Peak Transient Voltage (Load Dump on VIN)                             | 44          | V    |

| DC Voltage (EN/SYNC, PG)                                              | -0.3 to 6.0 | V    |

| DC Voltage (COMP, FB)                                                 | -0.3 to 3.6 | V    |

| DC Voltage Stress (VIN – GDRV)                                        | -0.7 to 12  | V    |

| Operating Junction Temperature Range                                  | -40 to 150  | °C   |

| Storage Temperature Range                                             | -65 to 150  | °C   |

| Peak Reflow Soldering Temperature: Pb-Free 60 to 150 seconds at 217°C | 265         | °C   |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# **PACKAGE ATTRIBUTES**

| Characteristic                                                    | Value                      |  |  |

|-------------------------------------------------------------------|----------------------------|--|--|

| ESD Capability Human Body Model Machine Model Charge Device Model | 2.0 kV<br>200 V<br>>1.0 kV |  |  |

| Moisture Sensitivity Level                                        | MSL 1 260°C                |  |  |

| Package Thermal Resistance Junction–to–Ambient, $R_{\theta JA}$   | 100°C/W                    |  |  |

**ELECTRICAL CHARACTERISTICS** ( $V_{IN} = 3.4 \text{ V}$  to 36 V, EN = 5 V. Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.)

| Characteristic                     | Symbol                | Conditions                                                           | Min  | Тур   | Max  | Unit  |

|------------------------------------|-----------------------|----------------------------------------------------------------------|------|-------|------|-------|

| GENERAL                            |                       |                                                                      |      |       |      |       |

| Quiescent Current                  | I <sub>q,sleep</sub>  | V <sub>IN</sub> = 13.2 V, EN = 0 V, Sleep Mode                       |      | 2.5   | 6.0  | μΑ    |

|                                    | I <sub>q,off</sub>    | $V_{IN}$ = 13.2 V, EN = 5 V or toggled, $V_{FB}$ = 1 V, No Switching |      | 2.0   | 3.0  | mA    |

|                                    | I <sub>q,on</sub>     | $V_{IN}$ = 13.2 V, EN = 5 V or toggled, $V_{FB}$ = 0 V, Switching    |      | 3.0   | 5.0  | mA    |

| Undervoltage Lockout               | $V_{uvlo}$            | V <sub>IN</sub> decreasing                                           | 2.9  | 3.1   | 3.3  | V     |

| Undervoltage Lockout<br>Hysteresis | V <sub>uvlo,hys</sub> |                                                                      | 50   | 150   | 300  | mV    |

| Overvoltage Lockout                | V <sub>ovlo</sub>     |                                                                      | 36.9 | 38    | 39.3 | V     |

| OSCILLATOR                         |                       |                                                                      |      |       |      |       |

| Switching Frequency                | F <sub>SW</sub>       |                                                                      | 306  | 340   | 374  | kHz   |

| Slope Compensation                 | m <sub>a</sub>        |                                                                      |      | 51    |      | mV/μs |

| Minimum On Time                    | t <sub>onmin</sub>    |                                                                      | 90   | 110   | 140  | ns    |

| Minimum Off Time                   | t <sub>offmin</sub>   |                                                                      |      | 93    |      | %     |

| Max Duty Cycle                     | D <sub>max</sub>      |                                                                      |      | 100   |      | %     |

| Soft-Start Time                    | t <sub>ss</sub>       |                                                                      | 1.0  | 1.5   | 2.0  | ms    |

| Soft-Start Delay                   | t <sub>ss,dlly</sub>  |                                                                      | 200  | 300   | 400  | μs    |

| EN/SYNC                            | •                     |                                                                      | •    | •     |      | •     |

| Low Threshold                      | $V_{s,il}$            |                                                                      |      |       | 0.8  | V     |

| High Threshold                     | $V_{s,ih}$            |                                                                      | 2.0  |       |      | V     |

| Input Current                      | I <sub>sync</sub>     |                                                                      |      | 5.0   | 10   | μΑ    |

| SYNC Frequency Range               | f <sub>sync</sub>     | Relative to Nominal Switching Frequency                              | 80   |       | 300  | %     |

| SYNC Delay                         | t <sub>s,dly</sub>    | From SYNC falling edge to GDRV falling edge                          |      | 50    | 100  | ns    |

| SYNC Duty Cycle                    | D <sub>sync</sub>     |                                                                      | 25   |       | 75   | %     |

| Disable Delay Time                 | t <sub>en</sub>       | % of F <sub>SW</sub>                                                 |      | 300   |      | %     |

| POWER GOOD                         |                       |                                                                      |      |       |      |       |

| Rising Threshold                   | PG <sub>rise</sub>    | % of V <sub>ref</sub>                                                | 87   | 90    | 93   | %     |

| Falling Threshold                  | PG <sub>fall</sub>    | % of V <sub>ref</sub>                                                | 90   | 93    | 96   | %     |

| Power Good Pulldown                | V <sub>pg</sub>       |                                                                      |      |       | 0.40 | V     |

| VOLTAGE ERROR AMP                  | , ,                   |                                                                      |      |       |      |       |

| DC Gain                            | $A_{V}$               |                                                                      | 55   | 80    | 91   | dB    |

| Gain-Bandwidth Product             | G <sub>BW</sub>       |                                                                      | 1.7  | 2.4   | 3.1  | MHz   |

| FB Bias Current                    | I <sub>vfb,bias</sub> |                                                                      |      | 0.1   | 1.0  | μΑ    |

| Charge Currents                    | I <sub>src,vea</sub>  | Source, V <sub>FB</sub> = 0.9 V, V <sub>COMP</sub> = 1.2 V           | 1.2  | 1.8   | 2.5  | mA    |

|                                    | I <sub>snk,vea</sub>  | Sink, V <sub>FB</sub> = 0.7 V, V <sub>COMP</sub> = 1.2 V             | 0.5  | 0.8   | 1.0  |       |

| Reference Voltage                  | $V_{ref}$             |                                                                      | 784  | 800   | 816  | mV    |

| High Saturation Voltage            | V <sub>c,max</sub>    |                                                                      | 2.2  | 2.3   |      | V     |

| Low Saturation Voltage             | V <sub>c,min</sub>    |                                                                      |      | 0.001 | 0.3  | V     |

| CURRENT SENSE AMP                  |                       |                                                                      |      |       |      |       |

| Common-Mode Range                  | CMR                   |                                                                      | 3.1  |       | 40   | V     |

| Differential Mode Range            | DMR                   |                                                                      | 300  |       |      | mV    |

| Amplifier Gain                     | A <sub>csa</sub>      |                                                                      |      | 2.0   |      | V/V   |

| Input Bias Current                 | I <sub>sns,bias</sub> |                                                                      |      | 30    | 50   | μΑ    |

| <u> </u>                           |                       |                                                                      | -    |       |      |       |

**ELECTRICAL CHARACTERISTICS** ( $V_{IN} = 3.4 \text{ V}$  to 36 V, EN = 5 V. Min/Max values are valid for the temperature range  $-40^{\circ}\text{C} \le T_{J} \le 150^{\circ}\text{C}$  unless noted otherwise, and are guaranteed by test, design or statistical correlation.)

| Characteristic                                                         | Symbol               | Conditions                                                    | Min     | Тур | Max  | Unit  |

|------------------------------------------------------------------------|----------------------|---------------------------------------------------------------|---------|-----|------|-------|

| CURRENT LIMIT / OVER CU                                                |                      |                                                               | I WIIII | קני | WIGA | Oilit |

|                                                                        |                      | I                                                             | 0.5     | 100 | 145  |       |

| Cycle-by-Cycle Current<br>Limit Threshold                              | V <sub>cl</sub>      |                                                               | 85      | 100 | 115  | mV    |

| Cycle-by-Cycle Current<br>Limit Response Time                          | t <sub>cl</sub>      |                                                               |         |     | 200  | nsec  |

| Over Current Protection<br>Threshold                                   | V <sub>ocp</sub>     | % of V <sub>cl</sub>                                          | 125     | 150 | 175  | %     |

| Over Current Protection<br>Response Time                               | t <sub>ocp</sub>     |                                                               |         |     | 200  | ns    |

| GATE DRIVERS                                                           |                      |                                                               |         |     |      |       |

| Leading Edge Blanking<br>Time                                          | t <sub>on,min</sub>  |                                                               |         |     | 100  | ns    |

| Gate Driver Pull Up<br>Current                                         | I <sub>sink</sub>    | V <sub>IN</sub> – V <sub>GDRV</sub> = 4 V                     |         | 200 | 300  | mA    |

| Gate Driver Pull Down<br>Current                                       | I <sub>src</sub>     | V <sub>IN</sub> – V <sub>GDRV</sub> = 4 V                     |         | 200 | 300  | mA    |

| Gate Driver Clamp<br>Voltage<br>(V <sub>IN</sub> – V <sub>GDRV</sub> ) | V <sub>drv</sub>     |                                                               | 6.0     | 8.0 | 10   | V     |

| Power Switch Gate to<br>Source Voltage                                 | V <sub>gs</sub>      | V <sub>IN</sub> = 4 V                                         | 3.8     |     |      | V     |

| SHORT CIRCUIT PROTECT                                                  | ION                  |                                                               | •       | •   | •    | •     |

| Startup Blanking Time                                                  | t <sub>scp,dly</sub> | From start of soft-start, % of soft-start time                | 105     |     | 300  | %     |

| Short-Circuit Threshold<br>Voltage                                     | V <sub>scp</sub>     | % of Feedback Voltage (V <sub>ref</sub> )                     | 65      | 70  | 75   | %     |

| Hiccup Time                                                            | t <sub>hcp,dly</sub> | % of Soft-Start Time                                          |         | 135 |      | %     |

| SC Response Time                                                       | t <sub>scp</sub>     | Switcher Running                                              |         | 60  | 200  | ns    |

| THERMAL SHUTDOWN                                                       |                      |                                                               |         |     |      |       |

| Thermal Shutdown<br>Threshold                                          | T <sub>sd</sub>      | T <sub>J</sub> rising                                         | 160     | 170 | 180  | °C    |

| Thermal Shutdown<br>Hysteresis                                         | T <sub>sd,hys</sub>  | T <sub>J</sub> Shutdown – T <sub>J</sub> Startup              | 10      | 15  | 20   | °C    |

| Thermal Shutdown Delay                                                 | t <sub>tsd</sub>     | T <sub>J</sub> > Thermal Shutdown Threshold to stop switching |         |     | 200  | ns    |

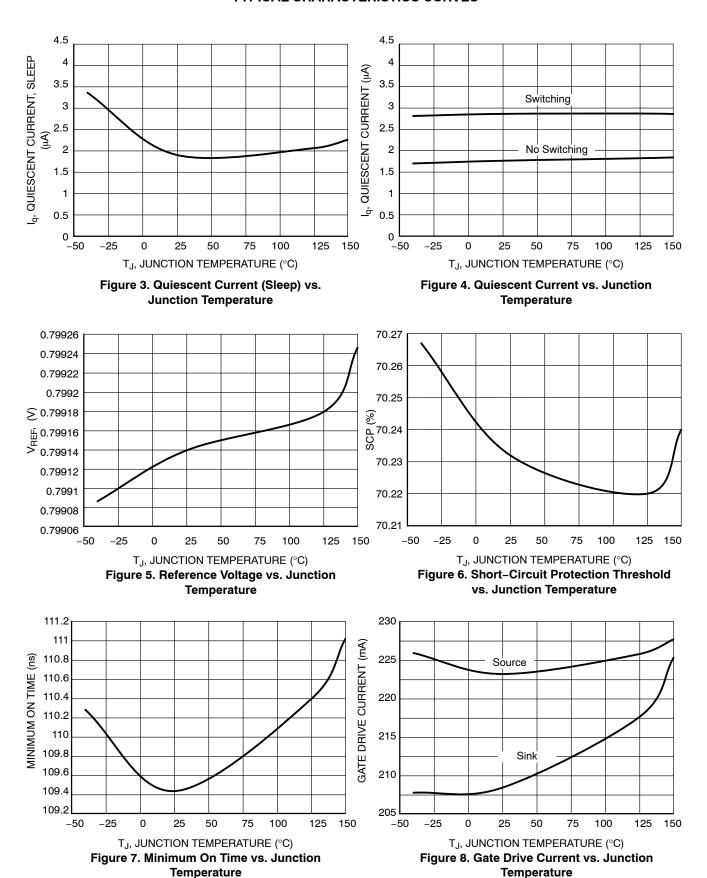

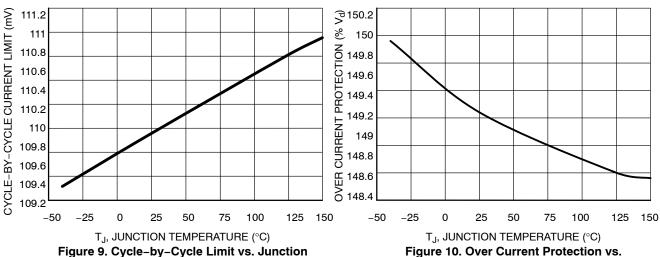

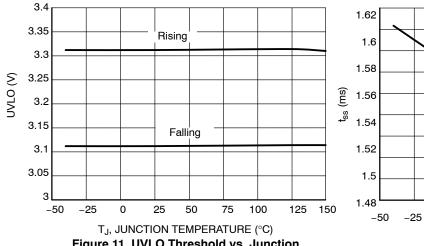

#### **TYPICAL CHARACTERISTICS CURVES**

### **TYPICAL CHARACTERISTICS CURVES**

Figure 9. Cycle-by-Cycle Limit vs. Junction Temperature

Figure 10. Over Current Protection vs.

Junction Temperature

Figure 11. UVLO Threshold vs. Junction Temperature

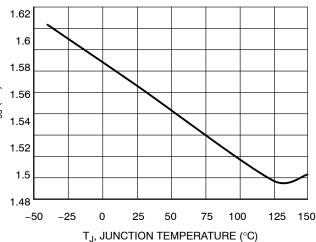

Figure 12. Soft-Start Time vs. Junction Temperature

#### THEORY OF OPERATION

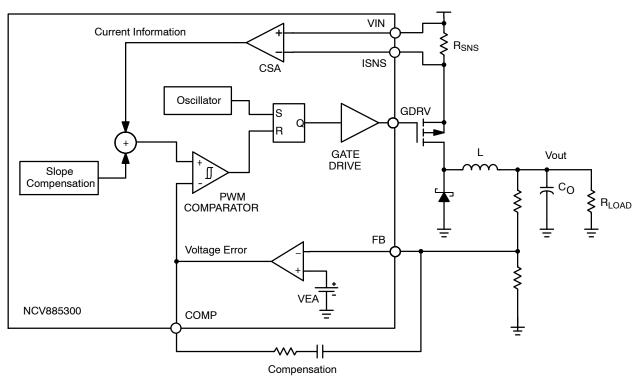

Figure 13. Current Mode Control Schematic

#### **Current Mode Control**

The NCV885300 SMPS incorporates a current mode control scheme, in which the PWM ramp signal is derived from the power switch current. This ramp signal is compared to the output of the error amplifier to control the on-time of the power switch. The oscillator is used as a fixed-frequency clock to ensure a constant operational frequency. The resulting control scheme features several advantages over conventional voltage mode control. First, derived from the resistor in the power path, the signal responds immediately to line voltage changes. This eliminates the delay caused by the output filter and error amplifier, which is commonly found in voltage mode controllers. The second benefit comes from inherent pulse-by-pulse current limiting by merely clamping the peak switching current. Finally, since current mode commands an output current rather than voltage, the filter offers only a single pole to the feedback loop. This allows for a simpler compensation.

The NCV885300 also includes a slope compensation scheme in which a fixed ramp generated by the oscillator is added to the current ramp. A proper slope rate is provided to improve circuit stability without sacrificing the advantages of current mode control.

#### **Overcurrent Protection**

The NCV885300 features two current limit protections: peak current mode and overcurrent hiccup mode. When the

current sense amplifier detects a voltage above the peak current limit between  $V_{IN}$  and ISNS after the current limit leading edge blanking time, the peak current limit causes the power switch to turn off for the remainder of the cycle. Set the current limit with a resistor from  $V_{IN}$  to ISNS, with  $R=0.100\,/\,I_{limit}$ .

If the voltage across the current sense resistor exceeds the overcurrent threshold voltage the part enters overcurrent hiccup mode. The part will remain off for the hiccup time and then go through the power on reset procedure.

#### **Short Circuit Hiccup Protection**

When the output voltage falls below the short circuit trip voltage the part enters short circuit latch off. When a short is detected the NCV885300 disables the outputs and attempts to re-enable the outputs after the short circuit hiccup time. The part remains off for the hiccup time and then goes through the power on reset procedure. If the short has been removed then the output stage re-enables and operates normally; however, if the short is still present the cycle begins again. Internal heat dissipation is kept to a minimum as current will only flow during the reset time of the protection circuitry. The hiccup mode is continuous until the short is removed.

#### **Gate Drive**

To turn on the P–Channel MOSFET, the gate driver turns on a current source to ground. A clamp ensures that the gate drive voltage does not exceed 10 V. When the clamp starts conducting the current source starts to turn off. To turn off the external MOSFET, the gate driver turns on a current source to  $V_{\rm IN}$ .

#### **EN/SYNC**

This pin has three modes. When a dc logic high (CMOS/TTL compatible) voltage is applied to this pin the NCV885300 operates at the default frequency. When a dc logic low voltage is applied to this pin the NCV885300 enters a low quiescent current sleep mode. When a square wave of at least 40% of the switching frequency is applied to this pin the switcher operates at the same frequency as the square wave. If the signal is slower than 40% of the switching frequency, it will be interpreted as enabling and disabling the part. The falling edge of the square wave corresponds to the start of the switching cycle.

#### **Power Good**

The power good pin is high when the reference voltage reaches 90% of its target of 800 mV. The pin should be pulled up with a 10  $k\Omega$  resistor to 5 V. The output voltage of the controller may be used in this case.

#### **Overvoltage Lockout**

To protect the IC, if the voltage on the VIN pin the exceeds  $V_{\text{ovlo}}$  the NCV885300 will shutdown. When the voltage drops below this voltage the part will go through the normal soft–start procedure.

#### **Undervoltage Lockout**

Undervoltage lockout protection is engaged when the input voltage drops below the  $V_{uvlo}$  signal. The part will remain off until the input voltage rises above the  $V_{uvlo}$  value plus hysteresis. Depending on the desired output voltage, it is possible to engage the short-circuit hiccup mode before undervoltage lockout occurs.

#### Soft-Start

To ensure moderate inrush current and reduce output overshoot, the NCV885300 features a soft start which periodically adds charge to a capacitor until the final reference voltage is achieved. When using an external SYNC signal, charging is based on the switching frequency. If, for example, the NCV885300 is synchronized to twice the free running (not synced) frequency, the soft–start will be half as long.

#### **DESIGN METHODOLOGY**

Choosing external components for the NCV885300 encompasses the following design process:

- 1. Define operational parameters

- 2. Select switching frequency

- 3. Select current sensor

- 4. Select a MOSFET

- 5. Select a diode

- 6. Select output inductor

- 7. Select output capacitors

- 8. Select compensator components

# (1) Operating Parameter Definition

First, select feedback resistors to choose the output voltage as follows:

$$V_{OUT} = V_{REF} \cdot \frac{R_1 + R_2}{R_2}$$

where:

V<sub>OUT</sub>: desired output voltage

$R_1$ : upper feedback resistor (between VOUT and FB) [ $\Omega$ ]  $R_2$ : lower feedback resistor (between FB and GND) [ $\Omega$ ]

For a 5.0 V output, set  $R_1$  to 42.2 k $\Omega$  and  $R_2$  to 8.06 k $\Omega$ .

Certain operating parameters must be defined before proceeding with the rest of the design. These are application dependent and include the following:

$V_{IN}$ : input voltage, range from minimum to maximum with a typical value [V]

I<sub>OUT</sub>: output current, range from minimum to maximum with an initial startup value

I<sub>CL</sub>: desired typical current limit

A number of basic calculations must be performed up front to use in the design process, as follows:

$$D_{MIN} = \frac{V_{OUT}}{V_{IN(max)}}$$

$$D\,=\,\frac{V_{OUT}}{V_{IN(typ)}}$$

$$D_{MAX} = \frac{V_{OUT}}{V_{IN(min)}}$$

where:

D<sub>MIN</sub>: minimum duty cycle (ideal) [%]

V<sub>IN(max)</sub>: maximum input voltage [V]

D: typical duty cycle (ideal) [%]

V<sub>IN(typ)</sub>: typical input voltage [V]

D<sub>MAX</sub>: maximum duty cycle (ideal) [%]

V<sub>IN(min)</sub>: minimum input voltage [V]

#### (2) Switching Frequency Selection

Selecting the switching frequency is a trade-off between component size and power losses. Operation at higher switching frequencies allows the use of smaller inductor and capacitor values to achieve the same inductor current ripple and output voltage ripple. However, increasing the frequency increases the switching losses of the MOSFETs, leading to decreased efficiency, especially noticeable at light loads

Typically, the switching frequency is selected to avoid interfering with signals of known frequencies. Using the EN/SYNC pin, the NCV885300 can be synced to frequencies from 80% to 300% of the nominal frequency (340 kHz).

#### (3) Current Sensor Selection

Current sensing for peak current mode control relies on the inductor current signal. This is translated into a voltage via a current sense resistor, which is then measured differentially by the current sense amplifier, generating a single-ended output to use as a signal. The easiest means of implementing this transresistance is through the use of a sense resistor in series with the source of the MOSFET and VIN. A sense resistor should be calculated as follows:

$$R_{SNS} = \frac{V_{CL}}{I_{CL}}$$

where:

$R_{SNS}$ : sense resistor [ $\Omega$ ]

V<sub>CL</sub>: current limit threshold voltage [V]

I<sub>CL</sub>: desired cycle-by-cycle current limit [A]

#### (4) MOSFET Selection

The NCV885300 has been designed to work with a P-channel MOSFET in a non-synchronous buck configuration. The MOSFET needs to be capable of handling the maximum allowable current in the system,  $I_{CL}$ . Keep in mind that, depending on your minimum  $V_{IN}$  signal, it is possible to achieve 100% duty cycle. The power dissipated through the MOSFET during conduction is as follows:

$$P_{MOS \text{ on}} = I_{Cl}^{2} \cdot D_{MAX} \cdot r_{DS \text{ on}}$$

where:

P<sub>MOS,on</sub>: power through MOSFET [W]

I<sub>CL</sub>: cycle-by-cycle current limit [A]

$r_{DS,on}$ : on-resistance of the MOSFET [ $\Omega$ ]

To calculate the switching losses through the MOSFET, use the following equation:

$$\begin{split} & P_{MOS,sw} = \frac{1}{2} V_{IN} \cdot I_{OUT} \cdot \left(t_{on} + t_{off}\right) \cdot F_{SW} \\ & t_{on} = t_{off} = \frac{Q_{Gate}}{I_{dot}} \end{split}$$

where:

P<sub>MOS, sw</sub>: MOSFET switching losses [W]

t<sub>on</sub>: time to turn on the MOSFET [s]

toff: time to turn off the MOSFET [s]

Q<sub>Gate</sub>: gate charge [C] I<sub>dry</sub>: gate drive current [A]

#### (5) Diode Selection

The diode must be chosen according to its maximum current and voltage ratings, and to thermal considerations.

The maximum reverse voltage the diode sees is the maximum input voltage (with some margin in case of ringing on the switch node). The maximum forward current is the peak current limit of the NCV885300, or 150% of  $I_{CL}$ .

#### (6) Output Inductor Selection

Both mechanical and electrical considerations influence the selection of an output inductor. From a mechanical perspective, smaller inductor values generally correspond to smaller physical size. Since the inductor is often one of the largest components in the power supply, a minimum inductor value is particularly important in space-constrained applications. From an electrical perspective, an inductor is chosen for a set amount of current ripple and to assure adequate transient response.

The output inductor controls the current ripple that occurs over a switching period. A high current ripple will result in excessive power loss and ripple current requirements. A low current ripple will result in a poor control signal and a slow current slew rate in the event of a load transient. A good starting point for peak—to—peak ripple is around 10% of the inductor current. To choose the inductor value based on the peak—to—peak ripple current, use the following equation:

$$i_{L} = \frac{V_{OUT} \cdot (1 - D_{MIN})}{L \cdot F_{SW}}$$

where:

i<sub>I</sub>: peak-to-peak output current ripple [Ap-p]

From this equation it is clear that the ripple current increases as L decreases, emphasizing the trade-off between dynamic response and ripple current. The peak and valley values of the triangular current waveform are as follows:

$$I_{L(pk)} = I_{OUT} + \frac{i_L}{2}$$

$$I_{L(vly)} = I_{OUT} - \frac{i_L}{2}$$

where:

$I_{L(pk)}$ : peak (maximum) value of ripple current [A]  $I_{L(vly)}$ : valley (minimum) value of ripple current [A]

Saturation current is specified by inductor manufacturers as the current at which the inductance value has dropped from the nominal value, typically 10%. For stable operation, the output inductor must be chosen so that the inductance is close to the nominal value even at the peak output current,  $I_{L(pk)}$ , it is recommended to choose an inductor with saturation current sufficiently higher than the peak output current, such that the inductance is very close to the nominal value at the peak output current. This allows for a safety factor and allows for more optimized compensation.

Inductor efficiency is another consideration when selecting an output inductor. Inductor losses include dc and ac winding losses, which are very low due to high core resistance, and magnetic hysteresis losses, which increase with peak-to-peak ripple current. Core losses also increase as switching frequency increases.

Ac winding losses are based on the ac resistance of the winding and the RMS ripple current through the inductor, which is much lower than the dc current. The ac winding losses are due to skin and proximity effects and are typically much less than dc losses, but increase with frequency. Dc winding losses account for a large percentage of output inductor losses and are the dominant factor at switching frequencies at or below 500 kHz. The dc winding losses in the inductor can be calculated with the following equation:

$$P_{L(dc)} = I_{OUT}^2 \cdot R_{dc}$$

where:

$P_{L(dc)}$ : dc winding losses in the output inductor  $R_{dc}$ : dc resistance of the output inductor (DCR)

#### (7) Output Capacitor Selection

The output capacitor is a basic component for the fast response of a power supply. In fact, for the first few microseconds of a load transient, they supply the current to the load. The controller recognizes the load transient and proceeds to increase the duty cycle to its maximum. Neglecting the effect of the ESL, the output voltage has a first drop due to ESR of the bulk capacitor(s).

$$\Delta V_{OUT(ESR)} = \Delta I_{OUT} \cdot ESR$$

A lower ESR produces a lower  $\Delta V$  during load transient. In addition, a lower ESR produces a lower output voltage ripple.

In the case of stepping into a short, the inductor current approaches zero with the worst case initial current at the current limit and the initial voltage at the output voltage set point, calculating the voltage overshoot as follows:

$$\Delta V_{OS} = \sqrt{\frac{L \cdot I_{CL}^2}{C} + V_{OUT}^2 - V_{OUT}}$$

Accordingly, a minimum amount of capacitance can be chosen for maximum allowed output voltage overshoot:

$$C_{MIN} = \frac{L \cdot I_{CL}^{2}}{\left(V_{OUT} + \Delta V_{OS(max)}\right)^{2} - V_{OUT}^{2}}$$

where:

$C_{MIN}$ : minimum amount of capacitance to minimize voltage overshoot to  $\Delta V_{OS(max)}[F]$

$\Delta V_{OS(max)}$ : maximum allowed voltage overshoot during a short [V]

#### (8) Select Compensator Components

The Current Mode control method employed by the NCV885300 allows the use of a simple, Type II compensation to optimize the dynamic response according to system requirements. Using a simulation tool such as <a href="CompCalc">CompCalc</a> can assist in the selection of these components.

#### PACKAGE DIMENSIONS

SOIC-8 NB

# CASE 751-07 ISSUE AK -X-В $| \oplus$ 0.25 (0.010) M Y M -Y-G С SEATING PLANE -Z-0.10 (0.004) Н 0.25 (0.010) M z YS XS SOLDERING FOOTPRINT\*

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982. CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

- DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIN | IETERS | INCHES    |       |  |  |  |

|-----|--------|--------|-----------|-------|--|--|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |  |  |

| Α   | 4.80   | 5.00   | 0.189     | 0.197 |  |  |  |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |  |  |  |

| С   | 1.35   | 1.75   | 0.053     | 0.069 |  |  |  |

| D   | 0.33   | 0.51   | 0.013     | 0.020 |  |  |  |

| G   | 1.27   | 7 BSC  | 0.050 BSC |       |  |  |  |

| Н   | 0.10   | 0.25   | 0.004     | 0.010 |  |  |  |

| J   | 0.19   | 0.25   | 0.007     | 0.010 |  |  |  |

| K   | 0.40   | 1.27   | 0.016     | 0.050 |  |  |  |

| М   | 0 °    | 8 °    | 0 °       | 8 °   |  |  |  |

| N   | 0.25   | 0.50   | 0.010     | 0.020 |  |  |  |

| S   | 5.80   | 6.20   | 0.228     | 0.244 |  |  |  |

0.024 0.050 (mm inches SCALE 6:1 \*For additional information on our Pb-Free strategy and soldering

details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

7.0

0.275

0.6

1.52 0.060

40

0.155

1.270

ON Semiconductor and un are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent—Marking.pdf. SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

### **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT: Literature Distribution Center for ON Semiconductor

P.O. Box 5163, Denver, Colorado 80217 USA

**Phone**: 303–675–2175 or 800–344–3860 Toll Free USA/Canada **Fax**: 303–675–2176 or 800–344–3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free USA/Canada

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910

Japan Customer Focus Center Phone: 81-3-5817-1050

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative