## **3V W-CDMA BAND 1 LINEAR PA MODULE**

Package Style: Module, 10-Pin, 3mmx3mmx1.0mm

### **Features**

- HSDPA Compliant

- Low Voltage Positive Bias Supply (3.0V to 4.2V)

- +28.0dBm Linear Output Power (+26.5dBm HSDPA)

- High Efficiency Operation 40% at P<sub>OUT</sub>=+28.0dBm

- Internal Voltage Regulator Eliminates the Need for External Reference Voltage (V<sub>RFF</sub>)

- 2-Mode Power States with Digital Control Interface

- Supports DC/DC Converter Operation

- Integrated Power Coupler

- Integrated Blocking and Collector Decoupling Capacitors

## **Applications**

WCDMA/HSDPA Wireless Data Cards

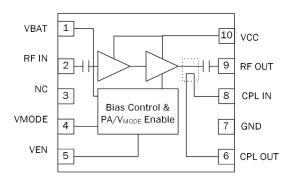

Functional Block Diagram

## **Product Description**

The RF3701 is a high-power, high-efficiency, linear power amplifier designed for use as the final RF amplifier in 3V,  $50\Omega$  W-CDMA mobile cellular equipment and spread-spectrum systems. This PA is developed for UMTS Band 1 which operates in the 1920MHz to 1980MHz frequency band. The RF3701 has a digital control pin which enables a low power mode to reduce amplifier gain at lower power levels. The part also has an integrated directional coupler which eliminates the need for an external discrete coupler at the output. The RF3701 is fully HSDPA-compliant and is assembled in a 10-pin, 3mmx3mm module.

## **Ordering Information**

RF3701 3V W-CDMA Band 1 Linear PA Module RF3701PCBA-410 Fully Assembled Evaluation Board

| ptimum recnnolog | gy watching® App          | niea        |

|------------------|---------------------------|-------------|

| ☐ SiGe BiCMOS    | ☐ GaAs pHEMT              | ☐ GaN HEMT  |

| ☐ Si BiCMOS      | ▼ Si CMOS                 | ☐ RF MEMS   |

| ☐ SiGe HBT       | ☐ Si BJT                  | ☐ LDMOS     |

|                  | ☐ SiGe BiCMOS ☐ Si BiCMOS | ☐ Si BiCMOS |

# **RF3701**

## **Absolute Maximum Ratings**

| Parameter                                         | Rating      | Unit |

|---------------------------------------------------|-------------|------|

| Supply Voltage in Standby Mode                    | 5.5         | V    |

| Supply Voltage in Idle Mode                       | 5.5         | V    |

| Supply Voltage in Operating Mode, $50\Omega$ Load | 5.5         | V    |

| Supply Voltage, V <sub>BAT</sub>                  | 5.5         | V    |

| Control Voltage, VMODE                            | 5.5         | V    |

| Control Voltage, V <sub>EN</sub>                  | 5.5         | V    |

| RF - Input Power                                  | +10         | dBm  |

| RF - Output Power                                 | +30         | dBm  |

| Output Load VSWR (Ruggedness)                     | 10:1        |      |

| Operating Ambient Temperature                     | -30 to +110 | °C   |

| Storage Temperature                               | -55 to +150 | °C   |

Caution! ESD sensitive device.

Exceeding any one or a combination of the Absolute Maximum Rating conditions may cause permanent damage to the device. Extended application of Absolute Maximum Rating conditions to the device may reduce device reliability. Specified typical performance or functional operation of the device under Absolute Maximum Rating conditions is not implied.

RoHS status based on EU Directive 2002/95/EC (at time of this document revision).

The information in this publication is believed to be accurate and reliable. However, no responsibility is assumed by RF Micro Devices, Inc. ("RFMD") for its use, nor for any infringement of patents, or other rights of third parties, resulting from its use. No license is granted by implication or otherwise under any patent or patent rights of RFMD. RFMD reserves the right to change component circuitry, recommended application circuitry and specifications at any time without prior notice.

| Davameter                        |                     | Specification |      |      | O anditi an           |

|----------------------------------|---------------------|---------------|------|------|-----------------------|

| Parameter                        | Min.                | Тур.          | Max. | Unit | Condition             |

| Recommended Operating Conditions |                     |               |      |      |                       |

| Operating Frequency Range        | 1920                |               | 1980 | MHz  |                       |

| V <sub>BAT</sub>                 | +3.0                | +3.2          | +4.2 | V    |                       |

| V <sub>CC</sub>                  | +0.5                | +3.21         | +4.2 | V    |                       |

| V <sub>EN</sub>                  | 0                   |               | 0.5  | V    | PA disabled.          |

|                                  | 1.35                | 1.80          | 3.10 | V    | PA enabled.           |

| V <sub>MODE</sub>                | 0                   |               | 0.5  | V    | Logic "low".          |

|                                  | 1.35                | 1.80          | 3.10 | V    | Logic "high".         |

| P <sub>OUT</sub>                 |                     |               |      |      |                       |

| Maximum Linear Output<br>(HPM)   | 28.0 <sup>2,3</sup> |               |      | dBm  | High Power Mode (HPM) |

| Maximum Linear Output<br>(LPM)   | 16 <sup>2,3</sup>   |               |      | dBm  | Low Power Mode (LPM)  |

| Ambient Temperature              | -20                 | +25           | +85  | °C   |                       |

## Notes:

<sup>&</sup>lt;sup>1</sup>Minimum V<sub>CC</sub> for max P<sub>OUT</sub> indicated. V<sub>CC</sub> down to 0.5V may be used for backed-off power when using DC/DC converter to conserve battery current.

$<sup>^2</sup>$ For operation at V<sub>CC</sub>=+3.0V, derate P<sub>OUT</sub> by 0.5 dB.

$<sup>^{3}</sup>P_{OUT}$  is specified for 3GPP (Voice) modulation. For HSDPA operation, derate  $P_{OUT}$  by 1.5dB: HSDPA Configuration:  $\beta c=12$ ,  $\beta d=15$ ,  $\beta hs=24$

| Dawanatan                         | Specification |       |      | 11.21  | On addition                                                                                                                                                                                                                |  |

|-----------------------------------|---------------|-------|------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                         | Min.          | Тур.  | Max. | Unit   | Condition                                                                                                                                                                                                                  |  |

| Electrical Specifications         |               |       |      |        | T=+25°C, $V_{CC}$ = $V_{BAT}$ =+3.2V, $V_{EN}$ =+1.8V, $50\Omega$ system, unless otherwise specified.                                                                                                                      |  |

| Gain                              | 26            | 28.5  | 31   | dB     | HPM, P <sub>OUT</sub> =28.0dBm                                                                                                                                                                                             |  |

|                                   | 11.75         | 14.5  | 16   | dB     | LPM, P <sub>OUT</sub> ≤16.0dBm                                                                                                                                                                                             |  |

| Gain Linearity                    |               | ±0.2  |      | dB     | HPM, 16.0dBm≤P <sub>OUT</sub> ≤28.0dBm                                                                                                                                                                                     |  |

| ACLR - 5MHz Offset                |               | -40   | -36  | dBc    | HPM, P <sub>OUT</sub> =28.0dBm                                                                                                                                                                                             |  |

|                                   |               | -40   | -36  | dBc    | LPM, P <sub>OUT</sub> =16.0dBm                                                                                                                                                                                             |  |

| ACLR - 10MHz Offset               |               | -55   | -48  | dBc    | HPM, P <sub>OUT</sub> =28.0dBm                                                                                                                                                                                             |  |

|                                   |               | -58   | -48  | dBc    | LPM, P <sub>OUT</sub> =16.0dBm                                                                                                                                                                                             |  |

| PAE Without DC/DC Converter       | 36            | 40    |      | %      | HPM, P <sub>OUT</sub> =28.0dBm                                                                                                                                                                                             |  |

|                                   |               | 7     |      | %      | LPM, P <sub>OUT</sub> =16.0dBm                                                                                                                                                                                             |  |

| Current Drain                     |               | 170   |      | mA     | LPM, P <sub>OUT</sub> =16.0dBm                                                                                                                                                                                             |  |

| Quiescent Current                 | 70            | 100   | 150  | mA     | HPM, DC only                                                                                                                                                                                                               |  |

| Enable Current                    |               | 0.1   |      | mA     | Source or sink current. V <sub>EN</sub> =1.8V.                                                                                                                                                                             |  |

| Mode Current (I <sub>MODE</sub> ) |               | 0.1   |      | mA     | Source or sink current. V <sub>MODE</sub> =1.8V.                                                                                                                                                                           |  |

| Leakage Current                   |               | 0.2   | 1.0  | μА     | DC only. V <sub>CC</sub> =V <sub>BAT</sub> =4.2V, V <sub>EN</sub> =V <sub>MODE</sub> =0.5V.                                                                                                                                |  |

| Noise Power in Receive Band       |               | -140  |      | dBm/Hz | All power modes, measured at duplex offset frequency (FTX+190MHz). Rx: 2110MHz to 2170MHz, P <sub>OUT</sub> ≤28.0dBm                                                                                                       |  |

| Input Impedance                   |               | 1.8:1 |      | VSWR   | No ext. matching, P <sub>OUT</sub> ≤28dBm, all modes.                                                                                                                                                                      |  |

| Harmonic, 2FO                     |               | -22   | -7   | dBm    | P <sub>OUT</sub> ≤28.0dBm, all power modes.                                                                                                                                                                                |  |

| Harmonic, 3FO                     |               | -30   | -12  | dBm    | P <sub>OUT</sub> ≤28.0dBm, all power modes.                                                                                                                                                                                |  |

| Spurious Output Level             |               |       | -70  | dBc    | All spurious, P <sub>OUT</sub> ≤ 28 dBm, all conditions, load VSWR ≤ 6:1, all phase angles.                                                                                                                                |  |

| Insertion Phase Shift             | -30           |       | +30  | o      | Phase shift at 16dBm when switching from HPM to LPM.                                                                                                                                                                       |  |

| DC Enable Time                    |               |       | 10   | μS     | DC only. Time from $V_{EN}$ = high to stable idle current (90% of steady state value).                                                                                                                                     |  |

| RF Rise/Fall Time                 |               |       | 6    | μS     | P <sub>OUT</sub> ≤28.0dBm, all modes. 90% of target, DC settled prior to RF.                                                                                                                                               |  |

| Coupling Factor                   |               | -20   |      | dB     | P <sub>OUT</sub> ≤28.0dBm, all modes.                                                                                                                                                                                      |  |

| Coupling Accuracy - Temp/Voltage  |               | ±0.2  |      | dB     | $\begin{array}{l} P_{OUT} {\leq} 28.0 dBm, \ all \ modes. \ -20^{\circ}C {\leq} T {\leq} 85^{\circ}C, \\ 3.0 V {\leq} V_{CC} \& V_{BAT} {\leq} 4.2 V, \ referenced \ to \ 25^{\circ}C, \\ 3.2 V \ conditions. \end{array}$ |  |

| Coupling Accuracy - VSWR          |               | ±0.25 |      | dB     | P <sub>OUT</sub> ≤28dBm, all modes, load VSWR=2.5:1,<br>±0.3dB accuracy corresponds to 22dB directivity.                                                                                                                   |  |

| Pin         | Function | Description                                                                                                                                                                                                                                     |  |  |  |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1           | VBAT     | Supply voltage for bias circuitry.                                                                                                                                                                                                              |  |  |  |

| 2           | RF IN    | RF input internally matched to $50\Omega$ and DC blocked. The RF input matching circuit has a shunt inductor to ground which would short any DC voltage placed on this pin.                                                                     |  |  |  |

| 3           | NC       | No connection.                                                                                                                                                                                                                                  |  |  |  |

| 4           | VMODE    | Digital control input for power mode selection (see Operating Modes truth table).                                                                                                                                                               |  |  |  |

| 5           | VEN      | Digital control input for PA enable and disable (see Operating Modes truth table).                                                                                                                                                              |  |  |  |

| 6           | CPL_OUT  | Coupler output.                                                                                                                                                                                                                                 |  |  |  |

| 7           | GND      | This pin must be grounded.                                                                                                                                                                                                                      |  |  |  |

| 8           | CPL_IN   | Coupler input used for cascading couplers in series. Terminate this pin with a $50\Omega$ resistor if not connected to another coupler.                                                                                                         |  |  |  |

| 9           | RF OUT   | RF output internally matched to $50\Omega$ and DC blocked.                                                                                                                                                                                      |  |  |  |

| 10          | vcc      | Supply voltage for the first and second stage amplifiers, which can be connected to battery supply or output of DC-DC converter.                                                                                                                |  |  |  |

| Pkg<br>Base | GND      | Ground connection. The package backside should be soldered to a topside ground pad connecting to the PCB ground plane with multiple ground vias. The pad should have a low thermal resistance and low electrical impedance to the ground plane. |  |  |  |

## **Operating Mode Truth Table**

| V <sub>EN</sub> | V <sub>MODE</sub> | V <sub>BAT</sub> | V <sub>CC</sub> | Conditions/Comments |

|-----------------|-------------------|------------------|-----------------|---------------------|

| Low             | Low               | 3.0V to 4.2V     | 3.0V to 4.2V    | Power down mode     |

| Low             | Х                 | 3.0V to 4.2V     | 3.0V to 4.2V    | Standby Mode        |

| High            | Low               | 3.0V to 4.2V     | 3.0V to 4.2V    | High power mode     |

| High            | High              | 3.0V to 4.2V     | 3.0V to 4.2V    | Low power mode      |

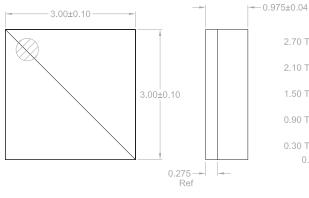

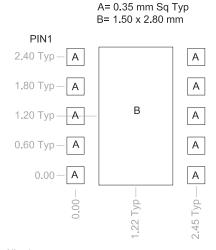

## **Package Drawing**

#### Notes:

- Shaded area represents Pin 1 location

- 2. Defining I/O Pad Center:

- To define center of the I/O pad oepning, draw a right triangle in one corner of the I/O pad

Then take the center of the hypotenuse to determine center of I/O pad

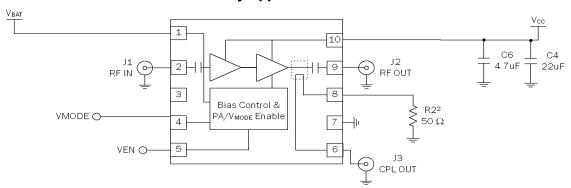

## **Preliminary Application Schematic**

#### NOTES:

- 1. VCC and VBAT are connected together if DC-DC converter is not used.

- 2. 50  $\Omega$  resistor will be removed if pin 8 is connected to another coupler.

## **PCB Design Requirements**

#### **PCB Surface Finish**

The PCB surface finish used for RFMD's qualification process is electroless nickel, immersion gold. Typical thickness is  $3\mu$ inch to  $8\mu$ inch gold over  $180\mu$ inch nickel.

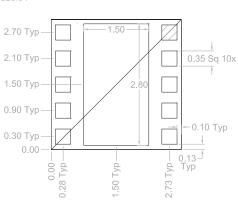

## **PCB Land Pattern Recommendation**

PCB land patterns for RFMD components are based on IPC-7351 standards and RFMD empirical data. The pad pattern shown has been developed and tested for optimized assembly at RFMD. The PCB land pattern has been developed to accommodate lead and package tolerances. Since surface mount processes vary from company to company, careful process development is recommended.

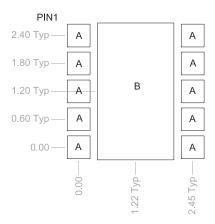

### **PCB Metal Land Pattern**

Figure 1. PCB Metal Land Pattern (Top View)

#### **PCB Solder Mask Pattern**

Liquid Photo-Imageable (LPI) solder mask is recommended. The solder mask footprint will match what is shown for the PCB metal land pattern with a 2mil to 3mil expansion to accommodate solder mask registration clearance around all pads. The center-grounding pad shall also have a solder mask clearance. Expansion of the pads to create solder mask clearance can be provided in the master data or requested from the PCB fabrication supplier.

A= 0.49 mm Sq Typ B= 1.64 x 2.94 mm

Figure 2. PCB Solder Mask Pattern (Top View)

#### Thermal Pad and Via Design

The PCB land pattern has been designed with a thermal pad that matches the die paddle size on the bottom of the device.

Thermal vias are required in the PCB layout to effectively conduct heat away from the package. The via pattern has been designed to address thermal, power dissipation and electrical requirements of the device as well as accommodating routing strategies.

The via pattern used for the RFMD qualification is based on thru-hole vias with 0.203 mm to 0.330 mm finished hole size on a 0.5 mm to 1.2 mm grid pattern with 0.025 mm plating on via walls. If micro vias are used in a design, it is suggested that the quantity of vias be increased by a 4:1 ratio to achieve similar results.