# 256Mb (16M x 16 bit) U*t*RAM

INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE.

NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY.

ALL INFORMATION IN THIS DOCUMENT IS PROVIDED ON AS "AS IS" BASIS WITHOUT GUAR-ANTEE OR WARRANTY OF ANY KIND.

1. For updates or additional information about Samsung products, contact your nearest Samsung office.

2. Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where Product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

\* Samsung Electronics reserves the right to change products or specification without notice.

### **Document Title**

16Mx16 bit Synchronous Burst Uni-Transistor Random Access Memory Revision History

| Revision No. | History | Draft Date     | <u>Remark</u> |

|--------------|---------|----------------|---------------|

| 0.0          | Initial | March 17, 2006 | Preliminary   |

## http://www.BDTIC.com/SAMSUNG Preliminary UtRAM

## K1B5616BAM

| Table of Contents                                             |    |

|---------------------------------------------------------------|----|

| GENERAL DESCRIPTION                                           |    |

| FEATURES & FUNCTION BLOCK DIAGRAM                             |    |

| PRODUCT FAMILY                                                |    |

| TERMINOLOGY DESCRIPTION                                       |    |

| POWER UP SEQUENCE                                             |    |

| MODE STATE MACHINE                                            |    |

| ABSOLUTE MAXIMUM RATINGS                                      |    |

| RECOMMENDED DC OPERATING CONDITIONS                           | 4  |

| CAPACITANCE                                                   | 4  |

| DC AND OPERATING CHARACTERISTICS                              | 4  |

| MRS (MODE REGISTER SET)                                       | 5  |

| MRS CODE                                                      |    |

| MRS TIMING WAVEFORM (SOFTWARE)                                | 6  |

| MRS TIMING WAVEFORM (PS Pin)                                  | 7  |

| PAR (Partial Array Refresh) mode [A3~A1]                      | 8  |

| DPD (Deep Power Down) mode [A4]                               | 8  |

| Burst Length [A7~A5] & Wrap [A12]                             | 9  |

| WAIT Configuration [A8] & WAIT Polarity [A13]                 | 9  |

| Latency [A11~A9]                                              | 10 |

| Driver Strength [A17~A16]                                     |    |

| OPEARTION MODE [A15-A14]                                      | 11 |

| MODE1. ASYNCHRONOUS READ / ASYNCHRONOUS WRITE MODE            | 11 |

| MODE2. SYNCHRONOUS BURST READ / ASYNCHRONOUS WRITE MODE       | 12 |

| MODE 1 AC OPERATING CONDITIONS (ASYNCH. READ / ASYNCH. WRITE) | 13 |

| TIMING WAVEFORMS (ASYNCH. READ / ASYNCH. WRITE)               | 14 |

| Asynch. READ                                                  |    |

| Asynch. PAGE READ                                             |    |

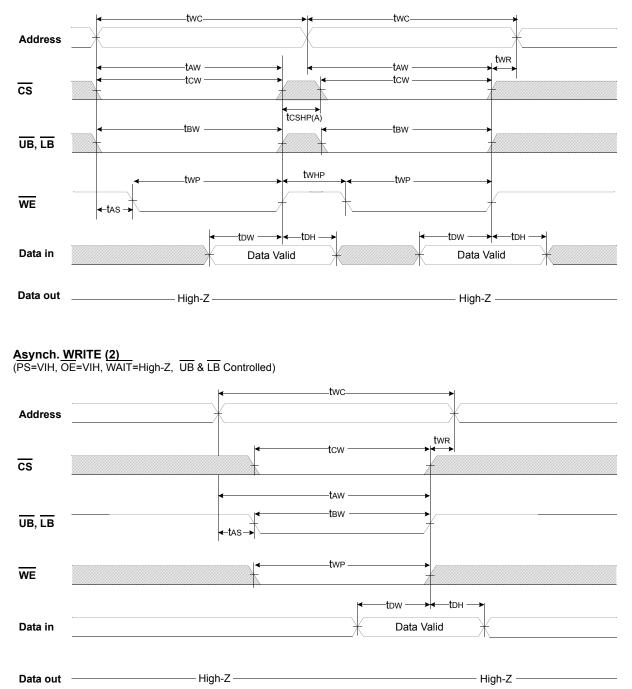

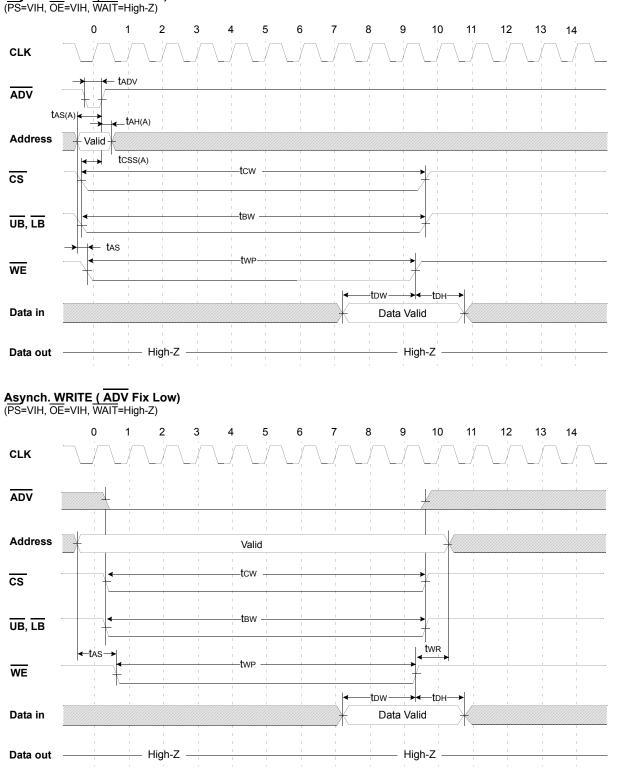

| Asynch. WRITE (1)                                             |    |

| Asynch. WRITE (2)                                             |    |

| MODE 2 AC OPERATING CONDITIONS (SYNCH. READ / ASYNCH. WRITE)  |    |

| TIMING WAVEFORMS (SYNCH. READ / ASYNCH. WRITE)                |    |

| Burst READ - Fixed Latency                                    |    |

| Burst READ - Variable Latency                                 |    |

| Burst READ ( ADV Interrupt) - Fixed Latency                   |    |

| Burst READ (ADV Interrupt) - Variable Latency                 |    |

| Burst READ STOP                                               |    |

| Asynch. WRITE ( ADV Latch)                                    |    |

| Asynch. WRITE ( ADV Fix Low)                                  |    |

| Burst READ followed by Asynch. WRITE                          |    |

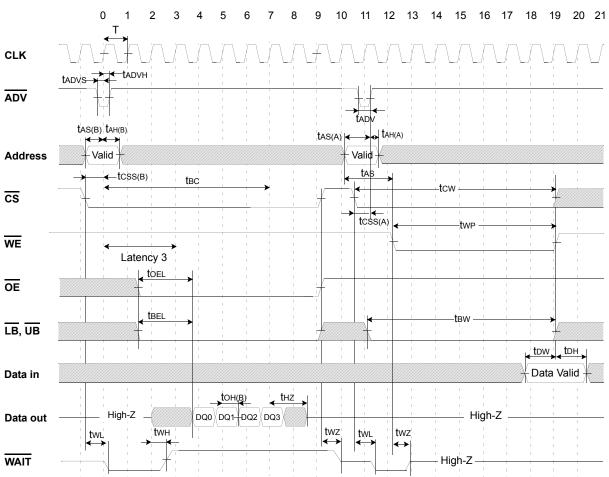

| Asynch. WRITE followed by Burst READ                          |    |

| ,,                                                            | -  |

### 16M x 16 bit Synchronous Burst Uni-Transistor CMOS RAM

#### **GENERAL DESCRIPTION**

The world is moving into the mobile multi-media era and therefore the mobile handsets need bigger & faster memory capacity to handle the multi-media data. SAMSUNG's UtRAM products are designed to meet all the request from the various customers who want to cope with the fast growing mobile market. UtRAM is the perfect solution for the mobile market with its low cost, high density and high performance feature. K1B5616BAM is fabricated by SAMSUNG's advanced CMOS technology using one transistor memory cell. The device supports the traditional SRAM like asynchronous operation (asynchronous page read and asynchronous write), the NOR flash like synchronous operation (synchronous burst read and asynchronous write). These two operation modes are defined through the mode register setting. The device also supports the special features for the standby power saving. Those are the Partial Array Refresh(PAR) mode, Deep Power Down(DPD) mode and internal TCSR (Temperature Compensated Self Refresh). The optimization of output drive strength is possible through the mode register setting to adjust for the different data loadings. Through this drive strength optimization, the device can minimize the noise generated on the data bus during read operation.

#### FEATURES & FUNCTION BLOCK DIAGRAM

- Organization: 16M x 16 bit

- Power supply voltage: 1.7V~1.95V

- Three state outputs

- Supports MRS (Mode Register Set)

- PS pin set up

- Software set up

- Supports power saving modes

- PAR (Partial Array Refresh)

- DPD (Deep Power Down)

- Internal TCSR (Temperature Compensated Self Refresh)

- Supports driver strength optimization

- K1B5616BAM supports

- Asynchronous read / Asynchronous write

- Synchronous burst read / Asynchronous write

- Synchronous burst operation

- Max. clock frequency : 104MHz

- Fixed and Variable read latency

- 4 / 8 / 16 / 32 and Continuous burst

- Wrap / No-wrap

- Latency : 4(Variable) @ 104MHz 3(Variable) @ 80MHz 2(Variable) @ 66MHz

- Burst stop

- Burst read suspend

- Burst write data masking

### PRODUCT FAMILY

|                                                                                               | Rc<br>Ad          | ⊶<br>ww<br>Idresses | <br>Row<br>select                            |   | Memory<br>Array             | ← Vcc<br>← Vcca<br>← Vss |

|-----------------------------------------------------------------------------------------------|-------------------|---------------------|----------------------------------------------|---|-----------------------------|--------------------------|

| 1/08~                                                                                         | I/Oo~I/O<br>I/O15 |                     | Data<br>cont<br>Data<br>cont<br>Data<br>cont | ] | VO Circuit<br>Column Select |                          |

| CLK<br>CS<br>AD<br>BU<br>BU<br>BU<br>BU<br>BU<br>BU<br>BU<br>BU<br>BU<br>BU<br>BU<br>BU<br>BU | $\rightarrow$     | ntrol Logi          | WAIT                                         |   |                             |                          |

Clk gen

Pre-charge circuit

|                |                              |                      |           |        | Current Consumption          |                            |  |  |

|----------------|------------------------------|----------------------|-----------|--------|------------------------------|----------------------------|--|--|

| Product Family | Operating Mode <sup>1)</sup> | Operating Temp.      | Vcc Range | Speed  | Standby<br>(Isв1, Max.)      | Operating<br>(Icc2P, Max.) |  |  |

| K1B5616BAM-I   | Mode 1 & Mode 2              | Industrial(-25~85°C) | 1.7~1.95V | 104MHz | 350μA < 85°C<br>200μA < 40°C | 20mA                       |  |  |

1) Mode1 : Asynchronous read / Asynchronous write

Mode2 : Synchronous burst read / Asynchronous write

### **TERMINOLOGY DESCRIPTION**

| Name       | Function               | Туре         | Description                                                                                                                                                                                                                                                                                                            |

|------------|------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK        | Clock                  | Input        | Synchronizes the memory to the system operating frequency during syn-<br>chronous operations. Commands are referenced to CLK.                                                                                                                                                                                          |

| ADV        | Address Valid          | Input        | Indicates that a valid address is present on the address inputs.<br>Addresses can be latched on the rising edge of ADV during asynchro-<br>nous READ and WRITE operations.                                                                                                                                             |

| PS         | Mode Register set      | Input        | $\overline{\text{PS}}$ low enables Mode Register to be set and enables either PAR or DPD to be set.                                                                                                                                                                                                                    |

| cs         | Chip Select            | Input        | $\overline{CS}$ low enables the chip to be active $\overline{CS}$ high disables the chip and puts it into standby mode or deep power down mode.                                                                                                                                                                        |

| OE         | Output Enable          | Input        | Enables the output buffers when LOW. when $\overline{\text{OE}}$ is HIGH, the output buffers are disabled.                                                                                                                                                                                                             |

| WE         | Write Enable           | Input        | $\overline{\text{WE}}$ low enables the chip to start writing the data                                                                                                                                                                                                                                                  |

| LB         | Lower Byte (I/Oo~7)    |              | $\overline{\text{UB}}$ ( $\overline{\text{LB}}$ ) low enables upper byte (lower byte) to allow data Input/output                                                                                                                                                                                                       |

| UB         | Upper Byte (I/O8~15)   | Input        | from I/O buffers.                                                                                                                                                                                                                                                                                                      |

| A0~A23     | Address 0 ~ Address 23 | Input        | Inputs for addresses during READ and WRITE operations. Addresses are internally latched during READ and WRITE cycles.                                                                                                                                                                                                  |

| I/O0~I/O15 | Data Inputs / Outputs  | Input/Output | Depending on $\overline{UB}$ or $\overline{LB}$ status,<br>word(16-bit, $\overline{UB} \& \overline{LB}$ low) data,<br>upper byte(8-bit, $\overline{UB}$ low & $\overline{LB}$ high) data or<br>lower byte(8-bit, $\overline{LB}$ low & $\overline{UB}$ high) data is loaded                                           |

| Vcc        | Voltage Source         | Power        | Device Power supply. Power supply for device core operation.                                                                                                                                                                                                                                                           |

| VCCQ       | I/O Voltage Source     | Power        | I/O Power supply. Power supply for input/output buffers.                                                                                                                                                                                                                                                               |

| Vss        | Ground Source          | GND          | Ground for device core operation                                                                                                                                                                                                                                                                                       |

| Vssq       | I/O Ground Source      | GND          | Ground for input/output buffers                                                                                                                                                                                                                                                                                        |

| WAIT       | Valid Data Indicator   | Output       | The $\overline{\text{WAIT}}$ signal is output signal indicating the status of the data on the bus whether or not it is valid. $\overline{\text{WAIT}}$ is asserted when a burst crosses a word-line boundary. $\overline{\text{WAIT}}$ is asserted and should be ignored during asynchronous and page mode operations. |

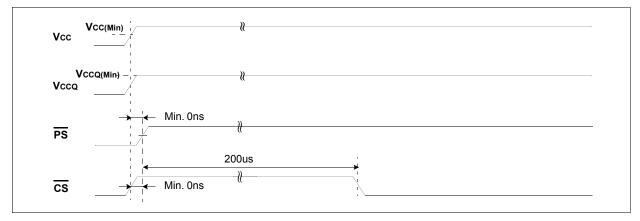

#### POWER UP SEQUENCE

After Vcc and Vccq reach minimum operating voltage(1.7V), drive  $\overline{CS}$  High first and then drive  $\overline{PS}$  High. Then the device gets into the Power Up mode. Wait for minimum 200µs to get into the normal operation mode. During the Power Up mode, the standby current can not be guaranteed. To get the stable standby current level, at least one cycle of active operation should be implemented regardless of wait time duration. To get the appropriate device operation, be sure to keep the following power up sequence. MODE1(Asynchronous Read / Asynchronous Write) is set up after power up, but this mode is not always guaranteed.

#### MODE STATE MACHINE

1) Refer to MRS(Mode Register Set).

#### **ABSOLUTE MAXIMUM RATINGS**

| Item                                 | Symbol    | Ratings           | Unit |

|--------------------------------------|-----------|-------------------|------|

| Voltage on any pin relative to Vss   | VIN, VOUT | -0.2 to VCCQ+0.3V | V    |

| Power supply voltage relative to Vss | Vcc, Vccq | -0.2 to 2.5V      | V    |

| Power Dissipation                    | PD        | 1.0               | W    |

| Storage temperature                  | Тѕтс      | -65 to 150        | °C   |

| Operating Temperature                | Та        | -25 to 85         | °C   |

1) Stresses greater than "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation should be restricted to be used under recommended operating condition. Exposure to absolute maximum rating conditions longer than 1 second may affect reliability.

#### **RECOMMENDED DC OPERATING CONDITIONS**

| Item                       | Symbol    | Min                | Тур | Max        | Unit |

|----------------------------|-----------|--------------------|-----|------------|------|

| Power supply voltage(Core) | Vcc       | 1.7                | 1.8 | 1.95       | V    |

| Power supply voltage(I/O)  | Vccq      | 1.7                | 1.8 | 1.95       | V    |

| Ground                     | Vss, Vssq | 0                  | 0   | 0          | V    |

| Input high voltage         | Vін       | 0.8 x VCCQ         | -   | VCCQ+0.22) | V    |

| Input low voltage          | VIL       | -0.2 <sup>3)</sup> | -   | 0.4        | V    |

1. TA=-25 to 85°C, otherwise specified.

2. Overshoot: Vccq +1.0V in case of pulse width ≤20ns. Overshoot is sampled, not 100% tested.

3. Undershoot: -1.0V in case of pulse width ≤20ns. Undershoot is sampled, not 100% tested.

#### CAPACITANCE (f=1MHz, TA=25°C)

| Item                     | Symbol | Test Condition | Min | Max | Unit |

|--------------------------|--------|----------------|-----|-----|------|

| Input capacitance        | CIN    | VIN=0V         | -   | 8   | pF   |

| Input/Output capacitance | Сю     | VIO=0V         | -   | 8   | pF   |

#### **DC AND OPERATING CHARACTERISTICS**

| ltem                               | Symbol              | Test Conditions                                                                                 |                |              | Min | Тур | Max | Unit |

|------------------------------------|---------------------|-------------------------------------------------------------------------------------------------|----------------|--------------|-----|-----|-----|------|

| Input Leakage Current              | Iц                  | VIN=Vss to Vccq                                                                                 |                | -1           | -   | 1   | μA  |      |

| Output Leakage Current             | Ilo                 | CS=VIH, PS=VIH, OE=VIH or WE=VIL, VIO=VS                                                        | ss to Vcc      | Q            | -1  | -   | 1   | μA   |

| Average Operating                  | ICC2 <sup>6)</sup>  | Cycle time=70ns, IIO=0mA <sup>4)</sup> , 100% duty, $\overline{CS}$ =VIL, $\overline{I}$        | PS=VIH, VI     | N=VIL or VIH | -   | -   | 35  | mA   |

| Current(Async)                     | ICC2P               | Cycle time=tRC+3tPC, IIO=0mA <sup>4)</sup> , 100% duty, <del>CS</del> =<br>VIH                  | IH, VIN=VIL or | -            | -   | 20  | mA  |      |

| Average Operating<br>Current(Sync) | Іссз                | Burst Length 4, Latency 5, 80MHz, IIO=0mA <sup>4)</sup> , Add<br>CS=VIL, PS=VIH, VIN=VIL or VIH | ition 1 time,  | -            | -   | 35  | mA  |      |

| Output Low Voltage                 | Vol                 | IoL=0.1mA                                                                                       |                | -            | -   | 0.2 | V   |      |

| Output High Voltage                | Vон                 | IOH=-0.1mA                                                                                      |                |              | 1.4 | -   | -   | V    |

| Standby Current(CMOS)              | SB1 <sup>1)</sup>   | $\overline{CS} \ge VCCQ-0.2V, \overline{PS} \ge VCCQ-0.2V, Other inputs=Vss$                    | <              | 40°C         | -   | -   | 200 | μA   |

| Standby Current(CMOS)              | 1981.4              | or VCCQ (Toggle is not allowed) <sup>5)</sup>                                                   | <              | 85°C         | -   | -   | 350 | μA   |

|                                    |                     |                                                                                                 | < 40°C         | 1/2 Block    | -   | -   | 180 |      |

| Partial Refresh Current            | SBP <sup>2)</sup>   | PS≤0.2V, CS≥VCCQ-0.2V, Other inputs=Vss or                                                      | < 40 C         | 1/4 Block    | -   | -   | 150 | μA   |

| Parlia Reliesh Current             | ISBP <sup>2</sup> / | VCCQ (Toggle is not allowed) <sup>5)</sup>                                                      | < 95°C         | 1/2 Block    | -   | -   | 250 |      |

|                                    |                     |                                                                                                 | < 85°C         | 1/4 Block    | -   | -   | 220 | μA   |

| Deep Power Down Current            | ISBD                | $\overline{PS} \le 0.2V$ , $\overline{CS} \ge VCCQ - 0.2V$ , Other inputs=Vss or                | <              | 85°C         | -   | -   | 10  | μA   |

1. ISB1 is measured 60ms after  $\overline{CS}$  high. CLK should be fixed at high or at Low.

2. Full Array Partial Refresh Current(ISBP) is same as Standby Current(ISB1).

3. Internal TCSR (Temperature Compensated Self Refresh) is used to optimize refresh cycle below 40°C.

4. IIO=0mA; This parameter is specified with the outputs disabled to avoid external loading effects.

5. VIN=0V; all inputs should not be toggle. 6. Clock should not be inserted between  $\overline{\text{ADV}}$  low and  $\overline{\text{WE}}$  low during Write operation.

#### MRS (MODE REGISTER SET)

The mode registers store the values for the various modes to make UtRAM suitable for a various applications through MRS. There are two ways to perform MRS. One is PS pin MRS and the other is Software MRS. The mode registers have lots of fields and each field consists of several options. Refer to the Table below for detailed Mode Register Setting. A19~A23 addresses are "Don't care" in Mode Register Setting.

#### MRS CODE

MRS code consists of 12 categories and several options in each category. RARS, PARA, PAR and DPD are related to power saving, BL, WC, Latency, Wrap, WP, MS and IL are related to bus operation and DS is related to device output impedance.

#### Mode Register Setting according to field of function

| J        |     | <u> </u> | J       |     | -    |         |    |       |     |     |      |       |

|----------|-----|----------|---------|-----|------|---------|----|-------|-----|-----|------|-------|

| Address  | A18 | A17~A16  | A15~A14 | A13 | A12  | A11~A9  | A8 | A7~A5 | A4  | A3  | A2   | A1~A0 |

| Function | IL  | DS       | MS      | WP  | Wrap | Latency | WC | BL    | DPD | PAR | PARA | PARS  |

| I   | Initial Latency |     | Driver | Strength   | Mode Select |     |                                           |  |  |

|-----|-----------------|-----|--------|------------|-------------|-----|-------------------------------------------|--|--|

| A18 | IL              | A17 | A16    | DS         | A15         | A14 | MS                                        |  |  |

| 0   | Fixed           | 0   | 0      | Full Drive | 0           | 0   | Mode 1(Async. 4 Page Read / Async. Write) |  |  |

| 1   | Variable        | 0   | 1      | 1/2 Drive  | 0           | 1   | Mode 2(Sync. Burst Read / Async. Write)   |  |  |

|     |                 | 1   | 0      | 1/4 Drive  |             |     |                                           |  |  |

| WA  | AIT Polarity            |     | Wrap    |     | Latend | cy Co | unt     | Wait | Configuration   |    | Burst Length |    |                          |

|-----|-------------------------|-----|---------|-----|--------|-------|---------|------|-----------------|----|--------------|----|--------------------------|

| A13 | <b>WP</b> <sup>1)</sup> | A12 | Wrap    | A11 | A10    | A9    | Latency | A8   | wc              | A7 | A6           | A5 | BL                       |

| 0   | Low Enable              | 0   | Wrap    | 1   | 0      | 0     | 2       | 0    | One clock prior | 0  | 1            | 0  | 4 word                   |

| 1   | High Enable             | 1   | No-Wrap | 0   | 0      | 0     | 3       | 1    | At data         | 0  | 1            | 1  | 8 word                   |

|     |                         |     |         | 0   | 0      | 1     | 4       |      |                 | 1  | 0            | 0  | 16 word                  |

|     |                         |     |         | 0   | 1      | 0     | 5       |      |                 | 1  | 0            | 1  | 32 word                  |

|     |                         |     |         | 0   | 1      | 1     | 6       |      |                 | 1  | 1            | 1  | Continuous <sup>2)</sup> |

|     |                         |     |         | 1   | 0      | 1     | 7       |      |                 |    |              |    |                          |

|     |                         |     |         | 1   | 1      | 0     | 8       |      |                 |    |              |    |                          |

|     |                         |     |         | 1   | 1      | 1     | 9       |      |                 |    |              |    |                          |

| Deep Power Down |             | Partial Array Refresh |             |    | PAR Array    | PAR Size |    |            |  |

|-----------------|-------------|-----------------------|-------------|----|--------------|----------|----|------------|--|

| A4              | DPD         | PD A3 PAR             |             | A2 | PARA         | A1       | A0 | PARS       |  |

| 0               | DPD Enable  | 0                     | PAR Enable  | 0  | Bottom Array | 0        | 0  | Full Array |  |

| 1               | DPD Disable | 1                     | PAR Disable | 1  | Top Array    | 1        | 0  | 1/2 Array  |  |

|                 |             |                       |             |    |              | 1        | 1  | 1/4 Arrav  |  |

[Note]

- A19~A23 addresses are "Don't care" & reserved for future use.

The modes are set automatically to default modes which are 4 Page Read and Asynchronous Write / DPD disable / PAR disable after power up or DPD exit.

1) WP[0]; The data is available when WAIT signal is High. All the timings in this spec are illustrated based on this mode.

WP[1]; The data is available when WAIT signal is Low.

2) Refresh command will be denied during continuous operation. CS low should not be longer than tBC(max. 1.2us)

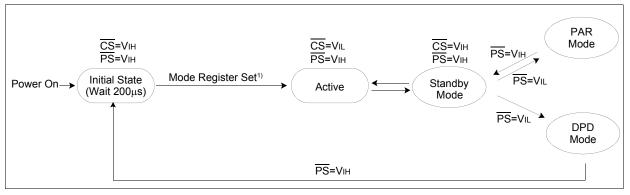

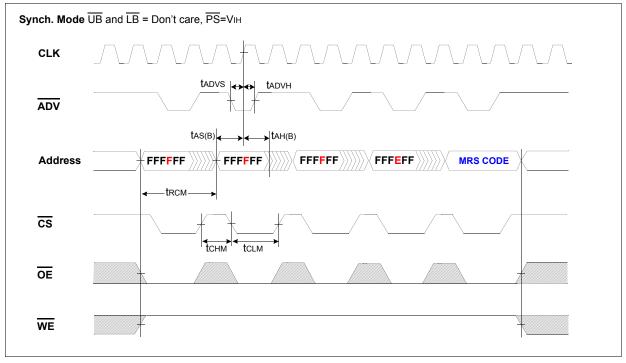

#### MRS TIMING WAVEFORM (SOFTWARE)

Software MRS timing consists of 5 Read cycles. Each cycle is normal Read cycle.  $\overline{\text{CS}}$  pin should be toggling between cycles. 1st, 2nd and 3rd cycle should be FFFFF(h), 4th cycle should be FFFEFF(h) and 5th cycle should be MRS code

Note) Above timing and address condition should not be used in the normal operation. The above condition should be used only for the mode register setting purpose.

| Parameter List               | Symbol | Min | Max | Units | Parameter List                   | Symbol | Min | Max | Units |

|------------------------------|--------|-----|-----|-------|----------------------------------|--------|-----|-----|-------|

| ADV setup time to clock      | tadvs  | 3   | -   | ns    | Read cycle time                  | trcм   | 70  | -   | ns    |

| ADV hold time from clock     | tadvh  | 2   | -   | ns    | $\overline{\text{CS}}$ high time | tснм   | 10  | -   | ns    |

| Address setup time to clock  | tAS(B) | 3   | -   | ns    | CS low time                      | tсьм   | 60  | -   | ns    |

| Address hold time from clock | tah(b) | 2   | -   | ns    |                                  |        |     |     |       |

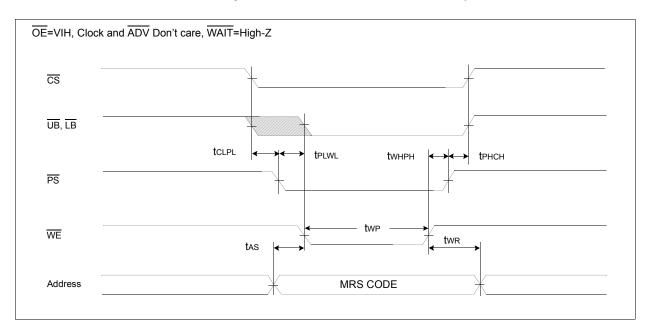

MRS TIMING WAVEFORM (PS Pin) MRS can be implemented using by PS pin. Serial assertion of control signals of CS , UB & LB, PS and WE will get the device to be ready for MRS. MRS CODE should be set up before WE low and keep the CODE until one of those control signals desserts. MRS terminates when one of those control signals desserts. Clock & ADV are don't care in Asynchronous mode.

| Parameter List |                                              | Symbol        | Sp  | Unite |       |

|----------------|----------------------------------------------|---------------|-----|-------|-------|

|                | Parameter List                               |               | Min | Max   | Units |

|                | CS Low to PS Low                             | <b>t</b> CLPL | 0   | -     | ns    |

| MDO            | PS Low to WE Low                             | <b>t</b> PLWL | 0   | -     | ns    |

| MRS            | $\overline{WE}$ High to $\overline{PS}$ High | twнpн         | 0   | -     | ns    |

|                | PS High to CS High                           | tрнсн         | 0   | -     | ns    |

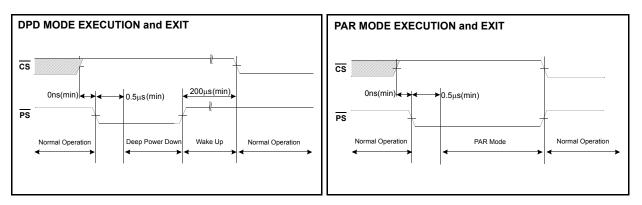

#### PAR (Partial Array Refresh) mode [A3~A1]

User can select half array, a fourth array as active memory array. The active memory array is periodically refreshed(data stored), whereas the disabled array is not going to be refreshed and so the previously stored data will be invalid. When re-enabling additional portions of the array, the new portions are available immediately upon writing to the MRS.

#### PAR mode execution;

- 1) Mode Register Setting into PAR enable(A3=0)

- DPD enabled setting(A4=0) has higher priority to PAR enabled setting(A3=0). A4=1 is necessary to use PAR mode.

- 2) PAR mode Enter; keep PS signal at VIL for longer than 0.5µs during standby mode (Mode Register: A4=1 & A3=0).

- 3) PAR mode Exit; The device returns to the standby mode when PS signal goes to VIH during PAR mode.

- \* Mode register values are not changed after the device has been to PAR mode.

#### DPD (Deep Power Down) mode [A4]

The deep power down mode disables all the refresh related activities. This mode can be used when the system needs to save power. The data become invalid when DPD mode is executed.

#### DPD mode execution ;

1) Mode Register Setting into DPD enable(A4=0)

2) DPD mode Enter; keep PS signal at Vi∟ for more than 0.5µs during standby mode (Mode Register: A4=0).

3) DPD mode Exit; The device returns to initial State when PS signal goes to VIH during DPD mode. Wake up sequence is needed for the device to do normal operation.

\* Mode register values are initialized to default value after the device has been to DPD mode.

Default modes are 4 Page Read and Asynchronous Write / DPD disable / PAR disable.

#### STANDBY MODE CHARACTERISTICS

| Power Mode                 | Address<br>(Bottom Array) <sup>2)</sup> | Address<br>(Top Array) <sup>2)</sup> | Memory<br>Cell Data | Standby <sup>3)</sup><br>(Isв1, <40°С) | Standby <sup>3)</sup><br>(Isв1, <85°C) | Wait<br>Time(μs) |

|----------------------------|-----------------------------------------|--------------------------------------|---------------------|----------------------------------------|----------------------------------------|------------------|

| Standby(Full Array)        | 000000h ~ FFFFFFh                       | 000000h ~ FFFFFFh                    | Valid <sup>1)</sup> | TBD                                    | TBD                                    | 0                |

| Partial Refresh(1/2 Block) | 000000h ~ 7FFFFh                        | 800000h ~ FFFFFFh                    | Valid <sup>1)</sup> | TBD                                    | TBD                                    | 0                |

| Partial Refresh(1/4 Block) | 000000h ~ 3FFFFFh                       | C00000h ~ FFFFFFh                    | Valid <sup>1)</sup> | TBD                                    | TBD                                    | 0                |

| Deep Power Down            | 000000h ~                               | Invalid                              | TBD                 | TBD                                    | 200                                    |                  |

1. Only the data in the selected block are valid

2. PAR Array can be selected through Mode Register Set

3. Standby mode is supposed to be set up after at least one active operation after power up.

ISB1 is measured after 60ms from the time when standby mode is set up.

#### Burst Length [A7~A5] & Wrap [A12]

The device supports 4 word, 8 word, 16 word, 32 word and Continuous burst read or write. and Wrap & No-Wrap are supported for Burst sequence.

|      |       |         |                        | Burst Address Sequence(Decimal)                   |                                             |

|------|-------|---------|------------------------|---------------------------------------------------|---------------------------------------------|

| Mode | Start | 4 word  | 8 word                 | 16 word                                           | 32 word                                     |

|      | 0     | 0-1-2-3 | 0-1-2-3-4-5-6-7        | 0-1-2-3-4-5-6-7-8-9-10-11-12-13-14-15             | 0 - 1 - 2 - 3 - 4 - 5 ~ 26-27-28-29-30-31   |

|      | 1     | 1-2-3-0 | 1-2-3-4-5-6-7-0        | 1-2-3-4-5-6-7-8-9-10-11-12-13-14-15-0             | 1 - 2 - 3 - 4 - 5 - 6 ~ 27-28-29-30-31 - 0  |

|      | 2     | 2-3-0-1 | 2-3-4-5-6-7-0-1        | 2-3-4-5-6-7-8-9-10-11-12-13-14-15-0-1             | 2 - 3 - 4 - 5 - 6 - 7 ~ 28-29-30-31 - 0 - 1 |

|      | 3     | 3-0-1-2 | 3-4-5-6-7-0-1-2        | 3-4-5-6-7-8-9-10-11-12-13-14-15-0-1-2             | 3 - 4 - 5 - 6 - 7 - 8 ~ 29-30-31- 0 - 1 - 2 |

| WRAP | ~     |         | ~                      | ~                                                 | ~                                           |

| WRAF | 7     |         | 7-0-1-2-3-4-5-6        | 7-8-9-10-11-12-13-14-15-0-1-2-3-4-5-6             | 7 - 8 - 9 - 10- 11- 12 ~ 2 - 3 - 4 - 5 - 6  |

|      | ~     |         |                        | ~                                                 | ~                                           |

|      | 15    |         |                        | 15-0-1-2-3-4-5-6-7-8-9-10-11-12-13-14             | 15-16-17-18-19-20 ~ 10- 11- 12- 13- 14      |

|      | ~     |         |                        |                                                   | ~                                           |

|      | 31    |         |                        |                                                   | 31- 0 - 1 - 2 - 3 - 4 ~ 25-26-27-28-29-30   |

|      | 0     | 0-1-2-3 | 0- 1- 2- 3- 4- 5- 6 -7 | 0- 1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12-13-14-15 | 0 - 1 - 2 - 3 - 4 - 5 ~ 26-27-28-29-30-31   |

|      | 1     | 1-2-3-4 | 1- 2- 3- 4- 5- 6- 7- 8 | 1- 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12-13-14-15-16 | 1 - 2 - 3 - 4 - 5 - 6 ~ 27-28-29-30-31-32   |

|      | 2     | 2-3-4-5 | 2- 3- 4- 5- 6- 7- 8- 9 | 2- 3- 4- 5- 6- 7- 8- 9- 10- 11- 12-13-14-15-16-17 | 2 - 3 - 4 - 5 - 6 - 7 ~ 28-29-30-31-32-33   |

|      | 3     | 3-4-5-6 | 3- 4- 5- 6- 7- 8- 9-10 | 3- 4- 5- 6- 7- 8- 9- 10- 11- 12-13-14-15-16-17-18 | 3 - 4 - 5 - 6 - 7 - 8 ~ 29-30-31-32-33-34   |

| No-  | ~     |         | ~                      | ~                                                 | ~                                           |

| WRAP | 7     |         | 7-8-9-10-11-12-13-14   | 7-8-9-10-11-12-13-14-15-16-17-18-19-20-21-22      | 7 - 8 - 9 - 10-11-12 ~ 33-34-35-36-37-38    |

|      | ~     |         |                        | ~                                                 | ~                                           |

|      | 15    |         |                        | 15-16-17-18-19-20-21-22-23-24-25-26-27-28-29-30   | 15-16-17-18-19-20 ~ 41-42-43-44-45-46       |

|      | ~     |         |                        |                                                   | ~                                           |

|      | 31    | ]       |                        |                                                   | 31-32-33-34-35-36 ~ 57-58-59-60-61-62       |

1. Continuous Burst mode needs to meet tBC(max. 1.2us) parameter.

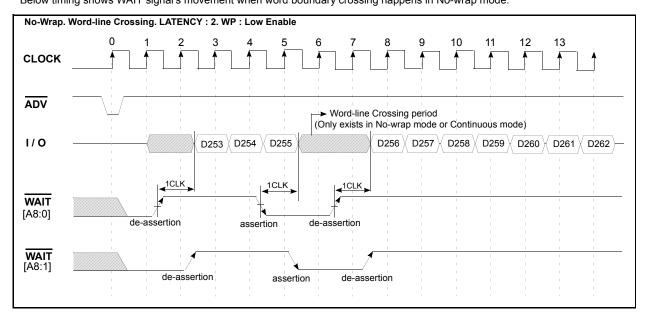

#### WAIT Configuration [A8] & WAIT Polarity [A13]

The WAIT signal is output signal indicating the status of the data on the bus whether or not it is valid. WAIT configuration is to decide the timing when WAIT asserts or desserts. WAIT asserts (or desserts) one clock prior to the data when A8 is set to 0. (WAIT asserts (or desserts) at data clock when A8 is set to 1). WAIT polarity is to decide the WAIT signal level at which data is valid or invalid. Data is valid if WAIT signal is high when A13 is set to 0. (Data is valid if WAIT signal is low when A13 is set to 1). All the timing diagrams in this SPEC are illustrated based on following setup; [A13 : 0] and [A8 : 0]. Below timing shows WAIT signal's movement when word boundary crossing happens in No-wrap mode.

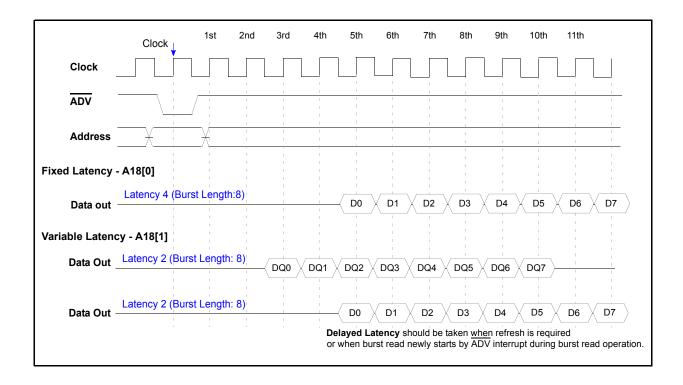

#### Latency [A11~A9]

The Latency stands for the number of clocks before the first data available from the burst command.

| ltem                      | Upto (            | 66MHz                   | Upto 8   | B0MHz                   | Upto 104MHz |             |  |

|---------------------------|-------------------|-------------------------|----------|-------------------------|-------------|-------------|--|

| nem                       | Fixed             | Variable                | Fixed    | Variable                | Fixed       | Variable    |  |

| Latency Set(A11:A10:A9)   | 4(0:0:1) 2(1:0:0) |                         | 5(0:1:0) | 3(0:0:0)                | 7(1:0:1)    | 4(0:0:1)    |  |

| Read Latency(min)         | 4                 | 2 / 41)                 | 5        | 3 / 5 <sup>1)</sup>     | 7           | 4 / 71)     |  |

| 1st Read data fetch clock | 5th               | 3rd / 5th <sup>1)</sup> | 6th      | 4th / 6th <sup>1)</sup> | 8th         | 5th / 8th1) |  |

1) Delayed Latency should be taken when refresh is required or when burst read newly starts by ADV interrupt during burst read operation.

#### Driver Strength [A17~A16]

The optimization of output driver strength is possible to adjust for the different data loadings. The device can minimize the noise generated on the data bus during read operation. The device supports full, 1/2 and 1/4 driver strength. The device's default mode is Full driver strength.

| Driver Strength | Full | 1 / 2 | 1 / 4 |

|-----------------|------|-------|-------|

| IMPEDANCE(typ.) | 40Ω  | 90Ω   | 150Ω  |

1. Impedance values are typical values, not 100% tested.

#### **OPEARTION MODE [A15~A14]**

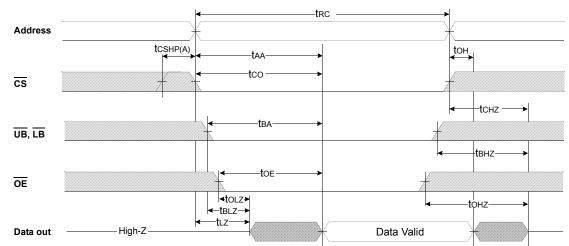

#### MODE1. ASYNCHRONOUS READ / ASYNCHRONOUS WRITE MODE

#### Asynchronous read operation

Asynchronous read operation starts when  $\overline{CS}$ ,  $\overline{OE}$  and  $\overline{UB}$  or  $\overline{LB}$  are asserted. First data come out after random access time(tAA) but second, third and fourth data come out after page access time(tPA) when using the page addresses (A0, A1).  $\overline{PS}$  and  $\overline{WE}$  should be de-asserted during read operation. Clock,  $\overline{ADV}$  are don't care during read operation and  $\overline{WAIT}$  is Hi-Z.

#### Asynchronous write operation

Asynchronous write operation starts when CS, WE and UB or LB are asserted. PS and should be de-asserted during write operation. Clock, OE, ADV are don't care during write operation and WAIT signal is Hi-Z.

| ASYNC    | CHRONOUS 4-PAGE RE | AD |   | ASYNC    | HRONOUS WRITE |        |

|----------|--------------------|----|---|----------|---------------|--------|

| A23~A2   |                    |    |   | Address  | χ             | X      |

| A1~A0    |                    |    |   | cs       |               |        |

| cs       |                    |    |   | UB, LB   |               |        |

| UB, LB   |                    |    |   | WE       |               |        |

| OE       |                    |    |   | Data in  | High-Z        |        |

| Data out |                    | -  | X | Data out | High-Z _      | High-Z |

#### FUNCTIONAL DESCRIPTION

| CS | PS | OE              | WE              | LB              | UB                     | I/O0~7 | I/O8~15 | Mode             | Power      |

|----|----|-----------------|-----------------|-----------------|------------------------|--------|---------|------------------|------------|

| н  | н  | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | <b>X</b> <sup>1)</sup> | High-Z | High-Z  | Deselected       | Standby    |

| Н  | L  | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup>        | High-Z | High-Z  | Deselected       | DPD or PAR |

| L  | н  | н               | н               | X <sup>1)</sup> | <b>X</b> <sup>1)</sup> | High-Z | High-Z  | Output Disabled  | Active     |

| L  | н  | X <sup>1)</sup> | X <sup>1)</sup> | н               | н                      | High-Z | High-Z  | Output Disabled  | Active     |

| L  | н  | L               | н               | L               | н                      | Dout   | High-Z  | Lower Byte Read  | Active     |

| L  | Н  | L               | н               | Н               | L                      | High-Z | Dout    | Upper Byte Read  | Active     |

| L  | Н  | L               | н               | L               | L                      | Dout   | Dout    | Word Read        | Active     |

| L  | н  | н               | L               | L               | н                      | Din    | High-Z  | Lower Byte Write | Active     |

| L  | Н  | н               | L               | Н               | L                      | High-Z | Din     | Upper Byte Write | Active     |

| L  | н  | Н               | L               | L               | L                      | Din    | Din     | Word Write       | Active     |

1. X means "Don't care". X should be low or high state.

2. In asynchronous mode, Clock and ADV are ignored. Clock and ADV should be low or high state.

3. /WAIT pin is High-Z in Asynchronous mode.

4. This mode(Mode 1) is supported K1B5616BAM product.

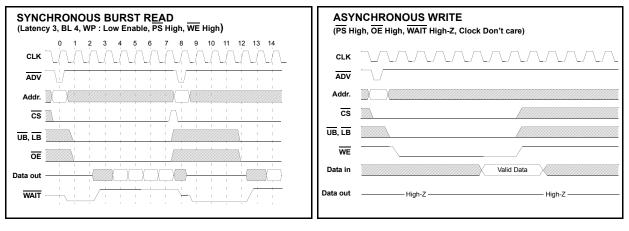

#### MODE2. SYNCHRONOUS BURST READ / ASYNCHRONOUS WRITE MODE

#### Synchronous Burst Read Operation

Burst Read command is implemented when  $\overline{\text{ADV}}$  is detected low at clock rising edge. WE should be de-asserted during Burst read, Burst operation re-starts whenever  $\overline{\text{ADV}}$  is detected low at clock rising edge even in the middle of operation. Variable latency allows the UtRAM to be configured for minimum latency at high frequencies, but the controller must monitor WAIT to detect any conflict with refresh cycles.

#### **Asynchronous Write Operation**

Asynchronous write operation starts when  $\overline{CS}$ ,  $\overline{WE}$  and  $\overline{UB}$  or  $\overline{LB}$  are asserted.  $\overline{PS}$  and should be de-asserted during write operation. Clock,  $\overline{OE}$ ,  $\overline{ADV}$  are don't care during write operation and  $\overline{WAIT}$  signal is Hi-Z.

#### FUNCTIONAL DESCRIPTION

| CS | PS | OE              | WE              | LB                     | UB                     | I/O0~7 | I/O8~15 | CLK             | ADV             | Mode             | Power   |

|----|----|-----------------|-----------------|------------------------|------------------------|--------|---------|-----------------|-----------------|------------------|---------|

| н  | Н  | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup>        | X <sup>1)</sup>        | High-Z | High-Z  | X <sup>2)</sup> | X <sup>2)</sup> | Deselected       | Standby |

| н  | L  | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup>        | X <sup>1)</sup>        | High-Z | High-Z  | X <sup>2)</sup> | X <sup>2)</sup> | Deselected       | PAR     |

| L  | Н  | н               | Н               | X <sup>1)</sup>        | X <sup>1)</sup>        | High-Z | High-Z  | X <sup>2)</sup> | н               | Output Disabled  | Active  |

| L  | Н  | X <sup>1)</sup> | X <sup>1)</sup> | н                      | н                      | High-Z | High-Z  | X <sup>2)</sup> | н               | Output Disabled  | Active  |

| L  | Н  | X <sup>1)</sup> | Н               | <b>X</b> <sup>1)</sup> | <b>X</b> <sup>1)</sup> | High-Z | High-Z  |                 |                 | Read Command     | Active  |

| L  | Н  | L               | Н               | L                      | Н                      | Dout   | High-Z  |                 | Н               | Lower Byte Read  | Active  |

| L  | Н  | L               | Н               | Н                      | L                      | High-Z | Dout    |                 | н               | Upper Byte Read  | Active  |

| L  | Н  | L               | Н               | L                      | L                      | Dout   | Dout    |                 | Н               | Word Read        | Active  |

| L  | Н  | Н               | L               | L                      | Н                      | Din    | High-Z  | X <sup>2)</sup> | or <b></b> _    | Lower Byte Write | Active  |

| L  | Н  | Н               | L               | Н                      | L                      | High-Z | Din     | X <sup>2)</sup> |                 | Upper Byte Write | Active  |

| L  | Н  | Н               | L               | L                      | L                      | Din    | Din     | X <sup>2)</sup> |                 | Word Write       | Active  |

1. X means "Don't care". X should be low or high state.

2. /WAIT is device output signal so does not have any affect to the mode definition. Please refer to each timing diagram for /WAIT pin function.

3. This mode(Mode 2) is supported only at K1B5616BAM product.

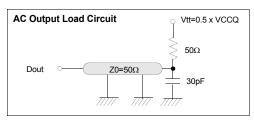

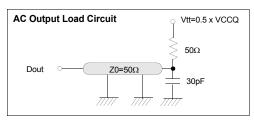

#### MODE 1 AC OPERATING CONDITIONS (ASYNCH. READ / ASYNCH. WRITE)

#### **TEST CONDITIONS**

(Test Load and Test Input/Output Reference) Input pulse level: 0.2 to Vccq-0.2V Input rising and falling time: 3ns Input and output reference voltage: 0.5 x Vccq Output load: CL=30pF Vcc:1.7V~1.95V TA: -25°C~85°C

#### AC CHARACTERISTICS

|                 |                                           |          | Sp               | eed |       |

|-----------------|-------------------------------------------|----------|------------------|-----|-------|

|                 | Parameter List                            | Symbol   | Min              | Max | Units |

| Common          | CS High Pulse Width                       | tcshp(A) | 10               | -   | ns    |

|                 | Read Cycle Time                           | trc      | 70               | -   | ns    |

|                 | Page Read Cycle Time                      | tPC      | 20               | -   | ns    |

|                 | Address Access Time                       | taa      | -                | 70  | ns    |

|                 | Page Access Time                          | tpa      | -                | 20  | ns    |

|                 | Chip Select to Output                     | tco      | -                | 70  | ns    |

|                 | Output Enable to Valid Output             | tOE      | -                | 20  | ns    |

| Asynch.         | UB, LB Access Time                        | tBA      | -                | 20  | ns    |

| Asynch.<br>Read | Chip Select to Low-Z Output               | tLZ      | 10               | -   | ns    |

|                 | UB, LB Enable to Low-Z Output             | tBLZ     | 5                | -   | ns    |

|                 | Output Enable to Low-Z Output             | toLz     | 5                | -   | ns    |

|                 | Chip Disable to High-Z Output             | tснz     | 0                | 10  | ns    |

|                 | UB, LB Disable to High-Z Output           | tвнz     | 0                | 10  | ns    |

|                 | Output Disable to High-Z Output           | tонz     | 0                | 10  | ns    |

|                 | Output Hold                               | tон      | 5                | -   | ns    |

|                 | Write Cycle Time                          | twc      | 70               | -   | ns    |

|                 | Chip Select to End of Write               | tcw      | 60               | -   | ns    |

|                 | Address Set-up Time to Beginning of Write | tas      | 0                | -   | ns    |

|                 | Address Valid to End of Write             | taw      | 60               | -   | ns    |

| Asynch.         | UB, LB Valid to End of Write              | tвw      | 60               | -   | ns    |

| Write           | Write Pulse Width                         | twp      | 55 <sup>1)</sup> | -   | ns    |

| Write           | WE High Pulse Width                       | twhp     | 5                | -   | ns    |

|                 | Write Recovery Time                       | twR      | 0                | -   | ns    |

|                 | Data to Write Time Overlap                | tow      | 20               | -   | ns    |

|                 | Data Hold from Write Time                 | tDH      | 0                | -   | ns    |

1. twp(min)=70ns for continuous write without CS toggling longer than 1.2us

2. The High-Z timings measure a 100mV transition from either VOH or VOL toward VCCQ x 0.5

3. The Low-Z timings measure a 100mV transition away from the High-Z level toward either VOH or VOL.

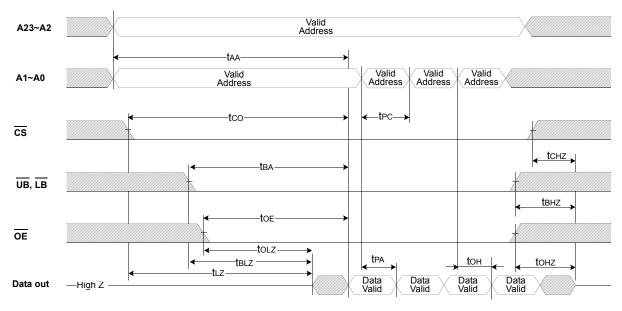

#### TIMING WAVEFORMS (ASYNCH. READ / ASYNCH. WRITE)

Asynch. READ (PS=VIH, WE=VIH, WAIT=High-Z)

#### Asynch. PAGE READ

(PS=VIH, WE=VIH, WAIT=High-Z)

1. tCHZ and tOHZ are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels. 2. At any given temperature and voltage condition, tCHZ(Max.) is less than tLZ(Min.) both for a given device and from device to device interconnection.

3. In asynchronous read cycle, Clock and  $\overline{\text{ADV}}$  signals are ignored.

4. If invalid address signals shorter than min. tRC are continuously repeated for over 1.2us, the device needs a normal read timing(tRC) or needs to sustain standby state for min. tRC at least once in every 1.2us.

5. In asynchronous 4 page read cycle, Clock and ADV signals are ignored.

#### Asynch. WRITE (1)

1. A write occurs during the overlap(twp) of low  $\overline{CS}$  and low  $\overline{WE}$ . A write begins when  $\overline{CS}$  goes low and  $\overline{WE}$  goes low with asserting  $\overline{UB}$  or  $\overline{LB}$  for single byte operation or simultaneously asserting UB and LB for double byte operation. A write ends at the earliest transition when  $\overline{CS}$  goes high or  $\overline{WE}$  goes high. The twp is measured from the beginning of write to the end of write.

2. tcw is measured from the  $\overline{CS}$  going low to the end of write.

3. tas is measured from the address valid to the beginning of write.

4. twr is measured from the end of write to the address change. twr is applied in case a write ends with  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  going high.

5. In asynchronous write cycle, Clock and ADV signals are ignored.

6. Condition for continuous write operation over 15 times : tWP(min)=70ns

### MODE 2 AC OPERATING CONDITIONS (SYNCH. READ / ASYNCH. WRITE)

#### **TEST CONDITIONS**

(Test Load and Test Input/Output Reference) Input pulse level: 0.2 to Vccq-0.2V Input rising and falling time: 1ns Input and output reference voltage: 0.5 x Vccq Output load: CL=30pF Vcc:1.7V~1.95V TA: -25°C~85°C

#### AC CHARACTERISTICS

|                      | Downworken Lint                         | Ourse had            | 66N | /IHz | 801  | /IHz | 104 | MHz  | Unite |

|----------------------|-----------------------------------------|----------------------|-----|------|------|------|-----|------|-------|

|                      | Parameter List                          | Symbol               | Min | Max  | Min  | Max  | Min | Max  | Units |

|                      | Clock Cycle Time                        | Т                    | 15  | 200  | 12.5 | 200  | 9.6 | 200  | ns    |

|                      | Burst Cycle Time                        | tвc                  | -   | 1200 | -    | 1200 | -   | 1200 | ns    |

|                      | Address Set-up Time to clock            | tas(b)               | 3   | -    | 3    | -    | 3   | -    | ns    |

|                      | Address Hold Time from clock            | tAH(B)               | 2   | -    | 2    | -    | 2   | -    | ns    |

|                      | ADV Setup Time to clock                 | tadvs                | 3   | -    | 3    | -    | 3   | -    | ns    |

|                      | ADV Hold Time from clock                | tadvh                | 2   | -    | 2    | -    | 2   | -    | ns    |

|                      | CS Setup Time to clock                  | tcss(B)              | 3   | -    | 3    | -    | 3   | -    | ns    |

|                      | CS High to ADV Low (Burst Stop)         | tbsadv <sup>1)</sup> | 0   |      | 0    |      | 0   |      | ns    |

|                      | CS Low Hold Time from Clock(Burst Stop) | <b>t</b> CSLH        | 2   | -    | 2    | -    | 2   | -    | ns    |

|                      | CS High Pulse Width                     | tcshp                | 5   | -    | 5    | -    | 5   | -    | ns    |

|                      | CS Low to WAIT Low                      | tw∟                  | -   | 12   | -    | 12   | -   | 12   | ns    |

| Synch. Burst<br>Read | Clock to WAIT High                      | twн                  | -   | 11   | -    | 9    | -   | 7    | ns    |

| rioud                | CS High to WAIT High-Z                  | twz                  | -   | 10   | -    | 10   | -   | 10   | ns    |

|                      | UB, LB Low to End of Latency Clock      | <b>t</b> BEL         | 20  | -    | 20   | -    | 20  | -    | ns    |

|                      | OE Low to End of Latency Clock          | toel                 | 20  | -    | 20   | -    | 20  | -    | ns    |

|                      | UB, LB Low to Low-Z Output              | tBLZ                 | 5   | -    | 5    | -    | 5   | -    | ns    |

|                      | OE Low to Low-Z Output                  | tolz                 | 5   | -    | 5    | -    | 5   | -    | ns    |

|                      | Clock Rising to Data Output             | tcp                  | -   | 11   | -    | 9    | -   | 7    | ns    |

|                      | Output Hold from clock                  | toh(b)               | 2   | -    | 2    | -    | 2   | -    | ns    |

|                      | Burst End Clock to Output High-Z        | tнz                  | -   | 10   | -    | 10   | -   | 10   | ns    |

|                      | CS High to Output High-Z                | tснz                 | -   | 10   | -    | 10   | -   | 10   | ns    |

|                      | OE High to Output High-Z                | tонz                 | -   | 10   | -    | 10   | -   | 10   | ns    |

|                      | UB, LB High to Output High-Z            | tвнz                 | -   | 10   | -    | 10   | -   | 10   | ns    |

1. Refresh can not be implemented when tBSADV is in the range of 0ns ~ 13ns. It may cause Refresh fail to use the device under that condition over 1.2us without CS toggling. To avoid Refresh fail, 13ns for all frequency is needed for tBSADV.

2. The High-Z timings measure a 100mV transition from either VOH or VOL toward VCCQ x 0.5

3. The Low-Z timings measure a 100mV transition away from the High-Z level toward either VOH or VOL.

|               | Parameter List                            | Symphol | Spee             | d   | Units |

|---------------|-------------------------------------------|---------|------------------|-----|-------|

|               | Parameter List                            | Symbol  | Min              | Max | Units |

|               | Write Cycle Time                          | twc     | 70               | -   |       |

|               | Chip Select to End of Write               | tcw     | 60               | -   | ns    |

|               | ADV Minimum Low Pulse Width               | tadv    | 5                | -   | ns    |

|               | Address Set-up Time to Beginning of Write | tas     | 0                | -   | ns    |

|               | Address Set-up Time to ADV Rising         | tas(a)  | 5                | -   | ns    |

|               | Address Hold Time from ADV Rising         | tah(a)  | 3                | -   | ns    |

| Asynch. Write | CS Setup Time to ADV Rising               | tcss(A) | 5                | -   | ns    |

|               | Address Valid to End of Write             | taw     | 60               | -   | ns    |

|               | UB, LB Valid to End of Write              | tвw     | 60               | -   | ns    |

|               | Write Pulse Width                         | twp     | 55 <sup>1)</sup> | -   | ns    |

|               | Write Recovery Time                       | twr     | 0                | -   | ns    |

|               | Data to Write Time Overlap                | tow     | 20               | -   | ns    |

|               | Data Hold from Write Time                 | tDH     | 0                | -   | ns    |

1. tWP(min)=70ns for continuous write longer than 1.2us without CS toggling.

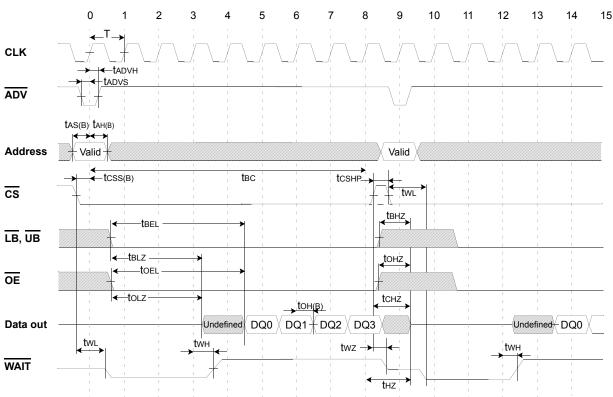

#### TIMING WAVEFORMS (SYNCH. READ / ASYNCH. WRITE)

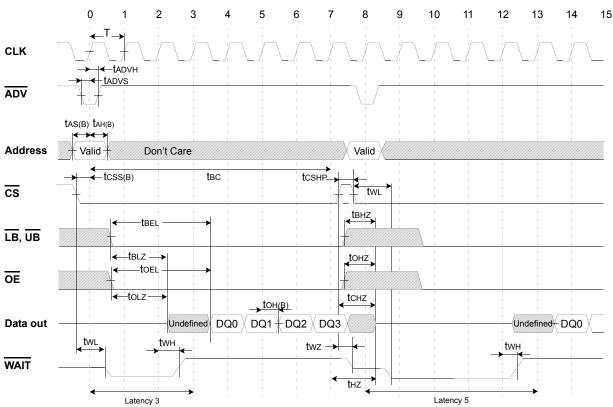

#### Burst READ - Fixed Latency

(PS=VIH, WE=VIH, WAIT=High-Z, Latency=4, Burst Length=4, WP=Low enable, WC=one clock prior to the data)

1. /WAIT Low(tWL) : Data not available(driven by  $\overline{CS}$  low going edge or  $\overline{ADV}$  low going edge) /WAIT High(tWH) : Data available(driven by Latency-1 clock) /WAIT High-Z(tWZ) : Data don't care(driven by  $\overline{CS}$  high going edge)

2. Multiple clock risings are allowed during low ADV period. The data starts after set Latency from the last clock rising.

3. Burst operation should not be longer than  $tBC(1.2\mu s)$

| Ourseland     | 661 | ٨Hz  | 80MHz |      | 104MHz |      | Units | Ourseland    | 661 | MHz | 80MHz |     | 104 | Units |       |

|---------------|-----|------|-------|------|--------|------|-------|--------------|-----|-----|-------|-----|-----|-------|-------|

| Symbol        | Min | Max  | Min   | Max  | Min    | Max  | Units | Symbol       | Min | Max | Min   | Max | Min | Max   | Units |

| Т             | 15  | 200  | 12.5  | 200  | 9.6    | 200  | ns    | <b>t</b> BLZ | 5   | -   | 5     | -   | 5   | -     | ns    |

| tвc           | -   | 1200 | -     | 1200 | -      | 1200 | ns    | ns tolz      |     | -   | 5     | -   | 5   | -     | ns    |

| tadvs         | 3   | -    | 3     | -    | 3      | -    | ns    | tHZ          | -   | 10  | -     | 10  | -   | 10    | ns    |

| <b>t</b> advh | 2   | -    | 2     | -    | 2      | -    | ns    | tснz         | -   | 10  | -     | 10  | -   | 10    | ns    |

| tas(b)        | 3   | -    | 3     | -    | 3      | -    | ns    | tонz         | -   | 10  | -     | 10  | -   | 10    | ns    |

| tah(B)        | 2   | -    | 2     | -    | 2      | -    | ns    | tвнz         | -   | 10  | -     | 10  | -   | 10    | ns    |

| tcss(B)       | 3   | -    | 3     | -    | 3      | -    | ns    | tcD          | -   | 11  | -     | 9   | -   | 7     | ns    |

| <b>t</b> CSHP | 5   | -    | 5     | -    | 5      | -    | ns    | toh(b)       | 2   | -   | 2     | -   | 2   | -     | ns    |

| <b>t</b> BEL  | 20  | -    | 20    | -    | 20     | -    | ns    | tw∟          | -   | 12  | -     | 12  | -   | 12    | ns    |

| <b>t</b> OEL  | 20  | -    | 20    | -    | 20     | -    | ns    | twн          | -   | 11  | -     | 9   | -   | 7     | ns    |

| twz           | -   | 10   | -     | 10   | -      | 10   | ns    |              |     |     |       |     |     |       |       |

### http://www.BDTIC.com/SAMSUNG Preliminary UtRAM

### K1B5616BAM

#### **Burst READ - Variable Latency**

(PS=VIH, WE=VIH, WAIT=High-Z, Latency=3, Burst Length=4, WP=Low enable, WC=one clock prior to the data)

1. Delayed Latency should be taken increased when refresh is required. Refer to Latency Table.

/WAIT Low(tWL) : Data not available(driven by CS low going edge or ADV low going edge) /WAIT High(tWH) : Data available(driven by Latency-1 clock)

/WAIT High (WI): Data don't care (driven by CS high going edge) 3. Multiple clock risings are allowed during low ADV period. The data starts after set Latency from the last clock rising.

4. Burst operation should not be longer than tBC(1.2 $\mu$ s)

| Querra ha a l | 66N | /IHz | 80N  | ЛНz  | 104 | MHz  | L lusita | Quanta al           | 661 | ИНz | 801 | ИНz | 104 | Unite |       |

|---------------|-----|------|------|------|-----|------|----------|---------------------|-----|-----|-----|-----|-----|-------|-------|

| Symbol        | Min | Max  | Min  | Max  | Min | Мах  | Units    | Symbol              | Min | Max | Min | Max | Min | Max   | Units |

| Т             | 15  | 200  | 12.5 | 200  | 9.6 | 200  | ns       | ns t <sub>BLZ</sub> |     | -   | 5   | -   | 5   | -     | ns    |

| tвc           | -   | 1200 | -    | 1200 | -   | 1200 | ns       | tolz                | 5   | -   | 5   | -   | 5   | -     | ns    |

| tadvs         | 3   | -    | 3    | -    | 3   | -    | ns       | tнz                 | -   | 10  | -   | 10  | -   | 10    | ns    |

| tadvh         | 2   | -    | 2    | -    | 2   | -    | ns       | tснz                | -   | 10  | -   | 10  | -   | 10    | ns    |

| tas(b)        | 3   | -    | 3    | -    | 3   | -    | ns       | tонz                | -   | 10  | -   | 10  | -   | 10    | ns    |

| tAH(B)        | 2   | -    | 2    | -    | 2   | -    | ns       | tвнz                | -   | 10  | -   | 10  | -   | 10    | ns    |

| tCSS(B)       | 3   | -    | 3    | -    | 3   | -    | ns       | tcp                 | -   | 11  | -   | 9   | -   | 7     | ns    |

| <b>t</b> CSHP | 5   | -    | 5    | -    | 5   | -    | ns       | toh(b)              | 2   | -   | 2   | -   | 2   | -     | ns    |

| <b>t</b> BEL  | 20  | -    | 20   | -    | 20  | -    | ns       | tw∟                 | -   | 12  | -   | 12  | -   | 12    | ns    |

| toel          | 20  | -    | 20   | -    | 20  | -    | ns       | twн                 | -   | 11  | -   | 9   | -   | 7     | ns    |

| twz           | -   | 10   | -    | 10   | -   | 10   | ns       |                     |     |     |     |     |     |       |       |

### http://www.BDTIC.com/SAMSUNG Preliminary **U**tRAM

### K1B5616BAM

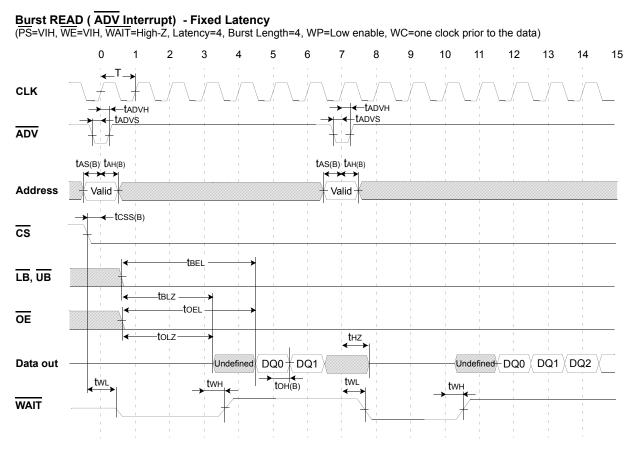

1. Refresh is blocked during ADV Interrupt Read and continuous Burst Read by ADV interrupt should not be longer than tBC (1.2us)

2. /WAIT Low(tWL) : Data not available(driven by CS low going edge or ADV low going edge)

$\begin{array}{l} \mbox{WAIT High(WH): Data available(driven by Cency-1 clock) \\ \mbox{WAIT High-Z(tWZ): Data available(driven by <u>CE</u>S high going edge) \\ \end{array}$

3. Multiple clock risings are allowed during low ADV period but the First valid data come out after set Latency from the last clock rising.

4. Burst interrupt is allowable after the first data received by controller.

| Symphol       | 661 | ИНz  | 80N  | ЛНz  | 104 | MHz  | Units | Symbol  | 66N | ЛНz | 80MHz |     | 104 | MHz | Units |  |

|---------------|-----|------|------|------|-----|------|-------|---------|-----|-----|-------|-----|-----|-----|-------|--|

| Symbol        | Min | Max  | Min  | Max  | Min | Мах  | Units | Symbol  | Min | Max | Min   | Max | Min | Max | Units |  |

| т             | 15  | 200  | 12.5 | 200  | 9.6 | 200  | ns    | ns tBLZ |     | -   | 5     | -   | 5   | -   | ns    |  |

| tвс           | -   | 1200 | -    | 1200 | -   | 1200 | ns    | tolz    | 5   | -   | 5     | -   | 5   | -   | ns    |  |

| tadvs         | 3   | -    | 3    | -    | 3   | -    | ns    | tнz     | -   | 10  | -     | 10  | -   | 10  | ns    |  |

| <b>t</b> advh | 2   | -    | 2    | -    | 2   | -    | ns    | tснz    | -   | 10  | -     | 10  | -   | 10  | ns    |  |

| tas(b)        | 3   | -    | 3    | -    | 3   | -    | ns    | tонz    | -   | 10  | -     | 10  | -   | 10  | ns    |  |

| tAH(B)        | 2   | -    | 2    | -    | 2   | -    | ns    | tвнz    | -   | 10  | -     | 10  | -   | 10  | ns    |  |

| tcss(B)       | 3   | -    | 3    | -    | 3   | -    | ns    | tcp     | -   | 11  | -     | 9   | -   | 7   | ns    |  |

| <b>t</b> CSHP | 5   | -    | 5    | -    | 5   | -    | ns    | tон(в)  | 2   | -   | 2     | -   | 2   | -   | ns    |  |

| <b>t</b> BEL  | 20  | -    | 20   | -    | 20  | -    | ns    | tw∟     | -   | 12  | -     | 12  | -   | 12  | ns    |  |

| toel          | 20  | -    | 20   | -    | 20  | -    | ns    | twн     | -   | 11  | -     | 9   | -   | 7   | ns    |  |

| twz           | -   | 10   | -    | 10   | -   | 10   | ns    |         |     |     |       |     |     |     |       |  |

### http://www.BDTIC.com/SAMSUNG Preliminary Utram

### K1B5616BAM

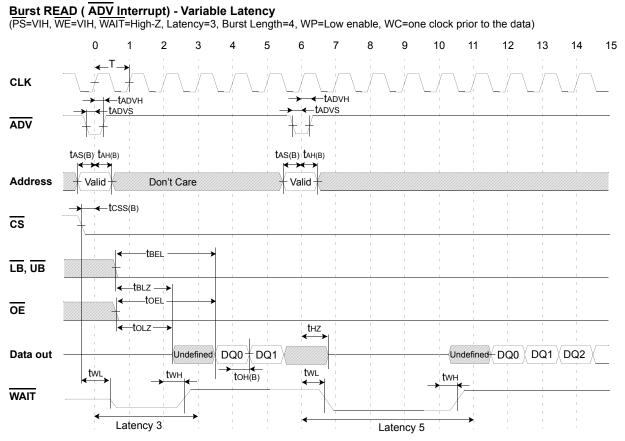

1. Delayed Latency should be taken increased when refresh is required. Refer to Latency Table.

Delayed Latency should be taken increased when the should not be longer than tBC (1.2us)

Refresh is blocked during ADV Interrupt Read and continuous Burst Read by ADV interrupt should not be longer than tBC (1.2us)

WAIT Low(tWL) : Data not available(driven by CS low going edge or ADV low going edge) /WAIT High(tWH) : Data available(driven by Latency-1 clock)

- WAIT HighI(Wr). Data available(unver by Latency 100k)

WAIT High-Z(tWZ) : Data don't care(driven by <u>CS</u> high going edge)

Multiple clock risings are allowed during low ADV period but the First valid data come out after set Latency from the last clock rising.

Burst interrupt is allowable after the first data received by controller.

| Cumula al     | 661 | ИHz  | 80N  | ЛНz  | 104MHz |      | 11    | Quanta  | 661 | ΛHz | 80MHz |     | 104 | Units |       |  |

|---------------|-----|------|------|------|--------|------|-------|---------|-----|-----|-------|-----|-----|-------|-------|--|

| Symbol        | Min | Max  | Min  | Max  | Min    | Max  | Units | Symbol  | Min | Max | Min   | Max | Min | Мах   | Units |  |

| Т             | 15  | 200  | 12.5 | 200  | 9.6    | 200  | ns    | is tBLZ |     | -   | 5     | -   | 5   | -     | ns    |  |

| tвс           | -   | 1200 | -    | 1200 | -      | 1200 | ns    | tolz    | 5   | -   | 5     | -   | 5   | -     | ns    |  |

| tadvs         | 3   | -    | 3    | -    | 3      | -    | ns    | tHZ     | -   | 10  | -     | 10  | -   | 10    | ns    |  |

| <b>t</b> advh | 2   | -    | 2    | -    | 2      | -    | ns    | tснz    | -   | 10  | -     | 10  | -   | 10    | ns    |  |

| tas(b)        | 3   | -    | 3    | -    | 3      | -    | ns    | tонz    | -   | 10  | -     | 10  | -   | 10    | ns    |  |

| tAH(B)        | 2   | -    | 2    | -    | 2      | -    | ns    | tвнz    | -   | 10  | -     | 10  | -   | 10    | ns    |  |

| tcss(B)       | 3   | -    | 3    | -    | 3      | -    | ns    | tCD     | -   | 11  | -     | 9   | -   | 7     | ns    |  |

| <b>t</b> CSHP | 5   | -    | 5    | -    | 5      | -    | ns    | toh(b)  | 2   | -   | 2     | -   | 2   | -     | ns    |  |

| <b>t</b> BEL  | 20  | -    | 20   | -    | 20     | -    | ns    | tw∟     | -   | 12  | -     | 12  | -   | 12    | ns    |  |

| toel          | 20  | -    | 20   | -    | 20     | -    | ns    | twн     | -   | 11  | -     | 9   | -   | 7     | ns    |  |

| twz           | -   | 10   | -    | 10   | I      | 10   | ns    |         |     |     |       |     |     |       |       |  |

### http://www.BDTIC.com/SAMSUNG Preliminary UtRAM

### K1B5616BAM

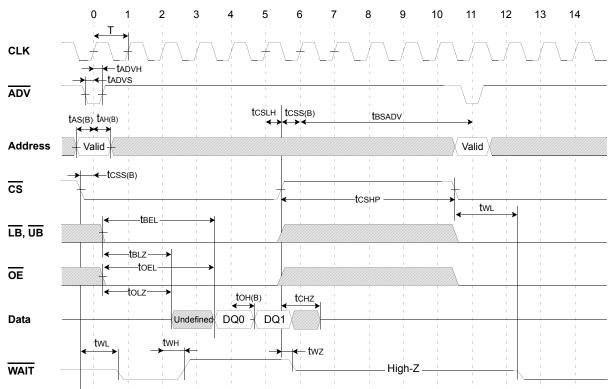

#### **Burst READ STOP**

(PS=VIH, Variable Latency=3, Burst Length=4, WP=Low Enable, WC=one clock prior to the data)

/WAIT Low(tWL): Data not available(driven by CS low going edge or ADV low going edge) /WAIT High(tWH): Data available(driven by Latency-1 clock)

WAIT High/(twn). Data available(unverbig) Later(cy-1 clock)

WAIT High-Z(tWZ): Data don't care(driven by <u>CS</u> high going edge)

Multiple clock risings are allowed during low ADV period. The data starts after set Latency from the last clock rising.

Refresh can not <u>b</u>e implemented when tBSADV is in the range of 0ns ~ 13ns. It may cause Refresh fail to use the device under that condition over 1.2us without <del>CS</del> toggling. To avoid Refresh fail, 13ns for all frequency is needed for tBSADV.

| Sympol       | 66N | 66MHz |     | 80MHz |     | 104MHz |       | Symbol | 66MHz |     | 80MHz |     | 104 | Units |       |  |

|--------------|-----|-------|-----|-------|-----|--------|-------|--------|-------|-----|-------|-----|-----|-------|-------|--|

| Symbol       | Min | Max   | Min | Max   | Min | Max    | Units | Symbol | Min   | Max | Min   | Max | Min | Max   | Units |  |

| tBSADV       | 0   | -     | 0   | -     | 0   | -      | ns    | tcp    | -     | 11  | -     | 9   | -   | 7     | ns    |  |

| tCSLH        | 2   | -     | 2   | -     | 2   | -      | ns    | toh(b) | 2     | -   | 2     | -   | 2   | -     | ns    |  |

| tCSHP        | 5   | -     | 5   | -     | 5   | -      | ns    | tснz   | -     | 10  | -     | 10  | -   | 10    | ns    |  |

| <b>t</b> BEL | 20  | -     | 20  | -     | 20  | -      | ns    | tw∟    | -     | 12  | -     | 12  | -   | 12    | ns    |  |

| <b>t</b> OEL | 20  | -     | 20  | -     | 20  | -      | ns    | twн    | -     | 11  | -     | 9   | -   | 7     | ns    |  |

| <b>t</b> BLZ | 5   | -     | 5   | -     | 5   | -      | ns    | twz    | -     | 10  | -     | 10  | -   | 10    | ns    |  |

| tolz         | 5   | -     | 5   | -     | 5   | -      | ns    |        |       |     |       |     |     |       |       |  |

### http://www.BDTIC.com/SAMSUNG Preliminary UtRAM

#### Asynch. WRITE ( ADV Latch)

#### Burst READ followed by Asynch. WRITE

(PS=VIH, WAIT=High-Z, Variable Latency=3)

1. A write occurs during the overlap(twP) of low CS and low WE. A write begins when CS goes low and WE goes low with asserting UB or LB for single byte operation or simultaneously asserting UB and LB for word operation. A write ends at the earliest transition when CS goes high or WE goes high. The twp is measured from the beginning of write to the end of write.

taw is measured from the address valid to the end of write. In this address latch type write timing, twc is same as taw.

tcw is measured from the <u>CS</u> going low to the end of write.

4. tew is measured from the UB and LB going low to the end of write.

| Asynch. WRITE followed by Burst READ<br>(PS=VIH, Variable Latency=3,Burst Length=4, WP=Low Enable, WC=one clock prior to the data) |                     |                  |                     |                     |                  |                  |                     |                     |                       |                       |                       |                       |                            |                                 |                          |                     |                     |                       |                     |                |                       |

|------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------|---------------------|---------------------|------------------|------------------|---------------------|---------------------|-----------------------|-----------------------|-----------------------|-----------------------|----------------------------|---------------------------------|--------------------------|---------------------|---------------------|-----------------------|---------------------|----------------|-----------------------|

|                                                                                                                                    |                     | 0                | 1                   | 2                   | 3                | 4                | 5                   | 6                   | 7                     | 8                     | 9                     | 10                    | 11 1<br>T                  | 2 13                            | 3 14                     | 15                  | 16                  | 17                    | 18                  | 19             | 20                    |

| CLK                                                                                                                                |                     | <u>j</u>         |                     |                     |                  |                  |                     |                     |                       |                       |                       | <u>/</u><br>≻ к       |                            | Ņ                               | Ì                        | \∱                  |                     | $\int_{-\frac{1}{2}}$ |                     | <u>_</u>       |                       |

| ADV                                                                                                                                |                     | <u>-</u><br>     | - tadv              |                     | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1 | 1<br>1<br>1<br>1    | 1<br>1<br>1<br>1    | <br> <br> <br>        |                       | DVS→                  |                       | <br> <br> <br> <br>        |                                 |                          | <br> <br> <br>      |                     | <br> <br> <br> <br>   | <br> <br> <br> <br> | <br> <br> <br> |                       |

|                                                                                                                                    |                     | ∖) t/<br>➤ >     | чн(А)<br>1          | I<br>I<br>I         | I<br>I<br>I      | <br> <br>        | <br> <br>           | I<br>I<br>I         | <br> <br>             | <br> <br>             |                       | 3) tah(e<br>★ →       | 3)                         |                                 | <br> <br>                | <br> <br>           | <br> <br>           | ,<br> <br>            | <br> <br>           | <br> <br>      | <br> <br>             |

| Addres                                                                                                                             | sV                  | alid -           | ŧ.                  |                     |                  | AW —             |                     |                     |                       |                       | <u> </u>              | /alid                 | -                          |                                 |                          |                     |                     | <u> </u>              |                     |                |                       |

| cs                                                                                                                                 |                     |                  | -tcss               | (A)                 | 1                | CW —             |                     |                     | 1<br>1<br>1<br>1<br>1 |                       |                       |                       | CSS(B)                     |                                 | tBC                      |                     | <br> <br> <br>      | -<br>-<br>-<br>-      |                     |                |                       |

| WE                                                                                                                                 |                     | AS               |                     |                     | I<br>I<br>I<br>I | twr              |                     | <br> <br> <br> <br> | <br> <br> <br> <br>   | →                     |                       | tw∟                   | 1<br>1<br>1<br>1<br>1<br>1 | I I<br>I I<br>I I<br>I I<br>I I | <br> <br> <br> <br>      | <br> <br> <br> <br> | <br> <br> <br> <br> |                       | tv                  | ×∠≯            |                       |

| OE                                                                                                                                 | <br> <br> <br> <br> |                  | <br> <br> <br>      | <br> <br> <br>      |                  | 1<br>1<br>1<br>1 | <br> <br> <br> <br> |                     | <br> <br> <br>        |                       |                       | 1                     | +                          | TOEL                            |                          | <br> <br> <br>      | <br> <br> <br>      | -<br>                 | <br> <br> <br>      |                |                       |

| LB, UB                                                                                                                             |                     |                  | <br> <br> <br>      | <br> <br> <br>      | te               | 3W               | 1<br>1<br>1<br>1    | <br> <br> <br> <br> | <br> <br> <br>        | <b>→</b>              | 1<br>1<br>1           | <br>                  | -                          | tBEL                            | → <sup>1</sup><br>1<br>1 | <br> <br> <br>      | <br> <br> <br>      | <br> <br> <br>        | <br> <br> <br> <br> |                |                       |