## **Document Title**

1Mx16 bit Uni-Transistor Random Access Memory

## **Revision History**

### Revision No. History

0.0

Initial Draft - Design target Draft Date

May 30, 2002

Remark Advance

The attached datasheets are provided by SAMSUNG Electronics. SAMSUNG Electronics CO., LTD. reserve the right to change the specifications and products. SAMSUNG Electronics will answer to your questions about device. If you have any questions, please contact the SAMSUNG branch offices.

## 1M x 16 bit Uni-Transistor CMOS RAM

### **FEATURES**

- Process Technology: CMOS

- Organization: 1M x16 bit

- Power Supply Voltage: 1.7V~2.2V

- Three State Outputs

- Compatible with Low Power SRAM

- Deep Power Down: Memory cell data holds invalid

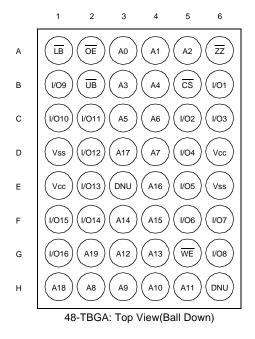

- Package Type: 48-TBGA

## PRODUCT FAMILY

### **GENERAL DESCRIPTION**

The K1S1616B5M is fabricated by SAMSUNG's advanced CMOS technology using one transistor memory cell. The device supports extended temperature range and 48 ball Chip Scale Package for user flexibility of system design. The device also supports deep power down mode for low standby current.

|                |                                |           |                 | Power Di | ssipation                 |          |

|----------------|--------------------------------|-----------|-----------------|----------|---------------------------|----------|

| Product Family | Product Family Operating Temp. |           | Vcc Range Speed |          | Operating<br>(Icc2, Max.) | РКС Туре |

| K1S1616B5M-E   | Extended(-25~85°C)             | 1.7V~2.2V | 70/85ns         | 60μΑ     | 25mA                      | 48-TBGA  |

### **PIN DESCRIPTION**

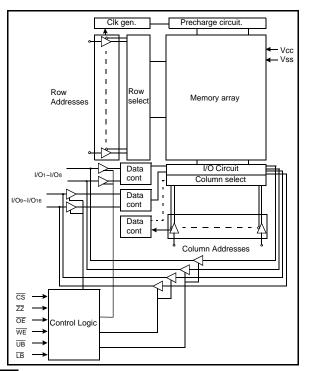

| FUNCTIONAL | BLOCK | DIAGRAM |

|------------|-------|---------|

|            |       |         |

| Name       | Function            | Name | Function                 |

|------------|---------------------|------|--------------------------|

| CS         | Chip Select Input   | Vcc  | Power                    |

| ZZ         | Deep Power Down     | Vss  | Ground                   |

| OE         | Output Enable Input | UB   | Upper Byte(I/O9~16)      |

| WE         | Write Enable Input  | LB   | Lower Byte(I/O1~8)       |

| A0~A19     | Address Inputs      | DNU  | Do Not Use <sup>1)</sup> |

| I/O1~I/O16 | Data Inputs/Outputs |      |                          |

1) Reserved for future use.

SAMSUNG ELECTRONICS CO., LTD. reserves the right to change products and specifications without notice.

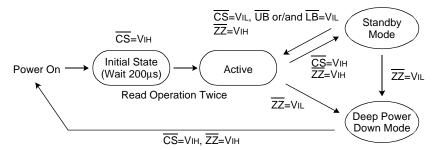

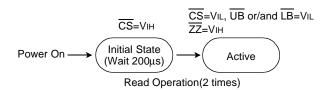

## POWER UP SEQUENCE

1. Apply power.

2. Maintain stable power(Vcc min.=1.7V) for a minimum 200 $\mu$ s with  $\overline{CS}$ =high.

3. Issue read operation at least twice.

## FUNCTIONAL DESCRIPTION

| CS              | ZZ | OE              | WE              | LB              | UB              | <b>I/O</b> 1~8 | <b>I/O</b> 9~16 | Mode             | Power           |

|-----------------|----|-----------------|-----------------|-----------------|-----------------|----------------|-----------------|------------------|-----------------|

| н               | н  | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          | Deselected       | Standby         |

| X <sup>1)</sup> | L  | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | X <sup>1)</sup> | High-Z         | High-Z          | Deselected       | Deep Power Down |

| L               | н  | X <sup>1)</sup> | X <sup>1)</sup> | Н               | Н               | High-Z         | High-Z          | Deselected       | Standby         |

| L               | Н  | Н               | Н               | L               | X <sup>1)</sup> | High-Z         | High-Z          | Output Disabled  | Active          |

| L               | н  | н               | н               | X <sup>1)</sup> | L               | High-Z         | High-Z          | Output Disabled  | Active          |

| L               | Н  | L               | Н               | L               | Н               | Dout           | High-Z          | Lower Byte Read  | Active          |

| L               | н  | L               | Н               | Н               | L               | High-Z         | Dout            | Upper Byte Read  | Active          |

| L               | н  | L               | Н               | L               | L               | Dout           | Dout            | Word Read        | Active          |

| L               | н  | X <sup>1)</sup> | L               | L               | Н               | Din            | High-Z          | Lower Byte Write | Active          |

| L               | Н  | X <sup>1)</sup> | L               | Н               | L               | High-Z         | Din             | Upper Byte Write | Active          |

| L               | Н  | X <sup>1)</sup> | L               | L               | L               | Din            | Din             | Word Write       | Active          |

1. X means don't care.(Must be low or high state)

### ABSOLUTE MAXIMUM RATINGS<sup>1)</sup>

| ltem                                  | Symbol    | Ratings          | Unit |

|---------------------------------------|-----------|------------------|------|

| Voltage on any pin relative to Vss    | Vin, Vout | -0.2 to Vcc+0.3V | V    |

| Voltage on Vcc supply relative to Vss | Vcc       | -0.2 to 2.5V     | V    |

| Power Dissipation                     | PD        | 1.0              | W    |

| Storage temperature                   | Тѕтс      | -65 to 150       | °C   |

| Operating Temperature                 | TA        | -25 to 85        | °C   |

1. Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Functional operation should be restricted to be used under recommended operating condition. Exposure to absolute maximum rating conditions longer than 1 second may affect reliability.

## STANDBY MODE STATE MACHINES

## STANDBY MODE CHARACTERISTIC

| Power Mode      | Memory Cell Data | Standby Current(µA) | Wait Time(μs) |

|-----------------|------------------|---------------------|---------------|

| Standby         | Valid            | 60                  | 0             |

| Deep Power Down | Invaild          | 10                  | 200           |

### **PRODUCT LIST**

| Extended Temperature Products(-25~85°C) |                                |  |  |

|-----------------------------------------|--------------------------------|--|--|

| Part Name                               | Function                       |  |  |

| K1S1616B5M-EE70<br>K1S1616B5M-EE85      | 48-TBGA, 70ns<br>48-TBGA, 85ns |  |  |

### **RECOMMENDED DC OPERATING CONDITIONS<sup>1)</sup>**

| Item               | Symbol | Min                | Тур  | Max       | Unit |

|--------------------|--------|--------------------|------|-----------|------|

| Supply voltage     | Vcc    | 1.7V               | 1.8V | 2.2V      | V    |

| Ground             | Vss    | 0                  | 0    | 0         | V    |

| Input high voltage | Viн    | 1.4                | -    | Vcc+0.22) | V    |

| Input low voltage  | VIL    | -0.2 <sup>3)</sup> | -    | 0.4       | V    |

1. TA=-25 to 85°C, otherwise specified.

2. Overshoot: Vcc+1.0V in case of pulse width  $\leq$ 20ns.

Undershoot: -1.0V in case of pulse width ≤20ns.

Overshoot and undershoot are sampled, not 100% tested.

### CAPACITANCE<sup>1</sup>(f=1MHz, TA=25°C)

| Item                     | Symbol | Test Condition | Min | Max | Unit |

|--------------------------|--------|----------------|-----|-----|------|

| Input capacitance        | CIN    | VIN=0V         | -   | 8   | pF   |

| Input/Output capacitance | Сю     | VIO=0V         | -   | 10  | pF   |

1. Capacitance is sampled, not 100% tested.

## DC AND OPERATING CHARACTERISTICS

| ltem                      | Symbol | Test Conditions                                                                      | Min | Тур | Max              | Unit |

|---------------------------|--------|--------------------------------------------------------------------------------------|-----|-----|------------------|------|

| Input leakage current     | L      | VIN=Vss to Vcc                                                                       | -1  | -   | 1                | μA   |

| Output leakage current    | Ilo    | $\overline{CS}$ =VIH or $\overline{OE}$ =VIH or $\overline{WE}$ =VIL, VIO=Vss to Vcc | -1  | -   | 1                | μA   |

| Average operating current | ICC1   | Cycle time=1µs, 100% duty, Iıo=0mA,                                                  | -   | -   | 5                | mA   |

|                           | ICC2   | Cycle time=Min, Iю=0mA, 100% duty, CS=VIL, VI№=VIH or VIL                            | -   | -   | 25               | mA   |

| Output low voltage        | Vol    | IOL = 0.1mA                                                                          | -   | -   | 0.2              | V    |

| Output high voltage       | Vон    | юн = -0.1mA                                                                          | 1.4 | -   | -                | V    |

| Standby Current(CMOS)     | ISB1   | CS≥Vcc-0.2V, Other inputs=0~Vcc                                                      | -   | -   | 60 <sup>1)</sup> | μA   |

1. This value is valid over the entire operating temperature range.

## AC OPERATING CONDITIONS

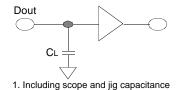

**TEST CONDITIONS**(Test Load and Test Input/Output Reference) Input pulse level: 0.2 to Vcc-0.2V Input rising and falling time: 5ns Input and output reference voltage: 0.5 x Vcc Output load (See right): CL=50pF

### AC CHARACTERISTICS (Vcc=1.7~2.2V, TA=-25 to 85°C)

|       | Parameter List                  | Symbol | 70  | <b>)ns</b> 1) | 85  | ns  | Units |

|-------|---------------------------------|--------|-----|---------------|-----|-----|-------|

|       | Due l Ourle True                |        | Min | Max           | Min | Max |       |

|       | Read Cycle Time                 | tRC    | 70  | -             | 85  | -   | ns    |

|       | Address Access Time             | tAA    | -   | 70            | -   | 85  | ns    |

|       | Chip Select to Output           | tco    | -   | 70            | -   | 85  | ns    |

|       | Output Enable to Valid Output   | tOE    | -   | 35            | -   | 40  | ns    |

|       | UB, LB Access Time              | tBA    | -   | 70            | -   | 85  | ns    |

| Read  | Chip Select to Low-Z Output     | t∟z    | 10  | -             | 10  | -   | ns    |

| Read  | UB, LB Enable to Low-Z Output   | tBLZ   | 10  | -             | 10  | -   | ns    |

|       | Output Enable to Low-Z Output   | tolz   | 5   | -             | 5   | -   | ns    |

|       | Chip Disable to High-Z Output   | tHZ    | 0   | 25            | 0   | 25  | ns    |

|       | UB, LB Disable to High-Z Output | tвнz   | 0   | 25            | 0   | 25  | ns    |

|       | Output Disable to High-Z Output | tонz   | 0   | 25            | 0   | 25  | ns    |

|       | Output Hold from Address Change | tон    | 5   | -             | 5   | -   | ns    |

|       | Write Cycle Time                | twc    | 70  | -             | 85  | -   | ns    |

|       | Chip Select to End of Write     | tcw    | 60  | -             | 70  | -   | ns    |

|       | Address Set-up Time             | tas    | 0   | -             | 0   | -   | ns    |

|       | Address Valid to End of Write   | tAW    | 60  | -             | 70  | -   | ns    |

|       | UB, LB Valid to End of Write    | tвw    | 60  | -             | 70  | -   | ns    |

| Write | Write Pulse Width               | tWP    | 50  | -             | 60  | -   | ns    |

|       | Write Recovery Time             | twr    | 0   | -             | 0   | -   | ns    |

|       | Write to Output High-Z          | twнz   | 0   | 20            | 0   | 25  | ns    |

|       | Data to Write Time Overlap      | tDW    | 30  | -             | 35  | -   | ns    |

|       | Data Hold from Write Time       | tdн    | 0   | -             | 0   | -   | ns    |

|       | End Write to Output Low-Z       | tow    | 5   | -             | 5   | -   | ns    |

1. The limitation in continuous write operation is up to 50 times. If you want to write continuously over 50 times, please refer to the technical note.

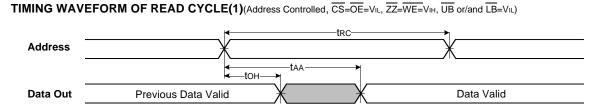

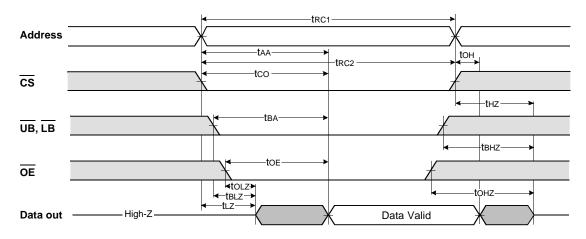

### TIMING DIAGRAMS

#### TIMING WAVEFORM OF READ CYCLE(2)(ZZ=WE=VIH)

#### (READ CYCLE)

- 1. tHZ and tOHZ are defined as the time at which the outputs achieve the open circuit conditions and are not referenced to output voltage levels.

- 2. At any given temperature and voltage condition, tHZ(Max.) is less than tLZ(Min.) both for a given device and from device to device interconnection.

- 3. The minimum read cycle(tRC) is determined by longer one of tRC1 and tRC2.

- 4. toE(max) is met only when  $\overline{OE}$  becomes enabled after tAA(max).

## http://www.BDTIC.com/SAMSUNG Advance UtRAM

## K1S1616B5M

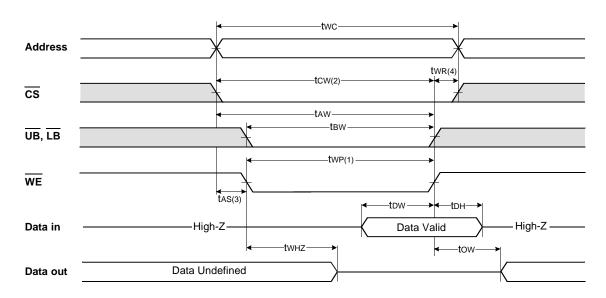

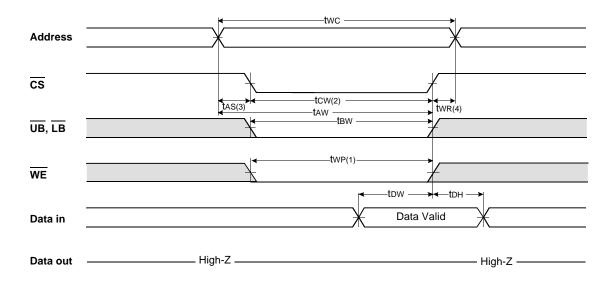

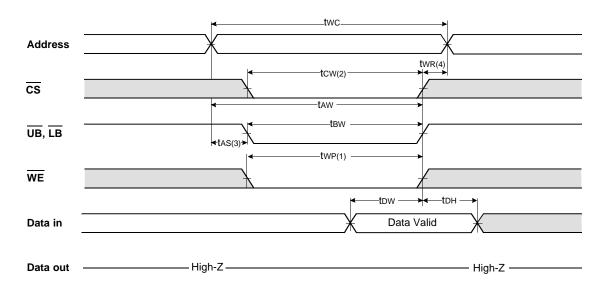

#### TIMING WAVEFORM OF WRITE CYCLE(2)(CS Controlled, ZZ=VIH)

#### TIMING WAVEFORM OF WRITE CYCLE(3)(UB, LB Controlled, ZZ=VIH)

#### (WRITE CYCLE)

1. A <u>write</u> occurs during the overlap(twp) of low CS and low WE. A write begins when CS goes low and WE goes low with asserting UB or LB for single byte operation or simultaneously asserting UB and LB for double byte operation. A write ends at the earliest transition when CS goes high and WE goes high. The twp is measured from the beginning of write to the end of write.

- 2. tcw is measured from the  $\overline{CS}$  going low to the end of write.

- 3. tas is measured from the address valid to the beginning of write.

4. twe is measured from the end of write to the address change. twe is applied in case a write ends with  $\overline{\text{CS}}$  or  $\overline{\text{WE}}$  going high.

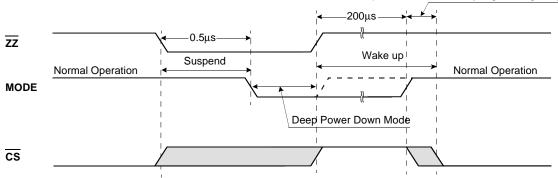

#### TIMING WAVEFORM OF DEEP POWER DOWN MODE

Read Operation Twice or Stay High during  $300\mu s$

(DEEP POWER DOWN MODE)

1. When you toggle  $\overline{ZZ}$  pin low, the device gets into the Deep Power Down mode after 0.5µs suspend period.

2. To return to normal operation, the device needs Wake Up period.

3. Wake Up sequence is just the same as Power Up sequence shown in next page.

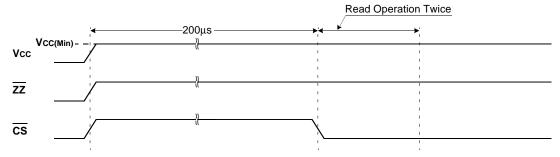

#### TIMING WAVEFORM OF POWER UP(1)

#### (POWER UP(1))

1. After Vcc reaches Vcc(Min.) following power application, wait 200µs with CS high and then toggle CS low and commit Read Operation at least twice. Then you get into the normal operation.

2. Read operation should be executed by toggling  $\overline{\text{CS}}$  pin low.

3. The read operation must satisfy the specified tRC.

4. ZZ pin should be kept high during whole power up sequence.

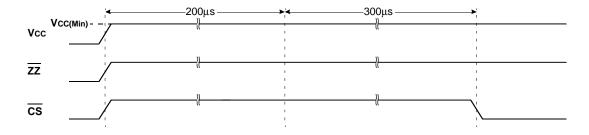

#### TIMING WAVEFORM OF POWER UP(2)(No Dummy Cycle)

#### (POWER UP(2))

1. After Vcc reaches Vcc(Min.) following power application, wait 200µs and wait another 300µs with CS high if you don't want to commit dummy read cycle. After total 500µs wait, toggle CS low, then you get into the normal mode. 2. ZZ pin should be kept high during whole power up sequence.

## http://www.BDTIC.com/SAMSUNG Advance UtRAM

## K1S1616B5M

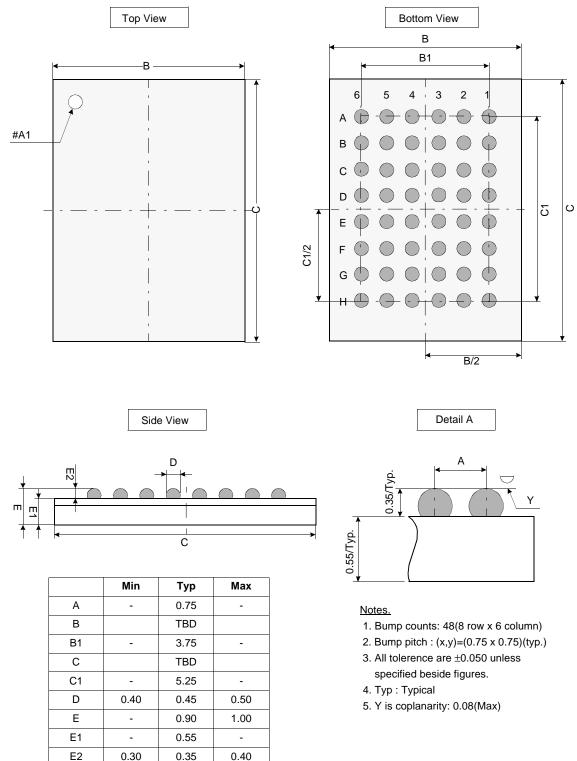

Unit: millimeters

### PACKAGE DIMENSION

48 TAPE BALL GRID ARRAY(0.75mm ball pitch)

Y

-

-

0.08

## TECHNICAL NOTE

## UtRAM USAGE AND TIMING

## INTRODUCTION

UtRAM is based on single-transistor DRAM cells. As with any other DRAM, the data in these cells must be periodically refreshed to prevent data loss. What makes the UtRAM unique is that it offers a true SRAM style interface that hides all refresh operations from the memory controller.

## START WITH A DRAM TECHNOLOGY

The key point of UtRAM is its high speed and low power. This high speed comes from the use of many small blocks such as 32Kbits each to create UtRAM arrays. The small blocks have short word lines thus with little capacitance eliminating a major factor of operating current dissipation in conventional DRAM blocks.

Each independent macro-cell on a UtRAM device consists of a number of these blocks. Each chip has one or more macro.

The address decoding logic is also fast. UtRAM performs a complete read operation in every tRC, but UtRAM needs power up sequence like DRAM.

Power Up Sequence and Diagram

1. Apply power.

Figure 1.

2. Maintain stable power for a minium 200 $\mu$ s with  $\overline{CS}$ =high.

3. Issue read operation at least 2 times.

# DESIGN ACHIEVES SRAM SPECIFIC OPERATIONS

The UtRAM was designed to work just like an SRAM - without any waits or other overhead for precharging or refreshing its internal DRAM cells. SAMSUNG Electronics(SAMSUNG) hides these operations inside with advanced design technology those are not to be seen from outside. Precharging takes place during every access, overlapped between the end of the cycle and the decoding portion of the next cycle.

Hiding refresh is more difficult. Every row in every block must be refreshed at least once during the refresh interval to prevent data loss. SAMSUNG provides an internal refresh controller for devices. When all accesses within refresh interval are directed to one macro-cell, as can happen in signal processing applications, a more sophisticated approach is required to hide refresh. The pseudo SRAM is sometimes used on these applications, which requires a memory controller that can hold off accesses when a refresh operation is needed. SAMSUNG's unique qualitative advantage over these parts(in addition to quantitative improvements in access speed and power consumption) is that the UtRAM never need to hold off accesses, and indeed it has no hold off signal. The circuitry that gives SAMSUNG this advantage is fairly simple but has not previously been disclosed.

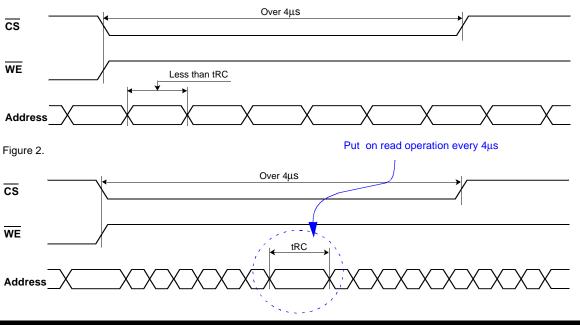

### **AVOID TIMING**

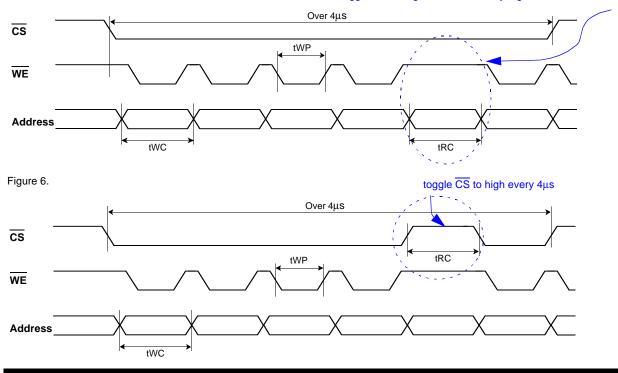

Following figures show you an abnormal timing which is not supported on U*t*RAM and its solution.

If your system has a timing which sustains invalid states over  $4\mu$ s at read mode like Figure 1, there are some guide lines for proper operation of U*t*RAM.

When your system has multiple invalid address signals shorter than tRC on the timing shown in Figure 1, U*t*RAM needs a normal read timing(tRC) during that cycle(Figure 2) or needs to toggle  $\overline{CS}$  once to 'high' for about 'tRC'(Figure 3).

SRAM PLANNING LIM-020311 SAMSUNG Electronics CO., LTD. reserves the right to change products or specifications without notice. ©2002 SAMSUNG Electronics CO., LTD.

| Figure 3. | toggle $\overline{CS}$ to high every 4µs |

|-----------|------------------------------------------|

|           | Over 4µs                                 |

| cs        |                                          |

| WE        |                                          |

| Address   |                                          |

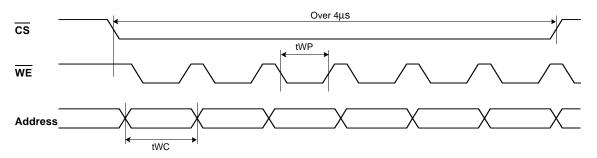

Write operation has similar restriction to Read operation. If your system has a timing which sustains invalid states over 4 $\mu$ s at write mode and has continuous write signals with length of Min. tWC over 4 $\mu$ s like Figure 4, you must toggle WE once to high

and make it stay high at least for tRC every 4µs or toggle  $\overline{\text{CS}}$  once to high for about tRC.

Figure 4.

Figure 5.

toggle  $\overline{WE}$  to high and make it stay high at least for tRC every 4µs

SRAM PLANNING LIM-020311 SAMSUNG Electronics CO., LTD. reserves the right to change products or specifications without notice. ©2002 SAMSUNG Electronics CO., LTD.