# AM335x ARM Cortex-A8 Microprocessors (MPUs) Silicon Revision 1.0

# **Silicon Errata**

Literature Number: SPRZ360 October 2011

# www.BDTIC.com/TI

# Contents

| 1 | Introdu  | iction                                                                      | 5 |

|---|----------|-----------------------------------------------------------------------------|---|

|   | 1.1      | AM335x Device and Development Support Tool Nomenclature                     | 5 |

|   | 1.2      | Revision Identification                                                     | 6 |

| 2 | All Erra | ata Listed With Silicon Revision Number                                     | 7 |

| 3 | Revisio  | on 1.0 Usage Notes and Known Design Exceptions to Functional Specifications | 8 |

|   | 3.1      | Revision 1.0 Usage Notes                                                    | 8 |

|   |          | 3.1.1 LCD: Color Assignments of LCD_DATA Terminals                          | 8 |

|   |          | 3.1.2 DDR3: JEDEC Compliance for Maximum Self-Refresh Command Limit         | 8 |

|   | 3.2      | Revision 1.0 Known Design Exceptions to Functional Specifications           | 9 |

3

Cortex is a trademark of ARM Ltd or its subsidiaries. ARM is a registered trademark of ARM Ltd or its subsidiaries.

Copyright © 2011, Texas Instruments Incorporated

# AM335x ARM Cortex-A8 Microprocessors (MPUs) (Silicon Revision 1.0)

# 1 Introduction

This document describes the known exceptions to the functional specifications for the AM335x ARM Cortex-A8 Microprocessors (MPUs). [See the AM335x ARM Cortex-A8 Microprocessors (MPUs) data manual (literature number <u>SPRS717</u>).]

For additional information, see the latest version of the AM335x ARM Cortex-A8 Microprocessors (MPUs) Technical Reference Manual (literature number <u>SPRUH73</u>).

# 1.1 AM335x Device and Development Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all microprocessors (MPUs) and support tools. Each device has one of three prefixes: X, P, or null (no prefix) (e.g., XAM3358ZCE). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMDX) through fully qualified production devices/tools (TMDS).

Device development evolutionary flow:

- **X** Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow.

- **P** Prototype device that is not necessarily the final silicon die and may not necessarily meet final electrical specifications.

- null Production version of the silicon die that is fully qualified.

Support tool development evolutionary flow:

- **TMDX** Development-support product that has not yet completed Texas Instruments internal qualification testing.

- **TMDS** Fully-qualified development-support product.

X and P devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Production devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

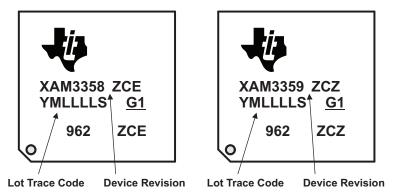

# 1.2 Revision Identification

The device revision can be determined by the symbols marked on the top of the package. Figure 1 provides an example of the AM335x device markings.

Figure 1. Example of Device Revision Codes for the AM335x Microprocessor

# NOTES:

- (A) Non-qualified devices are marked with the letters "X" or "P" at the beginning of the device name, while qualified devices have a "blank" at the beginning of the device name.

- (B) The AM3358 and AM3359 devices shown in this device marking example are two of several valid part numbers for the AM335x family of devices.

- (C) The device revision code is the device revision (A, B, etc.).

- (D) YM denotes year/month.

- (E) LLLL denotes Lot Trace Code.

- (F) 962 is a generic family marking ID.

- (G) G1 denotes green, lead-free.

- (H) ZCE or ZCZ is the package designator.

- (I) S denotes Assembly Site Code.

- (J) On some "X" devices, the device speed may not be shown.

(MF

Silicon revision is identified by a code marked on the package. The code is of the format AM3358x, where "x" denotes the silicon revision. Table 1 lists the information associated with each silicon revision for each device type. For more details on device nomenclature, see the device-specific data manual.

| DEVICE REVISION CODE (x) | SILICON REVISION | COMMENTS                |

|--------------------------|------------------|-------------------------|

| (blank)                  | 1.0              | Silicon revision is new |

Each silicon revision uses a specific revision of TI's ARM<sup>®</sup> Cortex<sup>™</sup>-A8 processor. The ARM Cortex-A8 processor variant and revision can be read from the Main ID Register. The ROM code revision can be read from address 2BFFCh. The ROM code version consists of two decimal numbers: major and minor. The major number is always 22, minor number counts ROM code version. The ROM code version is coded as hexadecimal readable values; e.g., ROM version 22.02 will be coded as 0000 2202h. Table 2 shows the ROM code revision for each silicon revision of the device.

# Table 2. Silicon Revision Variables

| SILICON  | ARM CORTEX-A8    | ROM      |

|----------|------------------|----------|

| REVISION | VARIANT/REVISION | REVISION |

| 1.0      | r3p2             |          |

evis

Sili

www.ti.com

# 2 All Errata Listed With Silicon Revision Number

|                |                                                                            | <b>Revision Affected</b> |

|----------------|----------------------------------------------------------------------------|--------------------------|

| Type/Number    | Title                                                                      | 1.0                      |

| Advisory 1.0.1 | DDR2/3/mDDR PHY: Control/Status Registers Configured for Write Only        | Х                        |

| Advisory 1.0.2 | Debug Subsystem: EMU[4:2] Signals Are Not Available by Default After Reset | Х                        |

| Advisory 1.0.3 | Debug Subsystem: Internal Inputs Tied-off to the Wrong Value               | Х                        |

| Advisory 1.0.4 | PRU Subsystem: Clock Domain Crossing (CDC) Issue                           | Х                        |

| Advisory 1.0.5 | RTC: 32.768-kHZ Clock is Gating Off                                        | Х                        |

| Advisory 1.0.6 | EXTINTn: Input Function of the EXTINTn Terminal is Inverted                | Х                        |

| Advisory 1.0.7 | Boot: Ethernet Boot ROM Code PHY Link Speed Detection                      | Х                        |

# Table 3. All Design Exceptions to Functional Specifications

# 3 Revision 1.0 Usage Notes and Known Design Exceptions to Functional Specifications

# 3.1 Revision 1.0 Usage Notes

This document contains Usage Notes. Usage Notes highlight and describe particular situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness. These notes may be incorporated into future documentation updates for the device (such as the device-specific data manual), and the behaviors they describe may or may not be altered in future device revisions.

# 3.1.1 LCD: Color Assignments of LCD\_DATA Terminals

The blue and red color assignments to the LCD data pins are reversed when operating in RGB888 (24bpp) mode compared to RGB565 (16bpp) mode. In order to correctly display RGB888 data from the SGX, or any source formatted as RGB in memory, it is necessary to connect the LCD panel as shown in Figure 2. Using the LCD Controller with this connection scheme limits the use of RGB565 mode. Any data generated for the RGB565 mode requires the red and blue color data values be swapped in order to display the correct color.

| 23   | 22   | 21   | 20   | 19   | 18   | 17   | 16   | 15            | 14 | 13 | 12 | 11 | 10 | 9      | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------|------|------|------|------|------|------|------|---------------|----|----|----|----|----|--------|---|---|---|---|---|---|---|---|---|

|      |      |      |      |      |      |      |      | PIXEL_n       |    |    |    |    |    |        |   |   |   |   |   |   |   |   |   |

| B[0] | G[0] | R[0] | B[1] | G[1] | R[1] | B[2] | R[2] | B[7:3] G[7:2] |    |    |    |    |    | R[7:3] |   |   |   |   |   |   |   |   |   |

|      |      |      |      |      |      |      |      |               |    |    |    |    |    |        |   |   |   |   |   |   |   |   |   |

| 1    |      |      |      |      |      |      |      | 16-bit panel  |    |    |    |    |    |        |   |   |   |   |   |   |   |   |   |

24-bit panel

# Figure 2. RGB888 Mode LCD Controller Output Pin Mapping (LCD\_DATA[23:0])

When operating the LCD Controller in RGB565 mode the LCD panel should be connected as shown in Figure 3. Using the LCD Controller with this connection scheme limits the use of RGB888 mode. Any data generated for the RGB888 mode requires the red and blue color data values be swapped in order to display the correct color.

| 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15      | 14                 | 13 | 12 | 11 | 10 | 9 | 8 | 7      | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|---------|--------------------|----|----|----|----|---|---|--------|---|---|---|---|---|---|---|

|    |    |    |    |    |    |    |    | PIXEL_n |                    |    |    |    |    |   |   |        |   |   |   |   |   |   |   |

| 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |         | R[7:3] G[7:2] B[7: |    |    |    |    |   |   | B[7:3] |   |   |   |   |   |   |   |

|    |    |    |    |    |    |    |    |         |                    |    |    |    |    |   |   |        |   |   |   |   |   |   |   |

| I  |    |    |    |    |    |    |    |         | 16-bit panel       |    |    |    |    |   |   |        |   |   |   |   |   |   |   |

24-bit panel

# Figure 3. RGB565 Mode LCD Controller Output Pin Mapping (LCD\_DATA[23:0])

# 3.1.2 DDR3: JEDEC Compliance for Maximum Self-Refresh Command Limit

-Us

C Soors

When using DDR3 EMIF Self-Refresh, it is possible to violate the maximum refresh command requirement specified in the JEDEC standard DDR3 SDRAM Specification (JESD79-3E, July 2010). This requirement states that the DDR3 EMIF controller should issue no more than 16 refresh commands within any 15.6-µs interval.

To avoid this requirement violation, when using the DDR3 EMIF and Self-Refresh (setting LP\_MODE = 0x2 field in the PMCR), the SR\_TIM value in the PMCR must to be programmed to a value greater than or equal to 0x9.

vi: on 1.0)

n R

Copyright © 2011, Texas Instruments Incorporated

Silic

AM335x ARM Corter-1871

www.ti.com

# 3.2 Revision 1.0 Known Design Exceptions to Functional Specifications

Table 4 lists known design exceptions to functional specifications for device revision 1.0. Advisories are numbered in the order in which they were added to this document. Some advisory numbers may be moved to the next revision and others may have been removed because the design exception was fixed or documented in the device-specific data manual or peripheral user's guide. When items are moved or deleted, the remaining numbers remain the same and are not re-sequenced.

### Table 4. Revision 1.0 Advisory List

# TitlePageAdvisory 1.0.1 — DDR2/3/mDDR PHY: Control/Status Registers Configured for Write Only10Advisory 1.0.2 — Debug Subsystem: EMU[4:2] Signals Are Not Available by Default After Reset10Advisory 1.0.3 — Debug Subsystem: Internal Inputs Tied-off to the Wrong Value10Advisory 1.0.4 — PRU Subsystem: Clock Domain Crossing (CDC) Issue11Advisory 1.0.5 — RTC: 32.768-kHZ Clock is Gating Off.11Advisory 1.0.6 — EXTINTn: Input Function of the EXTINTn Terminal is Inverted11Advisory 1.0.7 — Boot: Ethernet Boot ROM Code PHY Link Speed Detection12

SPRZ360–October 2011 nit Documentation Feedback

Sut

| Advisory 1.0.1       | DDR2/3/mDDR PHY: Control/Status Registers Configured for Write Only                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Revision(s) Affected | 1.0                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Details              | The DDR2/3/mDDR PHY control/status registers mapped in address range 0x44e12000-0x44E123FF are configured for write-only operations, so the contents of these register cannot be read.                                                                                                                                                                                                            |  |  |  |  |  |  |

|                      | These registers must be configured by performing write-only operations.                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Workaround(s)        | There is no workaround for this issue.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Advisory 1.0.2       | Debug Subsystem: EMU[4:2] Signals Are Not Available by Default After Reset                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Revision(s) Affected | 1.0                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Details              | All Debug subsystem components should remain unchanged when warm reset is asserted. For example, warm reset should not affect export of debug trace messages on the EMU[4:0] signals.                                                                                                                                                                                                             |  |  |  |  |  |  |

|                      | The AM335x EMU[4:2] signals can not be used to export trace messages from the Debug subsystem since AM335x does support warm reset and the EMU[4:2] signals are not assigned to pins after reset is asserted.                                                                                                                                                                                     |  |  |  |  |  |  |

| Workaround(s)        | Do not assert warm reset while performing trace functions.                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| Advisory 1.0.3       | Debug Subsystem: Internal Inputs Tied-off to the Wrong Value                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Revision(s) Affected | 1.0                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Details              | Internal inputs dbg_dpio_attr_dp_app_owner[4:0] and dbg_dpio_attr_dp_debug_only[4:0] to the Debug subsystem are used to report which EMU[4:0] signals can currently be used to export trace messages. These inputs were tied-off to the wrong value. The tie-off values used will always indicate EMU[4:2] signals are not available and EMU[1:0] signals are available to export trace messages. |  |  |  |  |  |  |

|                      | This should not cause a problem for EMU[4:2] since these signals can not be used to export trace messages for the reason explained in advisory 1.3. However, the AM335x pins used for EMU[1:0] signals may be configured as GPIO. The Debug subsystem would not know these signals are not available for exporting trace messages when these pins are configured as GPIO.                         |  |  |  |  |  |  |

| Workaround(s)        | Do not configure the AM335x EMU[1:0] pins to operate as GPIO if you need to export trace messages.                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

Silic n R vi: on 1.0)

Copyright © 2011, Texas Instruments Incorporated

<u>//</u>\_Us

cr spors

AM335x ARM Corter-Astric op

| www.ti.com           | Revision 1.0 Usage Notes and Known Design Exceptions to Functional Specifications                                                                                                                                                                                                                                                         |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Advisory 1.0.4       | PRU Subsystem: Clock Domain Crossing (CDC) Issue                                                                                                                                                                                                                                                                                          |

| Revision(s) Affected | 1.0                                                                                                                                                                                                                                                                                                                                       |

| Details              | The PRU subsystem has a clock domain crossing issue when the MII receive multiplexer is configured to connect PR1_MII signals to PRU0 and PR1_MII0 signals to PRU1.                                                                                                                                                                       |

|                      | The multiplexer logic always uses the PR1_MII_MR0_CLK input to synchronize the PRU0 MII receive signals and the PR1_MII_MR1_CLK input to synchronize the PRU1 MII receive signals. This cause the wrong clock to be used when the MII receive multiplexer is configured to connect PR1_MII1 signals to PRU0 and PR1_MII0 signals to PRU1. |

| Workaround(s)        | There is no workaround for this issue.                                                                                                                                                                                                                                                                                                    |

| Advisory 1.0.5       | RTC: 32.768-kHZ Clock is Gating Off                                                                                                                                                                                                                                                                                                       |

| Revision(s) Affected | 1.0                                                                                                                                                                                                                                                                                                                                       |

| Details              | The RTC has a clock gating issue that stops the internal 32.768-kHz clock when the VDD_CORE voltage domain drops below the recommended operating range or the PWRONRSTn input terminal is held low. This issue has the following side effects:                                                                                            |

|                      | <ul> <li>The RTC counters stop incrementing when the 32.768-kHz clock is gated. This causes the RTC to lose time while the clock is gated.</li> </ul>                                                                                                                                                                                     |

|                      | • A wakeup event applied to the EXT_WAKEUP input terminal is masked if the EXT_WAKEUP_DB_EN bit in the RTC PMIC register (0x98) is set to 1 which enables the de-bounce function for the EXT_WAKEUP input. This occurs because the 32.768-kHz clock is being used to clock the de-bounce circuit.                                         |

| Workaround(s)        | Do not turn off the VDD_CORE power source or source a logic low to the PWRONRSTn input while expecting RTC to keep an accurate time.                                                                                                                                                                                                      |

|                      | Do not enable the de-bounce circuit on the EXT_WAKEUP input if an external wakeup event needs to be detected while the 32.768-kHz clock is gated.                                                                                                                                                                                         |

| Advisory 1.0.6       | EXTINTn: Input Function of the EXTINTn Terminal is Inverted                                                                                                                                                                                                                                                                               |

| Revision(s) Affected | 1.0                                                                                                                                                                                                                                                                                                                                       |

| Details              | The EXTINTn input is active high.                                                                                                                                                                                                                                                                                                         |

| Workaround(s)        | Use an active high interrupt source or use an external inverter to change the polarity of any active low interrupt source.                                                                                                                                                                                                                |

| Advisory 1.0.7       | Boot: Ethernet Boot ROM Code PHY Link Speed Detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s) Affected | 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Details              | The device ROM code relies on the external PHY's Control Register (Register 0), specifically bits 0.6 [Speed Selection (MSB)] and 0.13 [Speed Selection (LSB)], to determine the operating speed of the link.                                                                                                                                                                                                                                                                                                                           |

|                      | If the external PHY does not update its link speed selection bits to reflect the current operating speed, the ROM code will incorrectly assume the PHY is operating at the speed indicated by the link speed selection bits and configure the device Ethernet MAC to the wrong speed. For example, if the default value of the PHY link speed selection bits indicates 1 Gbps, when the PHY is actually operating at 100 Mbps, the ROM will incorrectly configure the device Ethernet MAC for 100 Mbps mode.                            |

|                      | The IEEE 802.3 specification states: When Auto-Negotiation Enable (bit 0.12) is<br>enabled, bits 0.6 and 0.13 can be read or written to, but the state of bits 0.6 and 0.13<br>have no effect on the link configuration, and it is not necessary for bits 0.6 and 0.13 to<br>reflect the operating speed of the link when it is read. While some PHYs update the link<br>speed in these bits to reflect the current operating speed, other PHYs do not update<br>these bits because it is not mandatory according to the specification. |

| Workaround(s)        | When using Ethernet boot, an external PHY that updates the Register 0 link speed selection bits (0.6 and 0.13) to reflect the current operating speed is required.                                                                                                                                                                                                                                                                                                                                                                      |

Silic n R vi: on 1.0)

Copyright © 2011, Texas Instruments Incorporated

M-Us

AM335x ARM Corter-Aertific optics stors

### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products               |                                 | Applications                  |                                   |

|------------------------|---------------------------------|-------------------------------|-----------------------------------|

| Audio                  | www.ti.com/audio                | Communications and Telecom    | www.ti.com/communications         |

| Amplifiers             | amplifier.ti.com                | Computers and Peripherals     | www.ti.com/computers              |

| Data Converters        | dataconverter.ti.com            | Consumer Electronics          | www.ti.com/consumer-apps          |

| DLP® Products          | www.dlp.com                     | Energy and Lighting           | www.ti.com/energy                 |

| DSP                    | dsp.ti.com                      | Industrial                    | www.ti.com/industrial             |

| Clocks and Timers      | www.ti.com/clocks               | Medical                       | www.ti.com/medical                |

| Interface              | interface.ti.com                | Security                      | www.ti.com/security               |

| Logic                  | logic.ti.com                    | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Power Mgmt             | power.ti.com                    | Transportation and Automotive | www.ti.com/automotive             |

| Microcontrollers       | microcontroller.ti.com          | Video and Imaging             | www.ti.com/video                  |

| RFID                   | www.ti-rfid.com                 |                               |                                   |

| OMAP Mobile Processors | www.ti.com/omap                 |                               |                                   |

| Wireless Connectivity  | www.ti.com/wirelessconnectivity |                               |                                   |

|                        |                                 | u Hama Dawa                   | a O a Al a a m                    |

TI E2E Community Home Page

e2e.ti.com

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2011, Texas Instruments Incorporated

# www.BDTIC.com/TI