## COMBINATION MOTOR DRIVERS WITH DC-DC CONVERTERS

#### **FEATURES**

- Configurable to Eight Modes of Combination Motor Driver

- Bipolar Stepper Motor Driver

- 16-Step Current-Mode Control

- 800-mA Average Output Current as Stepper Motor Drive

- DC Motor Driver

- 800-mA Maximum Continuous Current and 8-A/500-ns or 3-A/100-ms Peak Current for Each DC Motor Drive

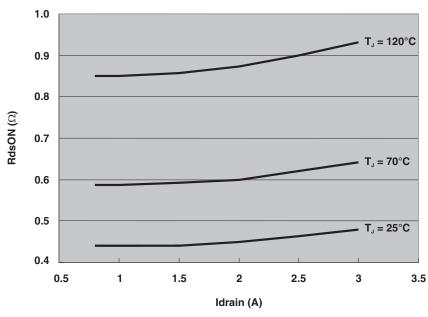

- Low ON resistance  $R_{ds(ON)} = 0.55 \Omega$  at  $T_J = 25$ °C (Typ)

- Three Integrated DC-DC Converters

- On/Off Selectable Using C\_SELECT Pin and Serial Interface

- Outputs Programmable With External Resistor Network From 1.5 V to VDIN x 0.8

- 1.5-A Output Capability for All Three Channels

- 7-V to 40-V Operating Voltage Range for DC-DC Converters

- Two Serial Interfaces for Communications

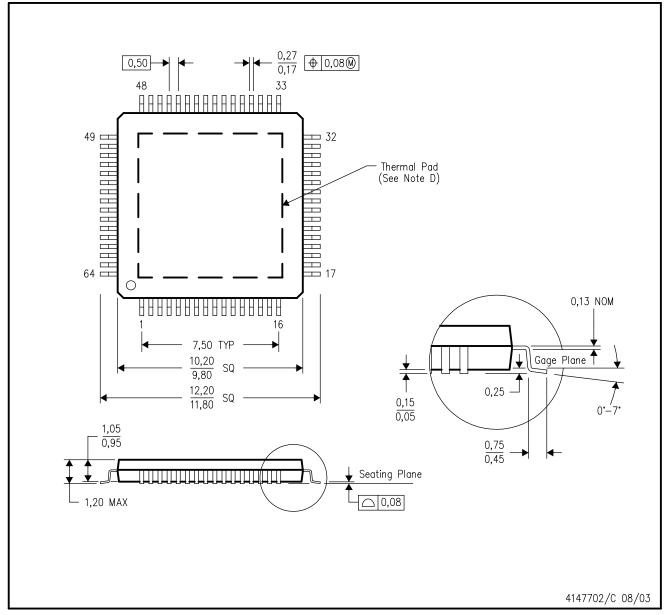

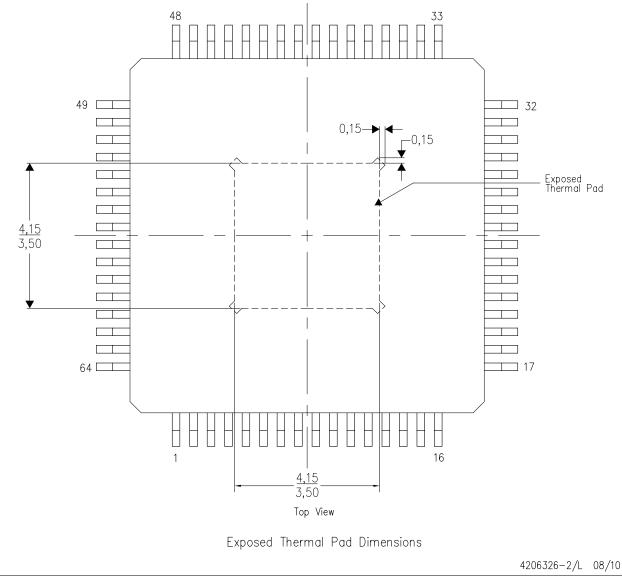

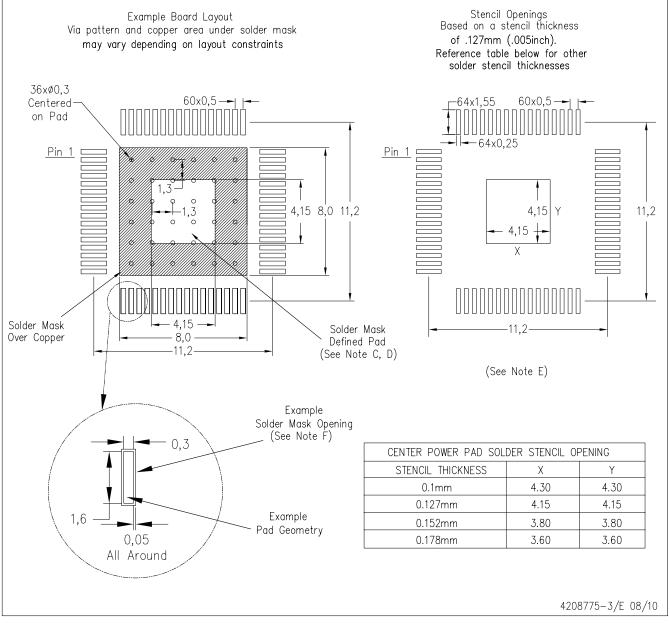

- Thermally-Enhanced Surface-Mount 64-Pin QFP PowerPAD™ Package (Eco-Friendly – RoHS and No Sb/Br)

- Power-Down Function (Deep-Sleep Mode)

- Reset Signal Output (Active Low)

- Reset (All Clear) Control Input

#### **DESCRIPTION/ORDERING INFORMATION**

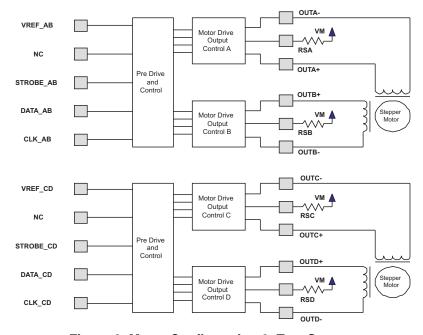

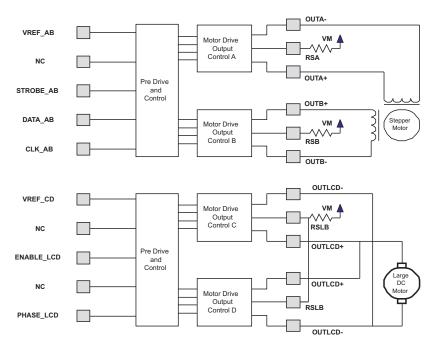

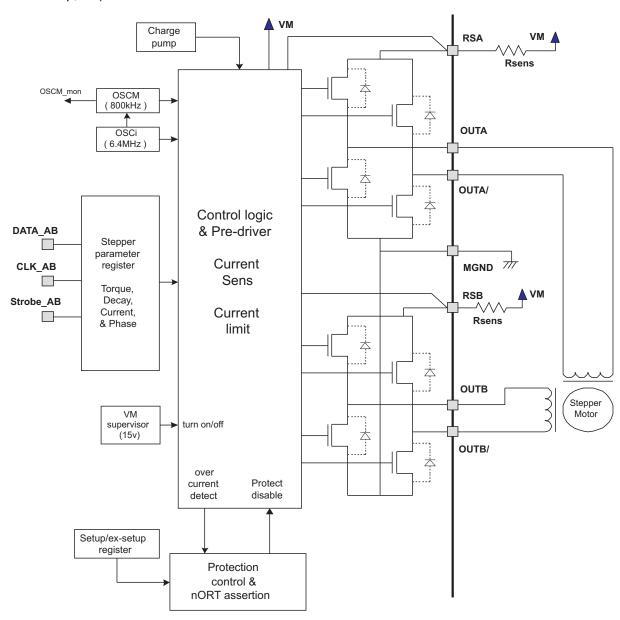

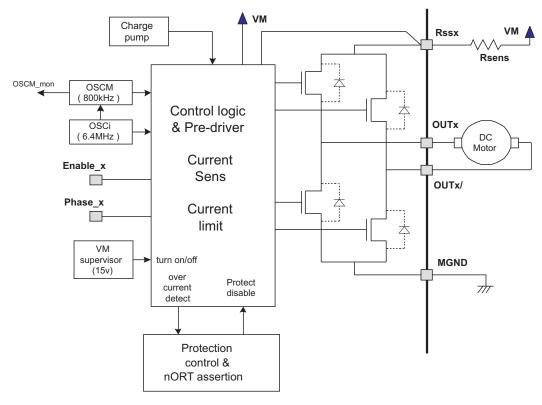

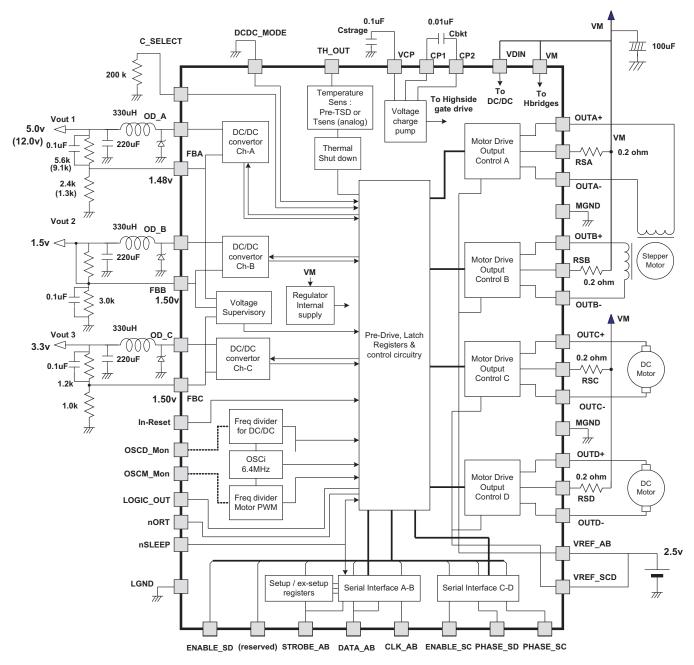

The DRV8809/DRV8810 provides an integrated motor driver solution. The chip has four H-bridges internally and is configurable to eight different modes of combination motor driver control.

The output driver block for each H-bridge consists of N-channel power MOSFETs configured as full H-bridges to drive the motor windings. The stepper motor control has a 16-step mode programmable through the three-wire serial interface (SPI). The SPI input pins are 3.3-V compatible and 5-V tolerant.

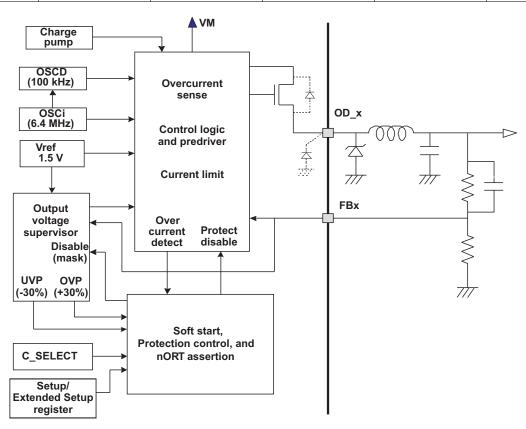

The DRV8809/DRV8810 has three DC-DC switch-mode buck converters to generate a programmable output voltage from 1.5 V to 80% of VDIN (Channel A) or up to 10 V (for Channel B and Channel C), with up to 1.5-A load current capability. The outputs are selected using the C\_SELECT terminal at start-up or using serial interface during operation.

An internal shutdown function is provided for overcurrent protection (OCP), short-circuit protection, overvoltage/undervoltage lockout (UVLO), and thermal shutdown (TSD). Also, the device has a reset function that operates at power on and at input to the In-Reset pin.

#### ORDERING INFORMATION

| T <sub>A</sub> | PACKAGE <sup>(1)(2)</sup>   | ORDERABLE PART NUMBER | TOP-SIDE MARKING |

|----------------|-----------------------------|-----------------------|------------------|

| -20°C to 80°C  | Plastic QFP 64 (S-PQFP-G64) | DRV8809A0PAP          | DRV8809A0PAP     |

| -20 C to 80 C  | Plastic QFP 64 (S-PQFF-G64) | DRV8810A0PAP          | DRV8810A0PAP     |

<sup>(1)</sup> For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PowerPAD is a trademark of Texas Instruments Inc.

<sup>(2)</sup> Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

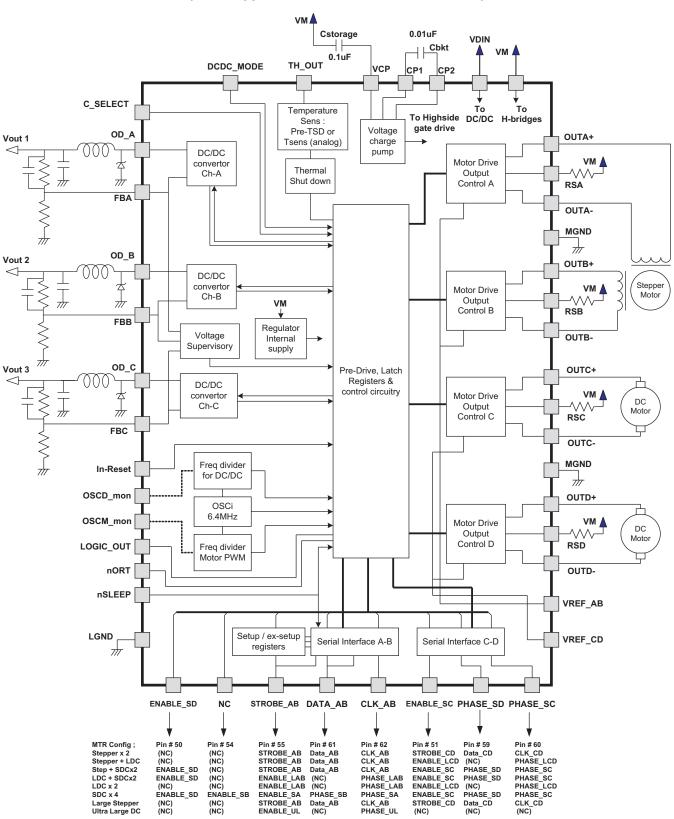

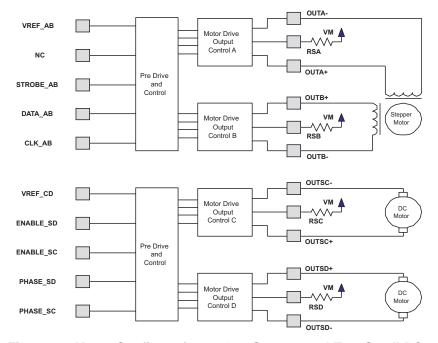

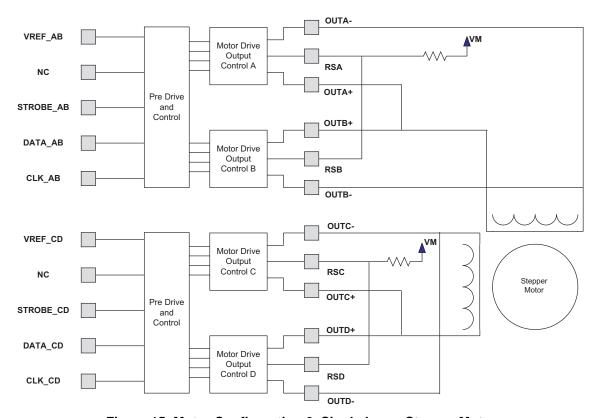

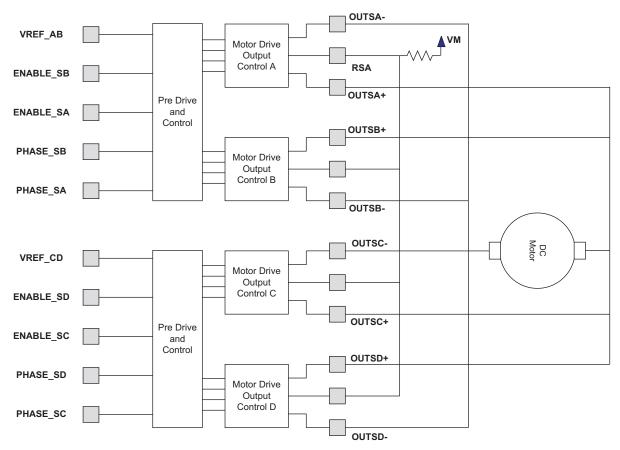

# BLOCK DIAGRAM (One Stepper Motor and Two DC Motor Drives)

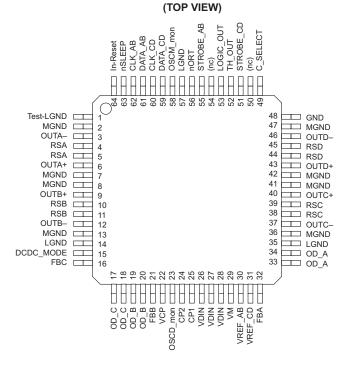

## PAP PACKAGE (TOP VIEW)

#### **TERMINAL FUNCTIONS**

|     | TERMINA               | L                 |     | DIII LUD/           | OUUNIT            |                                          |

|-----|-----------------------|-------------------|-----|---------------------|-------------------|------------------------------------------|

| NO. | NAME IN<br>SETUP MODE | NAME IN OPERATION | I/O | PULLUP/<br>PULLDOWN | SHUNT<br>RESISTOR | DESCRIPTION                              |

| 1   | Test-LGND             | Test-LGND         | -   |                     |                   | Low power or analog ground               |

| 2   | MGND                  | MGND              | -   |                     |                   | Power ground for motor                   |

| 3   | OUTA-                 | OUTA-             | 0   |                     |                   | Motor-drive output for winding A-        |

| 4   | RSA                   | RSA               | I   |                     |                   | Channel A current-sense resistor         |

| 5   | RSA                   | RSA               | I   |                     |                   | Channel A current-sense resistor         |

| 6   | OUTA+                 | OUTA+             | 0   |                     |                   | Motor-drive output for winding A+        |

| 7   | MGND                  | MGND              | =   |                     |                   | Power ground for motor                   |

| 8   | MGND                  | MGND              | -   |                     |                   | Power ground for motor                   |

| 9   | OUTB+                 | OUTB+             | 0   |                     |                   | Motor-drive output for winding B+        |

| 10  | RSB                   | RSB               | I   |                     |                   | Channel B current-sense resistor         |

| 11  | RSB                   | RSB               | I   |                     |                   | Channel B current-sense resistor         |

| 12  | OUTB-                 | OUTB-             | 0   |                     |                   | Motor-drive output for winding B-        |

| 13  | MGND                  | MGND              | -   |                     |                   | Power ground for motor                   |

| 14  | LGND                  | LGND              | -   |                     |                   | Low-power or analog ground               |

| 15  | DCDC_MODE             | DCDC_MODE         | I   | Up                  | 200 kΩ            | DC-DC Ch-B/Ch-C operation mode select    |

| 16  | FBC                   | FBC               | I   |                     |                   | Feedback signal for DC-DC converter C    |

| 17  | OD_C                  | OD_C              | 0   |                     |                   | Output for DC-DC switch mode regulator C |

| 18  | OD_C                  | OD_C              | 0   |                     |                   | Output for DC-DC switch mode regulator C |

| 19  | OD_B                  | OD_B              | 0   |                     |                   | Output for DC-DC switch mode regulator B |

| 20  | OD_B                  | OD_B              | 0   |                     |                   | Output for DC-DC switch mode regulator B |

| 21  | FBB                   | FBB               | 1   |                     |                   | Feedback signal for DC-DC converter B    |

| 22  | VCP                   | VCP               | -   |                     |                   | Charge pump capacitor                    |

## **TERMINAL FUNCTIONS (continued)**

|     | TERMINA               | L                 |     | WIIITAL I OITO      | `                 | ,                                                                                         |

|-----|-----------------------|-------------------|-----|---------------------|-------------------|-------------------------------------------------------------------------------------------|

| NO. | NAME IN<br>SETUP MODE | NAME IN OPERATION | I/O | PULLUP/<br>PULLDOWN | SHUNT<br>RESISTOR | DESCRIPTION                                                                               |

| 23  | OSCD_mon              | OSCD_mon          | 0   |                     |                   | OSCD clock monitoring                                                                     |

| 24  | CP2                   | CP2               | -   |                     |                   | Charge-pump bucket capacitor (high side)                                                  |

| 25  | CP1                   | CP1               | -   |                     |                   | Charge-pump bucket capacitor (low side)                                                   |

| 26  | VDIN                  | VDIN              |     |                     |                   | Voltage supply for DC-DC converter                                                        |

| 27  | VDIN                  | VDIN              |     |                     |                   | Voltage supply for DC-DC converter                                                        |

| 28  | VDIN                  | VDIN              |     |                     |                   | Voltage supply for DC-DC converter                                                        |

| 29  | VM                    | VM                | -   |                     |                   | Voltage supply for motors                                                                 |

| 30  | VREF_AB               | VREF_AB           | _   |                     |                   | Voltage reference for maximum stepper motor current through A and B bridges               |

| 31  | VREF_CD               | VREF_CD           | I   |                     |                   | Voltage reference for maximum stepper motor current through C and D bridges               |

| 32  | FBA                   | FBA               | I   |                     |                   | Feedback signal for DC-DC converter A                                                     |

| 33  | OD_A                  | OD_A              | 0   |                     |                   | Output for DC-DC switch mode regulator A                                                  |

| 34  | OD_A                  | OD_A              | 0   |                     |                   | Output for DC-DC switch mode regulator A                                                  |

| 35  | LGND                  | LGND              | -   |                     |                   | Low-power or analog ground                                                                |

| 36  | MGND                  | MGND              | -   |                     |                   | Power ground for motor                                                                    |

| 37  | OUTC-                 | OUTC-             | 0   |                     |                   | Motor-drive output for winding C-                                                         |

| 38  | RSC                   | RSC               | I   |                     |                   | Channel C current-sense resistor                                                          |

| 39  | RSC                   | RSC               | I   |                     |                   | Channel C current-sense resistor                                                          |

| 40  | OUTC+                 | OUTC+             | 0   |                     |                   | Motor-drive output for winding C+                                                         |

| 41  | MGND                  | MGND              | -   |                     |                   | Power ground for motor                                                                    |

| 42  | MGND                  | MGND              | -   |                     |                   | Power ground for motor                                                                    |

| 43  | OUTD+                 | OUTD+             | 0   |                     |                   | Motor-drive output for winding D+                                                         |

| 44  | RSD                   | RSD               | I   |                     |                   | Channel D current-sense resistor                                                          |

| 45  | RSD                   | RSD               | I   |                     |                   | Channel D current-sense resistor                                                          |

| 46  | OUTD-                 | OUTD-             | 0   |                     |                   | Motor drive output for winding D-                                                         |

| 47  | MGND                  | MGND              | -   |                     |                   | Power ground for motor                                                                    |

| 48  | GND                   | GND               | -   |                     |                   | Must be grounded                                                                          |

| 49  | C_SELECT              | C_SELECT          | I   | Up                  | 200 kΩ            | DC-DC converter selector                                                                  |

| 50  | -                     | ENABLE_SD         | ı   | Down                | 100 kΩ            | Enable input for DC motor D control                                                       |

| 50  | -                     | Reserved          | I   | Down                | 100 kΩ            | Reserved for DC motor operation                                                           |

| 51  | STROBE_CD             | ENABLE_SC         | I   | Down                | 100 kΩ            | Enable for DC motor C control                                                             |

| 51  | STROBE_CD             | ENABLE_LCD        | I   | Down                | 100 kΩ            | Enable for large DC motor CD control                                                      |

| 51  | STROBE_CD             | STROBE_CD         | Ι   | Down                | 100 kΩ            | Serial interface data strobe for H-bridge C, D stepper motor drive (latch on rising edge) |

| 52  | TH_OUT                | TH_OUT            | 0   | Open drain          |                   | Temperature-sensing output                                                                |

| 53  | LOGIC OUT             | LOGIC OUT         | 0   | Open drain          |                   | Protection-monitoring output                                                              |

| 54  | -                     | Reserved          | I   | Down                | 100 kΩ            | Reserved for four DC motor operation                                                      |

| 54  | -                     | ENABLE_SB         | I   | Down                | 100 kΩ            | Enable for DC motor B control                                                             |

| 55  | STROBE_ AB            | STROBE_ AB        | I   | Down                | 100 kΩ            | Serial interface data strobe for H-bridge A, B stepper motor drive (latch on rising edge) |

| 55  | STROBE_AB             | ENABLE_LAB        | I   | Down                | 100 kΩ            | Enable for large DC motor AB control                                                      |

| 55  | STROBE_AB             | ENABLE_SA         | I   | Down                | 100 kΩ            | Enable for DC motor A control                                                             |

| 56  | nORT                  | nORT              | 0   | Open drain          |                   | Reset output (open drain)                                                                 |

| 57  | LGND                  | LGND              | -   |                     |                   | Low power or analog ground                                                                |

| 58  | OSCM_mon              | OSCM_mon          | 0   | Open drain          |                   | OSCM clock monitoring                                                                     |

| 59  | DATA_CD               | PHASE_SD          | I   | Down                | 100 kΩ            | Serial input data for H-bridge C and D control                                            |

## **TERMINAL FUNCTIONS (continued)**

|     | TERMINA               | .L                |     | DUI LUD/            | CHINT             |                                                |

|-----|-----------------------|-------------------|-----|---------------------|-------------------|------------------------------------------------|

| NO. | NAME IN<br>SETUP MODE | NAME IN OPERATION | I/O | PULLUP/<br>PULLDOWN | SHUNT<br>RESISTOR | DESCRIPTION                                    |

| 59  | DATA_CD               | DATA_CD           | I   | Down                | 100 kΩ            | Serial input data for H-bridge C and D control |

| 60  | CLK_CD                | PHASE_SC          | I   | Down                | 100 kΩ            | Phase input for DC motor C control             |

| 60  | CLK_CD                | CLK_CD            | I   | Down                | 100 kΩ            | Clock input synchronization for serial data CD |

| 60  | CLK_CD                | PHASE_LCD         | I   | Down                | 100 kΩ            | Phase input for large DC motor CD control      |

| 61  | DATA_AB               | DATA_AB           | I   | Down                | 100 kΩ            | Serial input data for H-bridge A and B control |

| 61  | DATA_AB               | PHASE_SB          | I   | Down                | 100 kΩ            | Phase input for DC motor B control             |

| 62  | CLK_AB                | CLK_AB            | I   | Down                | 100 kΩ            | Clock input synchronization for serial data AB |

| 62  | CLK_AB                | PHASE_LAB         | I   | Down                | 100 kΩ            | Phase input for large DC motor AB control      |

| 62  | CLK_AB                | PHASE_SA          | I   | Down                | 100 kΩ            | Phase input for DC motor A control             |

| 63  | nSLEEP=L              | nSLEEP            | I   | Down                | 100 kΩ            | Enable/disable (part can be in sleep state)    |

| 64  | In-Reset              | In-Reset          | I   | Up                  | 200 kΩ            | Reset (L: Reset, H/open: Normal operation)     |

### Table 1. Alternate Functions of Select Pins By Operation Mode

| CONFIG                      |           |            |           | PI         | IN        |           |          |           |

|-----------------------------|-----------|------------|-----------|------------|-----------|-----------|----------|-----------|

| CONFIG                      | 50        | 51         | 54        | 55         | 59        | 60        | 61       | 62        |

| Default Name                | ENABLE_SD | ENABLE_SC  | ENABLE_SB | STROBE_AB  | PHASE_ SD | PHASE_SC  | DATA_AB  | CLK_AB    |

| Dual Stepper                | =         | STROBE_CD  | =         | STROBE_AB  | DATA_CD   | CLK_CD    | DATA_AB  | CLK_AB    |

| Stepper +<br>Large DC       | -         | ENABLE_LCD | -         | STROBE_AB  | -         | PHASE_LCD | DATA_AB  | CLK_AB    |

| Stepper + Dual<br>Small DC  | ENABLE_SD | ENABLE_SC  | -         | STROBE_AB  | PHASE_SD  | PHASE_SC  | DATA_AB  | CLK_AB    |

| Large DC +<br>Dual Small DC | ENABLE_SD | ENABLE_SC  | -         | ENABLE_LAB | PHASE _SD | PHASE_SC  | -        | PHASE_LAB |

| Dual Large DC               | -         | ENABLE_LCD | -         | ENABLE_LAB | -         | PHASE_LCD | -        | PHASE_LAB |

| Quad Small<br>DC            | ENABLE_SD | ENABLE_SC  | ENABLE_SB | ENABLE_SA  | PHASE_SD  | PHASE_SC  | PHASE_SB | PHASE_SA  |

| Large Stepper               | =         | STROBE_CD  | =         | STROBE_AB  | DATA_CD   | CLK_CD    | DATA_AB  | CLK_AB    |

| Ultra-Large DC              | =         | -          | =         | ENABLE_UL  | -         | -         | -        | PHASE_UL  |

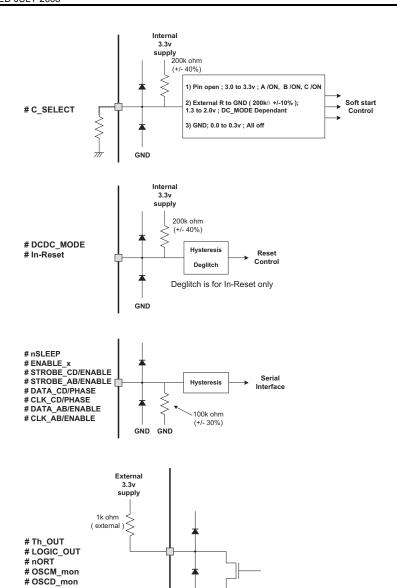

Figure 1. Input Pin Configurations

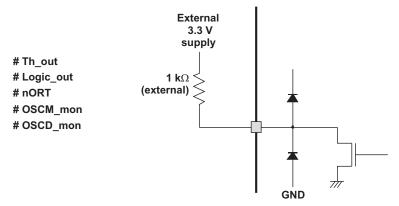

Figure 2. Open-Drain Output Pin Configurations

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)

| $V_{M}$          | Supply voltage <sup>(1)</sup>                                     | 50 V            |

|------------------|-------------------------------------------------------------------|-----------------|

|                  | Logic input voltage range, serial I/F inputs, and reset (2)       | −0.3 V to 5.5 V |

|                  | Continuous total power dissipation (θ <sub>JA</sub> = 20°C/W)     | 4 W             |

|                  | Continuous motor-drive output current for each H-bridge (100 ms)  | 3 A             |

|                  | Peak motor-drive output current for each H-bridge (500 ns)        | 8 A             |

|                  | Continuous DC-DC converter output current                         | 1.5 A           |

|                  | Continuous DC-DC converter output current ODB, C in parallel mode | 3.0 A           |

| TJ               | Operating junction temperature range (1 h)                        | 0°C to 150°C    |

| T <sub>stg</sub> | Storage temperature range                                         | −65°C to 150°C  |

|                  | Lead temperature 1.6 mm (1/16 in) from case for 10 s              | 260°C           |

|                  | ESD levels on every pin, Human-Body Model (HBM)                   | 2 kV            |

<sup>(1)</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### RECOMMENDED OPERATING CONDITIONS

|                                                           | MIN | NOM | MAX | UNIT |

|-----------------------------------------------------------|-----|-----|-----|------|

| Supply voltage, V <sub>M</sub> for motor control          | 18  | 27  | 40  | V    |

| Supply voltage for DC-DC converter (VDIN)                 | 7   | 27  | 40  | V    |

| Average output current for motor driver for each H-bridge |     |     | 800 | mA   |

| DC output current for DC-DC converter                     |     |     | 1.2 | Α    |

| DC output current for DC-DC in Ch-B/C parallel mode       |     |     | 2.4 | Α    |

| Operating ambient temperature                             | -10 |     | 50  | °C   |

| Operating junction temperature                            | 0   |     | 120 | °C   |

#### **ELECTRICAL CHARACTERISTICS**

$T_J = 0$ °C to 120°C,  $V_M = 40$  V (unless otherwise noted)

|                     | PARAMETER                | TEST CONDITIONS                                    | MIN | TYP | MAX | UNIT |

|---------------------|--------------------------|----------------------------------------------------|-----|-----|-----|------|

| Supply (Sl          | eep) Current             |                                                    |     |     |     |      |

| I <sub>SLEEP1</sub> | Supply (sleep) current 1 | nSLEEP = L, DC-DC all off                          |     | 4   | 5   | mA   |

| I <sub>SLEEP2</sub> | Supply (sleep) current 2 | nSLEEP = L, V <sub>M</sub> = 8 V, Full duty cycle  |     | 7   | 10  | mA   |

| I <sub>SLEEP3</sub> | Supply (sleep) current 3 | nSLEEP = L, V <sub>M</sub> = 40 V, Full duty cycle |     | 8   | 10  | mA   |

#### **ELECTRICAL CHARACTERISTICS**

$T_J = 0$ °C to 120°C,  $V_M = 7$  V to 40 V (unless otherwise noted)

|                   | PARAMETER                        | TEST CONDITIONS               | MIN | TYP  | MAX | UNIT |

|-------------------|----------------------------------|-------------------------------|-----|------|-----|------|

| Digital Interfa   | ace Circuit                      |                               |     |      |     |      |

| V <sub>IH</sub>   | Digital high-level input voltage | Digital inputs <sup>(1)</sup> | 2   |      | 5   | V    |

| I <sub>IH</sub>   | Digital high-level input current | Digital inputs                |     |      | 100 | μΑ   |

| $V_{IL}$          | Digital low-level input voltage  | Digital inputs                |     |      | 0.8 | V    |

| I <sub>IL</sub>   | Digital low-level input current  | Digital inputs                |     |      | 100 | μΑ   |

| V <sub>hys</sub>  | Digital input hysteresis         | Digital inputs                | 0.3 | 0.45 | 0.6 | V    |

| T <sub>degl</sub> | Digital input deglitch time      | In-Reset                      | 2.5 |      | 7.5 | μs   |

(1) Absolute maximum rating for charge-pump circuit is 60 V.

<sup>(2)</sup> The negative spike less than -5 V and narrower than 50-ns duration should not cause any problem.

$T_J = 0$ °C to 120°C,  $V_M = 7$  V to 40 V (unless otherwise noted)

|                      | PARAMETER                                                                                           | TEST CONDITIONS                                           | MIN                 | TYP                   | MAX                 | UNIT |

|----------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------|-----------------------|---------------------|------|

| Charge-Pump          | o VCP (= $_{P}$ = 0.1 $\mu$ F to 0.47 $\mu$ F, $C_{bk}$ =                                           | 0.01 μF ± 10%)                                            |                     |                       |                     |      |

| V <sub>O</sub> (CP)  | Output voltage                                                                                      | $I_{LOAD} = 0 \text{ mA}, \qquad V_{M} > VthV_{M2}$       | V <sub>M</sub> + 10 |                       | V <sub>M</sub> + 13 | V    |

| f <sub>(CP)</sub>    | Switching frequency                                                                                 |                                                           |                     | 1.6                   |                     | MHz  |

| t <sub>start</sub>   | Start-up time                                                                                       | CStorage = 0.1 $\mu$ F, $V_M \ge 16 \text{ V}$            |                     | 0.5                   | 2                   | ms   |

| Internal Cloc        | k OSCi                                                                                              |                                                           | •                   |                       |                     |      |

| f <sub>OSCi</sub>    | System clock frequency                                                                              |                                                           | 5.76                | 6.4                   | 7.04                | MHz  |

| VREF Input           |                                                                                                     |                                                           |                     |                       |                     |      |

| $V_{REF}$            | Reference voltage input                                                                             |                                                           | 0.8                 | 2.5                   | 3.6                 | V    |

| I <sub>leak-vr</sub> | Input leak current                                                                                  |                                                           |                     |                       | 1                   | μΑ   |

| C_SELECT fo          | or DC-DC Start-Up Selection (DCDC_                                                                  | MODE = L)                                                 | •                   |                       |                     |      |

| Vcs0                 | DC-DC all off                                                                                       |                                                           | 0                   |                       | 0.3                 | V    |

| Vcs1                 | Turn on ODB then ODA                                                                                | Pull down by external 200-kΩ resistor                     | 1.3                 |                       | 2                   | V    |

| Vcs2                 | Turn on ODB then ODC                                                                                | As pin open                                               | 3                   |                       | 3.3                 | V    |

| C_SELECT fo          | or DC-DC Start-Up Selection (DCDC_                                                                  | MODE = H or Open, Ch-B/C Parallel Mode)                   |                     |                       | '                   |      |

| Vcs0                 | DC-DC all off                                                                                       |                                                           | 0                   |                       | 0.3                 | V    |

| Vcs1                 | Turn on ODB/C then ODA                                                                              | Pull down by external 200-kΩ resistor                     | 1.3                 |                       | 2                   | V    |

| Vcs2                 | Turn on ODA then ODB/C                                                                              | As pin open                                               | 3                   |                       | 3.6                 | V    |

| Three DC-DC          | Converters <sup>(2)</sup>                                                                           |                                                           |                     |                       | '                   |      |

| V <sub>DINOPE</sub>  | Operating supply voltage                                                                            | Ratio to V <sub>OUT</sub> (DC)                            |                     | 1.25 = V <sub>O</sub> |                     | V    |

|                      | VoutA = 1.5 V - 30 V,                                                                               | 20 V ≤ VDIN < 40 V                                        | -3                  | Vo                    | 3                   |      |

| ODA<br>ODB           | VoutB/C = $1.5 \text{ V} - 10 \text{ V}$ ,<br>Programmable with external                            | 6.5 V ≤ VDIN < 20 V                                       | -3                  | Vo                    | 5                   | %    |

| ODC                  | reference on FBX  × VDIN > 1.25 × Vout (largest)                                                    | Vth <sub>VM−</sub> < VDIN < 6.5 V, V <sub>O</sub> ≤ 3.3 V | -3                  | Vo                    | 5                   | 70   |

| $V_{FB}$             | FBX feedback voltage                                                                                | For ODA/B/C                                               |                     | 1.50                  |                     | V    |

| I <sub>O ODx</sub>   | ODx output current (dc)                                                                             | With external L and C                                     |                     |                       | 1.5                 | Α    |

| I <sub>O ODBC</sub>  | OD <sub>BC</sub> output current (DC) in Ch-B/Ch-C parallel mode                                     | With external L and C DCDC_MODE = H                       |                     |                       | 3                   | Α    |

| I <sub>O ODx2</sub>  | Output current (dc) at low VDIN                                                                     | $VDIN = 7 \text{ V}, \qquad \qquad V_O = 5 \text{ V}$     |                     |                       | 0.8                 | Α    |

| I <sub>O ODx3</sub>  | Output current (dc) at low VDIN                                                                     | $VDIN = 7 \text{ V}, \qquad \qquad V_O = 3.3 \text{ V}$   |                     |                       | 1.5                 | Α    |

| f <sub>OSCD</sub>    | Switching (chopping frequency)                                                                      | $f_{OSCD} = (0,0)$                                        | 90                  | 100                   | 110                 | kHz  |

| D                    | FET ON resistance at 0.8 A for                                                                      | $T_J = 25^{\circ}C$                                       |                     | 0.35                  |                     |      |

| $R_{ds(ON)}$         | OD_x                                                                                                | T <sub>J</sub> = 120°C                                    |                     |                       | 0.50                | Ω    |

|                      | 5.5-V V <sub>O</sub> at VDIN = VthV_                                                                |                                                           | 4                   |                       |                     | ٧    |

| 5 V-Low              | V <sub>O</sub> voltage to 5.5 V                                                                     | $VDIN = VthV_{,} VthV_{,} = 5-V load (dc) = 0.5$          | -30                 |                       |                     | %    |

|                      | V <sub>O</sub> voltage drop from VDIN                                                               | 1                                                         |                     |                       | 1                   | V    |

| Vo_min6              | $V_O$ setting without kick UVP<br>when VDIN = VthV <sub>M+</sub><br>( $V_O$ setting at VDIN = 10 V) | $VthV_{M+} = 6-V load (DC) = 0.5 A^{(4)}$                 | 6                   |                       |                     | V    |

<sup>2)</sup> DCDC\_MODE = H, Ch-B and Ch-C are in parallel driving mode.

<sup>(3)</sup> Lower VDIN decrease gate drive and the voltage drop is increased. Specified by bench characterization only.

<sup>(4)</sup> V<sub>OUT</sub> (at VDIN = VthV<sub>M+</sub>) is lower than V<sub>O</sub> setting. When VDIN is down to VthV<sub>M+</sub>, undervoltage protection (UVP) shuts down the device, in case the V<sub>O</sub> is set as V<sub>O</sub> > 7 V. Specified by design.

$T_J = 0$  °C to 120 °C,  $V_M = 7$  V to 40 V (unless otherwise noted)

|                          | PARAMETER                                   | TEST CONDITIONS                                                            | MIN | TYP | MAX | UNIT           |

|--------------------------|---------------------------------------------|----------------------------------------------------------------------------|-----|-----|-----|----------------|

| Three DC-DC              | Converter Protection                        |                                                                            |     |     |     |                |

| I <sub>O DD ODx</sub>    | Overcurrent detect for OD_x source          | Peak current in each ON cycle                                              | 1.8 |     | 3   | Α              |

| tFILT <sub>OCP</sub>     | OCP filtering time                          | By OSCi cycles                                                             |     | 2   |     | cycles         |

| t <sub>ODSD</sub>        | DC-DC shutdown filter                       | Number of subsequent chopping cycles with OCP detection                    |     | 4   |     | chop<br>cycles |

| Vovpx                    | Overvoltage protection (OVP)                | Percentage of nominal Voutx detected at VFB                                | 25  | 30  | 35  | %              |

| Vuvpx                    | Undervoltage protection (UVP)               | Percentage of nominal Voutx detected at VFB (VFB decreasing)               | -25 | -30 | -35 | %              |

| tVfilter                 | OVP/UVP filtering time                      |                                                                            | 3   | 8   | 13  | us             |

| t <sub>sst</sub>         | Start-up time with soft start               |                                                                            |     |     | 56  | ms             |

| V <sub>stover</sub>      | Start-up overshoot                          | Ratio to V <sub>O</sub>                                                    |     |     | 3   | %              |

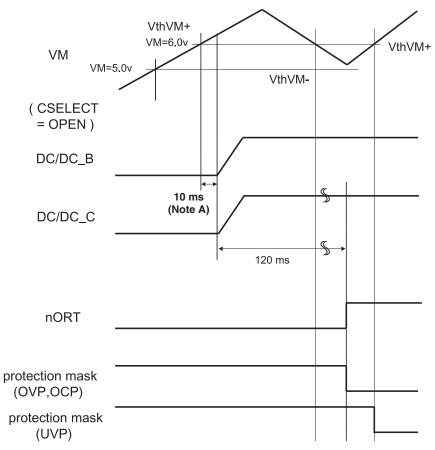

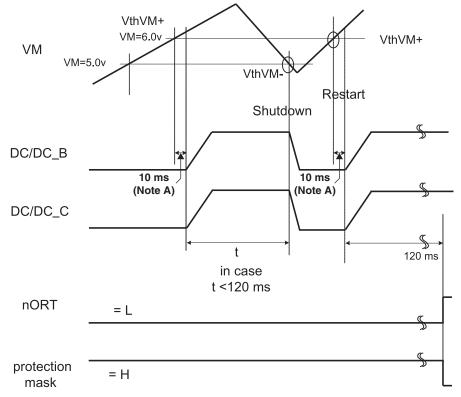

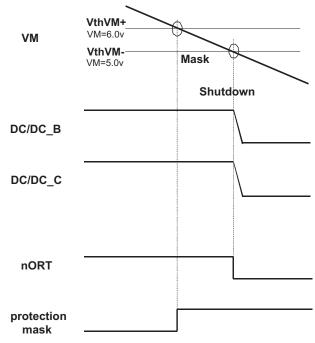

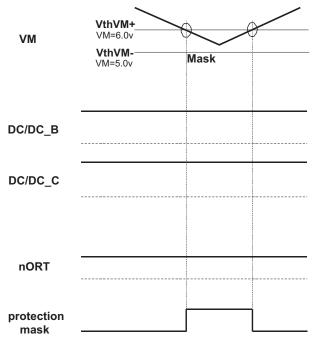

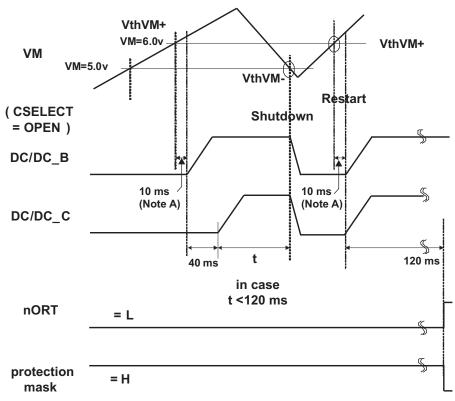

| V <sub>M</sub> Supervise | ory                                         |                                                                            |     |     |     |                |

| VthV <sub>M</sub>        | nORT for V <sub>M</sub> low threshold       | V <sub>M</sub> decreasing                                                  | 4.5 | 5   | 6   | V              |

| $VthV_{M+}$              | nORT for V <sub>M</sub> high threshold      | V <sub>M</sub> increasing                                                  | 5.5 | 6   | 7   | V              |

| $VthV_{Mh}$              | nORT for V <sub>M</sub> detect hysteresis   | (VthV <sub>M+</sub> ) - (VthV_)                                            | 0.5 | 1   |     | V              |

| VthV <sub>M2</sub>       | For motor driver off <sup>(5)</sup>         |                                                                            |     |     | 15  | V              |

| t <sub>VM</sub> filt     | V <sub>M</sub> monitor filtering time       | For V <sub>M</sub> threshold detect                                        | 10  |     | 30  | μs             |

| Thermal Shu              | tdown (TSD)                                 | 1                                                                          |     |     |     |                |

| T <sub>TSD</sub>         | Thermal shutdown set points                 |                                                                            | 150 | 170 | 190 | °C             |

|                          | Sense, Pre TSD (See Extended Setu           | ıp Register Definition)                                                    |     |     |     |                |

| T <sub>TSD0</sub>        | Temperature sense point 0                   | Register selectable,<br>Assert logic H at TH_OUT                           | 130 | 150 | 170 | °C             |

| T <sub>TSD1</sub>        | Temperature sense point 1                   | Register selectable,<br>Assert logic H at TH_OUT                           | 120 | 140 | 160 | °C             |

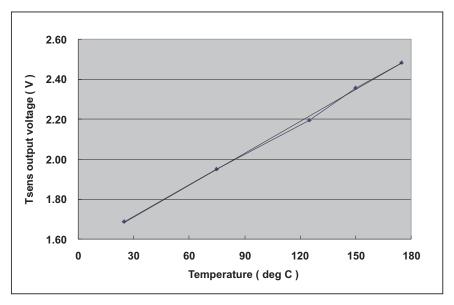

| Tc_sens                  | TH_OUT (analog out) temperature coefficient | Specified by design                                                        |     | 6   |     | mV/°C          |

| RESET/nORT               | Г։ Open-Drain Outputs (nORT, LOGIն          | C_OUT, TH_OUT)                                                             |     |     |     |                |

| V <sub>OH</sub>          | High-state voltage                          | $R_L = 1 \text{ k}\Omega \text{ to } 3.3 \text{ V}$                        | 3   |     |     | V              |

| V <sub>OL</sub>          | Low-state voltage                           | $R_L = 1 \text{ k}\Omega \text{ to } 3.3 \text{ V}$                        |     |     | 0.3 | V              |

| I <sub>OL</sub>          | Low-state sink current                      | V <sub>O</sub> = 0.4 V                                                     | 3   |     |     | mA             |

| t <sub>r</sub>           | Rise time                                   | 10% to 90%                                                                 |     |     | 1   | μs             |

| t <sub>f</sub>           | Fall time                                   | 90% to 10%                                                                 |     |     | 50  | ns             |

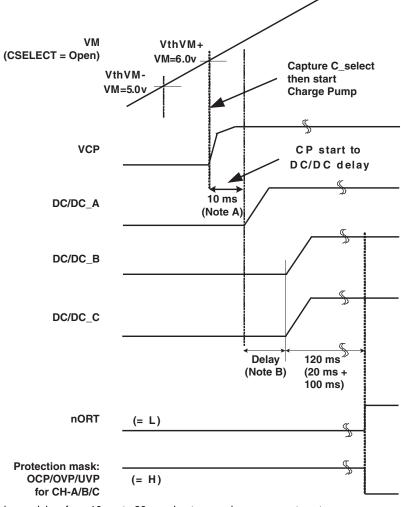

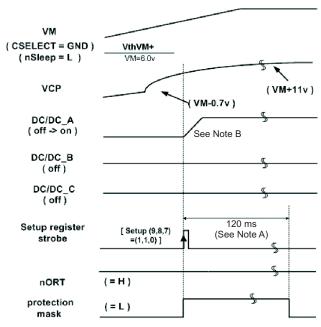

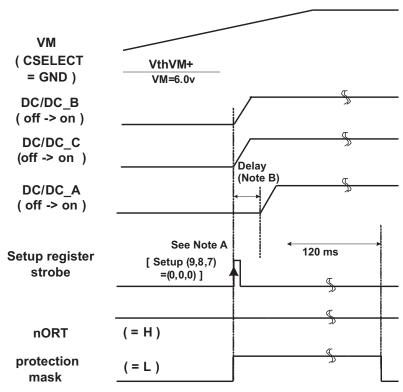

| RESET/nORT               | Г Delay: Start-Up Sequence                  | 1                                                                          |     |     |     |                |

| t <sub>ord1</sub>        | nORT delay 1                                | Reset deassertion from VthV <sub>M+</sub> < VDIN for DC-DC wake up falling |     | 300 | 390 | ms             |

| t <sub>ord3</sub>        | DC-DC turnon delay                          | From one DC-DC wake up to following DC-DC to go soft-start sequence        |     | 1.7 |     | ms             |

| t <sub>ord4</sub>        | nORT delay 4                                | Reset deassertion from 2nd DC-DC wake up                                   |     | 120 | 180 | ms             |

| In-Reset                 |                                             |                                                                            |     |     |     |                |

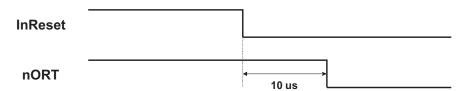

| t <sub>reset</sub>       | In-Reset assertion to nORT assertion delay  | In-Reset falling to nORT failing                                           |     | 5   | 10  | μs             |

<sup>(5)</sup> No nORT assertion to  $VthV_{M2}$  detection

$T_J = 0$ °C to 120°C,  $V_M = 7$  V to 40 V (unless otherwise noted)

|                            | PARAMETER                                                    | TEST CONDITIONS                                                             | MIN | TYP  | MAX | UNIT   |

|----------------------------|--------------------------------------------------------------|-----------------------------------------------------------------------------|-----|------|-----|--------|

| H-Bridge Drivers           | s (OUTx+ and OUTx-)                                          |                                                                             |     |      |     |        |

| I <sub>OUT1</sub> (max)    | Peak output current 1                                        | Less than 500-ns period                                                     |     |      | 8   | Α      |

| I <sub>OUT2</sub> (max)    | Peak output current 2                                        | Less than 100-ms period                                                     |     |      | 3   | Α      |

| I <sub>OUT</sub> (max)     | Average continuous output current                            |                                                                             |     |      | 0.8 | Α      |

| D                          | FFT ON registered at 0.9 A                                   | T <sub>J</sub> = 25°C                                                       |     | 0.55 |     | 0      |

| $R_{ds(ON)}$               | FET ON resistance at 0.8 A                                   | T <sub>J</sub> = 120°C                                                      |     |      | 1   | Ω      |

| I <sub>CEX</sub>           | Output leakage current                                       | V <sub>OUTX</sub> = 0 V or 10 V                                             |     |      | 10  | μΑ     |

| I <sub>RS</sub>            | Sense resistor supply current                                | nORT = Low                                                                  |     |      | 15  | μΑ     |

| I <sub>OC Motor</sub>      | Motor overcurrent threshold for each H-bridge <sup>(6)</sup> |                                                                             | 3   |      | 5   | Α      |

| t <sub>filterM</sub>       | Motor overcurrent filter time                                |                                                                             | 2.5 | 5    | 8.5 | μs     |

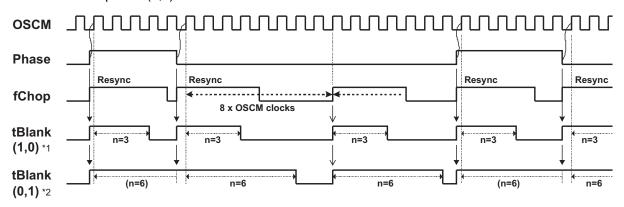

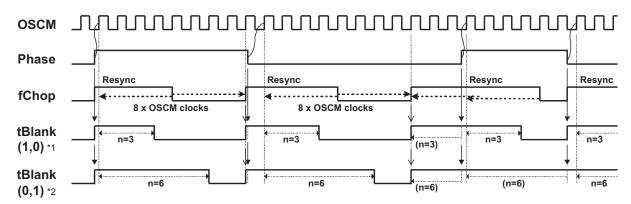

| f <sub>OSCM</sub>          | Motor oscillator frequency                                   | F_OSCM = (0,0)                                                              | 720 | 800  | 880 | kHz    |

| f <sub>chop</sub>          | Motor chopping frequency = f <sub>OSCM</sub> /8              | F_OSCM = (0,0)                                                              | 90  | 100  | 110 | kHz    |

| Stepper Motor D            | rive (Parameters Are Tested With                             | out Motor Loading)                                                          |     |      |     |        |

| I <sub>STEPMOTORAVG</sub>  | Average stepper motor current for H-bridge                   | V <sub>M</sub> = 40 V                                                       |     |      | 800 | mA     |

| I <sub>STEPMOTORPeak</sub> | Peak stepper motor current for H-bridge                      | V <sub>M</sub> = 40 V                                                       |     |      | 1.3 | Α      |

|                            |                                                              | VL <sub>16</sub> , Phase angle = 90°                                        |     | 100  |     |        |

|                            |                                                              | VL <sub>15</sub> , Phase angle = 84°                                        |     | 100  |     |        |

|                            |                                                              | VL <sub>14</sub> , Phase angle = 79°                                        |     | 98   |     |        |

|                            |                                                              | VL <sub>13</sub> , Phase angle = 73°                                        |     | 96   |     |        |

|                            |                                                              | VL <sub>12</sub> , Phase angle = 68°                                        |     | 92   |     |        |

|                            |                                                              | VL <sub>11</sub> , Phase angle = 62°                                        |     | 88   |     |        |

|                            |                                                              | VL <sub>10</sub> , Phase angle = 56°                                        |     | 83   |     |        |

|                            | Stepper motor current limit                                  | VL <sub>9</sub> , Phase angle = 51°                                         |     | 77   |     |        |

|                            | threshold                                                    | VL <sub>8</sub> , Phase angle = 45°                                         |     | 71   |     | %      |

|                            | (internal reference) (7)                                     | VL <sub>7</sub> , Phase angle = 40°                                         |     | 63   |     |        |

|                            |                                                              | VL <sub>6</sub> , Phase angle = 34°                                         |     | 56   |     |        |

|                            |                                                              | VL <sub>5</sub> , Phase angle = 28°                                         |     | 47   |     |        |

|                            |                                                              | VL <sub>4</sub> , Phase angle = 23°                                         |     | 38   |     |        |

|                            |                                                              | VL <sub>3</sub> , Phase angle = 17°                                         |     | 29   |     |        |

|                            |                                                              | VL <sub>2</sub> , Phase angle = 11°                                         |     | 20   |     |        |

|                            |                                                              | VL <sub>1</sub> , Phase angle = 6°                                          |     | 10   |     |        |

|                            |                                                              | VL <sub>0</sub> , Phase angle = 0°                                          |     | 0    |     |        |

| I <sub>OUT</sub>           | Output current accuracy at 100% setting <sup>(7)</sup>       | Excludes VREF and RSENS errors,<br>I <sub>OUT</sub> > 1 A <sup>(7)(8)</sup> | -5  |      | 5   | %      |

| Isw <sub>Leakage</sub>     | Switch (driver MOSFET) leakage current                       | Outputs off                                                                 | -10 |      | 10  | μА     |

| t <sub>ab</sub>            | Stepper motor blanking time                                  | By OSCi cycles                                                              | 8   |      | 9   | cycles |

<sup>6)</sup> When the overcurrent is detected, all H-bridges are shut down and assert nORT pulse (40 ms).

<sup>(7)</sup> This is not measured directly, checked by Itrip amplifier gain without motor loading

<sup>(8)</sup> This device may show current setting error when motor current is less than 1 A, due to noise filter delay at the Itrip comparator.

$T_J = 0$ °C to 120°C,  $V_M = 7$  V to 40 V (unless otherwise noted)

|                      | PARAMETER                                                   | TEST CONDITIONS                                                        | MIN | TYP | MAX  | UNIT |

|----------------------|-------------------------------------------------------------|------------------------------------------------------------------------|-----|-----|------|------|

| Stepper and          | DC Motor Drivers                                            |                                                                        | 1   |     |      |      |

| t <sub>r</sub>       | Rise time                                                   | V <sub>M</sub> = 27 V                                                  | 100 |     | 300  | ns   |

| t <sub>f</sub>       | Fall time                                                   | 20% to 80%                                                             | 100 |     | 300  | ns   |

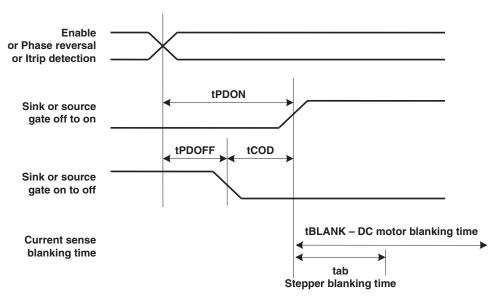

| t <sub>PDOFF</sub>   | Enable or strobe detection to sink or source gate off delay |                                                                        | 50  | 150 | 400  | ns   |

| t <sub>COD</sub>     | Crossover delay time, to prevent shoot through              |                                                                        | 100 | 600 | 1000 | ns   |

| t <sub>PDON</sub>    | Enable or strobe detection to sink or source gate on delay  |                                                                        |     | 750 |      | ns   |

| DC Motor Dr          | rivers                                                      |                                                                        |     |     |      |      |

| t <sub>blank</sub>   | Blanking time                                               | TBLNK = $(0,0)$ for Min, $(1,1)$ for Max, $f_{CHOP} = 100 \text{ kHz}$ | 1.6 |     | 5.65 | μs   |

| t <sub>wPminp</sub>  | Minimum pulse duration (phase)                              |                                                                        |     |     | 1    | μs   |

| t <sub>wPmine</sub>  | Minimum pulse duration (enable)                             |                                                                        |     |     | 1    | μs   |

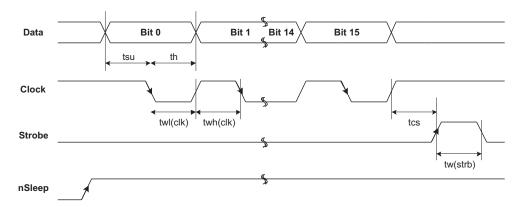

| Serial Interfa       | ace                                                         |                                                                        |     |     |      |      |

| f <sub>(CLK)</sub>   | Clock frequency                                             |                                                                        | 1   |     | 25   | MHz  |

| t <sub>wh(CLK)</sub> | Minimum high-level pulse width                              |                                                                        | 10  |     |      | ns   |

| t <sub>wl(CLK)</sub> | Minimum low-level pulse width                               |                                                                        | 10  |     |      | ns   |

| t <sub>su</sub>      | Setup time, data to CLK↓                                    |                                                                        | 10  |     |      | ns   |

| t <sub>h</sub>       | Hold time, CLK↓ to data                                     |                                                                        | 10  |     |      | ns   |

| t <sub>cs</sub>      | CLK↓ to STROBE↑                                             |                                                                        | 10  |     |      | ns   |

| t <sub>sc</sub>      | STROBE↓ to CLK↑                                             |                                                                        | 10  |     |      | ns   |

| t <sub>w(STRB)</sub> | Minimum strobe pulse duration                               |                                                                        | 20  |     |      | ns   |

| t <sub>ss_min</sub>  | Strobe mask time from nSLEEP                                |                                                                        | 1.5 |     | 4    | μs   |

| Serial Interfa       | ace: ID Monitor Function at LOGIC_OU                        | JT, Extended Setup Mode                                                |     |     |      |      |

| t <sub>ODL</sub>     | 0 data output delay bit 3 to bit 0 (ext-setup) = (1100)     | From strobe rise to LOGIC_OUT, 1 $k\Omega$ to external 3.3 $V$         |     |     | 4000 | ns   |

| t <sub>ODH</sub>     | 1 data output delay bit 3 to bit 0 (ext-setup) = (1111)     | From strobe rise to LOGIC_OUT, 1 kΩ to external 3.3 V                  |     |     | 4000 | ns   |

#### **Serial Interface**

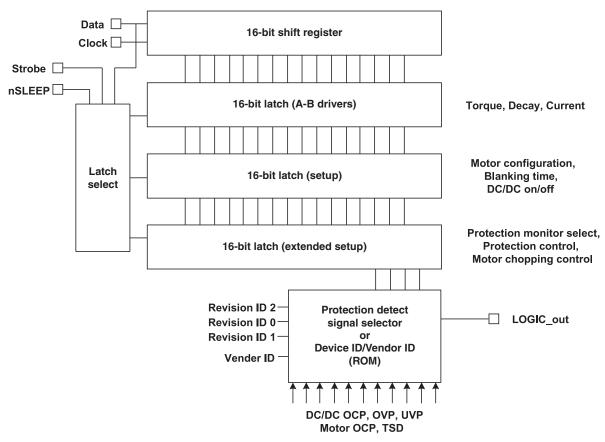

The device has two serial interface circuit blocks for stepper motor driving control. These two serial interfaces provide controls to each motor driver independently.

| CLKAB    | Serial clock for H-bridge A, B  |

|----------|---------------------------------|

| DATAAB   | Serial data for H-bridge A, B   |

| STROBEAB | Strobe input for H-bridge A, B  |

|          |                                 |

| CLKCD    | Serial clock for H-bridge C, D  |

| DATACD   | Serial data for H-bridge C, D   |

| STROBECD | Strobe signal for H-bridge C, D |

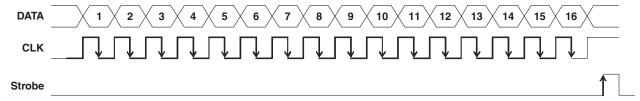

Sixteen bits serial data is shifted into the least significant bit (LSB) of the serial data input (DATA) shift register on the falling edge of the serial clock (CLK). After 16 bits of data transfer, the strobe signal (Strobe) rising edge latches all the shifted data. During data transfer, Strobe voltage level is acceptable high or low.

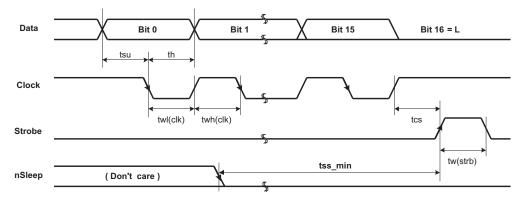

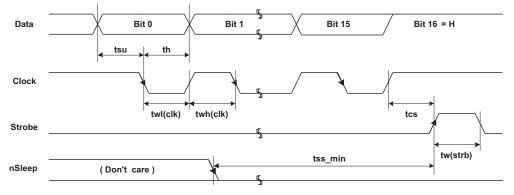

Figure 3. Serial Interface

#### Setup Mode/Power-Down Mode

The motor output mode is configured through serial interface (DATA AB, CLK AB and STROBEAB) when nSLEEP = L. After setup, the nSLEEP pin must be pulled high for normal motor drive control. The condition that the device requires for setup (initialization) is after the nORT (Reset) output goes to high from the low level (power on, recovery from  $V_M < 7$  V). While nSLEEP is low, all the motor drive functions are shut down and their outputs are high-impedance state. Also the stepper parameters in the register are all reset to 0. This device forces motor driver functions to shut down for the power-down mode, and it is not damaged even if nSLEEP is asserted during motor driving. At the Strobe pulse rising edge, the DATA signal level must be low for normal setup mode (see *Extended Setup Mode* for another option).

#### **Extended Setup Mode**

While nSLEEP = L, if the DATA signal level is set high when the Strobe pulse is set, the serial interface recognizes the input data to set the extended setup mode. This extended setup register enables monitoring and controlling the fault condition of this chip. One of the internal protection control signals is selected and provided to LOGIC OUT pin. Also, this enables the application to ignore the protection control and/or suppress the reset signal generation. This device has device ID (3-bit ROM) and vendor ID (1-bit ROM), which can be read out from LOGIC OUT. Four bits are assigned to select the LOGIC OUT signal, including the ID ROM bit readout.

Serial Interface A-B: Set A-B motor operating parameters and access to setup/extended setup register

A. A-B register at EXT-setup mode has device/vendor ID ROM. The ID must be read out at LOGIC OUT pin.

Figure 4. Serial Interface A-B

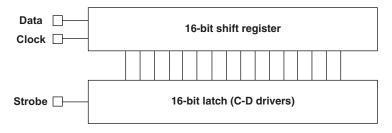

Serial interface C-D: Set C-D motor operating parameters

Figure 5. Serial Interface C-D

### **Serial Interface Timing**

Figure 6. nSLEEP = H: Set Stepper Motor Operating Parameters

Figure 7. nSLEEP = L (Bit 16 = L): Setup Mode

A. For initial setup, nSLEEP state can be don't care before the tss\_min timing prior to the strobe.

Figure 8. nSLEEP = L (Bit 16 = H): Extended Setup Mode

#### **Setup Register Bit Assignment**

Setup register bits are assigned for motor configuration, blanking time, gain, and DC-DC switches. This register can be accessed only in Setup mode (nSLEEP = L and bit 16 data = L).

Table 2. Setup Register

| BIT NO. | NAME             | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                   |

|---------|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Motor select 0   | 0       | Motor configuration, $< 2,1,0 > (0,0,0)$ : Stepper $\times 2$ (default)                                                                                                                                                                                                                                                       |

| 1       | Motor select 1   | 0       | (0,0,1): Stepper + LDC, (0,1,0): Stepper + 2 × sDCs<br>(0,1,1): DCL + 2 × sDC, (1,0,0): DCL × 2 (1,0,1): 4 × sDC                                                                                                                                                                                                              |

| 2       | Motor select 2   | 0       | (1,1,0): Large stepper (1,1,1): Ultra-large DC                                                                                                                                                                                                                                                                                |

| 3       | TBLNK AB0        | 0       | Tblank for DC motor driving, Tblank is inserted at any phase change                                                                                                                                                                                                                                                           |

| 4       | TBLNK AB1        | 0       | and beginning of each chopping cycle.  AB1 AB0: Blanking time for A/B side drivers,                                                                                                                                                                                                                                           |

| 5       | TBLNK CD0        | 0       | CD1 CD0: Blanking time for C/D side drivers,                                                                                                                                                                                                                                                                                  |

| 6       | TBLNK CD1        | 0       | 00: $(1 \div f_{CHOP}) \div 8 \times 5$ (= 6.25 $\mu$ s) (default)<br>01: $(1 \div f_{CHOP}) \div 8 \times 6$ (= 7.50 $\mu$ s)<br>10: $(1 \div f_{CHOP}) \div 8 \times 3$ (= 3.75 $\mu$ s)<br>11: $(1 \div f_{CHOP}) \div 8 \times 4$ (= 5.00 $\mu$ s)<br>For stepper motor driving, only the fixed blanking time is applied. |

| 7       | DC/DC_A SW       | 0       | DC-DC ODA control, 0: ON (default), 1: OFF                                                                                                                                                                                                                                                                                    |

| 8       | DC/DC_B SW       | 0       | DC-DC ODB control, 0: ON (default), 1: OFF                                                                                                                                                                                                                                                                                    |

| 9       | DC/DC_C SW       | 0       | DC-DC ODC control, 0: ON (default), 1: OFF This bit is ignored when DCDC_MODE = H or open                                                                                                                                                                                                                                     |

| 10      | Motor_AB gain    | 0       | 0: 1/10 (default), 1: 0                                                                                                                                                                                                                                                                                                       |

| 11      | Motor_CD gain    | 0       | 0: 1/10 (default), 1: 0                                                                                                                                                                                                                                                                                                       |

| 12      | OSCD frequency 0 | 0       | <1,0> = (0,0) 100 kHz (default)                                                                                                                                                                                                                                                                                               |

| 13      | OSCD frequency 1 | 0       | (0,1) 50 kHz (1,0) 200 kHz (1,1) 132.5 kHz These setup bits can be changed when the DC-DC regulators are in operation.                                                                                                                                                                                                        |

| 14      | OSCM frequency 0 | 0       | <1,0> = (0,0) 800 kHz (default)                                                                                                                                                                                                                                                                                               |

| 15      | OSCM frequency 1 | 0       | (0,1) 400 kHz<br>(1,0) 1.06 MHz<br>(1,1) 1.6 MHz                                                                                                                                                                                                                                                                              |

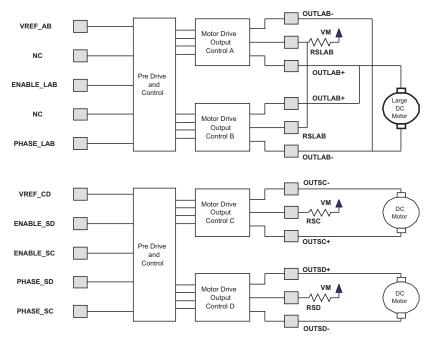

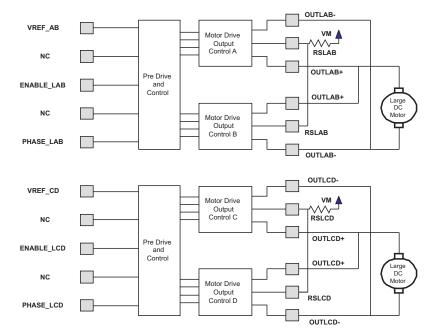

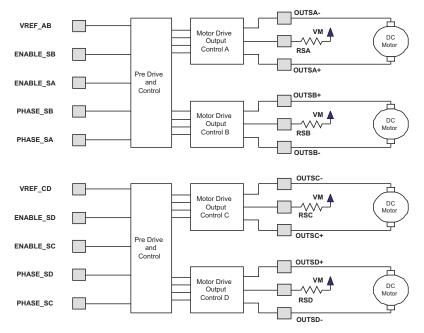

The device can be configured to one out of eight different motor control combination modes. When the device is powered on or is recovering from reset, the mode can be selected by writing to the setup register through the serial interface AB, during Setup mode (nSLEEP = L).

**Table 3. DC and Stepper Motor Configuration**

| SETUP REGISTER |       | H-BRIDGE AND MOTOR CONFIGURATION |                                                                              |              |                      |                |  |

|----------------|-------|----------------------------------|------------------------------------------------------------------------------|--------------|----------------------|----------------|--|

| BIT 2          | BIT 1 | BIT 0                            | OUTA+, OUTA-                                                                 | OUTB+, OUTB- | OUTC+, OUTC-         | OUTD+, OUTD-   |  |

| 0              | 0     | 0                                | Stepper me                                                                   | otor drive   | Stepper m            | otor drive     |  |

| 0              | 0     | 1                                | Stepper me                                                                   | otor drive   | Large DC n           | notor drive    |  |

| 0              | 1     | 0                                | Stepper me                                                                   | otor drive   | DC motor drive       | DC motor drive |  |

| 0              | 1     | 1                                | Large DC motor drive                                                         |              | DC motor drive       | DC motor drive |  |

| 1              | 0     | 0                                | Large DC motor drive                                                         |              | Large DC motor drive |                |  |

| 1              | 0     | 1                                | DC motor drive DC motor drive                                                |              | DC motor drive       | DC motor drive |  |

| 1              | 1     | 0                                | Large stepper motor drive: A + B for first winding, C + D for second winding |              |                      |                |  |

| 1              | 1     | 1                                | Ultra-large DC motor drive                                                   |              |                      |                |  |

Extended setup (EX-setup) register bits are assigned for protection control, pre TSD, and multiplexer test mode selection. This register can be accessed only in Setup mode (nSLEEP = L and bit 16 data = H).

Table 4. Extended Setup Register (EX-setup) Bit Assignment

| BIT NO. | NAME                                                     | DEFAULT | DESCRIPTION                                                                                                                                                                                                                                                                                                                   |

|---------|----------------------------------------------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | Signal select 0                                          | 0       | Signal selector monitored on LOGIC_OUT                                                                                                                                                                                                                                                                                        |

| 1       | Signal select 1                                          | 0       | DC-DC OCP detection, DC-DC voltage supervisor (OVP or UVP),                                                                                                                                                                                                                                                                   |

| 2       | Signal select 2                                          | 0       | Motor overcurrent (four H-bridges),                                                                                                                                                                                                                                                                                           |

| 3       | Signal select 3                                          | 0       | TSD, etc. [shutdown (protection) signals must be latched]                                                                                                                                                                                                                                                                     |

| 4       | Ignore SD 0                                              | 0       | 0 = Normal operation, 1 = Ignore DC-DC OCP                                                                                                                                                                                                                                                                                    |

| 5       | Ignore SD 1                                              | 0       | 0 = Normal operation, 1 = Ignore DC-DC voltage supervisor                                                                                                                                                                                                                                                                     |

| 6       | Ignore SD 2                                              | 0       | 0 = Normal operation, 1 = Ignore motor OCP                                                                                                                                                                                                                                                                                    |

| 7       | Ignore SD 3                                              | 0       | 0 = Normal operation, 1 = Ignore thermal shutdown                                                                                                                                                                                                                                                                             |

| 8       | Disable nORT 0<br>(selective shutdown for<br>DC-DC Ch-C) | 0       | 0 = Normal operation 1 = Disable nORT assertion but shut down DC-DC Ch-C, in case of DC-DC Ch-C fault condition Ch-C shutdown is released by nSLEEP rise edge. If fault condition is on the other channels (with bit = 0), assert nORT and shut down all three DC-DC channels. This bit is ignored when DCDC_MODE = H or open |

| 9       | Disable nORT 1<br>(Selective shutdown for<br>DC-DC Ch-B) | 0       | 0 = Normal operation 1 = Disable nORT assertion but shut down DC-DC channel B, in case of DC-DC Ch-B fault condition Ch-B shutdown is released by nSLEEP rise edge. If fault condition on the other channels (with bit = 0), assert nORT and shut down all three DC-DC channels.                                              |

| 10      | Disable nORT 2<br>(Selective shutdown for<br>DC-DC Ch-A) | 0       | 0 = Normal operation, 1 = Disable nORT assertion but shutdown the DC-DC Ch-A, in case of DC-DC Ch-A fault condition. Ch-A shutdown is released by nSLEEP rise edge. If fault condition on the other channels (with bit is 0), assert nORT and shut down all three DC-DC channels.                                             |

| 11      | Pre TSD 0                                                | 0       | 0 = Ttsd0 = Ttsd - 20°C, 1 = Ttsd1= Ttsd - 30°C                                                                                                                                                                                                                                                                               |

| 12      | Pre TSD 1                                                | 0       | 0 = Pre-TSD (logic) output, 1 = TH_OUT Analog output                                                                                                                                                                                                                                                                          |

| 13      | Test mux 0                                               | 0       | Test mode selection, < 2,1,0 > = (0,0,0) Normal operation                                                                                                                                                                                                                                                                     |

| 14      | Test mux 1                                               | 0       | (0,0,1) TSD control – 1,                                                                                                                                                                                                                                                                                                      |

| 15      | Test mux 2                                               | 0       | (0,1,0) TSD control – 2, (0,1,1) OSC monitor enable,                                                                                                                                                                                                                                                                          |

#### **Table 5. LOGIC OUT Selection**

| NO. | EX-setup<br>REGISTER<br>(BITS 3-0) | SIGNAL SELECTION<br>(LISTED SIGNAL                           | SIGNAL POINT    |             |             |

|-----|------------------------------------|--------------------------------------------------------------|-----------------|-------------|-------------|

| 0   | 0000 (default)                     | DC-DC OCP_A                                                  | DC-DC OVP_A     | DC-DC UVP_A | Latched out |

| 1   | 0001                               | DC-DC OCP_B                                                  | DC-DC OVP_B     | DC-DC UVP_B | Latched out |

| 2   | 0040                               | DC-DC OCP_C                                                  | DC-DC OVP_C     | DC-DC UVP_C | Latched out |

| 2   | 0010                               | This bit is ignored when DCDC_MODE p                         | in = H or open. |             |             |

| 3   | 0011                               | DC-DC OCP_A                                                  | DC-DC OCP_B     | DC-DC OCP_C | Latched out |

| 4   | 0100                               | DC-DC OVP_A                                                  | DC-DC OVP_B     | DC-DC OVP_C | Latched out |

| 5   | 0101                               | DC-DC UVP_A                                                  | DC-DC UVP_B     | DC-DC UVP_C | Latched out |

| 6   | 0110                               | Motor OCP                                                    |                 |             | Latched out |

| 7   | 0111                               | TSD                                                          | Latched out     |             |             |

| 8   | 1000                               | Revision $<0> = 1$ : For this device $<2,1,0> = (1,0,1) = 5$ |                 |             | ROM         |

| 9   | 1001                               | Revision <1> = 0: For this device                            |                 | ROM         |             |

| 10  | 1010                               | Revision <2> = 1: For this device                            |                 |             | ROM         |

| 11  | 1011                               | Vendor <0> = 0: For TI <1,0> = TI (0,0), NG (1,0)            |                 |             | ROM         |

| 12  | 1100                               | Vendor <1> = 0: For TI <1,0> = Reserve (0,1), (1,1)          |                 |             | ROM         |

| 13  | 1101                               | Internal oscillator clock (as divided by 32 = 200 kHz)       |                 |             |             |

| 14  | 1110                               | Fixed value as 1 (open-drain output buffer off)              |                 |             |             |

| 15  | 1111                               | Fixed value as 1 (open-drain output buffer off)              |                 |             |             |

### **Table 6. Test Mux Selection**

| NO. | BITS 15, 14, 13 |                    | DESCRIPTION                                                                                                                                                          |  |  |

|-----|-----------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 0   | 0, 0, 0         | Normal operation   |                                                                                                                                                                      |  |  |

| 1   | 0, 0, 1         | TSD control 1      | At TSD event, shut down only motor driver part, DC-DC keep ON, keep setup register values, motor shutdown released by nSLEEP = L, no nORT assertion                  |  |  |

| 2   | 0, 1, 0         | TSD control 2      | At TSD event, shut down only motor driver part, DC-DC keep ON, keep setup register values, motor shutdown released by nSLEEP = L, nORT assertion: 40-ms single pulse |  |  |