ZHCS034 – MARCH 2011

TCA4311A

# 可热插拔型双线式总线缓冲器 查询样品: TCA4311A

#### 特性

- 工作电源电压范围: 2.7V 至 5.5V

- 支持 I<sup>2</sup>C 总线信号的双向数据传输

- 对 SDA 及 SCL 线路进行了缓冲,因而增加了扇出数

- 在所有的 SDA 及 SCL 线路上均进行了 1V 预充 电,可防止在背板上进行带电电路板的插拔操作时 发生损坏

- SDA 及 SCL 输入线路与输出隔离

- 可适应标准模式及快速模式 I<sup>2</sup>C 器件

- 抗噪声性能有所改善

- 其应用包括带电电路板插入及总线扩展

- 低 Icc 芯片停用模式: <1µA

- **READY** 开漏输出

- 支持时钟展宽、仲裁及同步

- 断电高阻抗 I<sup>2</sup>C 引脚

- 开漏 I<sup>2</sup>C 引脚

- 闭锁性能超过 100mA,符合 JESD 78 Class II 标 准

- ESD 保护等级超过了 JESD 22 规范

- 8000V 人体模型 (A114-A)

- 200V 机器模型 (A115-A)

- 1000V 充电器件模型 (C101)

### 说明/订购信息

$\overline{M}$

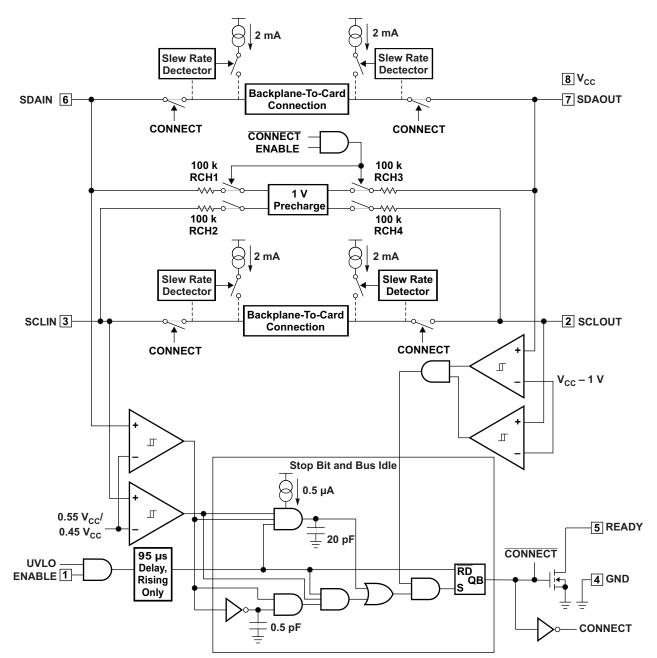

TCA4311A 是一款可热插拔型 I<sup>2</sup>C 总线缓冲器,支持在带电背板上进行 I/O 板卡的插拔操作,而不会损坏数据和时 钟总线。 控制电路可防止背板与板卡相连接(直到背板上出现停止命令或总线空闲为止),而不会在板卡上发生总 线争用的情况。 当建立连接时,该器件可提供双向缓冲,从而使背板及板卡电容保持隔离。 在板卡插入过程 中,SDA 及 SCL 线路被预充电至 1V,以最大限度地减小对芯片的寄生电容进行充电所需的电流。

当 I<sup>2</sup>C 总线空闲时,可通过将EN引脚设定为低电平来把 TCA4311A 置于停机模式之中。 当 EN 引脚为高电平时,TCA4311 将恢复正常运作。 该器件还包括一个开漏 READY 输出引脚,该引脚负责在背板与板卡侧相连时发出指示信号。 当 READY 引脚为高电平时,SDAIN 和 SCLIN 被连接至 SDAOUT 和 SCLOUT。 当两侧断接时,READY 引脚为低电平。

背板及板卡均可采用 2.7V 至 5.5V 的电源电压来供电,而对于它们哪一个的电源电压较高则未做限制。

TCA4311 具有标准的开漏 I/O。 至 I/O 的上拉电阻器的大小取决于系统,不过,该缓冲器的每一侧均必须设有一个 上拉电阻器。 这款器件专为与标准模式及快速模式 I<sup>2</sup>C 器件(而不单是 SMBus 器件)一起工作而设计。 在可以 接受标准模式器件和多个主控器的通用型 I<sup>2</sup>C 系统中,标准模式 I<sup>2</sup>C 器件只规定了 3mA。 在某些条件下,可以采 用高终端电流。

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

# TCA4311A

#### ZHCS034-MARCH 2011

**PIN NUMBER**

1

#### Table 1. ORDERING INFORMATION

| T <sub>A</sub> | PACKAGE <sup>(1)</sup> <sup>(2)</sup> |               | ORDERABLE PART NUMBER | TOP-SIDE MARKING |  |

|----------------|---------------------------------------|---------------|-----------------------|------------------|--|

| -40°C to 85°C  |                                       | Tube          | TCA4311AD             | PREVIEW          |  |

|                | SOIC – D                              | Tape and reel | TCA4311ADR            | PREVIEW          |  |

|                | MSOP – DGK                            | Tape and reel | TCA4311ADGKR          | 6KS              |  |

(1) Package drawings, thermal data, and symbolization are available at www.ti.com/packaging.

(2) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI website at www.ti.com.

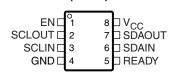

#### SOIC (D) OR MSOP (DGK) PACKAGE DESCRIPTION NAME Active-high chip enable pin. If EN is low, the TCA4311A is in a low current (<1 µA) mode. It also disables the rise-time accelerators, disables the bus precharge circuitry, drives READY low, isolates SDAIN from SDAOUT and isolates SCLIN from SCLOUT. EN should be high (at $V_{CC}$ ) for normal ΕN operation. Connect EN to $V_{\mbox{\scriptsize CC}}$ if this feature is not being used. ial ala al et this nin to the SCL h ~ .+ C . +h

| 2 | SCLOUT          | Serial clock output. Connect this pin to the SCL bus on the card.                                                                                                                                                                                                                                                             |  |

|---|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3 | SCLIN           | Serial clock input. Connect this pin to the SCL bus on the backplane.                                                                                                                                                                                                                                                         |  |

| 4 | GND             | Supply ground                                                                                                                                                                                                                                                                                                                 |  |

| 5 | READY           | Connection flag/rise-time accelerator control. READY is low when either EN is low or the start-up sequence described in the operation section has not been completed. READY goes high when EN is high and start-up is complete. Connect a $10$ -k $\Omega$ resistor from this pin to V <sub>CC</sub> to provide the pull up.  |  |

| 6 | SDAIN           | Serial data input. Connect this pin to the SDA bus on the backplane.                                                                                                                                                                                                                                                          |  |

| 7 | SDAOUT          | Serial data output. Connect this pin to the SDA bus on the card.                                                                                                                                                                                                                                                              |  |

| 8 | V <sub>CC</sub> | Supply power. Main input power supply from backplane. This is the supply voltage for the devices on the backplane I <sup>2</sup> C busses. Connect pullup resistors from SDAIN and SCLIN (and also from SDAOUT and SCLOUT) to this pin. Place a bypass capacitor of at least 0.01 $\mu$ F close to this pin for best results. |  |

Hoc uct old r Link(s TCA4211A

**TERMINAL FUNCTIONS**

Submit Documentation Feedback

2

AS TRUMENTS

www.ti.com.cn

Copyright © 2011, Texas Instruments Incorporated

ZHCS034-MARCH 2011

www.ti.com.cn

#### **BLOCK DIAGRAM**

2-Wire Bus Buffer and Hot Swap Controller

3

#### ZHCS034-MARCH 2011

### **ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>**

over operating free-air temperature range (unless otherwise noted)

|                  |                                                   |                              | MIN  | MAX  | UNIT |  |

|------------------|---------------------------------------------------|------------------------------|------|------|------|--|

| V <sub>CC</sub>  | Supply voltage range                              |                              | -0.5 | 7    | V    |  |

| V <sub>I/O</sub> | I <sup>2</sup> C bus voltage range <sup>(2)</sup> | SDAIN, SCLIN, SDAOUT, SCLOUT | -0.3 | 7    | V    |  |

| VI               | Input voltage range <sup>(2)</sup>                | EN                           | -0.3 | 7    | V    |  |

| I <sub>IK</sub>  | Input clamp current                               | V <sub>1</sub> < 0           |      | -50  | mA   |  |

| I <sub>OK</sub>  | Output clamp current                              | V <sub>O</sub> < 0           |      | -50  | mA   |  |

| lo               | Continuous output current                         |                              |      | ±50  | mA   |  |

| I <sub>CC</sub>  | Continuous current through V <sub>CC</sub> or GND |                              |      | ±100 | mA   |  |

| 0                | De alva sa tharrad ian a dan as (3)               | D package                    |      | 97   | °044 |  |

| $\theta_{JA}$    | Package thermal impedance <sup>(3)</sup>          | DGK package                  |      | 172  | °C/W |  |

| T <sub>stg</sub> | Storage temperature range                         |                              | -65  | 150  | °C   |  |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) The input negative-voltage and output voltage ratings may be exceeded if the input and output current ratings are observed.

(3) The package thermal impedance is calculated in accordance with JESD 51-7.

#### **RECOMMENDED OPERATING CONDITIONS**

|                 |                                  |                                                      | MIN                   | MAX                 | UNIT |

|-----------------|----------------------------------|------------------------------------------------------|-----------------------|---------------------|------|

| V <sub>CC</sub> | Supply voltage                   |                                                      | 2.7                   | 5.5                 | V    |

| V               | Lligh lovel input veltage        | SDA and SCL inputs                                   | 0.7 × V <sub>CC</sub> | 5.5                 | V    |

| V <sub>IH</sub> | High-level input voltage         | EN input                                             | 2                     | 5.5                 |      |

| V               |                                  | SDA and SCL inputs                                   | -0.5                  | $0.3 \times V_{CC}$ | V    |

| VIL             | Low-level input voltage          | EN input                                             | -0.5                  | 0.8                 |      |

|                 |                                  | butput current $\frac{V_{CC} = 3 V}{V_{CC} = 4.5 V}$ |                       | 3                   | ~ ^  |

| IOL             | Low-level output current         |                                                      |                       | 3                   | mA   |

| T <sub>A</sub>  | A Operating free-air temperature |                                                      | -40                   | 85                  | °C   |

ZHCS034-MARCH 2011

www.ti.com.cn

## ELECTRICAL CHARACTERISTICS

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                          | TEST CONDITIONS                                                                            | MIN                   | TYP                 | MAX                   | UNIT |

|-----------------------|------------------------------------|--------------------------------------------------------------------------------------------|-----------------------|---------------------|-----------------------|------|

| Power Sup             | oply                               |                                                                                            |                       |                     |                       |      |

| V <sub>CC</sub>       | Positive supply voltage            |                                                                                            | 2.7                   |                     | 5.5                   | V    |

| I <sub>CC</sub>       | Supply current                     | $V_{CC} = 5.5 \text{ V}, \text{ V}_{\text{SDAIN}} = \text{V}_{\text{SCLIN}} = 0 \text{ V}$ |                       | 5.1                 | 7                     | mA   |

| I <sub>SD</sub>       | Supply current in shutdown mode    | V <sub>EN</sub> = 0 V                                                                      |                       | 0.1                 |                       | μA   |

| Start-Up C            | ircuitry                           | ·                                                                                          |                       |                     |                       |      |

| V <sub>PRE</sub>      | Precharge voltage                  | SDA, SCL floating                                                                          | 0.8                   | 1                   | 1.2                   | V    |

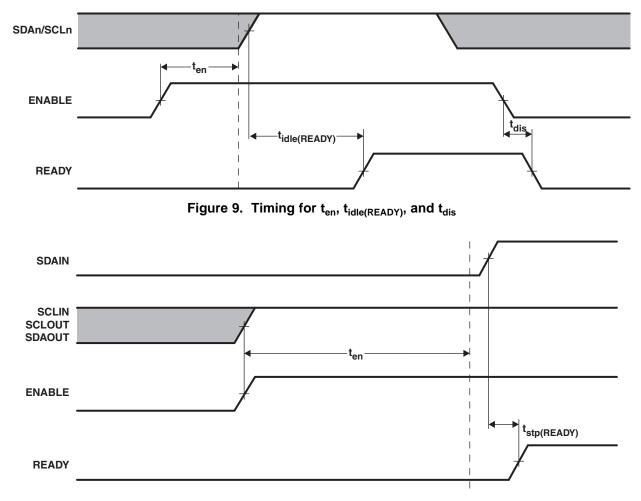

| t <sub>IDLE</sub>     | Bus idle time                      |                                                                                            | 50                    | 95                  | 150                   | μs   |

| V <sub>EN</sub>       | EN threshold voltage               |                                                                                            |                       | $0.5 \times V_{CC}$ | 0.9 × V <sub>CC</sub> | V    |

| V <sub>DIS</sub>      | Disable threshold voltage          | EN Pin                                                                                     | 0.1 × V <sub>CC</sub> | $0.5 \times V_{CC}$ |                       | V    |

| I <sub>EN</sub>       | EN input current                   | EN from 0 V to V <sub>CC</sub>                                                             |                       | ±0.1                | ±1                    | μA   |

| t <sub>EN</sub>       | Enable time                        |                                                                                            |                       | 95                  |                       | μs   |

| t <sub>DIS</sub>      | Disable time (EN to<br>READY)      |                                                                                            |                       | 30                  |                       | ns   |

| t <sub>STOP</sub>     | SDAIN to READY delay<br>after STOP |                                                                                            |                       | 1.2                 |                       | μs   |

| t <sub>READY</sub>    | SCLOUT/SDAOUT to<br>READY          |                                                                                            |                       | 0.8                 |                       | μs   |

| I <sub>OFF</sub>      | READY OFF state leakage<br>current |                                                                                            |                       | ±0.1                |                       | μA   |

| V <sub>OL</sub>       | READY output low voltage           | I <sub>PULLUP</sub> = 3 mA                                                                 |                       |                     | 0.4                   | V    |

| <b>Rise-Time</b>      | Accelerators                       |                                                                                            |                       |                     |                       |      |

| I <sub>PULLUPAC</sub> | Transient boosted pull-up current  | Positive transition on SDA, SCL, $V_{CC}$ = 2.7 V,                                         | 1                     | 2                   |                       | mA   |

| Input-Outp            | out Connection                     |                                                                                            |                       |                     |                       |      |

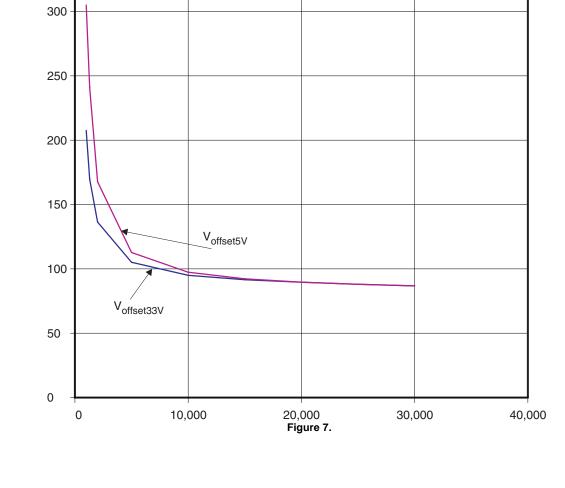

| V <sub>OS</sub>       | Input-output offset voltage        | 10 k $\Omega$ to V <sub>CC</sub> on SDA, SCL, V <sub>CC</sub> = 3.3 V, <sup>(1)</sup>      | 0                     | 100                 | 175                   | mV   |

| C <sub>IN</sub>       | Digital input capacitance          |                                                                                            |                       |                     | 10                    | pF   |

| V <sub>OL</sub>       | Output low voltage, input = 0 V    | SDA, SCL pins, I <sub>SINK</sub> = 3 mA,                                                   | 0                     |                     | 0.4                   | V    |

| l <sub>l</sub>        | Input leakage current              | SDA, SCL pins = $V_{CC}$ = 5.5 V                                                           |                       |                     | ±5                    | μA   |

(1) The connection circuitry always regulates its output to a higher voltage than its input. The magnitude of this offset voltage as a function of the pullup resistor and V<sub>CC</sub> voltage is shown in the Typical Performance Characteristics section.

Copyright © 2011, Texas Instruments Incorporated Bouch older Lirk (s TCA43 1140 11

5

### OPERATION

### Start-Up

When the TCA4311A first receives power on its  $V_{CC}$  pin, either during power-up or during live insertion, it starts in an undervoltage lockout (UVLO) state, ignoring any activity on the SDA and SCL pins until  $V_{CC}$  rises above 2.5 V.

During this time, the 1 V precharge circuitry is also active and forces 1 V through 100-k $\Omega$  nominal resistors to the SDA and SCL pins. Because the I/O card is being plugged into a live backplane, the voltage on the backplane SDA and SCL busses may be anywhere between 0 V and V<sub>CC</sub>. Precharging the SCL and SDA pins to 1 V minimizes the worst-case voltage differential these pins will see at the moment of connection, therefore minimizing the amount of disturbance caused by the I/O card.

Once the TCA4311A comes out of UVLO, it assumes that SDAIN and SCLIN have been inserted into a live system and that SDAOUT and SCLOUT are being powered up at the same time as itself. Therefore, it looks for either a stop bit or bus idle condition on the backplane side to indicate the completion of a data transaction. When either one occurs, the part also verifies that both the SDAOUT and SCLOUT voltages are high. When all of these conditions are met, the input-to-output connection circuitry is activated, joining the SDA and SCL busses on the I/O card with those on the backplane, and the rise time accelerators are enabled.

#### **Connection Circuitry**

Once the connection circuitry is activated, the functionality of the SDAIN and SDAOUT pins is identical. A low forced on either pin at any time results in both pin voltages being low. For proper operation, logic low input voltages should be no higher than 0.4 V with respect to the ground pin voltage of the TCA4311A. SDAIN and SDAOUT enter a logic high state only when all devices on both SDAIN and SDAOUT release high. The same is true for SCLIN and SCLOUT. This important feature ensures that clock stretching, clock synchronization, arbitration and the acknowledge protocol always work, regardless of how the devices in the system are tied to the TCA4311A.

Another key feature of the connection circuitry is that it provides bidirectional buffering, keeping the backplane and card capacitances isolated. Because of this isolation, the waveforms on the backplane busses look slightly different than the corresponding card bus waveforms, as described here.

#### Input to Output Offset Voltage

When a logic low voltage,  $V_{LOW1}$ , is driven on any of the TCA4311A's data or clock pins, the TCA4311A regulates the voltage on the other side of the chip (call it  $V_{LOW2}$ ) to a slightly higher voltage, as directed by the following equation:

#### $V_{LOW2} = V_{LOW1} + 75 \text{ mV} + (V_{CC}/R) \times 100$

where R is the bus pullup resistance in ohms ( $\Omega$ ). For example, if a device is forcing SDAOUT to 10 mV where  $V_{CC} = 3.3$  V and the pullup resistor R on SDAIN is 10 k $\Omega$ , then the voltage on SDAIN = 10 + 75 + (3.3/10000) × 100 = 118 mV. See the *Typical Performance Characteristics* section for curves showing the offset voltage as a function of  $V_{CC}$  and R.

#### **Propagation Delays**

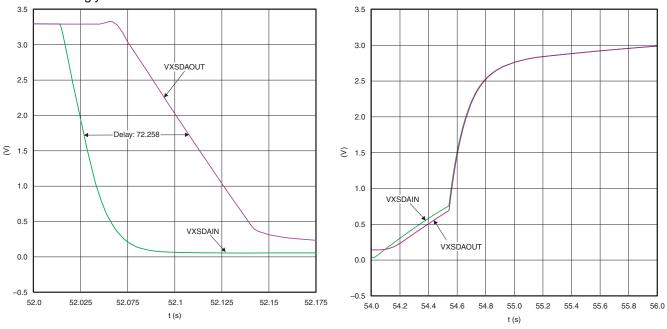

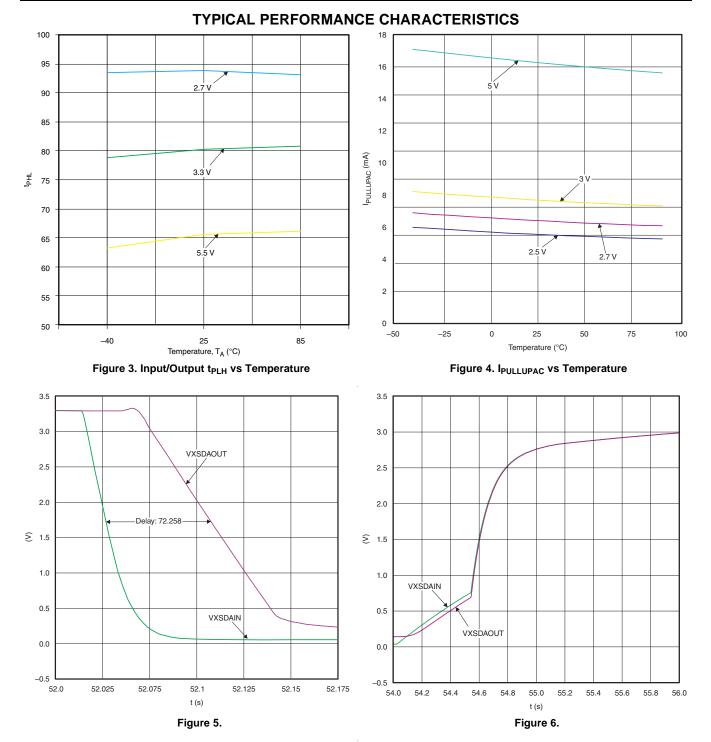

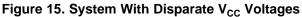

During a rising edge, the rise-time on each side is determined by the combined pullup current of the TCA4311A boost current and the bus resistor and the equivalent capacitance on the line. If the pullup currents are the same, a difference in rise-time occurs which is directly proportional to the difference in capacitance between the two sides. This effect is displayed in Figure 1 for  $V_{CC} = 3.3$  V and a 10-k $\Omega$  pullup resistor on each side (50 pF on one side and 150 pF on the other). Since the output side has less capacitance than the input, it rises faster and the effective  $t_{PLH}$  is negative.

There is a finite propagation delay,  $t_{PHL}$ , through the connection circuitry for falling waveforms. Figure 2 shows the falling edge waveforms for the same V<sub>CC</sub>, pullup resistors and equivalent capacitance conditions as used in Figure 1. An external NMOS device pulls down the voltage on the side with 150 pF capacitance; the TCA4311A pulls down the voltage on the opposite side, with a delay of 55 ns. This delay is always positive and is a function of supply voltage, temperature and the pullup resistors and equivalent bus capacitances on both sides of the bus. The *Typical Performance Characteristics* section shows  $t_{PHL}$  as a function of temperature and voltage for

#### ZHCS034 - MARCH 2011

10-k $\Omega$  pullup resistors and 100 pF equivalent capacitance on both sides of the part. By comparison with Figure 2, the V<sub>CC</sub> = 3.3 V curve shows that increasing the capacitance from 50 pF to 100 pF results in a t<sub>PHL</sub> increase from 55 ns to 75 ns. Larger output capacitances translate to longer delays (up to 150 ns). Users must quantify the difference in propagation times for a rising edge versus a falling edge in their systems and adjust setup and hold times accordingly.

Figure 2. Input-Output Connection t<sub>PHL</sub>

#### **Rise-Time Accelerators**

Once connection has been established, rise-time accelerator circuits on all four SDA and SCL pins are activated. These allow the user to choose weaker DC pullup currents on the bus, reducing power consumption while still meeting system rise-time requirements. During positive bus transitions, the TCA4311A switches in 2 mA (typical) of current to quickly slew the SDA and SCL lines once their DC voltages exceed 0.6 V. Using a general rule of 20 pF of capacitance for every device on the bus (10 pF for the device and 10 pF for interconnect), choose a pullup current so that the bus will rise on its own at a rate of at least 1.25 V/µs to guarantee activation of the accelerators.

For example, assume an SMBus system with  $V_{CC} = 3 \text{ V}$ , a 10-k $\Omega$  pullup resistor and equivalent bus capacitance of 200 pF. The rise-time of an SMBus system is calculated from ( $V_{IL(MAX)} - 0.15 \text{ V}$ ) to ( $V_{IH(MIN)} + 0.15 \text{ V}$ ), or 0.65 V to 2.25 V. It takes an RC circuit 0.92 time constants to traverse this voltage for a 3 V supply; in this case, 0.92 × (10 k $\Omega$  × 200 pF) = 1.84 µs. Thus, the system exceeds the maximum allowed rise-time of 1 µs by 84%. However, using the rise-time accelerators, which are activated at a DC threshold of below 0.65 V, the worst-case rise-time is: (2.25 V – 0.65 V) × 200 pF/1 mA = 320 ns, which meets the 1 µs rise-time requirement.

#### **READY Digital Output**

This pin provides a digital flag which is low when either EN is low or the start-up sequence described earlier in this section has not been completed. READY goes high when EN is high and start-up is complete. The pin is driven by an open drain pull-down capable of sinking 3 mA while holding 0.4 V on the pin. Connect a resistor of 10 k $\Omega$  to V<sub>CC</sub> to provide the pullup.

#### **EN Low Current Disable**

Grounding the EN pin disconnects the backplane side from the card side, disables the rise-time accelerators, drives READY low, disables the bus precharge circuitry and puts the part in a near-zero current state. When the pin voltage is driven all the way to  $V_{CC}$ , the part waits for data transactions on both the backplane and card sides to be complete (as described in the Start-Up section) before reconnecting the two sides.

For uct old r Ling(s. TCA4311A

Copyright © 2011, Texas Instruments Incorporated

#### ZHCS034 – MARCH 2011

#### **Resistor Pull-Up Value Selection**

The system pullup resistors must be strong enough to provide a positive slew rate of 1.25 V/ $\mu$ s on the SDA and SCL pins, in order to activate the boost pullup currents during rising edges. Choose maximum resistor value R using the formula:

$R \le (V_{CC(MIN)} - 0.6) (800,000) / C$

where R is the pullup resistor value in ohms,  $V_{CC(MIN)}$  is the minimum  $V_{CC}$  voltage and C is the equivalent bus capacitance in picofarads (pF).

In addition, regardless of the bus capacitance, always choose R  $\leq$  16 k $\Omega$  for V<sub>CC</sub> = 5.5 V maximum, R  $\leq$  24 k $\Omega$  for V<sub>CC</sub> = 3.6 V maximum. The start-up circuitry requires logic high voltages on SDAOUT and SCLOUT to connect the backplane to the card, and these pullup values are needed to overcome the precharge voltage.

#### Systems With Disparate Supply Voltages

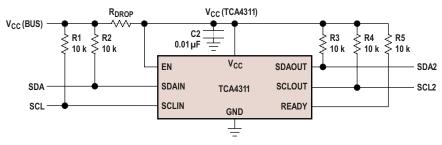

In large 2-wire systems, the V<sub>CC</sub> voltages seen by devices at various points in the system can differ by a few hundred millivolts or more. This situation is well modeled by a series resistor in the V<sub>CC</sub> line, as shown in Figure 15. For proper operation of the TCA4311A, make sure that  $V_{CC(BUS)} \ge V_{CC(TCA4311A)} - 0.5$  V.

Focuet old r Lir (s. TCA43 (1A

# TCA4311A

ZHCS034 - MARCH 2011

Copyright © 2011, Texas Instruments Incorporated Boout old r Lir (Is TCA4211AO 1)

Submit Decumentation Feedback

9

Bout older Lir (S TCA4311AO

**TYPICAL PERFORMANCE CHARACTERISTICS (continued)**

#### ZHCS034 - MARCH 2011

TCA4311A

350

www.ti.com.cn

**NSTRUMENTS**

**EXAS**

# TCA4311A

www.ti.com.cn

#### ZHCS034 - MARCH 2011

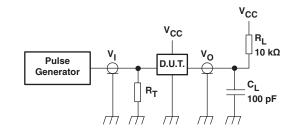

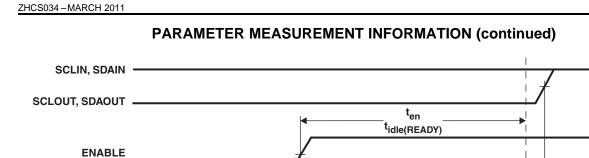

### PARAMETER MEASUREMENT INFORMATION

R<sub>L</sub> = Load resistor

$C_L$  = Load capacitance includes jig and probe capacitance

$R_T$  = Termination resistance should be equal to the output impedance  $Z_0$  of the pulse generators.

#### Figure 8. Test Circuitry for Switching Times

Figure 10. t<sub>stp(READY)</sub> That Can Occur After t<sub>en</sub>

Frocuct, old in Lin ((s. TCA43 114

TEXAS INSTRUMENTS

www.ti.com.cn

READY

Figure 11.  $t_{stp(READY)}$  That Can Occur After  $t_{en}$  and  $t_{idle(READY)}$

Focuet older Link(s TCA4311A

#### **APPLICATION INFORMATION**

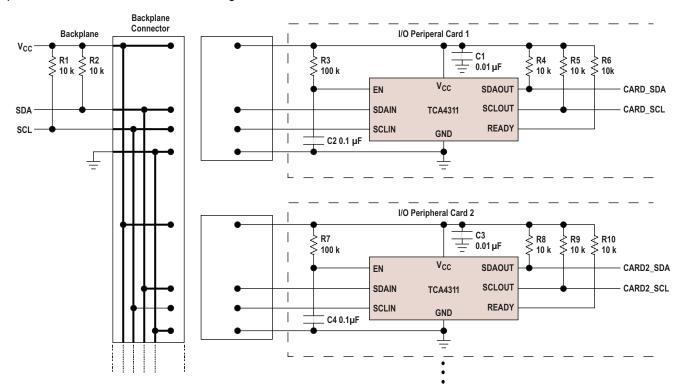

#### Live Insertion and Capacitance Buffering Application

Figure 12 through Figure 13 illustrate the usage of the TCA4311A in applications that take advantage of both its hot swap controlling and capacitance buffering features. In all of these applications, note that if the I/O cards were plugged directly into the backplane, all of the backplane and card capacitances would add directly together, making rise- and fall-time requirements difficult to meet. Placing a TCA4311A on the edge of each card, however, isolates the card capacitance from the backplane. For a given I/O card, the TCA4311A drives the capacitance of everything on the card and the backplane must drive only the capacitance of the TCA4311A, which is less than 10 pF.

Figure 12 shows the TCA4311A in a CompactPCI<sup>™</sup> configuration. Connect V<sub>CC</sub> and EN to the output of one of the CompactPCI power supply Hot Swap circuits. Use a pullup resistor to EN for a card side enable/disable.

$V_{CC}$  is monitored by a filtered UVLO circuit. With the  $V_{CC}$  voltage powering up after all other pins have established connection, the UVLO circuit ensures that the backplane and card data and clock busses are not connected until the transients associated with live insertion have settled. Owing to their small capacitance, the SDAIN and SCLIN pins cause minimal disturbance on the backplane busses when they make contact with the connector.

Figure 12. Inserting Multiple I/O Cards into a Live Backplane Using the TCA4311A in a CompactPCI System

Froquet, old r Link(st TCA4311A

TEXAS INSTRUMENTS

#### ZHCS034-MARCH 2011

www.ti.com.cn

Figure 13 shows the TCA4311A in a PCI application, where all of the pins have the same length. In this case, connect an RC series circuit on the I/O card between  $V_{CC}$  and EN. An RC product of 10 ms provides a filter to prevent the TCA4311A from becoming activated until the transients associated with live insertion have settled.

#### Figure 13. Inserting Multiple I/O Cards into a Live Backplane Using the TCA4311A in a PCI System

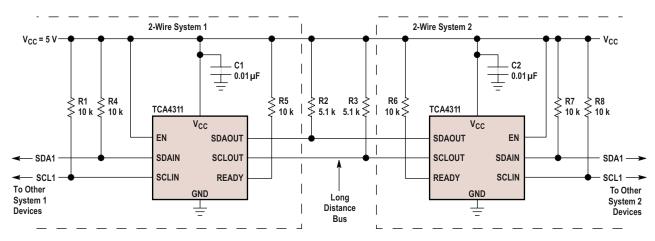

#### **Repeater/Bus Extender Application**

Users who wish to connect two 2-wire systems separated by a distance can do so by connecting two TCA4311A back-to-back, as shown in Figure 14. The I<sup>2</sup>C specification allows for 400 pF maximum bus capacitance, severely limiting the length of the bus. The SMBus specification places no restriction on bus capacitance, but the limited impedances of devices connected to the bus require systems to remain small if rise- and fall-time specifications are to be met. The strong pullup and pulldown impedances of the TCA4311A are capable of meeting rise- and fall-time specifications for one nanofarad of capacitance, thus allowing much more interconnect distance. In this situation, the differential ground voltage between the two systems may limit the allowed distance, because a valid logic low voltage with respect to the ground at one end of the system may violate the allowed  $V_{OL}$  specification with respect to the ground at the other end. In addition, the connection circuitry offset voltages of the back-to-back TCA4311A add together, directly contributing to the same problem.

Focuct old r Lir (s TCA43 11A

Copyright © 2011, Texas Instruments Incorporated

# TCA4311A

#### www.ti.com.cn

ZHCS034 - MARCH 2011

15

#### 重要声明

德州仪器 (TI)及其下属子公司有权在不事先通知的情况下,随时对所提供的产品和服务进行更正、修改、增强、改进或其它更改,并有权随时中止提供任何产品和服务。客户在下订单前应获取最新的相关信息,并验证这些信息是否完整且是最新的。所有产品的销售都遵循在订单确认时所提供的 TI 销售条款与条件。

TI 保证其所销售的硬件产品的性能符合 TI 标准保修的适用规范。 仅在 TI 保修的范围内,且 TI 认为有必要时才会使用测试或其它质量控制技术。 除非政府做出了硬性规定,否则没有必要对每种产品的所有参数进行测试。

TI 对应用帮助或客户产品设计不承担任何义务。客户应对其使用 TI 组件的产品和应用自行负责。为尽量减小与客户产品和应用相关的风险,客户应提供充分的设计与操作安全措施。

TI 不对任何 TI 专利权、版权、屏蔽作品权或其它与使用了 TI 产品或服务的组合设备、机器、流程相关的 TI 知识产权中授予的直接 或隐含权限作出任何保证或解释。TI 所发布的与第三方产品或服务有关的信息,不能构成从 TI 获得使用这些产品或服务的许可、授 权、或认可。使用此类信息可能需要获得第三方的专利权或其它知识产权方面的许可,或是 TI 的专利权或其它知识产权方面的许 可。

对于 TI 的数据手册或数据表,仅在没有对内容进行任何篡改且带有相关授权、条件、限制和声明的情况下才允许进行复制。在复制信息的过程中对内容的篡改属于非法的、欺诈性商业行为。 TI 对此类篡改过的文件不承担任何责任。

在转售 TI 产品或服务时,如果存在对产品或服务参数的虚假陈述,则会失去相关 TI 产品或服务的明示或暗示授权,且这是非法的、 欺诈性商业行为。 TI 对此类虚假陈述不承担任何责任。

可访问以下 URL 地址以获取有关其它 TI 产品和应用解决方案的信息:

产品

| 放大器   | http://www.ti.com.cn/amplifiers       |

|-------|---------------------------------------|

| 数据转换器 | http://www.ti.com.cn/dataconverters   |

| DSP   | http://www.ti.com.cn/dsp              |

| 接口    | http://www.ti.com.cn/interface        |

| 逻辑    | http://www.ti.com.cn/logic            |

| 电源管理  | http://www.ti.com.cn/power            |

| 微控制器  | http://www.ti.com.cn/microcontrollers |

| 应用    |                                       |

| 音频    | http://www.ti.com.cn/audio            |

| 汽车    | http://www.ti.com.cn/automotive       |

| 宽带    | http://www.ti.com.cn/broadband        |

| 数字控制  | http://www.ti.com.cn/control          |

| 光纤网络  | http://www.ti.com.cn/opticalnetwork   |

| 安全    | http://www.ti.com.cn/security         |

| 电话    | http://www.ti.com.cn/telecom          |

| 视频与成像 | http://www.ti.com.cn/video            |

| 无线    | http://www.ti.com.cn/wireless         |

|       |                                       |

邮寄地址: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2006, Texas Instruments Incorporated

# www.BDTIC.com/TI