## TPS40303, TPS40304, TPS40305

SLUS964 -NOVEMBER 2009

## 3-V TO 20-V INPUT SYNCHRONOUS BUCK CONTROLLER

Check for Samples : TPS40303 TPS40304 TPS40305

#### **FEATURES**

- Input Voltage Range from 3 V to 20 V

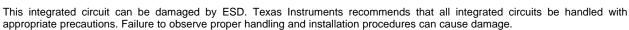

- 300 KHz (TPS40303), 600 KHz (TPS40304) and 1.2 MHz (TPS40305) Switching Frequencies

- High- and Low-Side FET R<sub>DS(on)</sub> Current • Sensing

- Programmable Thermally Compensated OCP Levels

- **Programmable Soft-Start**

- 600 mV, 1% Reference Voltage

- Voltage Feed-Forward Compensation

- **Supports Pre-Biased Output**

- **Frequency Spread Spectrum**

- Thermal Shutdown Protection at 145°C

- 10-Pin 3 mm × 3 mm SON Package with **Ground Connection to Thermal Pad**

#### CONTENTS

| Device Ratings             | 2  |

|----------------------------|----|

| Electrical Characteristics | 3  |

| Device Information         | 8  |

| Application Information    | 10 |

| Design Examples            | 14 |

| Additional References      | 24 |

#### APPLICATIONS

- POL Modules

- Printer

- **Digital TV**

- Telecom

#### DESCRIPTION

The TPS4030x is a family of cost-optimized synchronous buck controllers that operate from 3-V to 20-V input. The controller implements a voltage-mode control architecture with input-voltage feed-forward compensation that responds instantly to input voltage change. The switching frequency is fixed at 300 KHz, 600 KHz or 1.2 MHz.

Frequency Spread Spectrum feature adds dither to the switching frequency, significantly reducing the peak EMI noise and making it much easier to comply with EMI standards.

The TPS4030x offers design with a variety of user programmable functions, including soft-start, Over- Current Protection (OCP) levels, and loop compensation.

OCP level may be programmed by a single external resistor connected from LDRV pin to circuit ground. During initial power on, the TPS4030x enters a calibration cycle, measures the voltage at the LDRV pin, and sets an internal OCP voltage level. During operation, the programmed OCP voltage level is compared to the voltage drop across the low side FET when it is on to determine whether there is an overcurrent condition. The TPS4030x then enters a shutdown and restart cycle until the fault is removed.

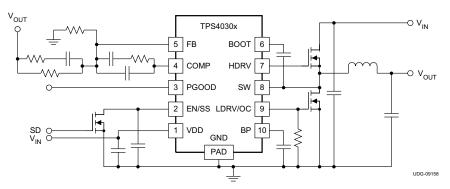

#### SIMPLIFIED APPLICATION DIAGRAM

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

SLUS964 -NOVEMBER 2009

18a

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

| OPERATING FREQUENCY | PACKAGE                  | TAPE AND REEL QUANTITY | PART NUMBER  |  |  |  |  |  |

|---------------------|--------------------------|------------------------|--------------|--|--|--|--|--|

| 1.2 MHz             | Plastic 10-Pin SON (DRC) | 250                    | TPS40305DRCT |  |  |  |  |  |

|                     |                          | 3000                   | TPS40305DRCR |  |  |  |  |  |

| 600 kHz             |                          | 250                    | TPS40304DRCT |  |  |  |  |  |

| 600 KH2             |                          | 3000                   | TPS40304DRCR |  |  |  |  |  |

| 300 kHz             |                          | 250                    | TPS40303DRCT |  |  |  |  |  |

|                     |                          | 3000                   | TPS40303DRCR |  |  |  |  |  |

#### **ORDERING INFORMATION**

#### ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                  |                                                         | VALUE      | UNIT |

|------------------|---------------------------------------------------------|------------|------|

|                  | VDD                                                     | -0.3 to 22 | V    |

|                  | SW                                                      | -3 to 27   | V    |

|                  | SW (< 100 ns pulse width, 10 μJ)                        | -5         | V    |

|                  | BOOT                                                    | -0.3 to 30 | V    |

|                  | HDRV                                                    | -5 to 30   | V    |

|                  | BOOT-SW, HDRV-SW (differential from BOOT or HDRV to SW) | -0.3 to 7  | V    |

|                  | COMP, PGOOD, FB, BP, LDRV, EN/SS                        | -0.3 to 7  | V    |

| $T_J$            | Operating junction temperature range                    | -40 to 145 | °C   |

| T <sub>stg</sub> | Storage temperature                                     | -55 to 150 | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other condition beyond those included under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods of time may affect device reliability.

#### **DISSIPATION RATINGS**

| PACKAGE          | AIRFLOW (LFM)          | R <sub>θJA</sub> HIGH-K BOARD <sup>(1)</sup><br>(°C/W) | POWER RATING (W)<br>T <sub>A</sub> = 25°C | POWER RATING (W)<br>T <sub>A</sub> = 85°C |

|------------------|------------------------|--------------------------------------------------------|-------------------------------------------|-------------------------------------------|

|                  | 0 (Natural Convection) | 47.9                                                   | 2.08                                      | 0.835                                     |

| 10-Pin SON (DRC) | 200                    | 40.5                                                   | 2.46                                      | 0.987                                     |

|                  | 400                    | 38.2                                                   | 2.61                                      | 1.04                                      |

Ratings based on JEDEC High Thermal Conductivity (High K) Board. For more information on the test method, see TI technical brief (SZZA017).

#### **RECOMMENDED OPERATING CONDITIONS**

|     |                                | MIN | NOM MAX | UNIT |

|-----|--------------------------------|-----|---------|------|

| VDD | Input voltage                  | 3   | 20      | V    |

| TJ  | Operating junction temperature | -40 | 125     | °C   |

#### **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

|                           | MIN | TYP  | MAX | UNIT |  |

|---------------------------|-----|------|-----|------|--|

| Human body model (HBM)    |     | 2000 |     | V    |  |

| Charge device model (CDM) |     | 1500 |     | V    |  |

uct Folo r link(): 7PS4(30 TPS4(304 T

2

Copyright © 2009 Texas Instruments Incorporated

www.ti.com

SLUS964 -NOVEMBER 2009

www.ti.com

#### **ELECTRICAL CHARACTERISTICS**

$T_J = -40^{\circ}$ C to 125°C,  $V_{VDD} = 12$  V, all parameters at zero power dissipation (unless otherwise noted)

|                                     | PARAMETER                           |                                    | TEST CONDITIONS                                              | MIN                   | TYP                 | MAX                   | UNIT            |

|-------------------------------------|-------------------------------------|------------------------------------|--------------------------------------------------------------|-----------------------|---------------------|-----------------------|-----------------|

| VOLTAGE F                           | REFERENCE                           |                                    |                                                              |                       |                     |                       |                 |

|                                     |                                     |                                    | T <sub>J</sub> = 25°C, 3 V < V <sub>VDD</sub> < 20 V         | 597                   | 600                 | 603                   |                 |

| V <sub>FB</sub>                     | FB input voltage                    |                                    | $-40^{\circ}C < T_J < 125^{\circ}C, 3 V < V_{VDD} < 20$<br>V | 594                   | 600                 | 606                   | mV              |

| INPUT SUP                           | PLY                                 |                                    |                                                              |                       |                     |                       |                 |

| V <sub>VDD</sub>                    | Input supply voltage range          |                                    |                                                              | 3                     |                     | 20                    | V               |

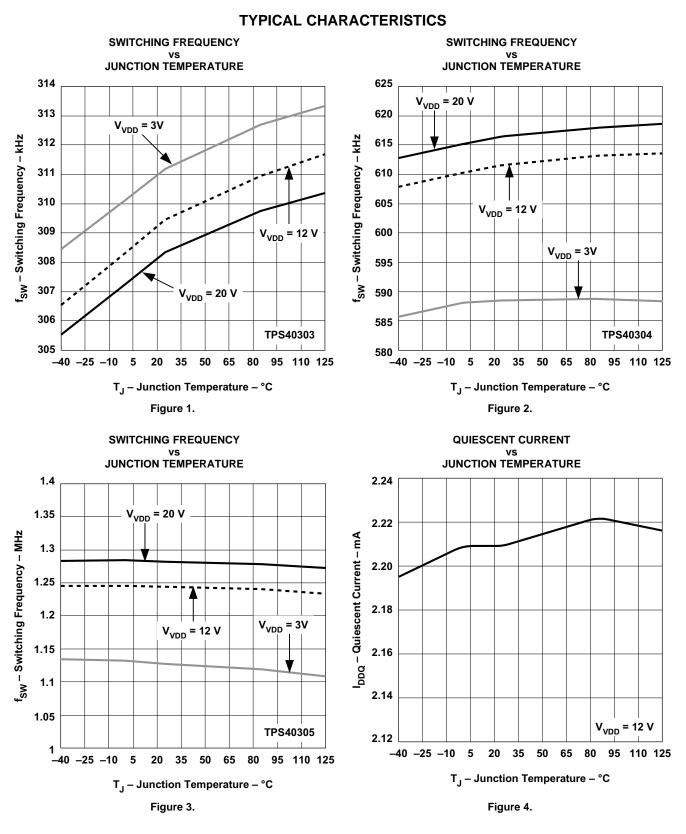

| IDD <sub>SD</sub>                   | Shutdown supply current             |                                    | V <sub>EN/SS</sub> < 0.2 V                                   |                       | 70                  | 100                   | μA              |

| IDD <sub>Q</sub>                    | Quiescent, non-switching            |                                    | Let EN/SS float, $V_{FB}$ = 1 V                              |                       | 2.5                 | 3.5                   | mA              |

| ENABLE/SC                           | OFT-START                           |                                    |                                                              |                       |                     |                       |                 |

| V <sub>IH</sub>                     | High-level input voltage, EN/       | 'SS                                |                                                              | 0.55                  | 0.70                | 1.00                  | V               |

| V <sub>IL</sub>                     | Low-level input voltage, EN/S       | SS                                 |                                                              | 0.27                  | 0.30                | 0.33                  | V               |

| I <sub>SS</sub>                     | Soft-start source current           |                                    |                                                              | 8                     | 10                  | 12                    | μA              |

| V <sub>SS</sub>                     | Soft-start voltage level            |                                    |                                                              | 0.4                   | 0.8                 | 1.3                   | V               |

| BP REGUL                            | ATOR                                |                                    |                                                              |                       |                     |                       |                 |

| V <sub>BP</sub>                     | Output voltage                      |                                    | I <sub>BP</sub> = 10 mA                                      | 6.2                   | 6.5                 | 6.8                   | V               |

| V <sub>DO</sub>                     | Regulator dropout voltage, V        | V <sub>VDD</sub> – V <sub>BP</sub> | $I_{BP} = 25 \text{ mA}, V_{VDD} = 3 \text{ V}$              |                       | 70                  | 110                   | mV              |

| OSCILLATO                           | )R                                  |                                    |                                                              |                       |                     |                       |                 |

|                                     |                                     | TPS40303                           |                                                              | 270                   | 300                 | 330                   | kHz             |

| f <sub>SW</sub>                     | PWM frequency                       | TPS40304                           | 3 V < V <sub>VDD</sub> < 20 V                                | 540                   | 600                 | 660                   | kHz             |

|                                     | •                                   | TPS40305                           |                                                              | 1.02                  | 1.20                | 1.38                  | MHz             |

| V <sub>RAMP</sub> <sup>(1)</sup>    | Ramp amplitude                      |                                    |                                                              | V <sub>VDD</sub> /6.6 | V <sub>VDD</sub> /6 | V <sub>VDD</sub> /5.4 | V               |

| f <sub>SWFSS</sub>                  | Frequency spread spectrum deviation | frequency                          |                                                              | 12%                   |                     |                       | f <sub>SW</sub> |

| f <sub>MOD</sub>                    | Modulation frequency                |                                    |                                                              |                       | 25                  |                       | KHz             |

| PWM                                 |                                     |                                    |                                                              |                       |                     |                       |                 |

|                                     |                                     | TPS40303                           |                                                              | 90%                   |                     |                       |                 |

| D <sub>MAX</sub> (1)                | Maximum duty cycle                  | TPS40304                           | $V_{FB} = 0 V, 3 V < V_{VDD} < 20 V$                         | 90%                   |                     |                       |                 |

|                                     | •                                   | TPS40305                           |                                                              | 85%                   |                     |                       |                 |

| t <sub>ON(min)</sub> <sup>(1)</sup> | Minimum controllable pulse          | width                              |                                                              |                       |                     | 100                   | ns              |

|                                     | Output driver dead time             |                                    | HDRV off to LDRV on                                          | 5                     | 25                  | 35                    | -               |

| t <sub>DEAD</sub>                   | Output driver dead time             |                                    | LDRV off to HDRV on                                          | 5                     | 25                  | 30                    | ns              |

| ERROR AM                            | PLIFIER                             |                                    |                                                              |                       |                     |                       |                 |

| G <sub>BWP</sub> <sup>(1)</sup>     | Gain bandwidth product              |                                    |                                                              | 10                    | 24                  |                       | MHz             |

| A <sub>OL</sub> <sup>(1)</sup>      | Open loop gain                      |                                    |                                                              | 60                    |                     |                       | dB              |

| I <sub>IB</sub>                     | Input bias current (current ou      | ut of FB pin)                      | V <sub>FB</sub> = 0.6 V                                      |                       |                     | 75                    | nA              |

| I <sub>EAOP</sub>                   | Output source current               |                                    | V <sub>FB</sub> = 0 V                                        | 2                     |                     |                       | ^               |

| I <sub>EAOM</sub>                   | Output sink current                 |                                    | V <sub>FB</sub> = 1 V                                        | 2                     |                     |                       | mA              |

eu Veruet Folo runk(): 7 254630 77546804 77 5 0 0

(1) Ensured by design. Not production tested.

Copyright © 2009, Texas Instruments Incorporated

SLUS964 -NOVEMBER 2009

www.ti.com

INSTRUMENTS

**FEXAS**

#### **ELECTRICAL CHARACTERISTICS (continued)**

$T_J = -40^{\circ}C$  to 125°C,  $V_{VDD} = 12$  V, all parameters at zero power dissipation (unless otherwise noted)

|                                       | PARAMETER                                                          | TEST CONDITIONS                                                       | MIN  | TYP  | MAX  | UNIT  |

|---------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------|------|------|------|-------|

| PGOOD                                 |                                                                    | · · · · ·                                                             |      |      |      |       |

| V <sub>OV</sub>                       | Feedback upper voltage limit for PGOOD                             |                                                                       | 655  | 675  | 700  |       |

| V <sub>UV</sub>                       | Feedback lower voltage limit for<br>PGOOD                          |                                                                       | 500  | 525  | 550  | mV    |

| V <sub>PGD-HYST</sub>                 | PGOOD hysteresis voltage at FB                                     |                                                                       |      | 25   | 40   |       |

| R <sub>PGD</sub>                      | PGOOD pull down resistance                                         | $V_{FB} = 0 V$ , $I_{FB} = 5 mA$                                      |      | 30   | 70   | Ω     |

| I <sub>PGDLK</sub>                    | PGOOD leakage current                                              | 550 mV < V <sub>FB</sub> < 655 mV, $V_{PGOOD} = 5 V$                  |      | 10   | 20   | μA    |

| OUTPUT DR                             | IVERS                                                              |                                                                       |      |      |      |       |

| R <sub>HDHI</sub>                     | High-side driver pull-up resistance                                | $V_{BOOT} - V_{SW} = 5 \text{ V}, \text{ I}_{HDRV} = -100 \text{ mA}$ | 0.8  | 1.5  | 2.5  | Ω     |

| R <sub>HDLO</sub>                     | High-side driver pull-down resistance                              | $V_{BOOT} - V_{SW} = 5 \text{ V}, \text{ I}_{HDRV} = 100 \text{ mA}$  | 0.5  | 1.0  | 2.2  | Ω     |

| R <sub>LDHI</sub>                     | Low-side driver pull-up resistance                                 | I <sub>LDRV</sub> = -100 mA                                           | 0.8  | 1.5  | 2.5  | Ω     |

| R <sub>LDLO</sub>                     | Low-side driver pull-down resistance                               | I <sub>LDRV</sub> = 100 mA                                            | 0.35 | 0.60 | 1.20 | Ω     |

| t <sub>HRISE</sub> <sup>(2)</sup>     | High-side driver rise time                                         | C <sub>LOAD</sub> = 5 nF                                              |      | 15   |      | ns    |

| t <sub>HFALL</sub> <sup>(2)</sup>     | High-side driver fall time                                         |                                                                       |      | 12   |      | ns    |

| t <sub>LRISE</sub> (2)                | Low-side driver rise time                                          |                                                                       |      | 15   |      | ns    |

| t <sub>LFALL</sub> <sup>(2)</sup>     | Low-side driver fall time                                          |                                                                       |      | 10   |      | ns    |

| OVERCURRE                             | ENT PROTECTION                                                     |                                                                       |      |      |      |       |

| t <sub>PSSC(min)</sub> <sup>(2)</sup> | Minimum pulse time during short circuit                            |                                                                       |      | 250  |      | ns    |

| t <sub>BLNKH</sub> <sup>(2)</sup>     | Switch leading-edge blanking pulse time                            |                                                                       |      | 150  |      | ns    |

| V <sub>OCH</sub>                      | OC threshold for high side FET                                     | $T_J = 25^{\circ}C$                                                   | 360  | 450  | 580  | mV    |

| IOCSET                                | OCSET current source                                               | $T_J = 25^{\circ}C$                                                   | 9.5  | 10.0 | 10.5 | μA    |

| V <sub>LD-CLAMP</sub>                 | Maximum clamp voltage at LDRV                                      |                                                                       | 260  | 340  | 400  | mV    |

| V <sub>OCLOS</sub>                    | OC comparator offset voltage for low side FET                      | $T_J = 25^{\circ}C$                                                   | -8   |      | 8    | mV    |

| V <sub>OCLPRO</sub> <sup>(2)</sup>    | Programmable OC range for low side FET                             | $T_J = 25^{\circ}C$                                                   | 12   |      | 300  | mV    |

| V <sub>THTC</sub> <sup>(2)</sup>      | OC threshold temperature coefficient (both high side and low side) |                                                                       |      | 3000 |      | ppm   |

| t <sub>OFF</sub>                      | OC retry cycles on EN/SS pin                                       |                                                                       |      | 4    |      | Cycle |

| BOOT DIODE                            | E                                                                  |                                                                       |      |      |      |       |

| V <sub>DFWD</sub>                     | Bootstrap diode forward voltage                                    | I <sub>BOOT</sub> = 5 mA                                              |      | 0.8  |      | V     |

| THERMAL S                             | HUTDOWN                                                            | · L                                                                   |      |      | 1    |       |

| T <sub>JSD</sub> <sup>(2)</sup>       | Junction shutdown temperature                                      |                                                                       |      | 145  |      | °C    |

| T <sub>JSDH</sub> <sup>(2)</sup>      | Hysteresis                                                         |                                                                       |      | 20   |      | °C    |

A Veruct Flor nkl): 1754680 77546804 77 5 0 0

(2) Ensured by design. Not production tested.

Texas

INSTRUMENTS

eu Veruet Filo r Ink() : 7 PS4( 30 7 PS4( 804 7 S 0 0

\* Varuet F 10 r ink() : 1PS4(80 TPS4(804 7) S Copyright © 2000 Texas Instruments Incorporated

Figure 8.

TEXAS INSTRUMENTS

www.ti.com

Figure 7.

14 ouct F IC r Ink() : 1PS4(30 TPS4(804 (1) S 0 0

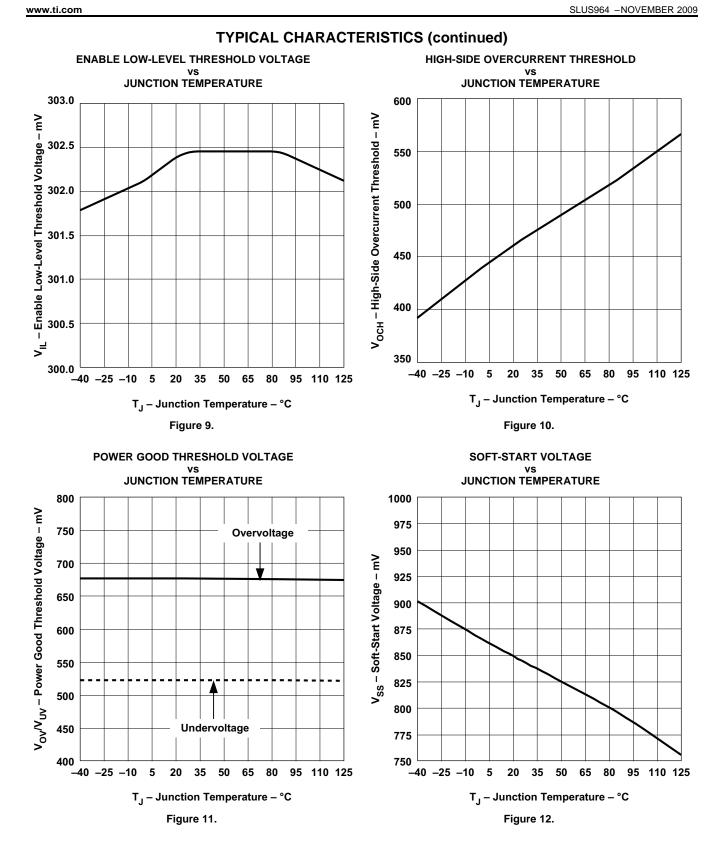

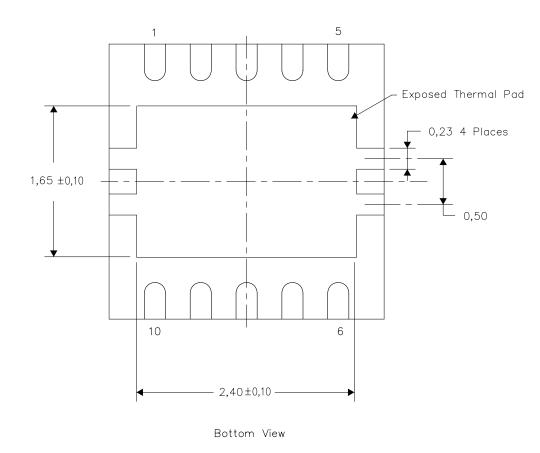

#### **DEVICE INFORMATION**

#### **TERMINAL CONFIGURATION**

The package is an 10-Pin SON (DRC) package. Note: The thermal pad is an electrical ground connection.

#### **PIN FUNCTIONS**

| TERMINAL |                | 1/0                                                                                                                   | DECODIDION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |

|----------|----------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NO.            | I/O                                                                                                                   | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| BOOT     | 6              | I                                                                                                                     | Gate drive voltage for the high side N-channel MOSFET. A 100 nF capacitor (typical) must be connected between this pin and SW. For low input voltage operation, an external schottky diode from BP to BOOT is recommended to maximize the gate drive voltage for the high-side.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| BP       | 10             | O Output bypass for the internal regulator. Connect a low ESR bypass ceramic capacitor of 1 µF or gruthis pin to GND. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| COMP     | 4              | 0                                                                                                                     | Output of the error amplifier and connection node for loop feedback components.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| EN/SS    | 2              | I                                                                                                                     | Logic level input which starts or stops the controller via an external user command. Letting this pin float turns the controller on. Pulling this pin low disables the controller. This is also the soft-start programming pin. A capacitor connected from this pin to GND programs the soft-start time. The capacitor is charged with an internal current source of 10 $\mu$ A. The resulting voltage ramp of this pin is also used as a second non-inverting input to the error amplifier after a 0.8 V (typical) level shift downwards. Output regulation is controlled by the internal level shifted voltage ramp until that voltage reaches the internal reference voltage of 600 mV – the voltage ramp of this pin reaches 1.4 V (typical). Optionally, a 267 k $\Omega$ resistor from this pin to BP enables frequency spread spectrum feature. |  |  |

| FB       | 5              | Ι                                                                                                                     | Inverting input to the error amplifier. In normal operation, the voltage on this pin is equal to the internal reference voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

| PGOOD    | 3              | 0                                                                                                                     | Open drain power good output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| HDRV     | 7              | 0                                                                                                                     | Bootstrapped gate drive output for the high side N-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| LDRV/OC  | 9              | 0                                                                                                                     | Gate drive output for the low side synchronous rectifier N-channel MOSFET. A resistor from this pin to GND is also used to determine the voltage level for OCP. An internal current source of 10 µA flows through the resistor during initial calibration and that sets up the voltage trip point used for OCP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| VDD      | 1              | Ι                                                                                                                     | Power input to the controller. Bypass VDD to GND with a low ESR ceramic capacitor of at least 1.0- $\mu$ F close to the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| SW       | 8              | 0                                                                                                                     | Sense line for the adaptive anti-cross conduction circuitry. Serves as common connection for the flying high side FET driver.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| GND      | Thermal<br>Pad |                                                                                                                       | Ground connection to the controller. This is also the thermal pad used to conduct heat from the device. This connection serves a twofold purpose. The first is to provide an electrical ground connection for the device. The second is to provide a low thermal impedance path from the device die to the PCB. This pad should be tied externally to a ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

Venuct F JC r nk(): 7 254( 30, TPS4( 304 7, S

0

8

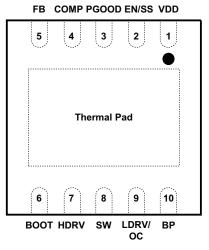

**TPS4030x BLOCK DIAGRAM**

#### **APPLICATION INFORMATION**

#### Introduction

The TPS4030x is a family of cost-optimized synchronous buck controllers providing high-end features to construct high-performance DC/DC converters. Pre-bias capability eliminates concerns about damaging sensitive loads during startup. Programmable over-current protection levels and hiccup over-current fault recovery maximize design flexibility and minimize power dissipation in the event of a prolonged output short. Frequency Spread Spectrum (FSS) feature reduces peak EMI noise by spreading the initial energy of each harmonic along a frequency band, thus giving a wider spectrum with lower amplitudes.

#### Voltage Reference

10

The 600 mV band gap cell is internally connected to the non-inverting input of the error amplifier. The reference voltage is trimmed with the error amplifier in a unity gain configuration to remove amplifier offset from the final regulation voltage. The 1% tolerance on the reference voltage allows the user to design a very accurate power supply.

#### Enable Functionality, Startup Sequence and Timing

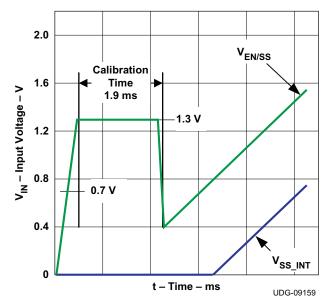

After input power is applied, an internal current source of 40  $\mu$ A starts to charge up the soft-start capacitor connected from EN/SS to GND. When the voltage across that capacitor increases to 0.7 V, it enables the internal BP regulator followed by a calibration. The total calibration time is about 1.9 ms. See Figure 13. During the calibration, the device performs in the following way. It disables the LDRV drive and injects an internal 10  $\mu$ A current source to the resistor connected from LDRV to GND. The voltage developed across that resistor is then sampled and latched internally as the OCP trip level until one cycles the input or toggles the EN/SS.

Figure 13. Startup Sequence and Timing

The voltage at EN/SS is internally clamped to 1.3 V before and/or during calibration to minimize the discharging time once calibration is complete. The discharging current is from an internal current source of 140  $\mu$ A and it pulls the voltage down to 0.4 V. It then initiates the soft-start by charging up the capacitor using an internal current source of 10  $\mu$ A. The resulting voltage ramp on this pin is used as a second non-inverting input to the error amplifier after an 800 mV (typical) downward level-shift; therefore, actual soft-start will not take place until the voltage at this pin reaches 800 mV.

If EN/SS is left floating, the controller starts automatically. EN/SS must be pulled down to less than 270 mV to guarantee that the chip is in shutdown mode.

#### Soft-Start Time

The soft-start time of the TPS4030x is user programmable by selecting a single capacitor. The EN/SS pin sources 10  $\mu$ A to charge this capacitor. The actual output ramp-up time is the amount of time that it takes for the 10  $\mu$ A to charge the capacitor through a 600mV range. There is some initial lag due to calibration and an offset (800 mV) from the actual EN/SS pin voltage to the voltage applied to the error amplifier.

The soft-start is done in a closed loop fashion, meaning that the error amplifier controls the output voltage at all times during the soft start period and the feedback loop is never open as occurs in duty cycle limit soft-start schemes. The error amplifier has two non-inverting inputs, one connected to the 600 mV reference voltage, and the other connected to the offset EN/SS pin voltage. The lower of these two voltages is what the error amplifier controls the FB pin to. As the voltage on the EN/SS pin ramps up past approximately 1.4 V (800 mV offset voltage plus the 600 mV reference voltage), the 600 mV reference voltage becomes the dominant input and the converter has reached its final regulation voltage.

The capacitor required for a given soft-start ramp time for the output voltage is given by Equation 1.

$$\mathbf{C}_{\mathbf{SS}} = \left(\frac{\mathbf{I}_{\mathbf{SS}}}{\mathbf{V}_{\mathsf{FB}}}\right) \times \mathbf{t}_{\mathbf{SS}}$$

(1)

where

- C<sub>SS</sub> is the required capacitance on the EN/SS pin (F)

- I<sub>ss</sub> is the soft-start source current (10 μA)

- V<sub>FB</sub> is the feedback reference voltage (0.6 V)

- t<sub>SS</sub> is the desired soft-start ramp time (s)

#### **Oscillator and Frequency Spread Spectrum (FSS)**

The oscillator frequency is internally fixed. The TPS40303 operating frequency is 300 KHz, the TPS40304 operating frequency is 600 KHz and the TPS40305 operating frequency is 1.2 MHz.

Connecting a resistor with a value of  $267 \text{ k}\Omega \pm 10\%$  from BP to EN/SS enables the FSS feature. When enabled, it spreads the internal oscillator frequency over a minimum 12% window using a 25-kHz modulation frequency with triangular profile. By modulating the switching frequency, side-bands are created. The emission power of the fundamental switching frequency and its harmonics is distributed into smaller pieces scattered around many side-band frequencies. The effect significantly reduces the peak EMI noise and makes it much easier for the resultant emission spectrum to pass EMI regulations.

#### **Overcurrent Protection**

Programmable OCP level at LDRV is from 6 mV to 150 mV at room temperature with 3000 ppm temperature coefficient to help compensate for changes in the low side FET channel resistance as temperature increases. With a scale factor of 2, the actual trip point across the low side FET is in the range of 12 mV to 300 mV. The accuracy of the internal current source is  $\pm 5\%$ . Overall offset voltage, including the offset voltage of the internal comparator and the amplifier for scale factor of 2, is limited to  $\pm 8$  mV.

Maximum clamp voltage at LDRV is 340 mV to avoid turning on the low side FET during calibration and in a pre-biased condition. The maximum clamp voltage is fixed and it does not change with temperature. If the voltage drop across  $R_{OCSET}$  reaches the 340 mV maximum clamp voltage during calibration (No  $R_{OCSET}$  resistor included), it disables OC protection. Once disabled, there is no low side or high side current sensing.

OCP level at HDRV is fixed at 450 mV with 3000 ppm temperature coefficient to help compensate for changes in the high side FET channel resistance as temperature increases. OCP at HDRV provides pulse-by-pulse current limiting.

veruct Folder Link():7PS4030\_\_\_\_\_7PS40304\_\_\_7\_S

SLUS964 -NOVEMBER 2009

OCP sensing at LDRV is a true inductor valley current detection, using sample and hold. Equation 2 can be used to calculate R<sub>OCSET</sub>:

$$R_{OCSET} = \left( \frac{\left(I_{OUT(max)} - \left(\frac{I_{P-P}}{2}\right)\right) \times R_{DS(on)} - V_{OCLOS}}{2 \times I_{OCSET}} \right)$$

where

- I<sub>OCSET</sub> is the internal current source

- V<sub>OCLOS</sub> is the overall offset voltage

- I<sub>P-P</sub> is the peak-to-peak inductor current

- R<sub>DS(on)</sub> is the drain to source on-resistance of the low-side FET

- I<sub>OUT(max)</sub> is the trip point for OCP

- R<sub>OCSET</sub> is the resistor used for setting the OCP level

To avoid over-current tripping in normal operating load range, calculate R<sub>OCSET</sub> using the equation above with:

- The maximum R<sub>DS(ON)</sub> at room temperature

- The lower limit of V<sub>OCLOS</sub> (-8 mV) and the lower limit of I<sub>OCSET</sub> (9.5 μA) from the *Electrical Characteristics* table.

- The peak-to-peak inductor current I<sub>P-P</sub> at minimum input voltage

Overcurrent is sensed across both the low-side FET and the high-side FET. If the voltage drop across either FET exceeds the OC threshold, a count increments one count. If no OC is detected on either FET, the fault counter decrements by one count. If three OC pulses are summed, a fault condition is declared which cycles the soft-start function in a hiccup mode. Hiccup mode consists of four dummy soft-start timeouts followed by a real one if overcurrent condition occurs from the beginning during start. This cycle continues indefinitely until the fault condition is removed.

#### Drivers

12

The drivers for the external high-side and low-side MOSFETs are capable of driving a gate-to-source voltage of  $V_{BP}$ . The LDRV driver for the low-side MOSFET switches between BP and GND, while HDRV driver for the high-side MOSFET is referenced to SW and switches between BOOT and SW. The drivers have non-overlapping timing that is governed by an adaptive delay circuit to minimize body diode conduction in the synchronous rectifier.

#### **Pre-Bias Startup**

The TPS4030x contains a circuit to prevent current from being pulled from the output during startup in the condition the output is pre-biased. There are no PWM pulses until the internal soft-start voltage rises above the error amplifier input (FB pin), if the output is pre-biased. Once the soft-start voltage exceeds the error amplifier input, the controller slowly initiates synchronous rectification by starting the synchronous rectifier with a narrow on time. It then increments that on time on a cycle-by-cycle basis until it coincides with the time dictated by (1-D), where D is the duty cycle of the converter. This approach prevents the sinking of current from a pre-biased output, and ensures the output voltage startup and ramp to regulation is smooth and controlled.

uct Folo r Link() : 7 PS4(30, TPS4(304, T

Copyright © 2000 Texas Instruments Incorporated

(2)

#### **Power Good**

The TPS4030x provides an indication that output is good for the converter. This is an open drain signal and pulls low when any condition exists that would indicate that the output of the supply might be out of regulation. These conditions include the following:

- V<sub>FB</sub> is more than ±12.5% from nominal

- Soft-start is active

- A short circuit condition has been detected

#### NOTE

When there is no power to the device, PGOOD is not able to pull close to GND if an auxiliary supply is used for the power good indication. In this case, a built in resistor connected from drain to gate on the PGOOD pull down device makes the PGOOD pin look approximately like a diode to GND.

#### **Thermal Shutdown**

If the junction temperature of the device reaches the thermal shutdown limit of 145°C, the PWM and the oscillator are turned off and HDRV and LDRV are driven low. When the junction cools to the required level (125°C typical), the PWM initiates soft start as during a normal power-up cycle.

nk():7PS4(30, TPS4(304, T, S

#### **DESIGN EXAMPLES**

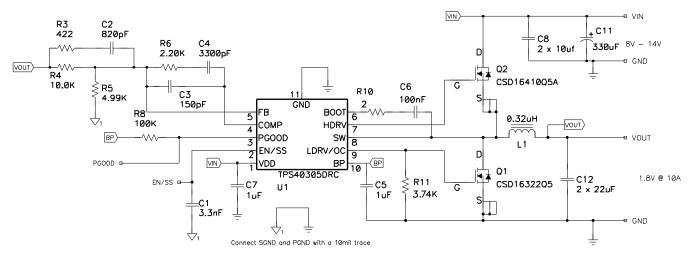

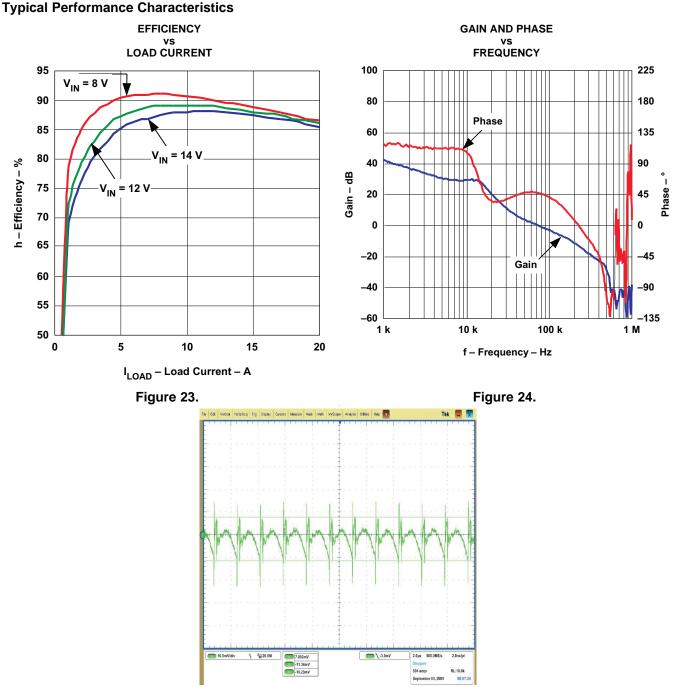

## Design Example 1: Using the TPS40305 for a 12 V to 1.8 V Point-of-Load Synchronous Buck Regulator

#### 12 V to 1.8 V Point-of-Load Synchronous Buck Regulator

The following example illustrates the design process and component selection for a 12 V to 1.8 V point-of-load synchronous buck regulator using the TPS40305.

|                         | PARAMETER                        | TEST CONDITIONS                                           | MIN   | TYP   | MAX   | UNIT |

|-------------------------|----------------------------------|-----------------------------------------------------------|-------|-------|-------|------|

| V <sub>IN</sub>         | Input voltage                    |                                                           | 8     |       | 14    | V    |

| V <sub>IN(ripple)</sub> | Input ripple voltage             | I <sub>OUT</sub> = 10 A                                   |       |       | 0.6   | V    |

| V <sub>OUT</sub>        | Output voltage                   | 0 A ≤ I <sub>OUT</sub> ≤ 10 A                             | 1.764 | 1.800 | 1.836 | V    |

|                         | Line regulation                  | $8 \text{ V} \leq \text{V}_{\text{IN}} \leq 14 \text{ V}$ |       |       | 0.5%  |      |

|                         | Load regulation                  | 0 A ≤ I <sub>OUT</sub> ≤ 10 A                             |       |       | 0.5%  |      |

| V <sub>RIPPLE</sub>     | Output voltage ripple            | I <sub>OUT</sub> = 10 A                                   |       |       | 36    | mV   |

| V <sub>OVER</sub>       | Output overshoot                 | I <sub>OUT</sub> falling from 7 A to 3 A                  |       | 100   |       | mV   |

| V <sub>UNDER</sub>      | Output undershoot                | I <sub>OUT</sub> rising from 3 A to 7 A                   |       | 100   |       | mV   |

| I <sub>OUT</sub>        | Output current                   | $4.5 \text{ V} \leq \text{V}_{IN} \leq 5.5 \text{ V}$     | 0     |       | 10    | А    |

| t <sub>SS</sub>         | Soft start time                  | V <sub>IN</sub> = 12 V                                    |       | 1.5   |       | ms   |

| I <sub>SCP</sub>        | Short circuit current trip point |                                                           | 13    | 15    |       | А    |

| f <sub>SW</sub>         | Switching frequency              |                                                           |       | 1200  |       | kHz  |

| η                       | Efficiency                       | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 5 A            |       | 90%   |       |      |

| η                       | Full load efficiency             | V <sub>IN</sub> = Nom, I <sub>OUT</sub> = Max             |       | 80%   |       |      |

#### Table 1. Design Example Electrical Characteristics

Figure 14. TPS40305 Design Example Schematic

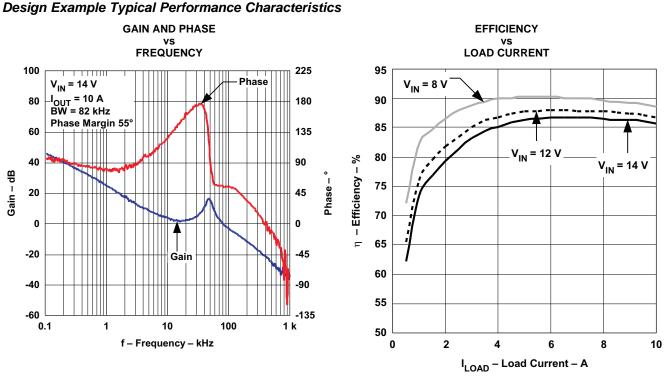

The list of materials for this application is shown in Table 3. The loop response and efficiency from boards built using this design are shown in Figure 15 and Figure 16. Gerber Files and additional application information are available from the factory.

#### **Design Procedure**

#### **Selecting the Switching Frequency**

To achieve the small size for this design the TPS40305, with  $f_{SW}$  = 1200 kHz, is selected for minimal external component size.

#### Inductor Selection (L1)

Synchronous buck power inductors are typically sized for approximately 30% peak-to-peak ripple current ( $I_{RIPPLE}$ ) Given this target ripple current, the required inductor size can be calculated in Equation 3.

$$L \approx \frac{V_{IN}(max) - V_{OUT}}{0.3 \times I_{OUT}} \times \frac{V_{OUT}}{V_{IN}(max)} \times \frac{1}{f_{SW}} = \frac{14 V - 1.8 V}{0.3 \times 10 A} \times \frac{1.8 V}{14 V} \times \frac{1}{1200 \text{ kHz}} = 471 \text{ nH}$$

(3)

Selecting a standard 400-nH inductor value, solve for IRIPPLE =3.5 A

The RMS current through the inductor is approximated by Equation 4.

$$I_{L(rms)} = \sqrt{I_{L(avg)}^{2} + \frac{1}{12}I_{RIPPLE}^{2}} = \sqrt{I_{OUT}^{2} + \frac{1}{12}I_{RIPPLE}^{2}} = \sqrt{10^{2} + \frac{1}{12}3.5^{2}} = 10.05 \text{ A}$$

(4)

#### **Output Capacitor Selection (C12)**

The selection of the output capacitor is typically driven by the output transient response. Equation 5 and Equation 6 overestimate the voltage deviation to account for delays in the loop bandwidth and can be used to determine the required output capacitance.

$$V_{OVER} < \frac{I_{TRAN}}{C_{OUT}} \times \Delta T = \frac{I_{TRAN}}{C_{OUT}} \times \frac{I_{TRAN} \times L}{V_{OUT}} = \frac{I_{TRAN}^2 \times L}{V_{OUT} \times C_{OUT}}$$

(5)

$$V_{\text{UNDER}} < \frac{I_{\text{TRAN}}}{C_{\text{OUT}}} \times \Delta T = \frac{I_{\text{TRAN}}}{C_{\text{OUT}}} \times \frac{I_{\text{TRAN}} \times L}{V_{\text{IN}} - V_{\text{OUT}}} = \frac{I_{\text{TRAN}}^2 \times L}{(V_{\text{IN}} - V_{\text{OUT}}) \times C_{\text{OUT}}}$$

(6)

If  $V_{IN(min)} > 2 \times V_{OUT}$ , use overshoot (Equation 5) to calculate minimum output capacitance. If  $V_{IN(min)} < 2 \times V_{OUT}$ , use undershoot(Equation 6) to calculate minimum output capacitance.

$$C_{OUT(min)} = \frac{I_{TRAN(max)}^{2} \times L}{(V_{OUT}) \times V_{OVER}} = \frac{4^{2} \times 400 \text{ nH}}{1.8 \times 100 \text{ mV}} = 35 \,\mu\text{F}$$

(7)

1

With a minimum capacitance, the maximum allowable ESR is determined by the maximum ripple voltage and is approximated by Equation 8.

$$\mathsf{ESR}_{\mathsf{MAX}} = \frac{\mathsf{V}_{\mathsf{RIPPLE}(\mathsf{total})} - \mathsf{V}_{\mathsf{RIPPLE}(\mathsf{cap})}}{\mathsf{I}_{\mathsf{RIPPLE}}} = \frac{\mathsf{V}_{\mathsf{RIPPLE}(\mathsf{total})} - \left(\frac{\mathsf{I}_{\mathsf{RIPPLE}}}{8 \times \mathsf{C}_{\mathsf{OUT}} \times \mathsf{f}_{\mathsf{SW}}}\right)}{\mathsf{I}_{\mathsf{RIPPLE}}}$$

$$=\frac{36\text{mV}-\left(\frac{3.5\text{A}}{8\times35\,\mu\text{F}\times1200\,\text{kHz}}\right)}{3.5\,\text{A}}=7\,\text{m}\Omega$$

(8)

Two 0805, 22- $\mu$ F, 6.3 V, X5R ceramic capacitors are selected to provide more than 35- $\mu$ F of minimum capacitance and less than 7 m $\Omega$  of ESR (2.5 m $\Omega$  each).

uct Folo r link() : 7PS4(30 TPS4(304 7

SLUS964 -NOVEMBER 2009

#### **Peak Current Rating of Inductor**

With output capacitance, it is possible to calculate the charge current during start-up and determine the minimum saturation current rating for the inductor. The start-up charging current is approximated by Equation 9.

$$I_{CHARGE} = \frac{V_{OUT} \times C_{OUT}}{t_{SS}} = \frac{1.8 \, V \times 2 \times 22 \, \mu F}{1.5 \, \text{ms}} = 0.053 \, \text{A}$$

(9)

#### **Table 2. Inductor Requirements**

| SYMBOL               | PARAMETER                        | VALUE | UNITS |

|----------------------|----------------------------------|-------|-------|

| L                    | Inductance                       | 400   | nH    |

| I <sub>L(rms)</sub>  | RMS current (thermal rating)     | 10.05 | А     |

| I <sub>L(peak)</sub> | Peak current (saturation rating) | 11.8  | А     |

A PG0083.401, 400 nH inductor is selected for its small size, low DCR ( $3.0m\Omega$ ) and high-current handling capability (17-A thermal, 27-A saturation).

#### Input Capacitor Selection (C8)

The input voltage ripple is divided between capacitance and ESR. For this design  $V_{RIPPLE(cap)} = 150 \text{ mV}$  and  $V_{RIPPLE(esr)} = 150 \text{ mV}$ . The minimum capacitance and maximum ESR are estimated by Equation 11.

$$C_{IN(min)} = \frac{I_{LOAD} \times V_{OUT}}{V_{RIPPLE(cap)} \times V_{IN} \times f_{SW}} = \frac{10 \times 1.8 V}{150 \text{ mV} \times 8 \text{ V} \times 1200 \text{ kHz}} = 12.5 \,\mu\text{F}$$

(11)

$$ESR_{MAX} = \frac{V_{RIPPLE(esr)}}{I_{LOAD} + \frac{1}{2}I_{RIPPLE}} = \frac{150 \text{ mV}}{11.75 \text{ A}} = 12.7 \text{ m}\Omega$$

(12)

The RMS current in the input capacitors is estimated by Equation 13.

$$I_{RMS(cin)} = I_{LOAD} \times \sqrt{D \times (1 - D)} = 10 A \times \sqrt{0.225 \times (1 - 0.225)} = 4.17 A_{RMS}$$

(13)

Two 1210, 10- $\mu$ F, 25-V, X5R ceramic capacitors with approximately 2-m $\Omega$  of ESR and a 2.5-A RMS current rating each are selected. Higher voltage capacitors are selected to minimize capacitance loss at the DC bias voltage to ensure the capacitors allow sufficient capacitance at the working voltage.

#### **MOSFET Switch Selection (Q1 and Q2)**

Reviewing available TI NexFET MOSFETs using TI's NexFET MOSFET selection tool, the CSD16410Q5A and CSD16322Q5 5 mm × 6 mm MOSFETs are selected.

These two FETs have maximum total gate charges of 5 nC and 10 nC respectively, which draws 18 mA at 1.2 MHz from the BP regulator, less than its 50 mA minimum rating.

#### **Bootstrap Capacitor (C6)**

To ensure proper charging of the high-side FET gate, limit the ripple voltage on the boost capacitor to less than 50 mV.

$$C_{BOOST} = 20 \times Q_{G2} = 20 \times 5nC = 100nF$$

(14)

#### VDD Bypass Capacitor (C7)

Per the TPS40305 Electrical Characteristics specifications, select a 1.0-µF X5R or better ceramic bypass capacitor for VDD.

#### **BP Bypass Capacitor (C5)**

Submit Documentation Feedback

As listed in the Electrical Characteristics table, a minimum of 1.0-µF ceramic capacitance is required to stabilize the BP regulator. To limit regulator noise to less than 10 mV, the value of the bypass capacitor is calculated in Equation 15.

uct Folo r Link() :7PS4(30 TPS4(304

16

Copyright @ 2009 Texas Instruments Incorporated

(10)

$$C_{BP} = 100 \times MAX(Q_{G1}, Q_{G2})$$

Since Q1 is larger than Q2, and the total gate charge of Q1 is 10 nC, a BP capacitor of 1.0  $\mu$ F is calculated. A standard value of 1.0  $\mu$ F is selected to limit noise on the BP regulator.

#### **Short Circuit Protection (R11)**

The TPS40305 uses the negative drop across the low-side FET at the end of the OFF time to measure the inductor current. Allowing for 30% over maximum load and 20% rise in  $R_{DS(on)Q1}$  for self-heating, the voltage drop across the low-side FET at current limit is given by Equation 16.

$$V_{OC} = (1.3 \times I_{LOAD} - \frac{1}{2}I_{RIPPLE}) \times 1.2 \times R_{DS(on)Q1} = (1.3 \times 10A - \frac{1}{2}3.5A) \times 1.2 \times 4.6 \,\text{m}\Omega = 62.1 \,\text{mV}$$

(16)

The TPS40305 internal temperature coefficient helps compensate for the MOSFET's R<sub>DS(on)</sub> temperature coefficient, so the current limit programming resistor is selected by Equation 17.

$$\mathsf{R}_{\mathsf{CS}} = \frac{\mathsf{V}_{\mathsf{OC}} - \mathsf{V}_{\mathsf{OCLOS}(\mathsf{min})}}{2 \times \mathsf{I}_{\mathsf{OCSET}(\mathsf{min})}} = \frac{62.1 \text{mV} - (-8 \text{mV})}{2 \times 9.5 \,\mu \text{A}} = 3.69 \,\text{k}\Omega \approx 3.74 \,\text{k}\Omega$$

(17)

#### Feedback Divider (R4, R5)

The TPS40305 controller uses a full operational amplifier with an internally fixed 0.600-V reference. R4 is selected between 10 k $\Omega$ and 50 k $\Omega$  for a balance of feedback current and noise immunity. With R4 set to 10 k $\Omega$ , The output voltage is programmed with a resistor divider given by Equation 18.

$$R5 = \frac{V_{FB} \times R4}{V_{OUT} - V_{FB}} = \frac{0.600 \, V \times 10.0 \, k\Omega}{1.8 \, V - 0.600 \, V} = 5.0 \, k\Omega \approx 4.99 \, k\Omega$$

(18)

nk():7PS4(30, TPS4(304, 7, S

#### Compensation: (C2, C3, C4, R3, R6)

Using the TPS40k Loop Stability Tool for 100 kHz bandwidth and 60° phase margin with a R4 value of 10.0 k $\Omega$ , the following values are returned.

- C2 = C\_1 = 820 pF

- C3 = C\_3 = 150 pF

- C4 = C\_2 = 3300 pF

- R3 = R\_2 = 422 Ω

- $R6 = R_3 = 2.20 \text{ k}\Omega$

(15)

Figure 15.

Figure 16.

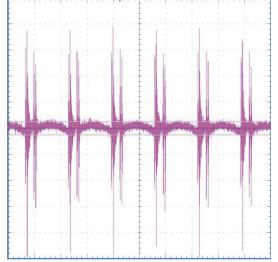

Figure 17. Output Ripple (500 MHz Bandwidth)

Varuet Filo r Ink(): 7 S4(80 TPS4(804 7)S

0 0

#### TPS40305 Design Example List of Materials

| REFERENCE<br>DESIGNATOR | QTY | VALUE   | DESCRIPTION                                   | SIZE                  | PART NUMBER | MFR       |

|-------------------------|-----|---------|-----------------------------------------------|-----------------------|-------------|-----------|

| C1                      | 1   | 3.3 nF  | Capacitor, Ceramic, 10 V, X7R, 20%            | 0603                  | Std         | Std       |

| C2                      | 1   | 820 pF  | Capacitor, Ceramic, 25 V, X7R, 10%            | 0603                  | Std         | Std       |

| C3                      | 1   | 150 pF  | Capacitor, Ceramic, 25 V, X7R, 10%            | 0603                  | Std         | Std       |

| C4                      | 1   | 3300 pF | Capacitor, Ceramic, 25 V, X7R, 10%            | 0603                  | Std         | Std       |

| C5                      | 1   | 1.0 µF  | Capacitor, Ceramic, 10 V, X7R, 20%            | 0805                  | Std         | Std       |

| C6                      | 1   | 100 nF  | Capacitor, Ceramic, 16 V, X7R, 20%            | 0603                  | Std         | Std       |

| C7                      | 1   | 1 µF    | Capacitor, Ceramic, 25 V, X7R, 20%            | 0805                  | Std         | Std       |

| C8                      | 2   | 10 µf   | Capacitor, Ceramic, 25 V, X7R, 10%            | 1210                  | Std         | Std       |

| C11                     | 1   | 330 µF  | Capacitor, Aluminum, 25 V, ±20%, 160mohms     | 0.328 x<br>0.390 inch | EEVFK1E331P | Panasonic |

| C12                     | 2   | 22 µF   | Capacitor, Ceramic, 6.3 V, X5R, 20%           | 0805                  | Std         | Std       |

| L1                      | 1   | 0.32 µH | Inductor, SMT, 17 A                           | 0.268 x<br>0.268 inch | PG0083.401  | Pulse     |

| Q1                      | 1   |         | MOSFET, N-Channel, 25 V, 97 A, 4.6 m $\Omega$ | QFN-8<br>POWER        | CSD16322Q5  | TI        |

| Q2                      | 1   |         | MOSFET, N-Channel, 25V, 59 A, 9.6 mΩ          | QFN-8<br>POWER        | CSD16410Q5A | ті        |

| R3                      | 1   | 422 Ω   | Resistor, Chip, 1/16W, 1%                     | 0603                  | Std         | Std       |

| R4                      | 1   | 10.0 kΩ | Resistor, Chip, 1/16W, 1%                     | 0603                  | Std         | Std       |

| R5                      | 1   | 4.99 kΩ | Resistor, Chip, 1/16W, 1%                     | 0603                  | Std         | Std       |

| R6                      | 1   | 2.20 kΩ | Resistor, Chip, 1/16W, 1%                     | 0603                  | Std         | Std       |

| R8                      | 1   | 100 kΩ  | Resistor, Chip, 1/16W, 1%                     | 0603                  | Std         | Std       |

| R10                     | 1   | 2 Ω     | Resistor, Chip, 1/16W, 1%                     | 0603                  | Std         | Std       |

| R11                     | 1   | 3.74 kΩ | Resistor, Chip, 1/16W, 1%                     | 0603                  | Std         | Std       |

| U1                      | 1   |         | IC, 3V-20V sync. 1.2MHz Buck controller       | DRC10                 | TPS40305DRC | TI        |

Veruct F 10 r nkr): 7PS4030 7PS40804 7 S 0 0

#### Table 3. Design Example List of Materials

SLUS964 -NOVEMBER 2009

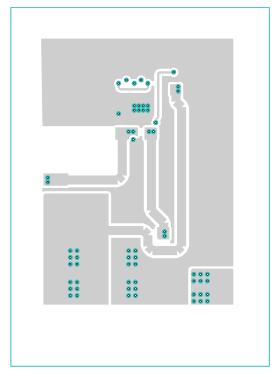

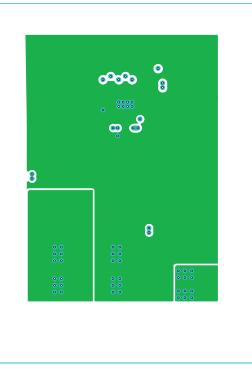

#### Layout Information

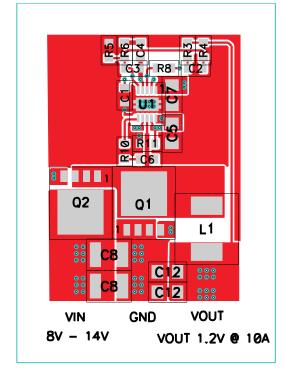

Figure 18. Top Copper with Components

Figure 20. Bottom Internal Copper Layout

Venuct F JC r nk( ) : 7 254( 30, TPS4( 804 7

Submit Documentation Feedback

8 8

Figure 21. Bottom Copper Layer

0 0

Copyright © 2009 Texas Instruments Incorporated

www.ti.com

INSTRUMENTS

Texas

8 Figure 19. Top Internal Copper Layout

20

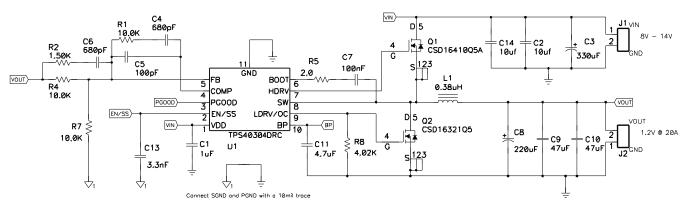

#### Design Example 2: A High Current, Low Voltage Design Using the TPS40304

For this 20-A, 12-V to 1.2-V design, the 600kHz, TPS40304 was selected for the balance between small size and high efficiency.

#### System Design Specifications

The system design specifications are shown in Table 4.

#### **Table 4. Design Example Electrical Characteristics**

| PARAMETER             |                                  | TEST CONDITIONS                                 | MIN   | TYP   | MAX   | UNIT            |

|-----------------------|----------------------------------|-------------------------------------------------|-------|-------|-------|-----------------|

| V <sub>IN</sub>       | Input voltage                    |                                                 | 8.0   |       | 14    | V               |

| V <sub>INripple</sub> | Input ripple                     | I <sub>OUT</sub> = 20 A                         |       |       | 0.5   | V               |

| V <sub>OUT</sub>      | Output voltage                   | 0 A ≤I <sub>OUT</sub> ≤ 20 A                    | 1.164 | 1.200 | 1.236 | V               |

|                       | Line regulation                  | 8 V ≤ V <sub>IN</sub> ≤14 V                     |       |       | 0.5%  |                 |

|                       | Load regulation                  | 0 A ≤I <sub>OUT</sub> ≤ 20 A                    |       |       | 0.5%  |                 |

| V <sub>RIPPLE</sub>   | Output ripple                    | I <sub>OUT</sub> = 20 A                         |       |       | 36    | mV              |

| V <sub>OVER</sub>     | Output overshoot                 | 5 A ≤I <sub>OUT</sub> ≤ 15 A                    |       | 100   |       | mV              |

| V <sub>UNDER</sub>    | Output undershoot                | 5 A ≤I <sub>OUT</sub> ≤ 15 A                    |       | 100   |       | mV              |

| I <sub>OUT</sub>      | Output current                   | 8 V ≤ V <sub>IN</sub> ≤14 V                     | 0     |       | 20    | А               |

| t <sub>SS</sub>       | Soft-start time                  | V <sub>IN</sub> = 12 V                          |       | 1.5   |       | ms              |

| I <sub>SCP</sub>      | Short-circuit current trip point |                                                 | 26    |       |       | А               |

|                       | Efficiency                       | V <sub>IN</sub> = 12 V, I <sub>OUT</sub> = 12 A |       |       |       | %               |

| f <sub>SW</sub>       | Switching frequency              |                                                 |       | 600   |       | kHz             |

|                       | Size                             |                                                 |       |       | 1.5   | in <sup>2</sup> |

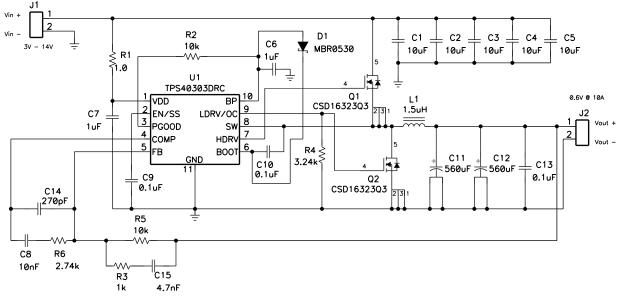

#### Schematic

#### Figure 22. TPS40304 Design Example Schematic

requet Fold r (ink/):7 254(30 TPS4(304 7) \$ 0

SLUS964 -NOVEMBER 2009

Figure 25. Output Ripple 10 mV/div, 2-µs/div, 20-MHz Bandwidth

Veruet File r ink(): 7 \$4430 TP\$40804 T S

0

Submit Documentation Feedback

TEXAS INSTRUMENTS

www.ti.com

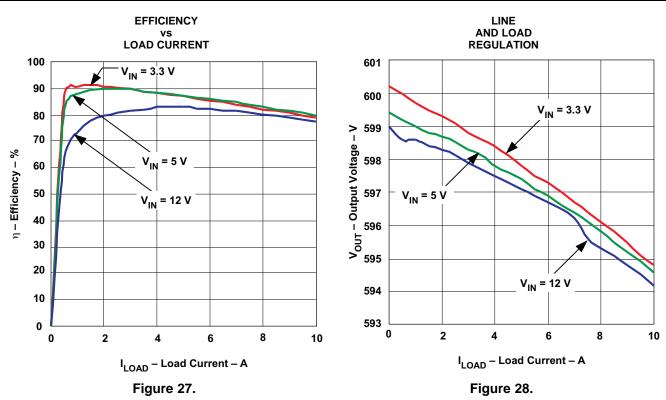

#### **Design Example 3: A Synchronous Buck Application Using the TPS40303**

This example illustrates a 3.3-V/5-V/12-V to 0.6-V at 10-A synchronous buck application using the TPS40303 switching at 300 kHz.

#### Schematic

Figure 26. TPS40303 Design Example Schematic

#### **Typical Performance Characteristics**

A typical efficiency graph for this design example using the TPS40303 is shown in Figure 27. The typical line and load regulation this design example using the TPS40303 is shown in Figure 28

#### TEXAS INSTRUMENTS

Copyright © 2009 Texas Instruments Incorporated

www.ti.com

## TPS40303, TPS40304, TPS40305

SLUS964 -NOVEMBER 2009

#### ADDITIONAL REFERENCES

#### **Related Devices**

The devices listed in have characteristics similar to the TPS4030x and may be of interest.

| Table 5 | Related | Devices |

|---------|---------|---------|

|---------|---------|---------|

| DEVICE     | DESCRIPTION                                                                   |

|------------|-------------------------------------------------------------------------------|

| TPS40192/3 | 4.5 V to 18 V Input 10-pin Synchronous Buck Controller with Power Good        |

| TPS40195   | 4.5 V to 20 V Synchronous Buck Controller with Synchronization and Power Good |

| TPS40190   | Low Pin Count Synchronous Buck Controller                                     |

#### References

These references, design tools and links to additional references, including design software, may be found at <a href="http://power.ti.com">http://power.ti.com</a>

- 1. Additional PowerPAD<sup>™</sup> information may be found in Applications Briefs (SLMA002A) and (SLMA004).

- 2. Under The Hood Of Low Voltage DC/DC Converters SEM1500 Topic 5 2002 Seminar Series

- 3. Understanding Buck Power Stages in Switchmode Power Supplies, (SLVA057), March 1999

- 4. Designing Stable Control Loops SEM 1400 2001 Seminar Series

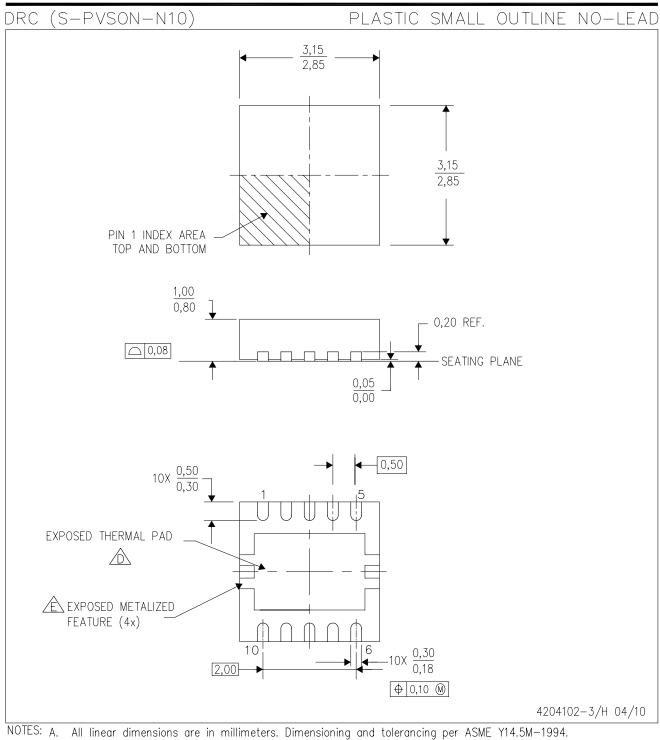

#### Package Outline and Recommended PCB Footprint

Submit Documentation Feedback

The following pages outline the mechanical dimensions of the 10-pin DRC package and provide recommendations for PCB layout.

ouct F-lo\_r = nk(-) : 7 PS4(-30 TPS4(-804-7)

#### **PACKAGING INFORMATION**

RUMENTS

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | Eco Plan <sup>(2)</sup>    | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|----------------------------|------------------|------------------------------|

| TPS40303DRCR     | ACTIVE                | SON             | DRC                | 10   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS40303DRCT     | ACTIVE                | SON             | DRC                | 10   | 250            | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS40304DRCR     | ACTIVE                | SON             | DRC                | 10   | 3000           | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS40304DRCT     | ACTIVE                | SON             | DRC                | 10   | 250            | Green (RoHS & no Sb/Br)    | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS40305DRCR     | ACTIVE                | SON             | DRC                | 10   | 3000           | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS40305DRCT     | ACTIVE                | SON             | DRC                | 10   | 250            | Green (RoHS &<br>no Sb/Br) | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

NRND: Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

# www.BDTIC.com/TI

## **MECHANICAL DATA**

- B. This drawing is subject to change without notice.

- Small Outline No-Lead (SON) package configuration. Ç.

- $\mathbb{A}$ The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- Æ. Metalized features are supplier options and may not be on the package.

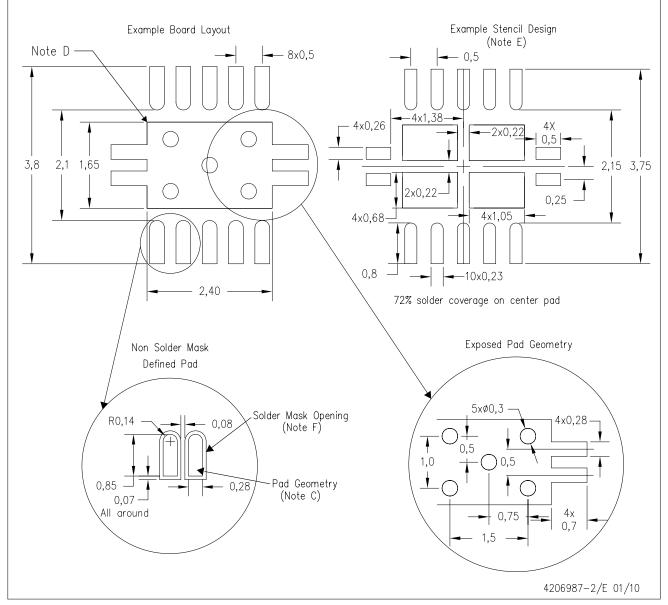

## THERMAL PAD MECHANICAL DATA

## DRC (S-PVSON-N10)

## PLASTIC SMALL OUTLINE NO-LEAD

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No-Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

DRC (S-PVSON-N10)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat-Pack Packages, Texas Instruments Literature No. SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="http://www.ti.com">http://www.ti.com</a>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.