TPS65810 **TPS65811**

SLVS658B-MARCH 2006-REVISED FEBRUARY 2007

# SINGLE-CELL LI-ION BATTERY- AND POWER-MANAGEMENT IC

### FEATURES

- **BATTERY CHARGER**

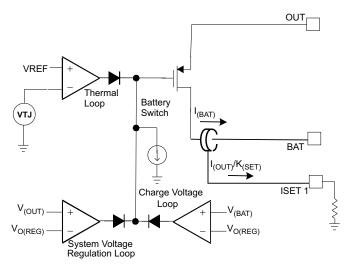

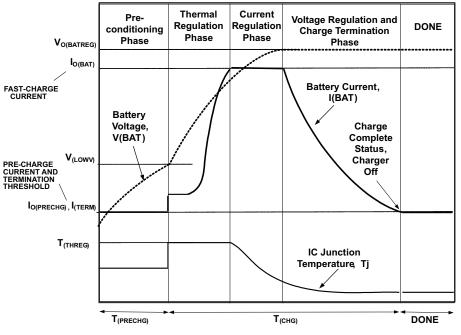

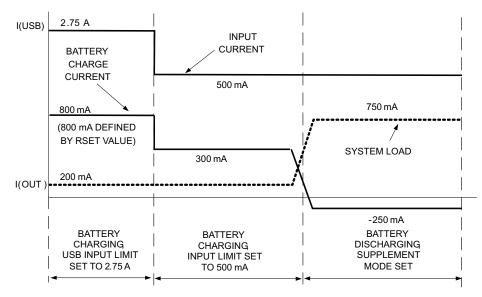

- Complete charge management solution for single Li-Ion/Li-Pol cell with thermal foldback, dynamic power management and pack temperature sensing, supporting up to 1.5-A max charge current

- Programmable charge parameters for AC adapter and USB port operation

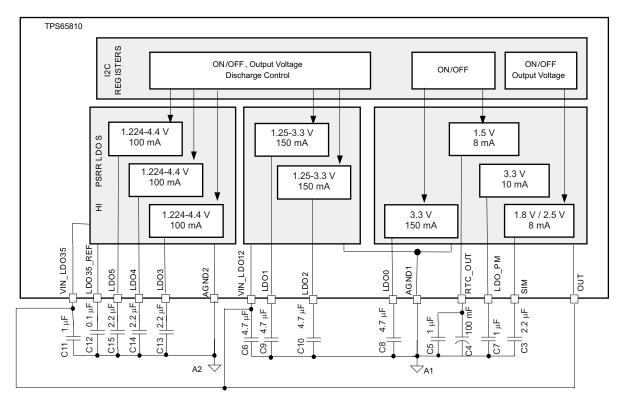

- **INTEGRATED POWER SUPPLIES**

- A total of 9 LDOs are integrated:

- Six adjustable output LDOs (1.25-V to 3.3-V)

- Two fixed-voltage LDOs (3.3-V)

- One RTC backup supply with low leakage (1.5-V)

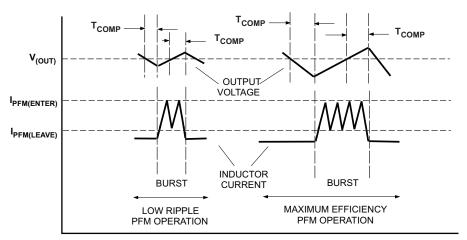

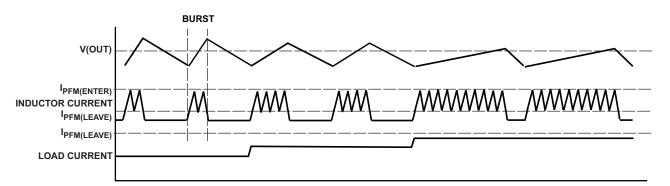

- Two 0.6-V to 3.4-V programmable dc/dc buck converters (600-mA for TPS65810, 750-mA for TPS65811) with enable, standby-mode operation, and automatic low-power mode setting

- **DISPLAY FUNCTIONS**

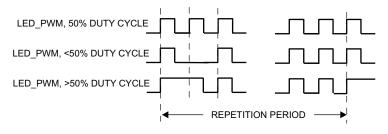

- Two open-drain PWM outputs with programmable frequency and duty cycle. Can be used to control keyboard backlight, vibrator, or other external peripheral functions

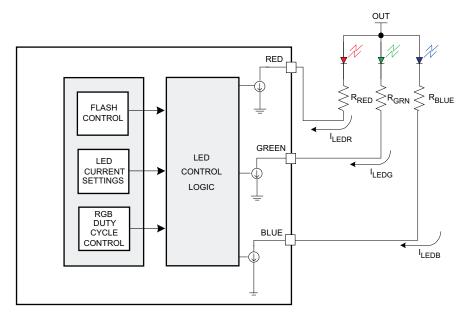

- RGB LED driver with programmable flashing period and individual R/G/B brightness control

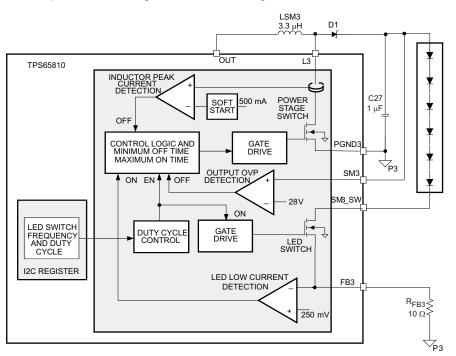

- Constant-current white LED driver, with programmable current level, brightness control, and overvoltage protection can drive up to 6 LEDs in series configuration

- SYSTEM MANAGEMENT

Products conform to specifications per the terms of the Instruments standard warranty. Projuctor to obsin to necessarily include testing of all parameters.

- Dual input power path function with input current limiting and OVP protection

- POR function with programmable masking monitors all integrated supplies outputs

- Software and hardware reset functions

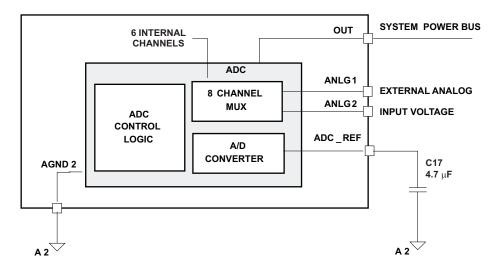

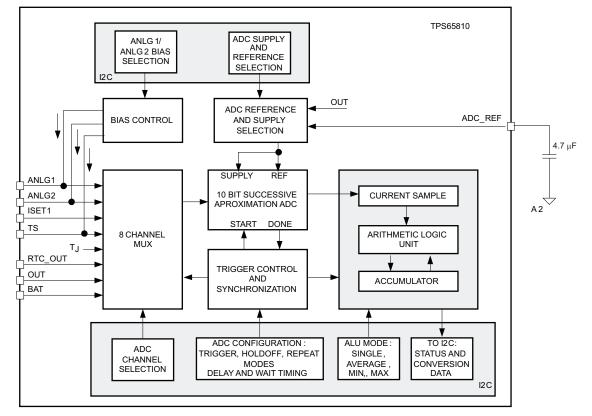

- 8-channel integrated A/D samples system parameters with single conversion, peak detection, or averaging operating modes

- HOST INTERFACE

- Host can set system parameters and access system status using I<sup>2</sup>C interface

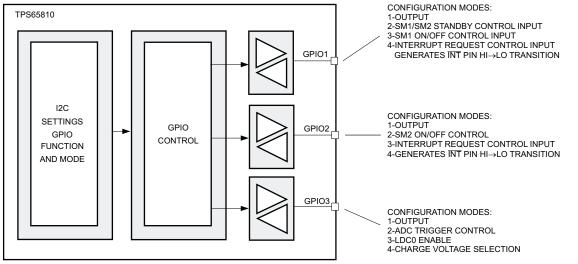

- Interrupt function with programmable masking signals system status modification to host

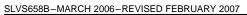

- 3 GPIO ports, programmable as drivers, integrated A/D trigger or buck converters standby mode control

### **APPLICATIONS**

- PDAs

- **Smart Phones** •

- MP3s

- **Internet Appliances** •

- Handheld Devices

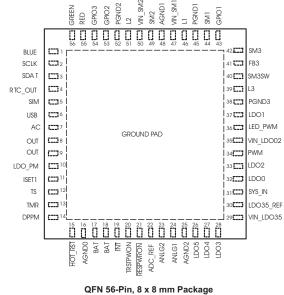

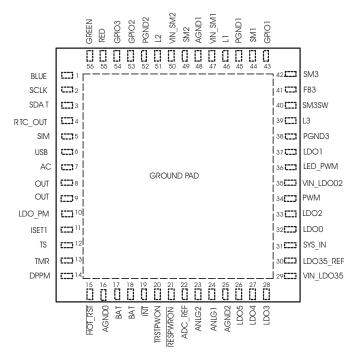

(Top View - Not To Scale)

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Res 1

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

### DESCRIPTION

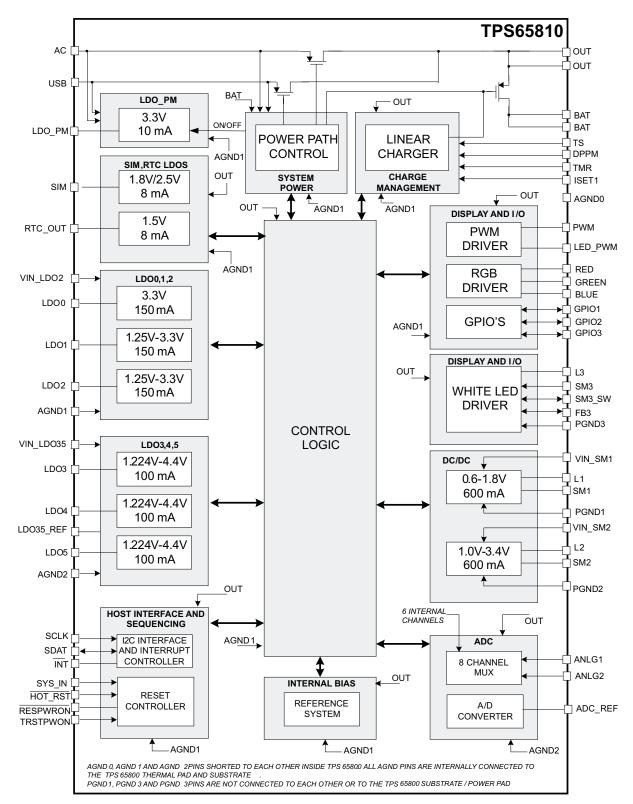

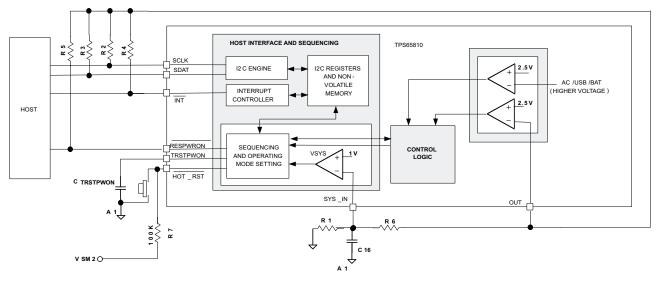

The TPS65810 provides an easy to use, fully integrated solution for handheld devices, integrating charge management, multiple regulated power supplies, system management and display functions, in a small thermally-enhanced 8x8 package. The high level of integration enables typical board area space savings of 70% when compared to equivalent discrete solutions, while implementing a high-performance and flexible solution, portable across multiple platforms. If required, an external host may control the TPS65810 via I<sup>2</sup>C interface, with access to all integrated systems. The I<sup>2</sup>C enables setting output voltages, current thresholds, and operation modes. Internal registers have a complete set of status information, enabling easy diagnostics, and host-controlled handling of fault conditions. The TPS65810 can operate in stand-alone mode, with no external host control, if the internal power-up defaults are compatible with the system requirements

#### AVAILABLE OPTIONS<sup>(1)</sup>

| TJ             | DEVICES <sup>(2)</sup> (3) (4) | MARKING  |

|----------------|--------------------------------|----------|

| –40°C to 125°C | TPS65810RTQ                    | TPS65810 |

| –40°C to 125°C | TPS65811RTQ                    | TPS65811 |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI Web site at www.ti.com.

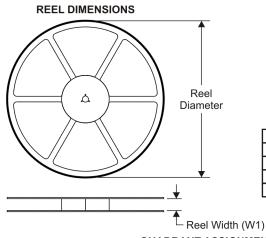

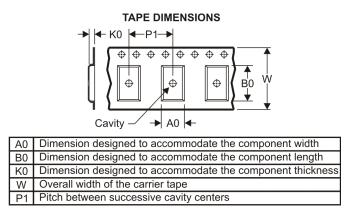

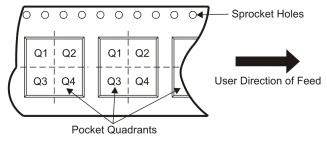

(2) The RTQ package is available in tape and reel. Add R suffix (TPS65810RTQR) to order quantities of 2000 parts per reel. Add T suffix (TPS65810RTQT) to order quantities of 250 parts per reel.

(3) This product is RoHS compatible, including a lead concentration that does not exceed 0.1% of total product weight, and is suitable for use in specified lead-free soldering processes. In addition, this product uses package materials that do not contain halogens, including bromine (Br) or antimony (Sb) above 0.1% of total product weight.

(4) Other power-up sequences and default power-up states for the supplies can be implemented upon request. Consult factory for available options

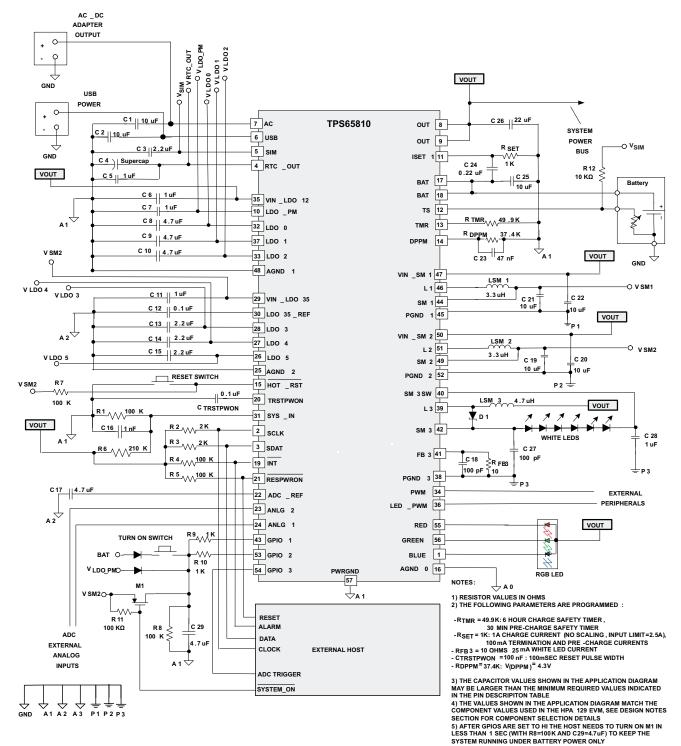

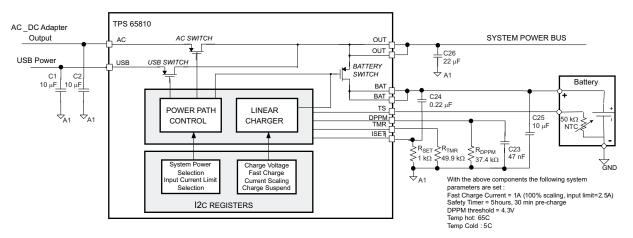

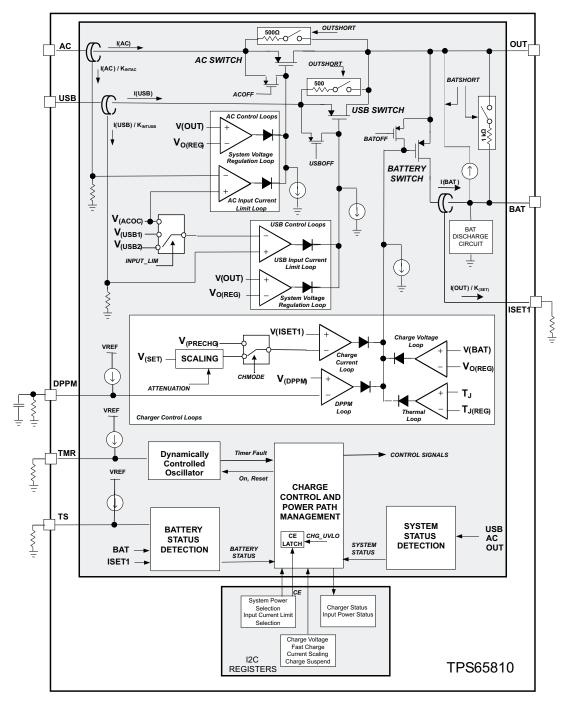

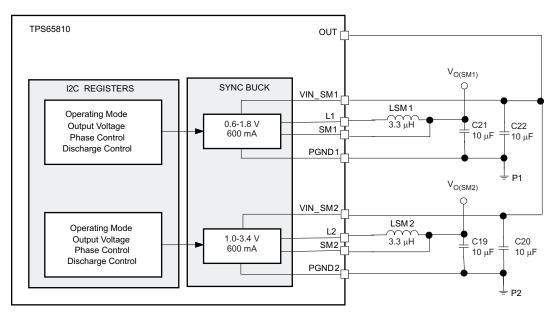

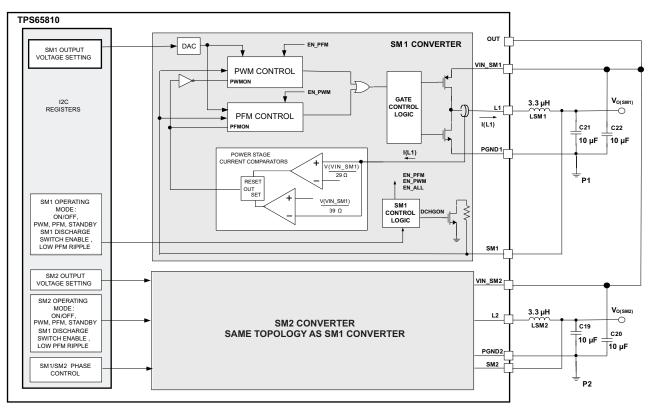

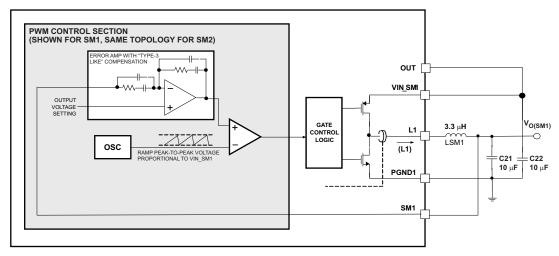

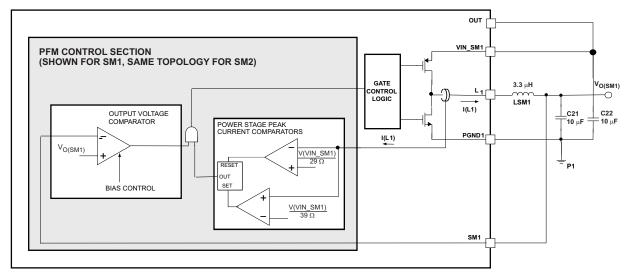

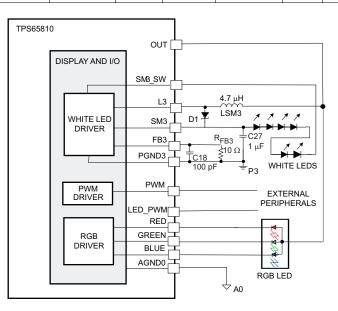

Figure 1. TPS65810 Simplified Block Diagram

SLVS658B-MARCH 2006-REVISED FEBRUARY 2007

Copyright © 2006 2007 Texas Instruments Incorporated

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>.

|                  |                                                              | VALUE                             | UNIT |

|------------------|--------------------------------------------------------------|-----------------------------------|------|

|                  | AC and USB with respect to AGND1                             | -0.3 to 18                        |      |

|                  | ANLG1, ANLG2 with respect to AGND2                           | -0.3 to V(OUT)                    |      |

|                  | V(OUT) with respect to AGND1                                 | 5                                 |      |

|                  | VIN_LDO12, VIN_LDO35, LDO3, LDO4, LDO5 with respect to AGND2 | -0.3 to V(OUT)                    |      |

|                  | LDO35_REF, ADC_REF with respect to AGND2                     | -0.3 to smaller of: 3.6 or V(OUT) |      |

|                  | SIM, RTC_OUT with respect to AGND1                           | -0.3 to smaller of: 3.6 or V(OUT) |      |

|                  | SM1, L1, VIN_SM1 with respect to PGND1                       | -0.3 to V(OUT)                    | V    |

|                  | SM2, L2, VIN_SM2 with respect to PGND2                       | -0.3 to V(OUT)                    |      |

|                  | SM3, L3 with respect to PGND3                                | -0.3 to 29                        |      |

|                  | SM3SW with respect to PGND3                                  | -0.3 to V(OUT)                    |      |

|                  | FB3 with respect to PGND3                                    | -0.3 to 0.5                       |      |

|                  | All other pins (except AGND and PGND), with respect to AGND1 | -0.3 to V(OUT)                    |      |

|                  | AGND2, AGND0, PGND1, PGND2, PGND3 with respect to AGND1      | -0.3 to +0.3                      |      |

|                  | Input Current, AC pin                                        | 2750                              |      |

|                  | Input Current, USB pin                                       | 600                               |      |

|                  | Output continuous current, OUT pin                           | 3000                              | mA   |

|                  | Output continuous current, BAT pin                           | -3000                             |      |

|                  | Continuous Current at L1, PGND1, L2, PGND2                   | 1800                              |      |

| T <sub>A</sub>   | Operating free-air temperature                               | -40 to 85                         |      |

| TJ               | Maximum junction temperature                                 | 125                               |      |

| T <sub>STG</sub> | Storage temperature                                          | -65 to 150                        | °C   |

|                  | Lead temperature 1,6 mm (1/16-inch) from case for 10 seconds | 260                               | 1    |

|                  | ESD rating, all pins                                         | 1.5                               | kV   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

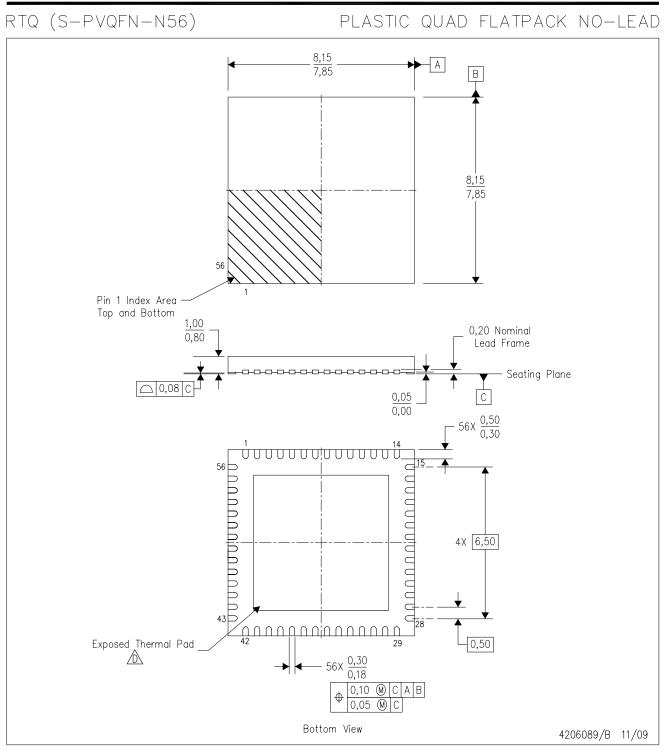

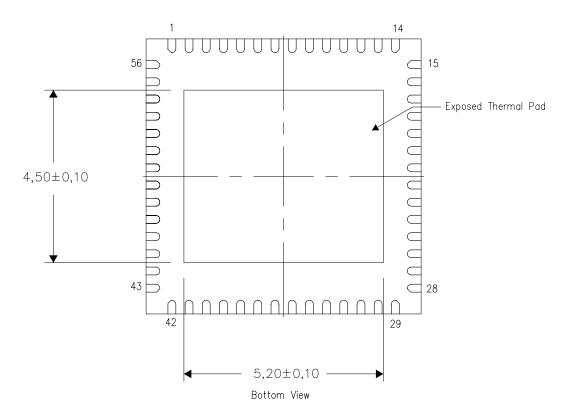

### DISSIPATION RATINGS

| PACKAGE                           | $\theta_{JA}$ | T <sub>A</sub> ≤ 55°C<br>POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 55°C |

|-----------------------------------|---------------|---------------------------------------|------------------------------------------------|

| RTQ <sup>(1)</sup> <sup>(2)</sup> | 21.7°C/W      | 3.22 W                                | 0.046 W/°C                                     |

(1) This data is based on using the JEDEC High-K board and the exposed die pad is connected to a Cu pad on the board. This is connected to the ground plane by a via matrix.

Pro lui Folde Lin (s): 79.65810 7956 58 1

(2) The RTQ package MSL level: HIR3 at 260°C

Submit Documentation Feedback

### **RECOMMENDED OPERATING CONDITIONS**

|                    |                                                          | MIN                                | MAX                 | UNIT |

|--------------------|----------------------------------------------------------|------------------------------------|---------------------|------|

|                    | AC and USB with respect to AGND1                         | 4.35                               | 16.5 <sup>(1)</sup> | V    |

|                    | ANLG1,ANLG2 with respect to AGND2                        | 0                                  | 2.6                 | V    |

|                    | VIN_LDO35 with respect to AGND2                          | Greater of: 3.6 V OR minimum input | 4.7                 |      |

|                    | VIN_LDO12 with respect to AGND1                          | voltage required for LDO/converter | 4.7                 | V    |

|                    | VIN_SM1 with respect to PGND1                            |                                    | 4.7                 | v    |

|                    | VIN_SM2 with respect to PGND2                            | -                                  | 4.7                 |      |

|                    | SM3 with respect to PGND3                                |                                    | 28                  | V    |

| T <sub>A</sub>     | Operating free-air temperature                           | -40                                | 85                  | С    |

| T <sub>J(op)</sub> | Junction temperature, functional operation assured       | -40                                | 125                 | С    |

| TJ                 | Junction temperature, electrical characteristics assured | 0                                  | 125                 | С    |

(1) Thermal operating restrictions are reduced or avoided if input voltage does not exceed 5 V.

TPS65810 TPS65811 SLVS658B-MARCH 2006-REVISED FEBRUARY 2007

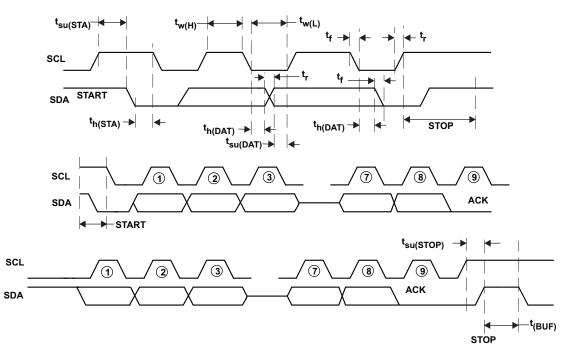

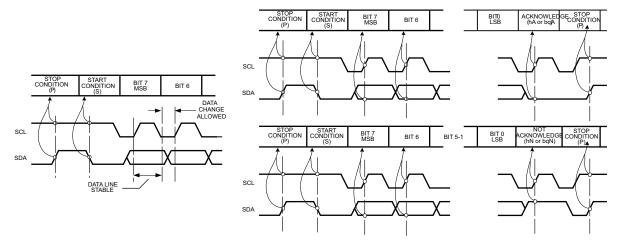

### ELECTRICAL CHARACTERISTICS – I<sup>2</sup>C INTERFACE

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}C$ ), application circuit as in Figure 3 (unless otherwise noted).

| PARAMETER                  | TEST CONDITIONS                                                      | MIN | TYP  | MAX | UNIT |

|----------------------------|----------------------------------------------------------------------|-----|------|-----|------|

| I <sup>2</sup> C TIMING CH | ARACTERISTICS                                                        |     |      |     |      |

| t <sub>R</sub>             | SCLK/SDATA rise time                                                 |     |      | 300 |      |

| t <sub>F</sub>             | SCLK/SDATA fall time                                                 |     |      | 300 | ns   |

| t <sub>W(H)</sub>          | SCLK pulse width high                                                | 600 |      |     |      |

| t <sub>W(L)</sub>          | SCLK Pulse Width Low                                                 | 1.3 |      |     | μs   |

| t <sub>SU(STA)</sub>       | Setup time for START condition                                       | 600 |      |     |      |

| t <sub>H(STA)</sub>        | START condition hold time after which first clock pulse is generated | 600 |      |     |      |

| t <sub>SU(DAT)</sub>       | Data setup time                                                      | 100 |      |     | ns   |

| t <sub>H(DAT)</sub>        | Data hold time                                                       | 0   |      |     |      |

| t <sub>SU(STOP)</sub>      | Setup time for STOP condition                                        | 600 |      |     |      |

| t <sub>(BUF)</sub>         | Bus free time between START and STOP condition                       | 1.3 |      |     | μs   |

| FSCL                       | Clock Frequency                                                      |     |      | 400 | kHz  |

| I <sup>2</sup> C INTERFAC  | E LOGIC LEVELS                                                       |     |      |     |      |

| V <sub>IH</sub>            | High level input voltage                                             | 1.3 |      | 6   | N    |

| V <sub>IL</sub>            | Low level input voltage                                              | 0   |      | 0.6 | V    |

| I <sub>H</sub>             | Input bias current                                                   |     | 0.01 |     | μA   |

Figure 2. I<sup>2</sup>C Timing

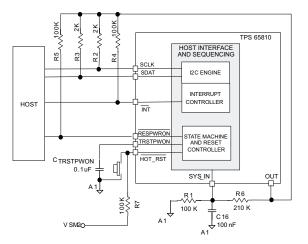

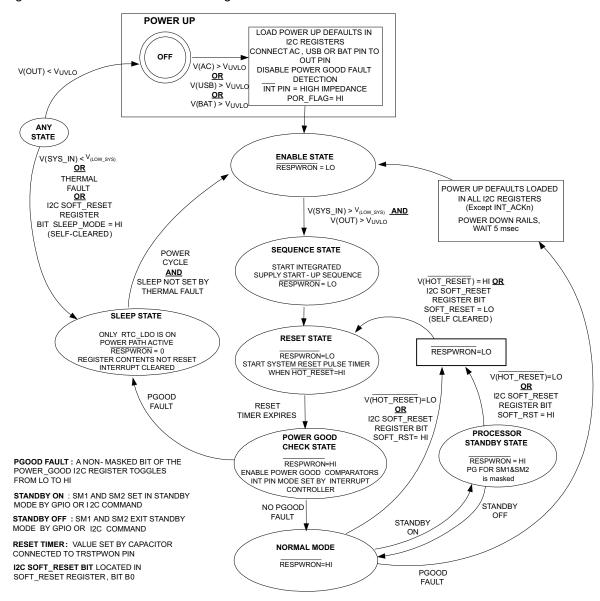

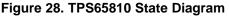

### ELECTRICAL CHARACTERISTICS – SYSTEM SEQUENCING AND OPERATING MODES

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}C$ ), application circuit as in Figure 3 (unless otherwise noted).

| F                        | PARAMETER                                      | TEST CONDITIONS                                                                                                                                                                | MIN  | TYP | MAX  | UNIT  |

|--------------------------|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| QUIESCENT                | CURRENT                                        | · · · · · ·                                                                                                                                                                    |      |     | 1    |       |

| I <sub>BAT(SLEEP)</sub>  | BAT pin current, sleep mode set                | Input power not detected, V(BAT) = 4.2 V, Sleep mode set                                                                                                                       |      | 400 |      | μΑ    |

| I <sub>BAT(DONE)</sub>   | BAT pin current, charge terminated             | Charger function enabled by I <sup>2</sup> C, termination detected, input power detected and selected                                                                          |      | 3   |      | μA    |

| IBAT(CHGOFF)             | BAT pin current, charge function OFF           | Charger function disabled by I <sup>2</sup> C, termination not detected, input power detected and selected                                                                     |      | 3   |      | μA    |

| I <sub>INP(CHGOFF)</sub> | AC or USB pin current, charge function OFF     | Charger function disabled by I <sup>2</sup> C, termination not detected,<br>input power detected and selected. All integrated supplies<br>and drivers OFF, no load at OUT pin. |      |     | 200  | μΑ    |

| UNDERVOLT                | AGE LOCKOUT                                    | · · · · · ·                                                                                                                                                                    |      |     | Ļ    |       |

| V <sub>UVLO</sub>        | Internal UVLO detection threshold              | NO POWER mode set at V(OUT) < V <sub>UVLO</sub> ,<br>V(OUT) decreasing                                                                                                         | -3%  | 2.5 | 3%   | V     |

| V <sub>UVLO_HYS</sub>    | UVLO detection<br>hysteresis                   | V(OUT) increasing                                                                                                                                                              |      | 120 |      | mV    |

| t <sub>DGL(UVLO)</sub>   | UVLO detection deglitch time                   | Falling voltage only                                                                                                                                                           |      | 5   |      | ms    |

| SYSTEM LOV               | V VOLTAGE THRESHOLD                            |                                                                                                                                                                                |      |     |      |       |

| V <sub>LOW_SYS</sub>     | Minimum system voltage detection threshold     | System voltage V(SYS_IN) decreasing, SLEEP mode set if V(SYS_IN) < $V_{LOW_SYS}$                                                                                               | 0.97 | 1   | 1.03 | V     |

| V <sub>HYS(LOWSYS)</sub> | Minimum system voltage detection hysteresis    | V(SYS_IN) increasing                                                                                                                                                           |      | 50  |      | mV    |

| t <sub>DGL(LOWSYS)</sub> | Minimum system voltage detection deglitch time | V(SYS_IN) decreasing                                                                                                                                                           |      | 5   |      | ms    |

| THERMAL FA               | ULT                                            |                                                                                                                                                                                |      |     |      |       |

| T <sub>SHUT</sub>        | Thermal shutdown                               | Increasing junction temperature                                                                                                                                                |      | 165 |      | °C    |

| T <sub>HYS(SHUT)</sub>   | Thermal shutdown<br>hysteresis                 | Decreasing junction temperature                                                                                                                                                |      | 30  |      | °C    |

| INTEGRATED               | SUPPLY POWER FAULT                             | DETECTION                                                                                                                                                                      |      |     | Ļ    |       |

| V <sub>PGOOD</sub>       | Power good fault detection threshold           | Falling output voltage, applies to all integrated supply outputs.<br>Referenced to the programmed output voltage value                                                         | 84%  | 90% | 96%  |       |

| V <sub>HYS(PGOOD)</sub>  | Power good fault detection hysteresis          | Rising output voltage, applies to all integrated supply outputs. Referenced to $V_{\text{PGOOD}}$ threshold                                                                    | 3%   | 5%  | 7%   |       |

| HOT RESET I              | FUNCTION                                       |                                                                                                                                                                                |      |     |      |       |

| V <sub>HRSTON</sub>      | Low level input voltage                        | RESET mode set at V(HOT_RESET) < V <sub>HRSTON</sub>                                                                                                                           |      |     | 0.4  | V     |

| V <sub>HRSTOFF</sub>     | High level input voltage                       | HOT reset not active at V(HOT_RESET) > V <sub>HRSTOFF</sub>                                                                                                                    | 1.3  |     |      | V     |

| t <sub>DGL(HOTRST)</sub> | Hot reset input deglitch                       |                                                                                                                                                                                |      | 5   |      | ms    |

| SYSTEM RES               | ET – OPEN DRAIN OUTP                           | UT RESPWRON                                                                                                                                                                    |      |     |      |       |

| V <sub>RSTLO</sub>       | Low level output voltage                       | I <sub>IL</sub> = 10 mA, V(RESPWRON) < V <sub>RSTLO</sub>                                                                                                                      | 0    |     | 0.3  | V     |

| ITRSTPWON                | Pull-up current source                         | Internally connected to TRSTPWRON pin                                                                                                                                          | 0.9  | 1.0 | 1.2  | μA    |

| K <sub>RESET</sub>       | Reset timer constant                           | $T_{RESET} = K_{RESET} \times C_{TRSTPWON}$                                                                                                                                    |      | 1   |      | ms/nF |

Prc lu Fulde Lin (s): P 65810 PS 68 1

Submit Desumentation Feedback

Copyright © 2005 2007 Texas Instruments Incorporated

# ELECTRICAL CHARACTERISTICS – POWER PATH AND CHARGE MANAGEMENT

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}C$ ), circuit as in Figure 3 (unless otherwise noted).

|                         | PARAMETER                                                             | TEST CONDITIO                                                                                                            | NS                               | MIN | TYP  | MAX  | UNIT  |

|-------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------|-----|------|------|-------|

| VOLTAGE D               | ETECTION THRESHOLDS                                                   |                                                                                                                          |                                  |     |      |      |       |

| V <sub>IN(DT)</sub>     | Input Voltage detection<br>threshold                                  | AC detected at V(AC)– V(BAT) > $V_{IN(DT)}$ ;<br>USB detected at V(USB)– V(BAT) > $V_{IN(DT)}$                           |                                  | 190 |      |      | mV    |

| V <sub>IN(NDT)</sub>    | Input Voltage removal threshold                                       | AC not detected at V(AC)– V(BAT) < V <sub>IN(NDT)</sub> ;<br>USB not detected at V(USB)– V(BAT) < V <sub>IN(NDT)</sub> ; | )T)                              |     |      | 125  | mV    |

| t <sub>DGL(NDT)</sub>   | Power not detected deglitch                                           |                                                                                                                          | ,                                |     | 22.5 |      | ms    |

| V <sub>SUP(DT)</sub>    | Supplement detection threshold                                        | Battery switch ON at V(BAT) – V(OUT) > V <sub>SUP</sub>                                                                  | (DT)                             |     | 60   |      | mV    |

| V <sub>SUP(NDT)</sub>   | Supplement not detected threshold                                     | Battery switch OFF at V(BAT)– V(OUT) < V <sub>SUF</sub>                                                                  | P(NDT)                           |     | 20   |      | mV    |

| POWER PA                | TH INTEGRATED MOSFETs CH                                              | HARACTERISTICS                                                                                                           |                                  |     |      |      |       |

| V <sub>ACDO</sub>       | AC switch dropout voltage                                             | V <sub>ACDO</sub> = V(AC)– V(OUT); V(AC) = 4.75 V AC i<br>(typ), I <sub>O(OUT)</sub> = 1.0 A                             | nput current limit set to 2.75 A |     | 350  | 375  | mV    |

| V <sub>USBDO</sub>      | USB switch dropout voltage                                            | V <sub>USBDO</sub> = V(USB)– V(OUT); V(USB) = 4.6 V                                                                      | I(OUT)+ I(BAT)= 0.5 A            |     | 175  | 190  | mV    |

| 03600                   |                                                                       | USB input current limit set to 2.75 A (typ)                                                                              | I(OUT)+ I(BAT)= 0.1 A            |     | 35   | 45   | mV    |

| VBATDODCH               | Battery switch dropout<br>voltage, discharge                          | V(BAT): 3 V $\rightarrow$ V <sub>CH(REG)</sub> , I(BAT) = -1 A                                                           |                                  |     | 60   | 100  | mV    |

| VBATDOCH                | Battery switch dropout voltage, charge                                | Charger on, V(BAT): 3 V $\rightarrow$ 4.2 V, I(BAT) = 1 .                                                                | A                                |     | 60   | 100  | mV    |

| POWER PA                | TH INPUT CURRENT LIMIT                                                |                                                                                                                          |                                  |     |      |      |       |

| I <sub>INP(LIM1)</sub>  | Selected input current limit, applies to USB input only               | Selected input switch not in dropout, I <sup>2</sup> C settin                                                            | gs: ISET2 = LO, PSEL = LO        | 80  |      | 100  | mA    |

| I <sub>INP(LIM2)</sub>  | Selected Input current limit, applies to USB input only               | Selected input switch not in dropout, I <sup>2</sup> C settings: ISET2 = HI, PSEL = LO                                   |                                  | 400 |      | 500  | mA    |

| I <sub>INP(LIM3)</sub>  | Selected Input current limit,<br>applies to either AC or USB<br>input | Selected input switch not in dropout, I <sup>2</sup> C settings: ISET2 = HI OR LO, PSEL = HI                             |                                  |     |      | 2.75 | А     |

| SYSTEM RE               | GULATION VOLTAGE                                                      |                                                                                                                          |                                  |     |      |      |       |

| V <sub>SYS(REG)</sub>   | Output regulation voltage                                             | V <sub>SYS(REG)</sub> = V(OUT), DPPM loop not active, se reached. Selected input voltage (AC or USB) >                   |                                  |     | 4.6  | 4.7  | V     |

| POWER PA                | TH PROTECTION AND RECOV                                               | ERY FUNCTIONS                                                                                                            |                                  | 1   |      |      |       |

| VINOUTSH                | Input-to-output short-circuit detection threshold                     | AC and USB switches set to OFF if V(OUT) <                                                                               | V <sub>INOUTSH</sub>             |     | 0.6  |      | V     |

| R <sub>SH(USBSH)</sub>  | OUT short circuit recovery<br>pullup resistor                         | V(OUT) < 1 V, internal resistor connected from                                                                           | n USB to OUT                     |     | 500  |      | Ω     |

| R <sub>SH(ACSH)</sub>   | OUT short circuit recovery<br>pullup resistor                         | V(OUT) < 1 V, internal resistor connected from                                                                           | AC to OUT                        |     | 500  |      | Ω     |

|                         | Overvoltage detection threshold                                       | Rising voltage, overvoltage detected when V( $A$ V(USB) > V <sub>OVP</sub>                                               | $AC) > V_{OVP}$ or               | 6   | 6.5  | 6.8  |       |

| V <sub>OVP</sub>        | Overvoltage detection hysteresis                                      | Falling voltage, relative to detection threshold                                                                         |                                  |     | 0.1  |      | V     |

| VBATOUTSH               | Battery-to-output short-circuit detection threshold                   | BAT switch set to OFF if V(BAT) – V(OUT) > V                                                                             | BATOUTSH                         |     | 200  |      | mV    |

| K <sub>BLK(SHBAT)</sub> | Battery-to-ouput short-circuit<br>blanking time constant              | V(DPPM) < 1v, t <sub>BLK(SHBAT)</sub> = K <sub>BLK(SHBAT)</sub> X C <sub>DPI</sub><br>connected from DPPM pin to AGND1   | $P_{PM,} C_{DPPM}$ capacitor is  |     | 1    |      | mS/nF |

| I <sub>SH(BAT)</sub>    | OUT short circuit recovery pullup current source                      | $V_{(BAT)} - V_{(OUT)} > V_{BATOUTSH}$ ,<br>Internal current source connected between OL                                 | JT and BAT                       |     | 10   |      | mA    |

| R <sub>SH(BAT)</sub>    | BAT short circuit recovery resistor                                   | V <sub>(BAT)</sub> < 1V,<br>Internal resistor connected from OUT to BAT                                                  |                                  |     | 1    |      | kΩ    |

| R <sub>DCH(BAT)</sub>   | BAT pulldown resistor                                                 | Internal resistor connected from BAT to AGND by ANLG1                                                                    | 1 when battery is not detected   |     | 500  |      | Ω     |

Prc lui Folde Lin (s): P65810 TES 58 1

### ELECTRICAL CHARACTERISTICS – POWER PATH AND CHARGE MANAGEMENT (Continued)

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}C$ ), application circuit as in Figure 3 (unless otherwise noted).

|                         | PARAMETER                                             |                                                                                        | CONDITIONS                                                                                        | MIN   | TYP                 | MAX   | UNIT   |

|-------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------|---------------------|-------|--------|

| POWER PA                | TH TIMING CHARACTERISTICS, DPP                        | AND THERMAL LOOPS NOT                                                                  | Γ ACTIVE, $R_{TMR}$ = 50 kΩ                                                                       | -1    |                     |       |        |

| t <sub>BOOT</sub>       | Boot-up time                                          | Measured from input power of                                                           |                                                                                                   | 120   | 200                 | 300   | ms     |

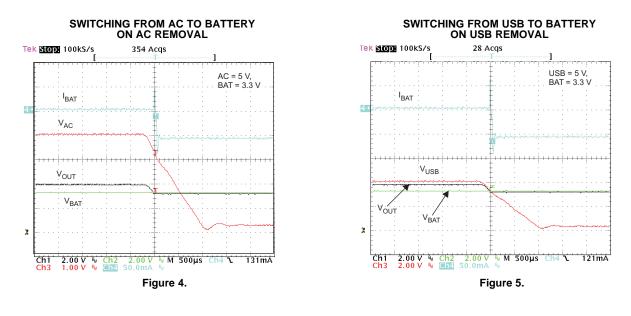

| t <sub>SW(ACBAT)</sub>  | Switching from AC to BAT                              | No USB: measured from V(A<br>detected:CE=LO (after CE he                               | No USB: measured from V(AC)– V(BAT) < $V_{IN(NDT)}$ , USB detected:CE=LO (after CE hold-off time) |       |                     | 50    | μs     |

| <sup>I</sup> SW(USBBAT) | Switching from USB to BAT                             | No AC: measured from V(US detected:CE=LO (after CE he                                  |                                                                                                   |       |                     | 50    | μs     |

| <sup>t</sup> SW(PSEL)   | Switching from USB to AC                              | Toggling I <sup>2</sup> C PSEL bit                                                     |                                                                                                   |       |                     | 50    | μs     |

| t <sub>SW(ACUSB)</sub>  | Switching from AC to USB or USB to AC                 | AC power removed or USB p                                                              | power removed                                                                                     |       |                     | 100   | μs     |

| BATTERY R               | EMOVAL DETECTION                                      |                                                                                        |                                                                                                   |       |                     |       |        |

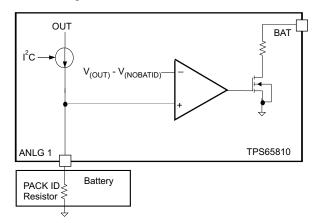

| V <sub>NOBATID</sub>    | Battery ID resistor detection                         | ID resistor not detected at V(                                                         | OUT)– V(ANLG1) < V <sub>NOBATID</sub>                                                             |       | 0.5                 |       | V      |

| t <sub>DGL(NOBAT)</sub> | Deglitch time for battery removal<br>detection        |                                                                                        |                                                                                                   | 0.6   |                     | 1.2   | ms     |

|                         |                                                       | Set via I <sup>2</sup> C bits                                                          | 00, $V_{(OUT)}\!\!:$ 2.5 V to 4.4 V                                                               |       | UT) – 1.:<br>500 kΩ | 2     |        |

|                         | ANI G1 pullup current                                 | (BATID1,BATID2)                                                                        | 01                                                                                                |       | 10                  |       | μA     |

| O(ANLG1)                | ANLG1 pullup current                                  | ADC_WAIT register                                                                      | 10                                                                                                |       | 50                  |       |        |

|                         |                                                       |                                                                                        | 11                                                                                                |       | 60                  |       |        |

|                         |                                                       | Total accuracy                                                                         |                                                                                                   | 25%   |                     | 25%   |        |

| FAST CHAR               | RGE CURRENT, V(OUT) > V(BAT) + 0.1                    | V, V(BAT) > V <sub>LOWV</sub>                                                          |                                                                                                   |       |                     | 1     |        |

| I <sub>O(BAT)</sub>     | Charge current range                                  | $I_{O(BAT)} = \frac{K_{(SET)} \times V_{(SET)}}{R_{SET}}$                              |                                                                                                   | 100   |                     | 1500  | mA     |

|                         |                                                       |                                                                                        | 11, 100% scaling                                                                                  | 2.475 | 2.500               | 2.525 |        |

| V <sub>SET</sub>        |                                                       | V <sub>SET</sub> = V(ISET1),                                                           | 10, 75% scaling                                                                                   | 1.875 | 1.900               | 1.925 |        |

|                         | Battery charge current set voltage                    | (ISET1_1, ISET1_0) =                                                                   | 01, 50% scaling                                                                                   | 1.225 | 1.250               | 1.275 | V      |

|                         |                                                       |                                                                                        | 00, 25% scaling                                                                                   |       | 0.600               | 0.625 |        |

|                         |                                                       | 100 mA < I <sub>O(BAT)</sub> ≤ 1 A                                                     |                                                                                                   | 0.575 | 400                 | 450   |        |

| K <sub>SET</sub>        | Battery charge current set factor                     | $1 \text{ mA} < I_{O(BAT)} \le 100 \text{ mA}$                                         |                                                                                                   | 100   | 400                 | 1000  |        |

| PRE-CHAR                | GE CURRENT, V(OUT) > V(BAT) + 0.1                     | - ( )                                                                                  |                                                                                                   |       |                     |       |        |

| O(PRECHG)               | Precharge current range                               | $I_{O(PRECHG)} = \frac{V_{(PRECHG)}}{R_{SE}}$                                          |                                                                                                   | 10    |                     | 150   | mA     |

| V <sub>PRECHG</sub>     | Precharge set voltage                                 | V <sub>PRECHG</sub> = V(ISET1)                                                         |                                                                                                   | 220   | 250                 | 270   | m∖     |

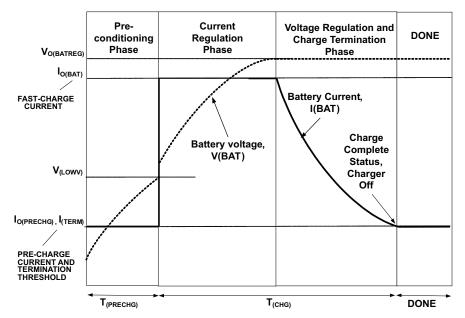

| VLOWV                   | Precharge to fast-charge transition                   | Fast charge at V(BAT) > V <sub>LO</sub>                                                | WV                                                                                                | 2.8   | 3                   | 3.2   | V      |

| t <sub>DGL(PRE)</sub>   | Deglitch time for fast charge to precharge transition | Decreasing battery voltage, R                                                          | R <sub>TMR</sub> = 50 kΩ                                                                          |       | 22.5                |       | ms     |

| CHARGE RI               | EGULATION VOLTAGE, $V(OUT) > V_{O(E)}$                | ATREG) + 0.1V                                                                          |                                                                                                   |       |                     |       |        |

|                         |                                                       | Voltage options, selection via                                                         | a l <sup>2</sup> C                                                                                |       | 4.2<br>4.356        |       | V<br>V |

| V <sub>O(BATREG)</sub>  | Battery charge voltage                                | Accuracy, T <sub>A</sub> = 25°C                                                        |                                                                                                   | -0.5% | 1.000               | 0.5%  | v      |

|                         |                                                       | Total accuracy                                                                         |                                                                                                   | -1%   |                     | 1%    |        |

| CHARGE TE               | ERMINATION, V(BAT) > V <sub>RCH</sub> , VOLTAG        |                                                                                        |                                                                                                   | 170   |                     | 170   |        |

|                         |                                                       |                                                                                        |                                                                                                   |       |                     |       |        |

| TERM                    | Charge termination current range                      | $I_{(\text{TERM})} = \frac{V_{(\text{TERM})} \times K_{(\text{SET})}}{R_{\text{SET}}}$ |                                                                                                   | 10    |                     | 150   | mA     |

|                         |                                                       |                                                                                        | 11, 100% scaling                                                                                  | 240   | 260                 | 280   |        |

| N/                      | Battery termination detection set                     | V <sub>TERM</sub> = V(ISET1),                                                          | 10, 75% scaling                                                                                   | 145   | 160                 | 175   |        |

| V <sub>TERM</sub>       | voltage                                               | (ISET1_1, SET1_0) =                                                                    | 01, 50% scaling                                                                                   | 90    | 110                 | 130   | m∖     |

|                         |                                                       | 00, 25% scaling                                                                        |                                                                                                   | 40    | 60                  | 75    |        |

| t <sub>DGL(TERM)</sub>  | Deglitch time for termination detection               | $V(ISET1) < V_{TERM}, R_{TMR} = 50$                                                    | 0 κΩ                                                                                              |       | 22.5                |       | ms     |

Submit Desumentation Feedback

# ELECTRICAL CHARACTERISTICS – POWER PATH AND CHARGE MANAGEMENT (Continued)

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}C$ ), circuit as in Figure 3 (unless otherwise noted).

|                       | PARAMETER                                               | TEST CONDITIONS                                                                                                   | MIN   | ТҮР                       | MAX   | UNIT |

|-----------------------|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-------|---------------------------|-------|------|

| BATTERY               | RECHARGE DETECTION                                      |                                                                                                                   |       |                           |       |      |

| V <sub>RCH</sub>      | Recharge threshold voltage                              | New charge cycle starts if V(BAT) < V_{O(BATREG)} - V_{RCH}, after termination was detected                       | 80    | 100                       | 130   | mV   |

| t <sub>DGL(RCH)</sub> | Deglitch time for recharge detection                    | $R_{TMR} = 50 \text{ k}\Omega$                                                                                    |       | 22.5                      |       | ms   |

| DPPM FU               | NCTION                                                  |                                                                                                                   |       |                           |       |      |

| V <sub>DPPM</sub>     | DPPM regulation point range                             | $V_{(DPPM)} = R_{DPPM} \times K_{DPPMM} \times I_{O(DPPM)}$                                                       | 2.6   |                           | 4.4   | V    |

| I <sub>O(DPPM)</sub>  | DPPM pin current source                                 | AC or USB Present                                                                                                 | 95    | 100                       | 105   | μΑ   |

| K <sub>DPPM</sub>     | DPPM scaling factor                                     |                                                                                                                   | 1.139 | 1.15                      | 1.162 |      |

| t <sub>DGL(DPPM</sub> | DPPM de-glitch time                                     | Status bit set indicating DPPM loop active after deglitch time, $R_{TMR}$ = 50 $k\Omega$                          |       | 500                       |       | μs   |

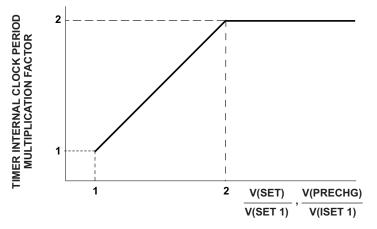

| CHARGE                | AND PRE-CHARGE SAFETY TIN                               | /IER                                                                                                              |       |                           |       |      |

| t <sub>CHG</sub>      | Charge safety timer<br>programmed value                 | Safety timer range, thermal/DPPM loop not active, $t_{CHG} = R_{TMR} \times K_{TMR}$                              | 3     | 5                         | 10    | h    |

| K <sub>TMR</sub>      | Charge timer set factor                                 |                                                                                                                   | 0.313 | 0.36                      | 0.414 | s/Ω  |

| t <sub>CHGADD</sub>   | Total elapsed time when DPPM or thermal loop are active | Fast charge on, $t_{\text{CHGADD}}$ is the maximum add-on time added to $t_{\text{CHG}}$                          |       | $2 \times t_{\text{CHG}}$ |       | h    |

| t <sub>PRECHG</sub>   | Precharge safety timer<br>programmed value              | Pre charge safety timer range, thermal/DPPM loop not active, $t_{PRECHG} = K_{PRE} \times R_{TMR} \times K_{TMR}$ | 18    | 30                        | 60    | min  |

| K <sub>PRE</sub>      | Pre-charge timer set factor                             |                                                                                                                   | 0.09  | 0.1                       | 0.11  |      |

| t <sub>PCHGADD</sub>  | Total elapsed time when DPPM or thermal loop are active | Pre-charge on, $t_{\text{PCHGADD}}$ is the maximum add-on time added to $t_{\text{PRECHG}}$                       |       | $2 	imes t_{PRECHG}$      |       | h    |

| R <sub>TMR</sub>      | External timer resistor limits                          |                                                                                                                   | 30    |                           | 100   | kΩ   |

| R <sub>TMR(FLT)</sub> | Timer fault recovery pullup resistor                    | Internal resistor connected from OUT to BAT after safety timer timeout                                            |       | 1                         |       | kΩ   |

| THERMAL               | REGULATION LOOP                                         | ·                                                                                                                 |       |                           |       |      |

| T <sub>THREG</sub>    | Temperature regulation limit                            | Charge current decreased and timer extended when $T_J > T_{THREG}$                                                | 115   |                           | 135   | °C   |

| CHARGE                | R THERMAL SHUTDOWN                                      | · · · · · · · · · · · · · · · · · · ·                                                                             |       |                           |       |      |

| T <sub>THCHG</sub>    | Charger thermal shutdown                                | Charger turned off when T <sub>J</sub> >T <sub>THCHG</sub>                                                        |       | 150                       |       |      |

| T <sub>HCHGHYS</sub>  | Charger thermal shutdown hystersis                      |                                                                                                                   |       | 30                        |       | °C   |

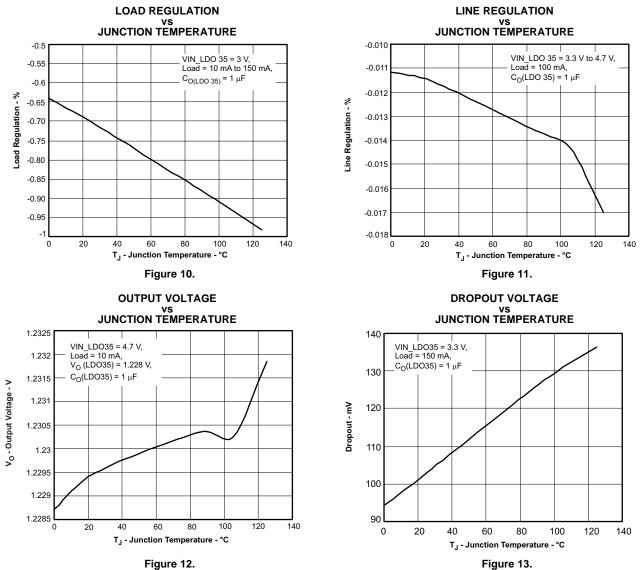

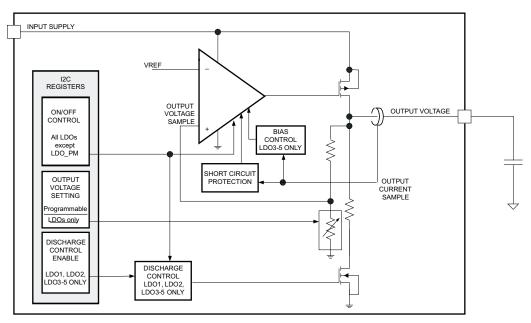

#### **ELECTRICAL CHARACTERISTICS – LINEAR REGULATORS**

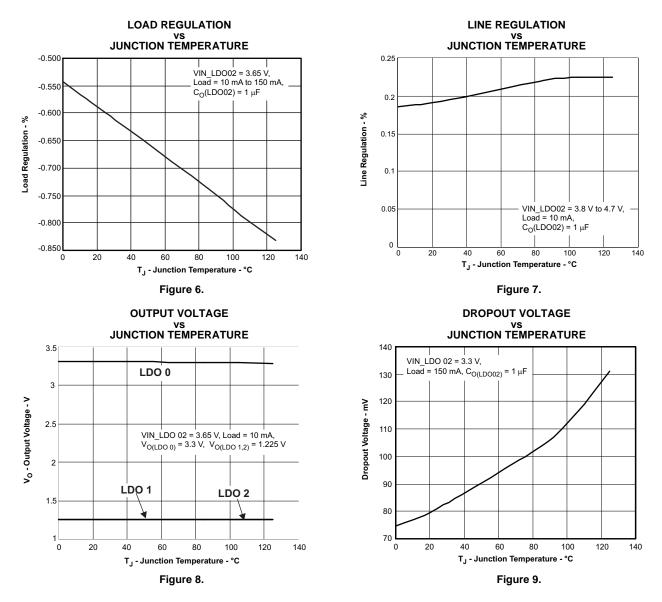

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}C$ ), application circuit Figure 3 (unless otherwise noted).

|                          | PARAMETER                                                     | TEST CONDITIONS                                                                                                  | MIN TYP MAX                                                                                         | UNIT |

|--------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------|

| SELECTABL                | E OUTPUT VOLTAGE LDO'S: LDO1                                  | LDO2                                                                                                             |                                                                                                     |      |

| I <sub>Q(LDO12)</sub>    | Quiescent current, either LDO1 or LDO2 enabled, LDO0 disabled | $I_{Q(LDO12)} = I(VIN\_LDO02) \qquad \qquad \frac{I_{(LDO1,2)} = -1 \text{ mA}}{I_{(LDO1,2)} = -150 \text{ mA}}$ | 15<br>160                                                                                           | μΑ   |

| I <sub>O(LDO1,2)</sub>   | Output current range                                          | (LD01,2) = 100 m/t                                                                                               | 150                                                                                                 | mA   |

| V <sub>O(LDO1,2)</sub>   |                                                               | Output Voltage, Selectable via I <sup>2</sup> C.                                                                 | Available output voltages:<br>V <sub>O(LDD1,2</sub> TYP = 1.25, 1.5, 1.8,<br>2.5, 2.85, 3, 3.2, 3.3 |      |

|                          |                                                               | Dropout voltage, 150 mA load                                                                                     | 300                                                                                                 | mV   |

|                          | LDO1, LDO2 Output Voltage                                     | Total accuracy, V(VIN_LDO02) = 3.65 V                                                                            | -3% 3%                                                                                              |      |

|                          |                                                               | Line Regulation, 100 mA load, V(VIN_LDO02): V <sub>(LD01.2)TYP</sub> + 0.5 V $\rightarrow$ 4.7 V                 | -1% 1%                                                                                              |      |

|                          |                                                               | Load regulation, load: 10 mA $\rightarrow$ 150 mA V(VIN_LDO02) > V <sub>O(LDO1,2)</sub> TYP + 0.5V               | -1.5% 1.5%                                                                                          |      |

| P <sub>SR(LDO12)</sub>   | PSRR at 20 kHz                                                | 150mA load at output, V(VIN_LDO02) - V <sub>O(LDO1,2)</sub> =1V                                                  | 40                                                                                                  | dB   |

| I <sub>SC(LDO1,2)</sub>  | LDO1&2 short circuit current limit                            | Output grounded                                                                                                  | 300                                                                                                 | mA   |

| R <sub>DCH(LDO1,2)</sub> | Discharge resistor                                            | LDO disabled by I <sup>2</sup> C command                                                                         | 300                                                                                                 | Ω    |

| ILKG(LDO1,2)             | Leakage current                                               | LDO off                                                                                                          | 2                                                                                                   | μΑ   |

| SIM LINEAR               | REGULATOR                                                     |                                                                                                                  |                                                                                                     |      |

| I <sub>Q(SIM)</sub>      | Quiescent current                                             | Internally connected to OUT pin                                                                                  | 20                                                                                                  | μΑ   |

| I <sub>O(SIM)</sub>      | Output current range                                          |                                                                                                                  | 8                                                                                                   | mA   |

|                          |                                                               | Output voltage, selectable via I <sup>2</sup> C.                                                                 | Available output voltages:<br>V <sub>O(SIM)TYP</sub> = 1.8 or 2.5                                   | V    |

|                          |                                                               | Dropout voltage, 8 mA load                                                                                       | 0.2                                                                                                 | V    |

| V <sub>O(SIM)</sub>      | SIM LDO output voltage                                        | Total accuracy, V(OUT): 3.2 V to 4.7 V, 8 mA                                                                     | -5% 5%                                                                                              |      |

| O(OIM)                   |                                                               | Load regulation, load: 1 mA $\rightarrow$ 8 mA, V(OUT) > V_{O(SIM) TYP} + 0.5 V                                  | -3% 3%                                                                                              |      |

|                          |                                                               | Line regulation, 5 mA load, V(OUT): $V_{O(SIM) TYP}$ + 0.5 V $\rightarrow$ 4.7 V                                 | -2% 2%                                                                                              |      |

| I <sub>SC(SIM)</sub>     | Short-circuit current limit                                   | Output grounded                                                                                                  | 20                                                                                                  | mA   |

| I <sub>LKG(SIM)</sub>    | Leakage current                                               | LDO off                                                                                                          | 1                                                                                                   | μΑ   |

| PROGRAM                  | IABLE OUTPUT VOLTAGE LDO'S: L                                 | DO3, LDO4, LDO5                                                                                                  |                                                                                                     |      |

| I <sub>Q(LDO35)</sub>    | Quiescent current, only one of LDO3, LDO4, LDO5 is enabled    | I <sub>Q(LDO35)</sub> = I(VIN_LDO35)                                                                             | 70                                                                                                  | μΑ   |

| I <sub>O(LDO35)</sub>    | Output current range                                          |                                                                                                                  | 100                                                                                                 | mA   |

|                          |                                                               | Output voltage, selectable via I <sup>2</sup> C                                                                  | Available output voltages:<br>V <sub>O(LDO35)TYP</sub> = 1.224 V to<br>4.46 V, 25-mV steps          | V    |

|                          |                                                               | Dropout voltage, 100-mA load                                                                                     | 240                                                                                                 | mV   |

| V <sub>O(LDO35)</sub>    | LDO3, LDO4, LDO5 output voltage                               | Total accuracy, 100 mA load V <sub>(VIN_LDO35)</sub> = 5 V                                                       | -3% 3%                                                                                              |      |

|                          |                                                               | Load regulation, V(VIN_LDO35) > V <sub>O(LDO35)TYP</sub> + 0.5 V, load mA $\rightarrow$ 50 mA                    | : 1 _1% 1%                                                                                          |      |

|                          |                                                               | Line regulation, 10-mA load, V(VIN_LDO35): V_{O(LDO35)TYP} + 0.5 V $\rightarrow$ 4.7 V                           | -1% 1%                                                                                              |      |

| SC(LDO35)                | Short-circuit current limit                                   | Output grounded                                                                                                  | 250                                                                                                 | mA   |

| PSR <sub>(LDO35)</sub>   | PSRR at 10 kHz                                                | $V(VIN\_LDO35) > V_{O(LDO3,5)} +1 V, 50 mA load at output$                                                       | 40                                                                                                  | dB   |

| R <sub>DCH(LDO35)</sub>  | Discharge resistor                                            | LDO is disabled by I <sup>2</sup> C command                                                                      | 400                                                                                                 | Ω    |

| ILKG(LDO35)              | Leakage current                                               | LDO off                                                                                                          | 1                                                                                                   | μA   |

## **ELECTRICAL CHARACTERISTICS – LINEAR REGULATORS (continued)**

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}$ C), application circuit as in Figure 3 (unless otherwise noted).

| PARAMETER                | TEST CONDITIONS | MIN | ТҮР | MAX | UNIT |

|--------------------------|-----------------|-----|-----|-----|------|

| RTC_OUT LINEAR REGULATOR |                 |     |     |     |      |

Copyright © 2006–2007, Texas Instruments Incorporated Pro IU Folde Lin (s): 1765810 12568 1

# ELECTRICAL CHARACTERISTICS – LINEAR REGULATORS (continued) (continued)

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}C$ ), application circuit as in Figure 3 (unless otherwise noted).

| I <sub>Q(RTC_OUT)</sub>  | Quiescent current for RTC LDO | Internally connected to OUT pin                                                   |                           |       | 20  |      | μΑ |

|--------------------------|-------------------------------|-----------------------------------------------------------------------------------|---------------------------|-------|-----|------|----|

| I <sub>O(RTC_OUT)</sub>  | Output current range          |                                                                                   |                           |       |     | 8    | mA |

|                          |                               | Fixed output voltage value                                                        |                           |       | 1.5 |      | V  |

|                          |                               | Dropout voltage, I(RTC_OUT) = -8 m                                                | hΑ                        |       |     | 200  | mV |

| V <sub>O(RTC OUT)</sub>  | RTC OUT output voltage        | Total accuracy, V(OUT): 2 V to 4.7 V sleep mode not set                           | , 8 mA load,              | -5%   |     | 5%   |    |

| • O(RTC_OUT)             |                               | Load regulation, load: 1 mA $\rightarrow$ 8 mA,<br>2 V < V(OUT) < 4.7 V           |                           | -3%   |     | 3%   |    |

|                          |                               | Line regulation, 5-mA load V(OUT): 2 V $\rightarrow$ 4.7 V                        |                           | -2%   |     | 2%   |    |

| I <sub>SH(RTC_OUT)</sub> | Short-circuit current limit   | V(RTC_OUT) = 0 V                                                                  |                           |       | 20  |      | mA |

|                          |                               | V(RTC_OUT) = 1.5 V,                                                               | $T_J = 85^{\circ}C$       |       | 880 |      |    |

| LKG(RTC_OUT)             | Leakage current               | V(OUT) = 0 V                                                                      | $T_J = 25^{\circ}C$       |       | 250 |      | nA |

| LDO0 LINEAR              | REGULATOR                     |                                                                                   |                           |       |     |      |    |

| I <sub>Q(LDO0)</sub>     | Quiescent current             |                                                                                   | I(LDO0) = -1 mA           |       | 15  |      | ۵  |

|                          |                               |                                                                                   | I(LDO0) = -150 mA         |       | 160 |      | μA |

| I <sub>O(LDO0)</sub>     | Output current range          |                                                                                   |                           |       |     | 150  | mA |

|                          |                               | Fixed output voltage value<br>Dropout voltage, I(LDO0) = -150 mA                  |                           |       | 3.3 |      | V  |

|                          |                               |                                                                                   |                           |       |     | 300  | mV |

| V <sub>O(LDO0)</sub>     | Output voltage                | Total accuracy                                                                    |                           | -3%   |     | 3%   |    |

| • O(LDO0)                | Output Voltage                | Line regulation, V(OUT): V_{O(LDO0)} + 0.5 $\rightarrow$ 4.7 V, I(LDO0) = –100 mA |                           | -1%   |     | 1%   |    |

|                          |                               | Load regulation, I(LDO0) = $-10 \text{ mA} \rightarrow -150 \text{ mA}$           |                           | -1.5% |     | 1.5% |    |

| PSR <sub>(LDO0)</sub>    | PSRR at 20 kHz                | 150 mA load at output, V(VIN_LDO12                                                | $2) - V_{O(LDO1,2)} = 1V$ |       | 40  |      | dB |

| I <sub>SC(LDO0)</sub>    | Short circuit current limit   | V(LDO0) = 0 V                                                                     |                           |       | 300 |      | mA |

| I <sub>LKG(LDO0)</sub>   | Leakage current               | LDO off                                                                           |                           |       | 1   |      | μΑ |

| LDO_PM LINE              | AR REGULATOR                  |                                                                                   |                           |       |     |      |    |

| I <sub>Q(LD0_PM)</sub>   | Output current range          |                                                                                   |                           |       |     | 20   | mA |

|                          |                               | Fixed output voltage value, V(OUT) >                                              | - 4V                      |       | 3.3 |      | V  |

| V <sub>O(LDO_PM)</sub>   | Output voltage                | Dropout voltage, I(LDOPM) = -12 mA                                                |                           |       | 0.5 | 0.7  | V  |

|                          |                               | Total accuracy                                                                    |                           | -5%   |     | 5%   |    |

| ILKG(LDOPM)              | Leakage current               | LDO off                                                                           |                           |       | 1   |      | μA |

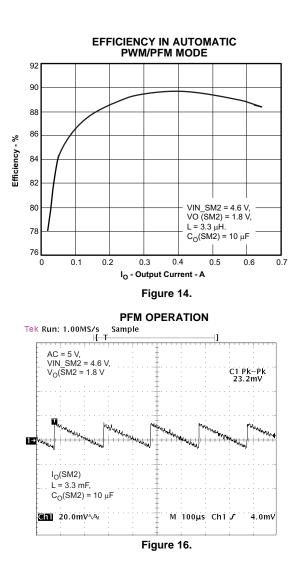

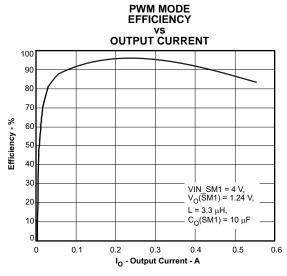

## ELECTRICAL CHARACTERISTICS – SWITCHED-MODE SM1 STEP-DOWN CONVERTER

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}C$ ),  $V_{O(SM1)} = 1.24$  V, application circuit Figure 3 (unless otherwise noted).

|                         | PARAMETER                         | TEST CONDITIONS                                                                                                               | MIN                                  | TYP                                                                                                       | MAX   | UNIT |     |

|-------------------------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------|-------|------|-----|

|                         | 0                                 | I <sub>Q(SM1)</sub> = I(VIN_SM1), no output load                                                                              | Not switching                        |                                                                                                           | 10    |      | •   |

| I <sub>Q(SM1)</sub>     | Quiescent current for SM1         | SM1 OFF, set via I <sup>2</sup> C                                                                                             |                                      |                                                                                                           | 0.1   |      | μA  |

| 1                       |                                   | Vin = 4.2 v, Vout = 1.24 V (TPS65810)                                                                                         | 600                                  |                                                                                                           |       | ٣Å   |     |

| I <sub>O(SM1)</sub>     | Output current range              | Vin = 4.2 v, Vout = 1.24 V (TPS65811)                                                                                         |                                      | 750                                                                                                       |       |      | mA  |

|                         |                                   | Output voltage, selectable via I <sup>2</sup> C, Standb                                                                       | y OFF                                | Available output<br>voltages: V <sub>O(SM1)TYP</sub> =<br>0.6 V to 1.8 V,<br>adjustable in 40-mV<br>steps |       |      |     |

| V <sub>O(SM1)</sub>     | Output voltage, PWM mode          | $V_{O(SM1)} = V_{SBY(SM1)}$ , Output voltage range                                                                            | , Standby ON                         | Available output<br>voltages: V <sub>SBY(SM1)</sub> =<br>0.6 V to 1.8 V,<br>adjustable in 40-mV<br>steps  |       |      | V   |

|                         |                                   | Total accuracy, $V_{O(SM1)TYP} = V_{SBY(SM1)} = 7$<br>V(VIN_SM1) = 3.0 V to 4.7 V; 0 mA ≤ I <sub>O(S</sub>                    | 1.24 V,<br><sub>M1)</sub> ≤ 600 mA   | -3%                                                                                                       |       | 3%   |     |

|                         |                                   | Line Regulation, V(VIN_SM1): 3.0 $\rightarrow$ 4.70 V, $I_{O(SM1)}$ = 10 mA                                                   |                                      | 0.027                                                                                                     |       |      | %/V |

|                         |                                   | Load Regulation, V(VIN_SM1) = 4.7 V, $I_{O(SM1)}$ : 60 mA $\rightarrow$ 540 mA                                                | Load Regulation, V(VIN_SM1) = 4.7 V, |                                                                                                           | 0.139 |      | %/A |

| R <sub>DSON(PSM1)</sub> | P-channel MOSFET<br>on-resistance | V(VIN_SM1) = 3.6 V, 100% duty cycle set                                                                                       | :                                    |                                                                                                           | 310   | 500  | mΩ  |

| I <sub>LKG(PSM1)</sub>  | P-channel leakage current         |                                                                                                                               |                                      |                                                                                                           | 0.1   |      | μA  |

| R <sub>DSON(NSM1)</sub> | N-channel MOSFET<br>on-resistance | V(VIN_SM1) = 3.6 V, 0% duty cycle set                                                                                         |                                      |                                                                                                           | 220   | 330  | mΩ  |

| ILKG(PSM1)              | N-channel leakage current         |                                                                                                                               |                                      |                                                                                                           | 5     |      | μA  |

| L                       | P- and N-channel current limit    | 3 V < V(VIN_SM1) < 4.7 V (TPS65810)                                                                                           |                                      | 900                                                                                                       | 1050  | 1200 | mA  |

| I <sub>LIM(SM1)</sub>   |                                   | 3 V < V(VIN_SM1) < 4.7 V (TPS65811)                                                                                           |                                      | 1000                                                                                                      | 1200  | 1400 | ША  |

| f <sub>S(SM1)</sub>     | Oscillator frequency              | PWM mode set                                                                                                                  |                                      | 1.3                                                                                                       | 1.5   | 1.7  | MHz |

| EFF <sub>(SM1)</sub>    | Efficiency                        | $ \begin{array}{ c c c } V(VIN\_SM1) = 4.2 \text{ V}, \text{ PWM mode, } I_{O(SM1)} \\ V_{O(SM1)} = 3 \text{ V} \end{array} $ | = 300 mA,                            |                                                                                                           | 90%   |      |     |

| t <sub>SS(SM1)</sub>    | Soft start ramp time              | Converter OFF $\rightarrow$ ON, V <sub>O(SM1)</sub> : 5% $\rightarrow$ 95% value                                              | of target                            |                                                                                                           | 750   |      | μs  |

| t <sub>DLY(SM1)</sub>   | Converter turn-on delay           | GPIO1 pin programmed as SM1 converted control. Measured from V(GPIO1): LO →                                                   |                                      | 170                                                                                                       |       | μs   |     |

Copyright © 2006–2007, Texas Instruments Incorporated Product Folde Lin (s): P65810 12568 1

Submit Decumentation Feedback

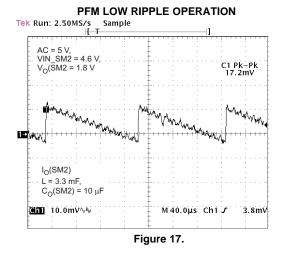

# ELECTRICAL CHARACTERISTICS – SWITCHED MODE SM2 STEP DOWN CONVERTER

Over recommended operating conditions (typical values at  $T_J = 25^{\circ}C$ ),  $V_{O(SM1)} = 1.24$  V, application circuit Figure 3 (unless otherwise noted).