SLUS608D - JANUARY 2005 REVISED NOVEMBER 2005

# ADVANCED PFC/PWM COMBINATION CONTROLLER WITH TRAILING-EDGE/TRAILING-EDGE MODULATION

#### **FEATURES**

- Provides Control of PFC and PWM Power Stages In One Device

- Trailing-Edge PFC, Trailing-Edge PWM Modulation

- Built-In Sequencing of PFC and PWM Turn-On

- 2-A Source and 3-A Sink Gate Drive for Both PFC and PWM Stages

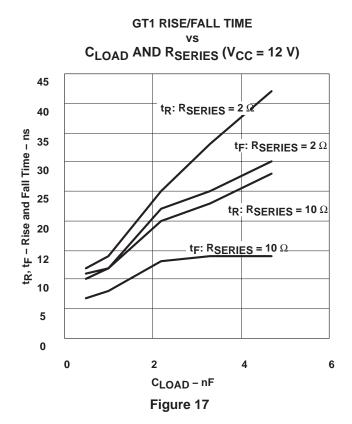

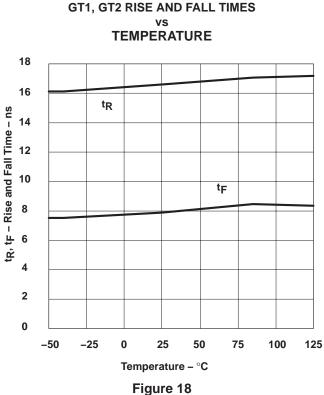

- Typical 16-ns Rise Time and 7-ns Fall Time into 1-nF Loads

#### **PFC Features**

- Average-Current-Mode Control for Continuous Conduction Mode Operation

- Highly-Linear Multiplier for Near-Unity Power Factor

- Input Voltage Feedforward Implementation

- Improved Load Transient Response

- Accurate Power Limiting

- Zero Power Detect

#### **PWM Features**

- Peak-Current-Mode Control Operation

- 1:1 PFC:PWM Frequency Option

- Programmable maximum Duty Cycle Limit Up to 90%

- Programmable Soft-Start

#### **APPLICATIONS**

- High-Efficiency Server and DesktopSupplies

- High-Efficiency Telecom AC-DC Converter

#### DESCRIPTION

The UCC28521 and UCC28528 combination PFC/PWM controllers provide complete control functionality for any off-line power system requiring compliance with the IEC1000-3-2 harmonic reduction requirements. By combining the control and drive signals for the PFC and the PWM stages into a single device, significant performance and cost benefits are gained.

Based on the UCC28511, the new devices employ an average current mode control architecture with input voltage feedforward. The major difference of the UCC28521/28 is the trailing-edge / trailing-edge (TEM/TEM) modulation scheme for the PFC/PWM stages. The UCC28528 differs from the UCC28521 as its PWM stage does not turn off with the falling bulk voltage. The UCC28528 PWM was designed for low power auxiliary supplies.

These devices offer performance advantages over earlier generation combination controllers. A key PWM feature is programmable maximum duty cycle. For the PFC stage, the devices feature an improved multiplier and the use of a transconductance amplifier for enhanced transient response.

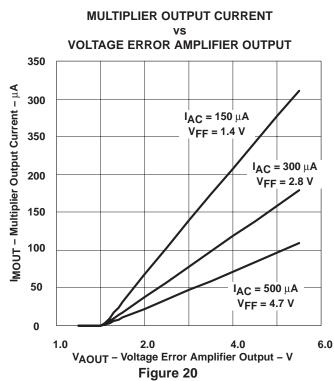

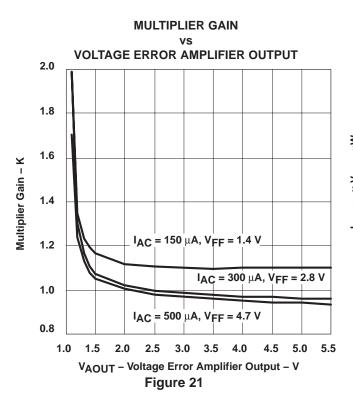

The core of the PFC section is in a three-input multiplier that generates the reference signal for the line current. The UCC28521/28 features a highly linearized multiplier circuit capable of producing a low distortion reference for the line current over the full range of line and load conditions. A low-offset, high-bandwidth current error amplifier ensures that the actual inductor current (sensed through a resistor in the return path) follows the multiplier output command signal. The output voltage error is processed through a transconductance voltage amplifier.

1

#### AVAILABLE APPLICATION OPTIONS

| PART NUMBER PWM STAGE |                                                  | APPLICATION                    |

|-----------------------|--------------------------------------------------|--------------------------------|

| UCC28521              | PWM shuts off at 71% of the nomonal bulk voltage | ac-dc and main dc-dc converter |

| UCC28528              | PWM does not turn off with falling bulk voltage  | ac-dc and standby converter    |

www.ti.com

#### **DESCRIPTION (CONTINUED)**

The transient response of the circuit is enhanced by allowing a much faster charge/discharge of the voltage amplifier output capacitance when the output voltage falls outside a certain regulation window. A number of additional features such as UVLO circuit with selectable hysteresis levels, an accurate reference voltage for the voltage amplifier, zero power detect, OVP/enable, peak current limit, power limiting, high-current output gate driver characterize the PFC section.

The PWM section features peak current mode control (with a ramp signal available to add slope compensation), programmable soft-start, accurate maximum duty cycle clamp, peak current limit and high-current output gate driver. The PWM stage is suppressed until the PFC output has reached 90% of its programmed value during startup. During line dropout and turn off, the UCC28521 allows the PWM stage to operate until the PFC output has dropped to 71% of its nominal bulk output value. The UCC28528 on the other hand allows the PWM stage to operate continuously until the bias falls below the UVLO turn-off threhold.

Both devices are available in 20-pin DW package.

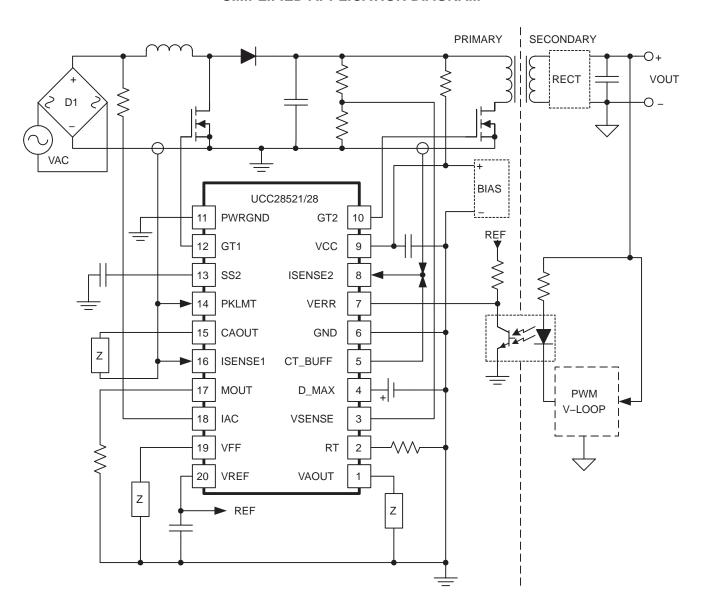

#### SIMPLIFIED APPLICATION DIAGRAM

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature (unless otherwise noted)†‡

Supply voltage VCC

| ldle      | <br>0 V |

|-----------|---------|

| Operating | <br>8 V |

Gate drive current (GT1, GT2)

Pulsed

Input voltage

VSENSE ...... 0 V to 11 V

Pin Current

Maximum pin capacitance

Storage temperature range,  $T_{stq}$  ...... –65  $^{0}C$  to 150  $^{0}C$

#### **ELECTROSTATIC DISCHARGE (ESD) PROTECTION**

| PARAMETER        | MAX | UNITS |

|------------------|-----|-------|

| Human body model | 2.5 | 137   |

| CDM              | 0.5 | kV    |

#### AVAILABLE OPTIONS†‡

| OPTIONS                       |                     |                        |                           |                             | PACKAGED<br>DEVICES |

|-------------------------------|---------------------|------------------------|---------------------------|-----------------------------|---------------------|

| PFC:PWM<br>FREQUENCY<br>RATIO | UVLO<br>TURN-ON (V) | UVLO<br>HYSTERESIS (V) | PWM UVLO2<br>TURN-OFF (V) | PWM UVLO2<br>HYSTERESIS (V) | SOIC W-20<br>(DW)   |

| 1:1                           | 10.2                | 0.5                    | 5.30                      | 1.45                        | UCC28521DW          |

| 1:1                           | 10.2                | 0.5                    | -                         | -                           | UCC28528DW          |

<sup>†</sup> The DW package is available taped and reeled. Add R suffix to device type (e.g. UCC28512DWR) to order quantities of 2,000 devices per reel. ‡ All devices are rated from -40°C to +105°C.

#### **AVAILABLE OPTIONS**†

| PACKAGE                    | THERMAL<br>IMPEDANCE<br>JUNCTION TO<br>AMBIENT | THERMAL<br>IMPEDANCE<br>JUNCTION TO<br>CASE | T <sub>A</sub> < 25°C<br>POWER RATING | T <sub>A</sub> < 25°C<br>DERATING<br>FACTOR | T <sub>A</sub> < 105°C<br>POWER RATING |

|----------------------------|------------------------------------------------|---------------------------------------------|---------------------------------------|---------------------------------------------|----------------------------------------|

| 8-pin plastic SOIC<br>(DW) | 84.3 °C/W                                      | 16.4 °C/W                                   | 1.5 W                                 | 84.3 mW/°C                                  | 0.5 W                                  |

<sup>&</sup>lt;sup>†</sup>Based on low–K PCB Ø LFM.

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect reliability.

<sup>‡</sup> Currents are positive into, negative out of the specified terminal. All voltages are referenced to GND.

SLUS608D - JANUARY 2005 REVISED NOVEMBER 2005

#### **ELECTRICAL CHARACTERISTICS**

$T_A=-40^{\circ}C$  to 105°C for the UCC2851x,  $T_A=T_J,$  VCC = 12 V,  $R_T=156~k\Omega,$   $R_{CT\_BUFF}=10~k\Omega$  (unless otherwise noted)

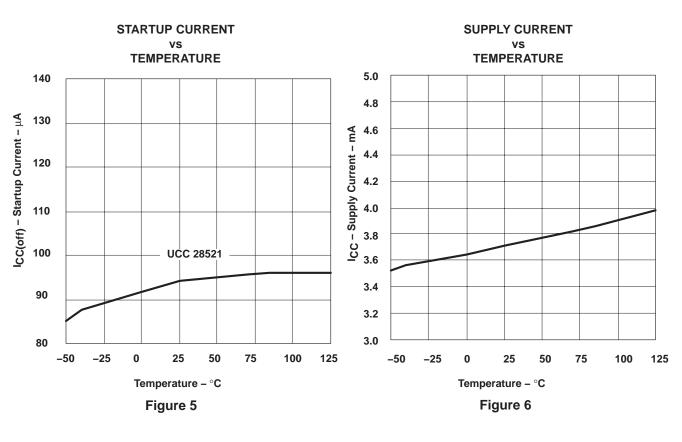

#### supply current

| PARAMETER           | TEST CONDITIONS               | MIN | TYP | MAX | UNITS |

|---------------------|-------------------------------|-----|-----|-----|-------|

| Supply current, off | VCC turn-on threshold –300 mV |     | 100 | 150 | μА    |

| Supply current, on  | no load on GT1 or GT2         |     | 4   | 6   | mA    |

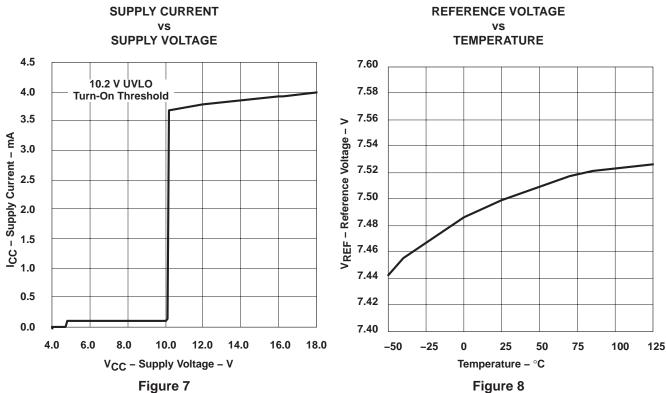

#### undervoltage lockout (UVLO)

| PARAMETER              |          | TEST CONDITIONS | MIN | TYP  | MAX  | UNITS |

|------------------------|----------|-----------------|-----|------|------|-------|

| VCC turn-on threshold  | UCC28521 |                 | 9.7 | 10.2 | 10.8 |       |

| VCC turn-off threshold | UCC28521 |                 | 9.1 | 9.7  | 10.6 | V     |

| UVLO hysteresis        | UCC28521 |                 | 0.3 | 0.5  | 0.8  |       |

#### voltage amplifier

| PARAMETER                       | TEST CONDITIONS                       | MIN  | TYP  | MAX  | UNITS |

|---------------------------------|---------------------------------------|------|------|------|-------|

| Input voltage                   | 25°C                                  | 7.39 | 7.50 | 7.61 | .,    |

|                                 | Over temperature                      | 7.35 | 7.50 | 7.65 | V     |

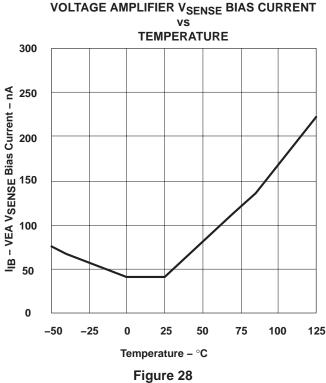

| V <sub>SENSE</sub> bias current | V <sub>SENSE</sub> = V <sub>REF</sub> |      | 100  | 300  | nA    |

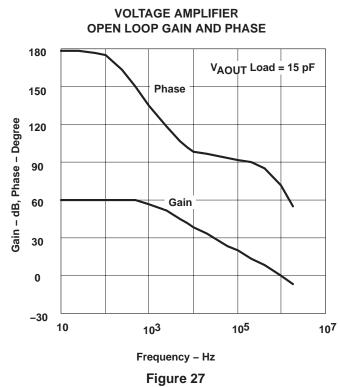

| Open loop gain                  | 2 V ≤ VAOUT ≤ 4 V                     | 50   | 60   |      | dB    |

| High-level output voltage       | $I_{LOAD} = -150 \mu A$               | 5.3  | 5.5  | 5.6  | .,    |

| Low-level output voltage        | I <sub>LOAD</sub> = 150 μA            | 0.00 | 0.05 | 0.15 | V     |

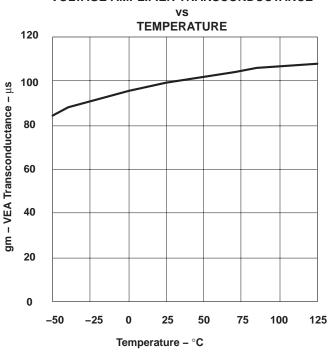

| g <sub>M</sub> conductance      | $I_{VAOUT} = -20 \mu A$ to 20 $\mu A$ | 70   | 100  | 130  | μS    |

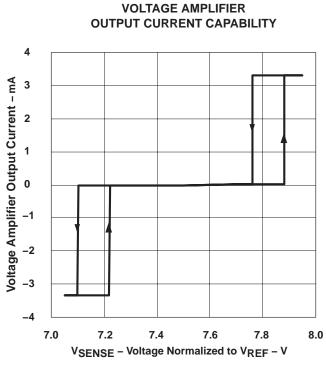

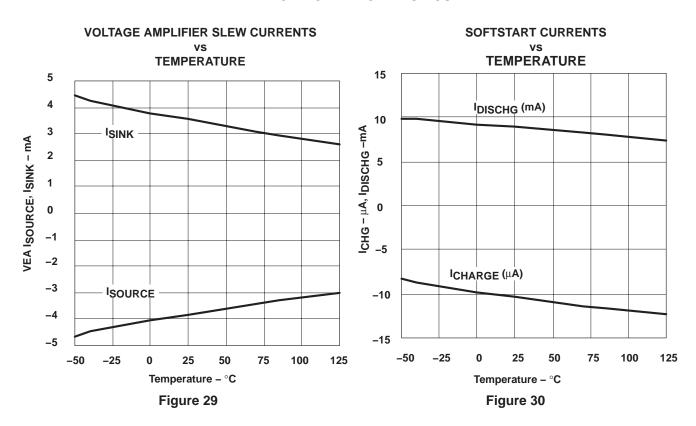

| Maximum source current          |                                       | -1   | -3.5 |      |       |

| Maximum sink current            |                                       | 1    | 3.5  |      | mA    |

#### PFC stage overvoltage protection and enable

| 5 5 1                        |                 |                 |                 |                 |       |

|------------------------------|-----------------|-----------------|-----------------|-----------------|-------|

| PARAMETER                    | TEST CONDITIONS | MIN             | TYP             | MAX             | UNITS |

| Overvoltage reference window |                 | VREF<br>+ 0.440 | VREF<br>+ 0.490 | VREF<br>+ 0.540 | V     |

| Hysteresis                   |                 | 300             | 500             | 600             | mV    |

| Enable threshold             |                 | 1.7             | 1.9             | 2.1             | .,    |

| Enable hysteresis            |                 | 0.08            | 0.2             | 0.3             | V     |

**ELECTRICAL CHARACTERISTICS** T<sub>A</sub> =  $-40^{\circ}$ C to  $105^{\circ}$ C for the UCC2851x, T<sub>A</sub> = T<sub>J</sub>, VCC = 12 V, R<sub>T</sub> = 156 k $\Omega$ , R<sub>CT\_BUFF</sub> = 10 k $\Omega$  (unless otherwise noted)

#### current amplifier

| PARAMETER                             | TEST CONDITIONS               |                                | MIN | TYP | MAX  | UNITS |

|---------------------------------------|-------------------------------|--------------------------------|-----|-----|------|-------|

| Input offset voltage                  | $V_{CM} = 0 V$                | V <sub>CAOUT</sub> = 3 V       | -5  | 0   | 5    | mV    |

| Input bias current                    | V <sub>CM</sub> = 0 V,        | V <sub>CAOUT</sub> = 3 V       |     | -50 | -100 |       |

| Input offset current                  | V <sub>CM</sub> = 0 V,        | V <sub>CAOUT</sub> = 3 V       |     | 25  | 100  | nA    |

| Open loop gain                        | V <sub>CM</sub> = 0 V,        | 2 V ≤ V <sub>CAOUT</sub> ≤ 5 V | 90  |     |      | i     |

| Common-mode rejection ratio           | 0 V ≤ V <sub>CM</sub> ≤ 1.5 V | /, V <sub>CAOUT</sub> = 3 V    | 80  |     |      | dB    |

| High-level output voltage             | I <sub>LOAD</sub> = -500 μA   | I <sub>LOAD</sub> = -500 μA    |     | 6.3 | 7.0  | .,    |

| Low-level output voltage              | I <sub>LOAD</sub> = 500 μA 0  |                                | 0.2 | 0.5 | V    |       |

| Gain bandwidth product <sup>(1)</sup> | See Note 1                    |                                |     | 2.0 |      | MHz   |

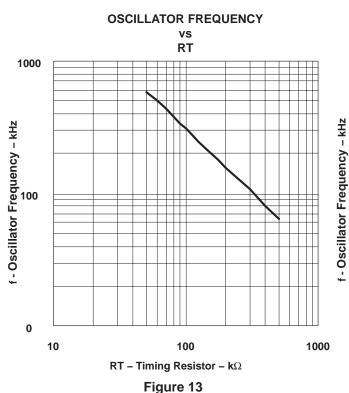

#### oscillator

| PARAMETER                                         | TEST CONDITIONS                 | MIN | TYP | MAX | UNITS |

|---------------------------------------------------|---------------------------------|-----|-----|-----|-------|

| fPWM, PWM frequency, initial accuracy             | T <sub>A</sub> = 25°C           | 170 | 200 | 230 | kHz   |

| Frequency, voltage stability                      | 10.8 V ≤ V <sub>CC</sub> ≤ 15 V | -1% |     | 1%  |       |

| Frequency, total variation                        | Line, Temp                      | 160 |     | 240 | kHz   |

| dc-to-dc ramp peak voltage                        |                                 | 4.5 | 5.0 | 5.5 |       |

| dc-to-dc ramp amplitude voltage(1) (peak-to-peak) |                                 |     | 4.0 |     | V     |

| PFC ramp peak voltage                             |                                 | 4.5 | 5.0 | 5.5 |       |

| PFC ramp amplitude voltage (peak-to-peak)         |                                 | 3.5 | 4.0 | 4.5 |       |

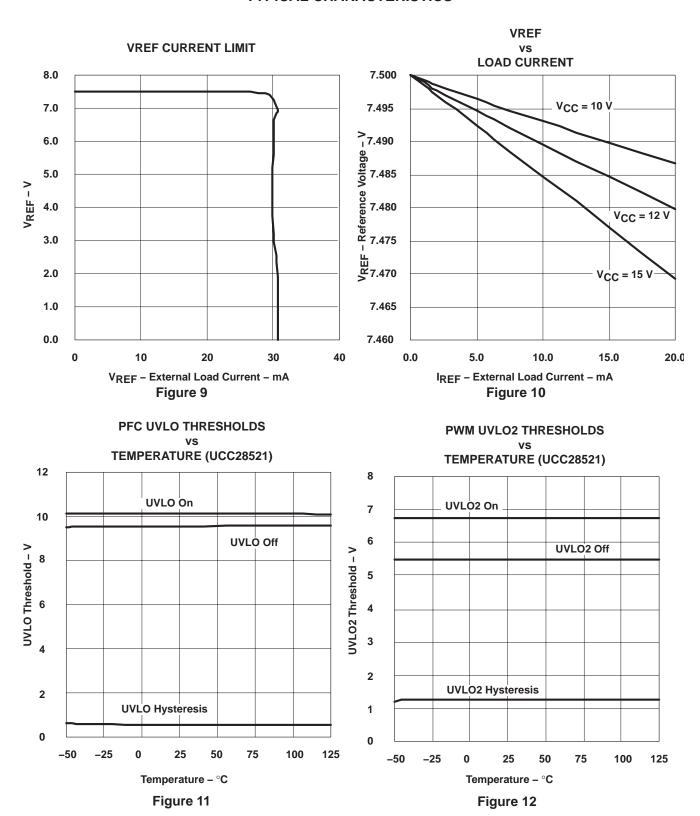

#### voltage reference

| PARAMETER             | TEST CONDITIONS                 | MIN  | TYP  | MAX  | UNITS |

|-----------------------|---------------------------------|------|------|------|-------|

| Input voltage         | 25°C                            | 7.39 | 7.50 | 7.61 | V     |

|                       | Over temperature                | 7.35 | 7.50 | 7.65 | V     |

| Load regulation       | IREF = -1 mA to -6 mA           |      | 5    | 15   | >/    |

| Line regulation       | 10.8 V ≤ V <sub>CC</sub> ≤ 15 V |      | 1    | 10   | mV    |

| Short circuit current | VREF = 0V                       | -20  | -25  | -50  | mA    |

#### peak current limit

| PARAMETER               | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|-------------------------|-----------------|-----|-----|-----|-------|

| PKLMT reference voltage |                 | -20 | 0   | 20  | mV    |

| PKLMT propagation delay | PKLMT to GT1    | 150 | 300 | 500 | ns    |

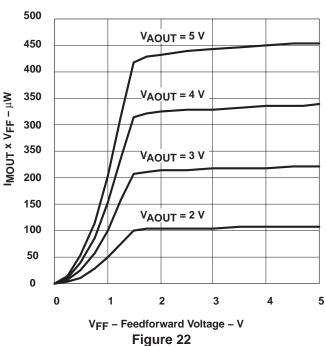

#### multiplier

| PARAMETER                                               | TEST CONDITIONS                                                       | MIN          | TYP  | MAX  | UNITS |

|---------------------------------------------------------|-----------------------------------------------------------------------|--------------|------|------|-------|

| I <sub>MOUT</sub> , high-line low-power output current  | $I_{AC} = 500 \mu\text{A}, \text{ VFF} = 4.7 \text{V}, \text{ VAOUT}$ | = 1.25 V3    | -6   | -9   |       |

| I <sub>MOUT</sub> , high-line high-power output current | $I_{AC} = 500 \mu\text{A}, \text{ VFF} = 4.7 \text{V}, \text{ VAOUT}$ | = 5 V -75    | -90  | -110 |       |

| I <sub>MOUT</sub> , low-line low-power output current   | $I_{AC} = 150 \mu\text{A}, \text{ VFF} = 1.4 \text{V}, \text{ VAOUT}$ | = 1.25 V -10 | -15  | -50  | μΑ    |

| I <sub>MOUT</sub> , low-line high-power output current  | $I_{AC} = 150 \mu\text{A}, \text{ VFF} = 1.4 \text{V}, \text{ VAOUT}$ | = 5 V -245   | -290 | -330 |       |

| I <sub>MOUT</sub> , IAC-limited output current          | $I_{AC} = 150 \mu\text{A}, \text{ VFF} = 1.3 \text{V}, \text{ VAOUT}$ | = 5 V -245   | -290 | -330 |       |

| Gain constant (k)                                       | $I_{AC} = 300 \mu\text{A}, \text{ VFF} = 2.8 \text{V}, \text{ VAOUT}$ | = 2.5 V 0.8  | 1    | 1.2  | 1/V   |

|                                                         | $I_{AC} = 150 \mu\text{A}, \text{ VFF} = 1.4 \text{V}, \text{ VAOUT}$ | = 0.25 V     | 0    | -0.2 | μΑ    |

| I <sub>MOUT</sub> , zero current                        | $I_{AC} = 500 \mu\text{A},  \text{VFF} = 4.7  \text{V}, $             | = 0.25 V     | 0    | -0.2 | μΑ    |

|                                                         | $I_{AC} = 500 \mu A$ , VFF = 4.7 V, VAOUT                             | = 0.5 V      | 0    | -0.2 | μА    |

| Power limit (I <sub>MOUT</sub> × V <sub>FF</sub> )      | $I_{AC} = 150 \mu\text{A}, \text{ VFF} = 1.4 \text{V}, \text{ VAOUT}$ | = 5 V -343   | -406 | -462 | μW    |

<sup>1.</sup> Ensured by design. Not 100% tested in production.

SLUS608D – JANUARY 2005 REVISED NOVEMBER 2005

#### **ELECTRICAL CHARACTERISTICS**

$T_A=-40^{\circ}C$  to 105°C for the UCC2851x,  $T_A=T_J,$  VCC = 12 V,  $R_T=156~k\Omega,$   $R_{CT\_BUFF}=10~k\Omega$  (unless otherwise noted)

#### zero power

| PARAMETER                        | TEST CON           | TEST CONDITIONS |      |      | MAX  | UNITS |

|----------------------------------|--------------------|-----------------|------|------|------|-------|

| Zero power comparator threshold  | Measured on VAOUT, | falling edge    | 0.20 | 0.33 | 0.50 | V     |

| Zero power comparator hysteresis | Measured on VAOUT, | rising edge     | 40   | 90   | 140  | mV    |

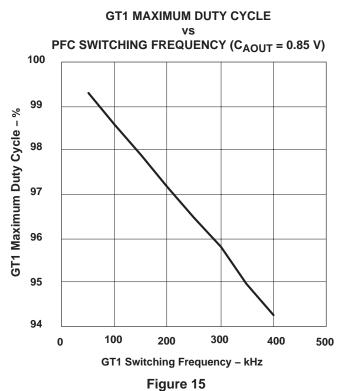

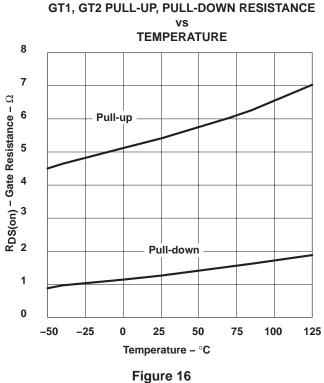

#### PFC gate driver

| PARAMETER                          | TEST CON                           | MIN                                   | TYP | MAX | UNITS |    |

|------------------------------------|------------------------------------|---------------------------------------|-----|-----|-------|----|

| GT1 pull-up resistance             | -100 mA ≤ ΔI <sub>OUT</sub> ≤ -200 | –100 mA ≤ Δl <sub>OUT</sub> ≤ –200 mA |     |     | 12    | 0  |

| GT1 pull-down resistance           | I <sub>OUT</sub> = 100 mA          |                                       |     | 2   | 10    | Ω  |

| GT1 output rise time               |                                    | <b>D</b> 40.0                         |     | 16  | 25    |    |

| GT1 output fall time               | $C_{LOAD} = 1 \text{ nF},$         | $R_{LOAD} = 10 \Omega$                |     | 7   | 15    | ns |

| Maximum duty cycle                 |                                    |                                       | 93% | 95% | 100%  |    |

| Minimum duty cycle (trailing edge) | See Note 1                         |                                       | 1%  | _   | 7%    |    |

#### PWM stage undervoltage lockout (UVLO2)

| PARAMETER              |          | TEST CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|------------------------|----------|-----------------|------|------|------|-------|

| PWM turn-on reference  | UCC28521 |                 | 6.30 | 6.75 | 7.30 |       |

| PWM turn-off threshold | UCC28521 |                 |      | 5.3  |      | V     |

| Hysteresis             | UCC28521 |                 | 1.16 | 1.45 | 1.74 |       |

#### **PWM** stage soft-start

| 3                     |          |                                         |                           |      |       |       |       |

|-----------------------|----------|-----------------------------------------|---------------------------|------|-------|-------|-------|

| PARAMETER             |          | TEST CO                                 | NDITIONS                  | MIN  | TYP   | MAX   | UNITS |

| SS2 charge current    |          | V <sub>SENSE</sub> = 7.5 V,             | SS2 = 0 V                 | -7.0 | -10.5 | -14.0 | μΑ    |

| SS2 discharge current | UCC28521 | VSENSE = 2.5 V,<br>(UVLO2 = Low, ENABLI | SS2 = 2.5 V,<br>E = High) | 6    | 10    | 14    | mA    |

| Input voltage (VERR)  | UCC28521 | I <sub>VERR</sub> = 2 mA,UVLO2 =        | = Low                     |      |       | 300   | mV    |

#### PWM stage duty cycle clamp

| PARAMETER          | TEST CONDITIONS | MIN | TYP | MAX | UNITS |

|--------------------|-----------------|-----|-----|-----|-------|

| Maximum duty cycle | D_MAX = 4.15 V  | 70% | 75% | 80% |       |

#### PWM stage pulse-by-pulse current sense

| PARAMETER                               | TEST CONDITIONS |                  | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------|-----------------|------------------|------|------|------|-------|

| Current sense comparator offset voltage | ISENSE2 = 0 V.  | measured on VERR | 1.35 | 1.50 | 1.65 | V     |

<sup>1.</sup> Ensured by design. Not 100% tested in production.

**ELECTRICAL CHARACTERISTICS** T<sub>A</sub> =  $-40^{\circ}$ C to  $105^{\circ}$ C for the UCC2851x, T<sub>A</sub> = T<sub>J</sub>, VCC = 12 V, R<sub>T</sub> = 156 k $\Omega$ , R<sub>CT\_BUFF</sub> = 10 k $\Omega$  (unless otherwise noted)

#### **PWM** stage overcurrent limit

| PARAMETER                                 | TEST CONDITIONS | MIN  | TYP  | MAX  | UNITS |

|-------------------------------------------|-----------------|------|------|------|-------|

| Peak current comparator threshold voltage |                 | 1.15 | 1.30 | 1.45 | V     |

| Input bias current <sup>(1)</sup>         |                 |      | 50   |      | nA    |

#### PWM stage gate driver

| PARAMETER                | TEST CONDITIONS                                          | MIN | TYP | MAX | UNITS |

|--------------------------|----------------------------------------------------------|-----|-----|-----|-------|

| GT2 pull-up resistance   | $-100 \text{ mA} \le \Delta I_{OUT} \le -200 \text{ mA}$ |     | 5   | 12  | Ω     |

| GT2 pull-down resistance | I <sub>OUT</sub> = 100 mA                                |     | 2   | 10  | Ω     |

| GT2 output rise time     | 0 4.5 5 400                                              |     | 16  | 25  | ns    |

| GT2 output fall time     | $C_{LOAD} = 1 \text{ nF},$ $R_{LOAD} = 10 \Omega$        |     | 7   | 15  | ns    |

<sup>1.</sup> Ensured by design. Not 100% tested in production.

#### **TERMINAL FUNCTIONS**

| TE      | RMINAL |       |     |                                                                                                                                                        |  |

|---------|--------|-------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME    | NO.    | Stage | 1/0 | DESCRIPTION                                                                                                                                            |  |

| CAOUT   | 15     | PFC   | 0   | Output of the current control amplifier of the PFC stage. CAOUT is internally connected to the PWM comparator input in the PFC stage                   |  |

| CT_BUFF | 5      | PWM   | 0   | Internally buffered PWM stage oscillator ramp output, typically used to program slope compensation with a single resistor                              |  |

| D_MAX   | 4      | PWM   | 1   | Positive input to set the maximum duty cycle clamp level of the PWM stage duty ratio can be between 0.09 and 0.90.                                     |  |

| GND     | 6      | -     | -   | Analog ground                                                                                                                                          |  |

| GT1     | 12     | PFC   | 0   | PFC stage gate drive output                                                                                                                            |  |

| GT2     | 10     | PWM   | 0   | PWM stage gate drive output                                                                                                                            |  |

| IAC     | 18     | PFC   | I   | Multiplier current input that is proportional to the instantaneous rectified line voltage                                                              |  |

| ISENSE1 | 16     | PFC   | I   | Non-inverting input to the PFC stage current amplifier                                                                                                 |  |

| ISENSE2 | 8      | PWM   | I   | Input for PWM stage current sense and peak current limit                                                                                               |  |

| MOUT    | 17     | PFC   | I/O | PFC multiplier high–impedance current output, internally connected to the current amplifier inverting input                                            |  |

| PKLMT   | 14     | PFC   | I   | Voltage input to the PFC peak current limit comparator                                                                                                 |  |

| PWRGND  | 11     | _     | -   | Power ground for GT1, GT2 and high current return paths                                                                                                |  |

| RT      | 2      | -     | I   | Oscillator programming pin that is set with a single resistor to GND                                                                                   |  |

| SS2     | 13     | PWM   | I   | Soft start for the PWM stage                                                                                                                           |  |

| VAOUT   | 1      | PFC   | I/O | Output of the PFC transconductance voltage amplifier and it is internally connected to the Zero Power Detect comparator input and the multiplier input |  |

| VCC     | 9      | -     | ı   | Positive supply voltage pin                                                                                                                            |  |

| VERR    | 7      | PWM   | I   | Feedback error voltage input for the PWM stage, typically connected to an optocoupler output                                                           |  |

| VFF     | 19     | PFC   | I   | Voltage feedforward pin for the PFC stage, sources an IAC/2 current that should be externally filtered                                                 |  |

| VREF    | 20     | -     | 0   | Precision 7.5-V reference output                                                                                                                       |  |

| VSENSE  | 3      | PFC   | I   | Inverting input to the PFC transconductance voltage amplifier, and input to the OVP, ENABLE and UVLO2 comparators                                      |  |

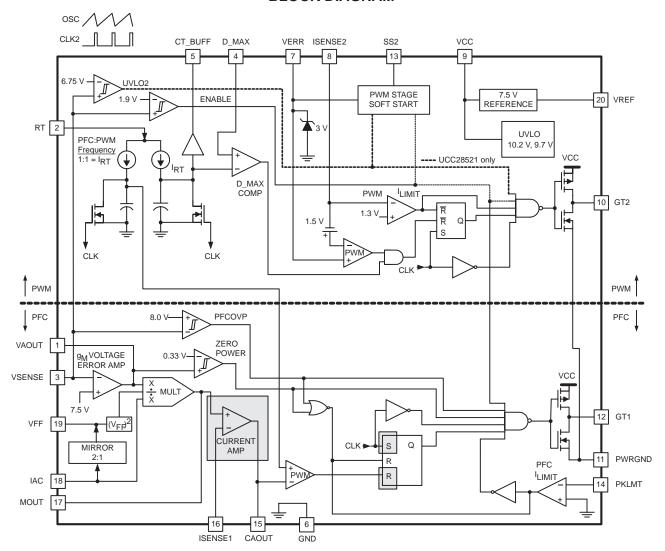

#### **BLOCK DIAGRAM**

#### **DETAILED PIN DESCRIPTIONS**

**CAOUT (Pin 15):** This is the output of a wide-bandwidth operational amplifier that senses line current and commands the PFC stage PWM comparator to force the correct duty cycle. This output can swing above the PFC ramp peak voltage to command maximum duty cycle and below the PFC ramp voltage to force zero duty cycle when necessary. Connect current loop compensation components between CAOUT and MOUT.

**CT\_BUFF (Pin 5):** The 4-V amplitude oscillator ramp is internally buffered at this pin to allow a resistor to be connected directly from this pin to ISENSE2 for slope compensation. The internal buffer can drive a typical 500-μA resistive load at this pin.

**D\_MAX (Pin 4):** Program the maximum duty cycle at GT2 by applying a dc voltage to this pin. Between 0.09 and 0.90, the maximum duty ratio is linearly related to D\_MAX. Usually, this voltage is set with a precision resistor divider powered by VREF. A first order approximation, with the CT\_BUFF frequency near 200 kHz, is estimated by:

$$D_{MAX} \cong \frac{V_{DX} - 1.15 \text{ V}}{4 \text{ V}}$$

where,  $D_{MAX}$  is a dimensionless ratio  $V_{DX}$  is the voltage at  $D_{MAX}$  in volts

This pin can also be used to set  $D_{MAX}$  to 0 by setting  $V_{DX}$  less than 0.7 V.

#### **DETAILED PIN DESCRIPTIONS (CONTINUED)**

**GND (Pin 6):** Signal ground for the integrated circuit. All voltages measured with respect to ground are referenced to this pin. The bypass capacitors for VCC and VREF should connect to this pin with as little lead length as possible. PWRGND must be externally connected to this pin. For best results, use a single small circuit trace to electrically connect between the circuits that use the GND return path and the circuits that use the PWRGND return path.

**GT1 (Pin 12):** A 2-A peak source and 3-A peak sink current totem pole MOSFET gate driver for the PFC stage. Some overshoot at GT1 can be expected when driving a capacitive load, but adding a minimal series resistor of about 2  $\Omega$  between GT1 and the external MOSFET gate can reduce this overshoot. GT1 is disabled unless VCC is outside the UVLO region and VREF is on.

**GT2 (Pin 10):** A 2-A peak source and 3-A peak sink current totem pole MOSFET gate driver for the PWM stage, identical to the driver at GT1.

IAC (Pin 18): This multiplier input senses the rectified ac line voltage. A resistor between IAC and the line voltage converts the instantaneous line voltage waveform into a current input for the analog multiplier. The recommended maximum IAC current is  $500 \, \mu A$ .

**ISENSE1** (Pin 16): This pin is the non-inverting input terminal of the current amplifier. Connect a resistor between this pin and the grounded side of the PFC stage current sensing resistor. The resistor connected to this pin should have a value that equals the value of the resistor that is connected between the MOUT pin and the ungrounded side of the PFC current sense resistor.

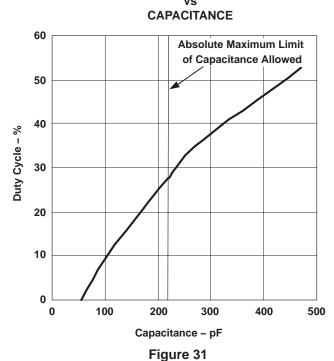

**ISENSE2** (Pin 8): A voltage across the PWM stage external current sense resistor generates the input signal to this pin, with the peak limit threshold set to 1.3 V for peak current mode control. An internal 1.5-V level shift between ISENSE2 and the input to the PWM comparator provides greater noise immunity. The oscillator ramp can also be summed into this pin for slope compensation. Figure 31 shows the typical relationship of the capacitance on the ISENSE2 pin and the minimum controllable limit of the pulse width on the gate2 output. If the V<sub>ERR</sub> is at the voltage that corresponds to a minimum controllable duty cycle and then is reduced further the pulse width collapses to near zero.

**MOUT (Pin 17):** The output of the multiplier and the input to the current amplifier in the PFC stage are internally connected at this pin. Set the power range of the PFC stage with a resistor tied between the MOUT pin and the non-grounded end of the PFC current sense resistor. Connect impedance between the MOUT pin and the CAOUT pin to compensate the PFC current control loop. The multiplier output is a current and the current amplifier input is high impedance. The multiplier output current is given by:

$$I_{MOUT} = \frac{\left(V_{VAOUT} - 1.0\right) \times I_{IAC}}{K \times \left(V_{VFF}\right)^{2}}$$

where, K is the multiplier gain constant, in volts<sup>-1</sup>.

IMOUT is limited to two times IAC for power limiting.

**PKLMT (Pin 14):** Program the peak current limit of the PFC stage using this pin. The threshold for peak limit is 0 V. Use a resistor divider between VREF and the non-grounded side of the PFC current sense resistor in order to shift the level of this signal to a voltage that corresponds to the desired overcurrent threshold voltage, measured across the PFC current sense resistor.

**PWRGND (Pin 11):** Ground for the output drivers at GT1 and GT2. This ground should be tied to GND externally via a single Kelvin connection.

#### **DETAILED PIN DESCRIPTIONS (CONTINUED)**

**RT (Pin 2):** A resistor between RT and GND programs the oscillator frequency, measured at CT\_BUFF. In all options, the PWM stage operates at the frequency that is measured at CT\_BUFF. In the UCC28521 the PFC stage operates at the same frequency as the PWM stage. The voltage is dc (nominally 3 V); do not connect a capacitor to this pin in an attempt to stabilize the voltage. Instead, connect the GND side of the oscillator-programming resistor closer to the GND pin. The recommended range of resistors is 45 k $\Omega$  to 500 k $\Omega$  for a frequency range of 600 kHz to 65 kHz, respectively. Resistor R<sub>T</sub> programs the oscillator frequency f<sub>S</sub>, as measured at CT\_BUFF, according to the following equation:

$$R_{T} = \frac{1}{31 \times 10^{-12}} \left( \frac{1}{f_{S}} - 2.0 \times 10^{-7} \right)$$

where,  $R_T$  is in  $\Omega$   $f_S$  is in Hz

**SS2** (pin 13): A capacitor between SS2 and GND programs the softstart duration of the PWM stage gate drive. When the UVLO2 comparator enables the PWM stage, an internal 10.5-μA current source charges the external capacitor at SS2 to 3 V to ramp the voltage at VERR during startup. This allows the GT2 duty cycle to increase from 0% to the maximum clamped by the duty cycle comparator over a controlled time delay t<sub>SS</sub> given by:

$$C_{SS2} = \frac{t_{SS} \times 10.5 \times 10^{-6}}{3}, \quad \text{Farads}$$

In the event of a disable command or a UVLO2 dropout, SS2 quickly discharges to ground to disable the PWM stage gate drive.

**VAOUT (Pin 1):** This transconductance voltage amplifier output regulates the PFC stage output voltage and operates between GND and 5.5 V maximum to prevent overshoot. Connect the voltage compensation components between VAOUT and GND. When this output goes below 1 V, the multiplier output current goes to zero. When this output falls below 0.33 V, the zero power detect comparator ensures the PFC stage gate drive is turned off. In the linear range, this pin sources or sinks up to 30  $\mu$ A. A slew rate enhancement feature enables VAOUT to sink or source up to 3.3 mA, when operating outside the linear range.

**VCC (Pin 9):** Chip positive supply voltage that should be connected to a stable source of at least 20 mA between 12 V and 17 V for normal operation. Bypass VCC directly to GND with a 0.1  $\mu$ F or larger ceramic capacitor to absorb supply current spikes caused by the fast charging of the external MOSFET gate capacitances.

**VERR (Pin 7):** The voltage at this pin controls the GT2 duty cycle and is connected to the feedback error signal from an external amplifier in the PWM stage. This pin is clamped to a maximum of 3 V and can demand 100% duty cycle at GT2. The typical pull-up current flowing out of this pin is 10 μA.

VFF (Pin 19): The output current from this pin comes from an internal current mirror that divides the IAC input current by 2. The input voltage feedforward signal for the multiplier is then generated across an external single-pole R/C filter connected between VFF and GND. At low line, the VFF voltage should be set to 1.4 V.

VREF (Pin 20): This is the output of an accurate 7.5-V reference that powers most of the internal circuitry and can deliver over 10 mA, with a typical load regulation of 5 mV ensured for an external load of up to 6 mA. The internal reference is current limited to 25 mA, which protects the part if VREF is short-circuited to ground. VREF should be bypassed directly to GND with a ceramic capacitor between 0.1  $\mu$ F and 10  $\mu$ F for stability. VREF is disabled and remains at 0 V when VCC is below the 9.7-V UVLO threshold.

**VSENSE** (Pin 3): Inverting input to the PFC transconductance voltage amplifier, which serves as the PFC feedback connection point. When VSENSE operates within  $\pm -0.35$  V of its steady-state value, the current at VAOUT is proportional to the difference between the VREF and VSENSE voltages by a factor of  $g_M$ . Outside this range, the magnitude of the current of VAOUT is increased in order to enhance the slew rate for rapid voltage control recovery in the PFC stage. Decisive activation and deactivation of the voltage control recovery is internally implemented with about 120 mV of hysteresis at VSENSE. VSENSE is internally connected to the PFC OVP, Enable and UVLO2 comparators as well.

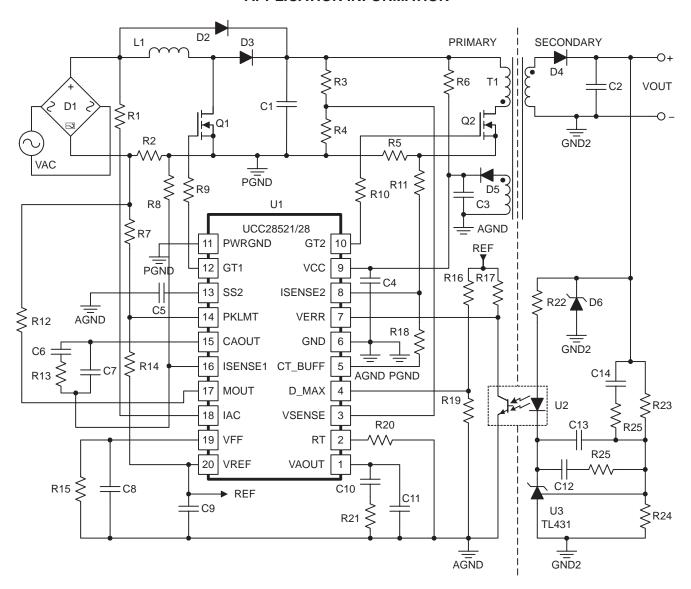

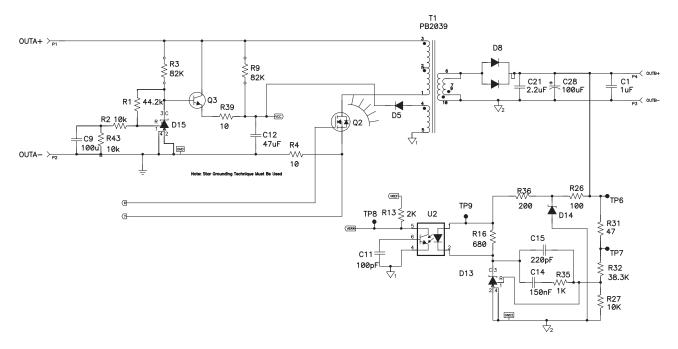

Figure 1. Typical Application Circuit: Boost PFC and Flyback PWM Power System

The UCC28521 combination controller includes a power factor correction (PFC) controller that is synchronized with a pulse width modulator (PWM) controller integrated into one chip. The PFC controller has all of the features for an average current mode controlled PFC. The PWM controller has all of the features for an isolated peak current program mode controlled converter. The two controllers are internally synchronized at a fixed frequency with both the PFC controller and the PWM controller are trailing edge modulated (TEM).

#### design procedure

The following discussion steps through the typical design process of a PFC/PWM converter system. The design process begins with the power stage elements, then the control elements for the PFC stage, then the control elements for the PWM stage. Keep in mind that a general design process is often iterative. Iteration typically begins after either simulating and/or testing the completed PFC/PWM system. This design procedure refers to the typical application in Figure 1.

A design begins with a list of requirements for output voltage, output power and ac line voltage range. Other details, such as efficiency and permissible current harmonics could be given at the onset, or developed throughout the product design cycle. The need for power factor correction arises from either an agency requirement, such as EN-61000, or if the available line power is nearly equal to the output power of the power system. Hold-up time requirements are also necessary at the early stages of design. Typically, the hold-up time,  $t_{HII}$ , is at least the period of 1.5 line cycles.

The general structure of the PFC/PWM stage power system is two switched-mode converters connected in cascade. Each stage has an associated efficiency and each stage has its own set of fault limiting controls that must be properly set in order to achieve the desired line harmonic and load regulation performance, simultaneously. The PFC stage must always be designed to supply sufficient average power to the PWM stage. The cycle-by-cycle current limit of the PFC stage should be programmed to activate at a slightly larger power level at low ac line voltage than the average power clamp in order to allow for PFC current sense tolerances. This will allow power factor correction for the full range of maximum rated load. If the instantaneous load nearly equals the average load, then the fault clamps for the PWM stage can be programmed to limit power at a level that is slightly less than or equal to the average power clamp of the PFC stage. The margin for the clamping action should allow for measurement tolerances and efficiency. Conversely, if the instantaneous load has high peaks that are much shorter than the hold-up time, the current limit and duty ratio limits of the PWM stage can clamp at a higher level than the average power clamp in the PFC stage. In order to simplify the design procedure, the average and the peak loads of the PWM stage are assumed to be equal. Thus, all of the current limits and duty cycle limits are programmed to clamp power at a slightly lower level (10%) than the average power clamp on the PFC stage.

#### developing the internal parameters

Select the energy storage voltage  $V_{C1}$ . Since the PFC stage is a boost converter, the voltage across C1 must be larger than the peak ac line voltage by enough to permit controllability in the event of load transients. Typically, this will be around 5% which is about 400 V for a universal ac line application of 85  $V_{AC}$  to 265  $V_{AC}$ .

Once the energy storage voltage,  $V_{C1}$ , is determined, the range of the PFC stage duty ratio,  $D_1$ , is set. For CCM operation of the PFC stage, the minimum PFC duty ratio is given by:

$$D_{1(min)} = 1 - \frac{\sqrt{2} \times VAC_{MIN}}{V_{C1}}$$

(1)

Select an approximate switching frequency for the PFC stage. A good starting frequency for a MOSFET based PFC stage is in the range of 100 kHz to 200 kHz, depending on maximum line voltage and maximum line current. Adjustments in switching frequency may result from meeting switching loss requirements in Q1 and D3, or in order to optimize the design of L1.

Select an appropriate topology for the PWM stage using the information about the power requirements and the magnitude of  $V_{C1}$ . For simplicity, the typical application in Figure 1 shows a flyback converter in the PWM stage. In most cases, the PWM stage topology must have transformer isolation and the topology must require only one pulse-width signal. Topologies that have these features include:

- single-transistor forward converter

- single-transistor flyback converter

- two-transistor forward converter

- two-transistor flyback converter

Estimate the nominal and the maximum duty ratios of the PWM stage  $(D_{2(nom)}, D_{2(max)})$  and the associated peak Q2 drain current,  $i_{Q2(peak)})$ , based on the topology, PWM hysteresis option and output voltage requirements of the PWM stage. Also estimate whether or not it is appropriate to operate the PWM stage at the same switching frequency as the PFC stage or if the PWM stage can operate at twice the switching frequency of the PFC stage. Base the estimation for the switching frequency of the PWM stage on the maximum voltages and currents of the power MOSFETs and power diodes. Program the oscillator frequency of the PWM stage with the value of R20.

R20 =

$$\frac{1}{31 \times 10^{-12}} \left( \frac{1}{f_{S(pwm)}} - 2.0 \times 10^{-7} \right), \quad \Omega$$

(2)

Most applications require that the PWM stage regulates at the minimum energy storage capacitance voltage. Maximum duty ratio  $D_{2(max)}$  and  $i_{Q2(peak)}$  should be calculated for the minimum energy storage voltage in order to estimate the peak current stresses for transformer T1 and any other inductive element in the PWM stage.

At this point, enough information is available to estimate which member of the UCC28510 family should be selected.

#### power stage elements

The power stage elements include the following elements: C1–3, D1–5, L1, R2, R5, Q1, Q2, T1. Details concerning the PWM stage elements C2, D4, D5, Q2 and T1 will not be discussed in detail here, due to their dependence on the choice PWM stage topology. The PWM stage is an isolated dc-to-dc topology with the same stresses and loss mechanisms that are typical for the selected topology. An estimation of the average steady state duty ratio of the PWM stage and the Q2 switch current will be needed for stress estimations in the PFC stage. Also, the natural step response of the PWM stage is required to estimate the soft start capacitor, C5, and the bias supply capacitor, C3.

The selection process of the PFC stage elements C1, C3, D1–3 and Q1 are discussed in detail here. In general, the selection process for the PFC stage elements is the same as for a typical fixed switching frequency PFC design, except for capacitor C1 due to PFC/PWM stage synchronization.

Diode bridge D1 is selected to withstand the rms line current and the peak ac line voltage. Diode D2 allows capacitor C1 to charge during initial power up without saturating L1 and it is selected to withstand the peak inrush current and peak of the maximum ac line voltage. Additional inrush current limiting circuitry in series with the ac line could be required, depending on agencies or situations.

The PFC stage inductor, L1, is selected to have a maximum current ripple at the minimum ac line voltage. Typically a ripple factor, k<sub>RF</sub>, is chosen to be about 0.2. If the line current has excessive crossover distortion, a larger ripple factor (perhaps 0.3) will reduce the distortion but the line current will have more switching ripple. Initially, the inductance can be estimated by approximating the input power equal to the output power.

$$\begin{split} \text{L1} &= \frac{\text{V}_{\text{AC(min)}}^2 \times \text{D}_{\text{1(min)}} \times \text{T}_{\text{S(pfc)}}}{\text{k}_{\text{RF}} \times \text{P}_{\text{IN}}} \\ \text{where, } \text{k}_{\text{RF}} &= \frac{\Delta i_{\text{L1(p-p)}}}{i_{\text{L1(max)}}} \text{ and } \text{T}_{\text{S(pfc)}} \text{ is } \frac{1}{\text{switching frequency of the PFC}} \end{split}$$

Inductor L1 must be designed to withstand the maximum ac rms line current without saturation at the peak ac line current.

Select power MOSFET Q1 and diode D3 with the same criteria that is normally used for fixed switching frequency PFC design. They must have sufficient voltage rating to withstand the energy storage voltage, V<sub>C1</sub> and they must have sufficient current ratings. Gate drive resistor R9 is necessary to limit the source and sink current from the GT1 pin. Some circumstances require additional gate drive components for improved protection and performance.<sup>[10]</sup> A similar gate drive resistor, R10, is required between the GT2 pin and the gate of Q2 for the same reason.

The current sense resistor for the PFC stage, R2, is selected to operate over a 1-V dynamic range (V<sub>DYNAMIC</sub>). The sense resistor must also have a large enough power rating to permit safe operation with the maximum RMS line current.

$$R2 = \frac{V_{DYNAMIC}}{i_{L1(max)} + 0.5 \times \Delta i_{L1(p-p)}}$$

where,  $i_{L1(max)} = \frac{\sqrt{2} \times P_{IN}}{V_{AC(min)}}$  (4)

The PFC  $I_{LIMIT}$  comparator threshold is at the ground reference for the controller device. So, the PFC current sense voltage, measured at PKLMT must be biased with a positive voltage to cross 0.0 V when the instantaneous PFC current is at its maximum. The bias voltage is established with R14 and R7, as shown in equation 7, and resistor R14 is arbitrarily chosen around 10 k $\Omega$ .

$$\frac{R7}{R14} = \frac{1}{\frac{V_{REF}}{i_{L1(max)} \times R2} - 1}$$

(5)

The capacitance value of the energy storage capacitor, C1 is selected to meet hold-up time requirements (t<sub>HU</sub>) by the equation:

$$C1 = \frac{2P_{OUT} \times t_{HU}}{V_{C1}^2 - (V_{C1} - 0.7V_{C1})^2}$$

(6)

Capacitor C1 must be rated for the selected energy storage voltage and it must be able to withstand the rms ripple current,  $I_{C1(rms)}$ , that is produced by the combined action of the PFC stage and the PWM stage. The average Q2 drain current during the interval that GT2 activates MOSFET Q2 is used to find  $I_{C1(rms)}$ . An initial estimate can be made using the inequality in equation 9, then consult Figure 2 for better accuracy.

$$I_{C1(rms)} = P_{OUT} \times \sqrt{\frac{16 \times V_{BOOST}}{3 - \pi \times V_{AC(max)}} - 1}$$

(7)

The ratio of  $I_{C1(rms)}$  to  $I_{Q2}$  can be found by using the appropriate graph, Figure 3 for the 1X:1X oscillator option or Figure 4 for the 1X:2X oscillator option. To use the graphs, locate the ratio of VAC to  $V_{C1}$  along the horizontal axis then, draw a vertical line to the intersection of the curve for the duty ratio of the PWM stage. Draw a horizontal line from the intersection to the vertical axis and read the ratio of  $I_{C1(rms)}$  to  $I_{Q2}$ .

The current sense resistor for the PWM stage, R5, is selected so that at maximum current, its voltage is the threshold voltage of the peak current comparator (nominally 1.3 V).

$$R5 = \frac{V_{TH}(PWM \text{ stage} \times I_{LIMIT})}{i_{Q2(peak)}}$$

(8)

In many cases, an input line filter will be necessary in order to meet the requirements of an agency or application. The input line filter design has been omitted from this procedure due to the vast array of requirements and circumstances. We urge you to refer to Reference [11] for details.

#### PFC stage control

The PFC stage is designed in a three-step process. First, set the dynamic range of the multiplier, second, stabilize the average current control loop and third, stabilize the voltage loop that controls the energy storage capacitor voltage. Use as much of the dynamic range of the multiplier as possible. The current control loop must have wide bandwidth in order to follow the instantaneous rectified line voltage. The voltage loop must be slower than twice the ac line frequency so that it will not compromise the power factor.

#### multiplier

The dynamic range of the multiplier is a function of the currents and/or voltages of the IAC, VAOUT and VFF pins. Coordinate the selection process to use the full range of the multiplier and obtain the desired power limiting features. Select the components R1 and R15 to use the  $i_{IAC}(t)$  range and the  $V_{VFF}$  range under the condition that the maximum of the  $V_{VAOUT}$  range, described in equation 11. The selection process is similar to the selection process for UC3854, except for the VFF voltage and MOUT current limitations. [12] In this product series, the divide-by-square function is internally implemented so that it divides by the greater of 1.4 V or  $V_{VFF}$ . If the 1.4-V level controls the divider, power factor correction may still occur if the VAOUT level is within the functioning range of the multiplier. Power factor correction occurs during that condition because the multiplier section functions as a two-input multiplier, rather than a three-input multiplier. Notice that the voltage at the VFF pin will be proportional to the average of the IAC current. Typically,  $V_{VFF}$ =1.4 V at low ac line voltage is set as the design boundary; the upper boundary of  $V_{VFF}$  will remain within the range if the functional ac line voltage range varies by less than 4.3:1.

$$0 \le i_{IAC}(t) \le 500 \,\mu\text{A},$$

$$0 \le V_{VAOUT}(t) \le 5 \,\text{V},$$

$$1.4 \,\text{V} \le V_{VFF} \le V_{VREF} - 1.4 \,\text{V}$$

$$(9)$$

The selection process begins with the selection of R1 so that the peak  $I_{AC}$  current at high ac line is about 500  $\mu$ A, see Table 2. Second, select R15 for the minimum VFF voltage, also shown in Table 2. Third, select C8, in Table 2, to average the VFF voltage with sufficiently low ripple to meet a third harmonic distortion budget. For a system with a 3% THD target, it is typical to allow the feedforward circuit to contribute 1.5% third harmonic distortion to the input waveform [4]. An attenuation factor of 0.022 will meet the criteria. Finally, select the MOUT resistor in Table 2, R12, so that the voltage across R12 equals the voltage across sense resistor R2 under the condition of maximum power, minimum ac line voltage ( $V_{VFF,MIN}$ ), and VAOUT at its maximum level of 5 V. Experimentally, the multiplier output resistor, R12, may need to be increased slightly if the energy storage capacitor voltage sags under maximum load. This would be due to tolerances in the components and the multiplier. In order to minimize current amplifier offsets, set the value of the resistor on the ISENSE1 pin, R8, equal to the value of R12 as shown in Table 2.

REFERENCE **EQUATION NOTES DESIGNATOR**  $\sqrt{2}$  VAC(max) R1 set  $i_{IAC(peak)} = 500 \mu A$ I<sub>IAC(peak)</sub> VVFF(avgmin) R15 set  $V_{VFF(avgmin)} = 1.4 V$  $A_{FF(2)} = 0.022 \text{ for } 3\% \text{ THD}$ C8 k = 1VVFF(min) R12  $V_{VFF(min)} = 1.4V$  $V_{VAOUT(max)} = 5.0V$ R8 R12 Always change R8 if R12 is changed

Table 1.

#### PFC current loop control

This controller uses average current loop control for the PFC stage. The current control loop must typically be fast enough to track the rectified sinusoidal ac line voltage. There are many ways to design a controller that will stabilize the PFC current loop. The method that is described here achieves good results for most applications.<sup>[5]</sup> This method assumes that both the natural frequency of the system and the zero of the linearized boost PFC are much lower than both the switching frequency and the desired crossover frequency, f<sub>CO(pfc)</sub>, as described in equation 12. The left side of the inequality in equation 12 will usually be true since the capacitance of C1 is quite large.

$$\frac{1-D_{PWM(min)}}{\sqrt{\text{L1}\times\text{C1}}} \text{ and } \frac{2P_{\text{IN}}}{\text{C1}\times\text{V}_{\text{C1}}^{2}} << 2\times\pi\times\text{f}_{\text{CO(pfc)}} << 2\times\pi\times\text{f}_{\text{S(pfc)}} \tag{10}$$

The left side of the inequality should be at least a factor of 10 lower than the middle term; the right side of the inequality should be at least five times larger than the middle term. For the purposes of 50 Hz to 60 Hz power factor correction, good results can be achieved with the crossover frequency set to about 10 kHz. A lower crossover might be necessary if the switching frequency of the PWM stage is below 100 kHz, or if the compensator gain at the crossover frequency is large (over ~40 dB).

Upon selecting the crossover frequency, select R13 to set the gain at the crossover frequency, then select C6 to place a zero at the crossover frequency and select C7 to provide a pole at half of the switching frequency. The equations are in Table 3.

| REFERENCE<br>DESIGNATOR | EQUATION                                                                                       | NOTES                           |

|-------------------------|------------------------------------------------------------------------------------------------|---------------------------------|

| R13                     | $R12 \times \frac{2 \times \pi \times f_{CO(pfc)} \times L1 \times V_{CT\_BUFF(p-p)}}{V_{C1}}$ | V <sub>CT_BUFF(p-p)</sub> = 4 V |

| C6                      | $\frac{1}{R13 \times 2 \times \pi \times f_{CO(pfc)}}$                                         |                                 |

| C7                      | $\frac{1}{\pi \times f_{S(pfc)}}$                                                              |                                 |

Table 2.

#### PFC voltage loop

The voltage loop must crossover at a lower frequency than twice the ac line frequency so that voltage corrections will not interfere with power factor correction. Second harmonic ripple from the sensed  $V_{C1}$  voltage directly results in third harmonic distortion on the ac line, similar to ripple on the VFF voltage.

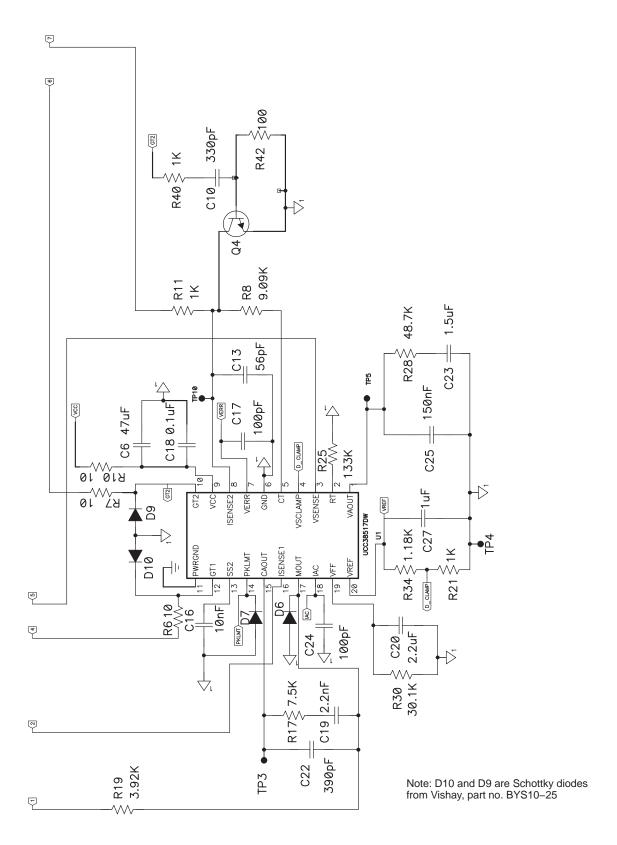

#### **PWM stage control**

The control elements of the PWM stage are the same as a typical isolated current program mode converter. The secondary elements include C12 to C14, D6, R22 to R25, U2 and U3, which perform the error amplifier, compensation and isolation functions. On the primary side, VERR is connected to the node between the opto-isolator output, U2, and a pull-up resistor, R17. Resistor R17 represents the gain in the conversion from the output current of opto-isolator U2 and the VERR input.

Slope compensation is programmed using resistors R18 and R11, which form a summing node at ISENSE2. The voltage at CT\_BUFF is a saw-tooth waveform that swings between 1 V and 5 V.

Many applications require a duty ratio limit for the PWM stage in order to prevent transformer saturation. Program the maximum duty ratio using the following ratio of resistors R16 to R19.

$$\frac{R16}{R19} = \frac{V_{VREF}}{1 + 4 \times D_{PWM(max)}} - 1 \tag{11}$$

#### Soft-start

The soft-start capacitor, C5, which is connected to SS2, controls the soft-start ramp of the PWM stage. The soft-start ramp begins when the VSENSE voltage exceeds 6.75 V. In order to avoid loop saturation, the soft-start ramp rate must be less than or equal to the open loop response of the PWM stage converter.

#### REFERENCE DESIGN

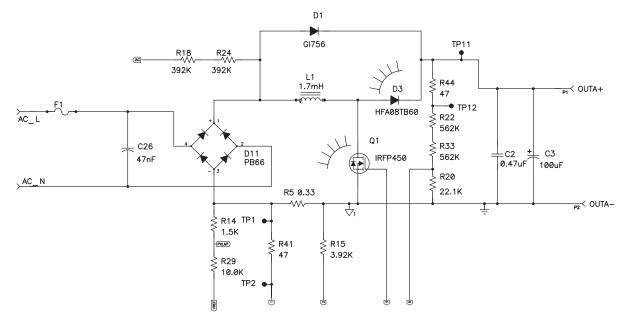

Universal line input 100-W PFC output with 12 V, 8-W bias rail supply design is discussed in UCC28517EVM, TI literature number SLUU117. UCC28517 is a closely related combo device to the UCC28521. The UCC28517 has 1:2 PFC:PWM frequency option. The schematic is shown in Figures 2, 3, 4. Please refer to the SLUU117 document on http://www.ti.com for further details.

Figure 2. Section A

Figure 3. Section B

#### **REFERENCE DESIGN**

Figure 4. Section C

**OSCILLATOR FREQUENCY** RT OVER VCC (11 V TO 15 V) (-40°C TO 105°C) 800 700 600 500 400 300 200 100 0 10 100 1000 RT – Timing Resistor –  $k\Omega$ Figure 14

#### **GT2 MAXIMUM DUTY CYCLE D\_MAX VOLTAGE** 100 100 kHz 90 %<sup>80</sup> 200 kHz 500 kHz 800 kHz 20 10 0 1.5 3.0 3.5 1.0 2.5 4.0 4.5 5.0 5.5 D\_MAX Voltage - V Figure 19

# MULTIPLIER CONSTANT POWER PERFORMANCE

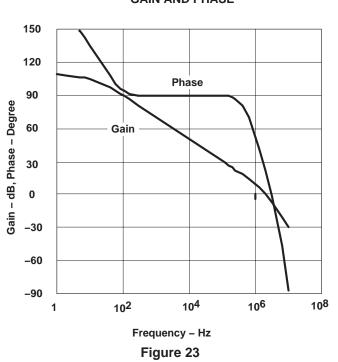

CURRENT AMPLIFIER OPEN LOOP

GAIN AND PHASE

**VOLTAGE AMPLIFIER TRANSCONDUCTANCE**

Figure 24

### Figure 25

# TYPICAL MINIMUM ON TIME vs

#### **REFERENCES**

- Evaluation Module and associated User's Guide, UCC28521EVM, Texas Instruments Literature Number SLUU218

- Datasheet, UCC38500/1/2/3 BiCMOS PFC/PWM Combination Controller, Texas Instruments Literature Number SLUS419C

- 3. Power Supply Seminar SEM–600, *High Power Factor Preregulator for Off-line Power Supplies*, L.H. Dixon, Texas Instruments Literature Number SLUP087

- 4. Power Supply Seminar SEM–700, *Optimizing the Design of a High Power Factor Switching Preregulator*, L.H. Dixon, Texas Instruments Literature Number SLUP093

- 5. Power Supply Seminar SEM-1500 Topic 2, *Designing High-Power Factor Off-Line Power Supplies*, by James P. Noon

- Application Note, UC3854 Controlled Power Factor Correction Circuit Design, Texas Instruments Literature Number SLUA144

- 7. Design Note, Optimizing Performance in UC3854 Power Factor Correction, Texas Instruments Literature Number SLUA172

- 8. Design Note, *UC3854A and UC3854B Advanced Power Factor Correction Control ICs*, Texas Instruments Literature Number SLUA177

- 9. Design Note, UC3854A/B and UC3855A/B Provide Power Limiting with Sinusoidal Input Current for PFC Front Ends, Texas Instruments Literature Number SLUA196

- 10. Laszlo Balogh, A Design and Application Guide for High Speed Power MOSFET Gate Drive Circuits, 2001 Power Supply Design Seminar Manual SEM1400, 2001

- 11. Bob Mammano and Bruce Carsten, *Understanding and Optimizing Electromagnetic Compatibility in Switchmode Power Supplies*, 2002 Power Supply Design Seminar Manual SEM1500, 2002

#### **RELATED PRODUCTS**

| PART NUMBER    | DESCRIPTION                                                                                 | COMMENTS                                                                                     |  |  |

|----------------|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--|--|

| UCC28510-17    | Advanced BiCMOS PFC/PWM combination controllers                                             | 1:1 or 1:2 frequency option; leading edge, trailing edge modulation, programmable PWM Max dc |  |  |

| UCC38500/1/2/3 | BiCMOS PFC/PWM combination controller                                                       | 1:1 leading edge, trailing edge modulation, 50% PWM Max dc                                   |  |  |

| UCC3817/18     | BiCMOS power factor preregulator                                                            | High PF, UC3854 compatible, leading edge trailing edge modulation                            |  |  |

| UCC3819        | Programmable output power factor preregulator                                               | Tracking boost topology for dynamic output voltage adjustments                               |  |  |

| UC3854         | High Power Factor Preregulator                                                              | High PF, industry standard PFC controller; 35 V <sub>CC</sub> max                            |  |  |

| UC3854A/B      | Enhanced high power factor preregulator                                                     | Improved high PF, industry standard PFC controller; 22 V <sub>CC</sub> max                   |  |  |

| UC3855A/B      | High performance power factor preregulator                                                  | ZVT output for lower EMI emission & higher efficiencies                                      |  |  |

| UC3853         | High power factor preregulator  8-Pin package; simplified architecture to minimized exnents |                                                                                              |  |  |

| UCC38050       | Transition mode PFC controller                                                              | Constant on-time transition mode PFC controller                                              |  |  |

| UC3852         | High power factor preregulator                                                              | Constant off-time transition mode PFC controller; 30 V <sub>CC</sub> max                     |  |  |

#### **REVISION HISTORY**

| REVISION | DATE    | CHANGE                           |  |  |  |  |

|----------|---------|----------------------------------|--|--|--|--|

| SLUS608B | 6/27/05 | Corrected CAOUT pin description. |  |  |  |  |

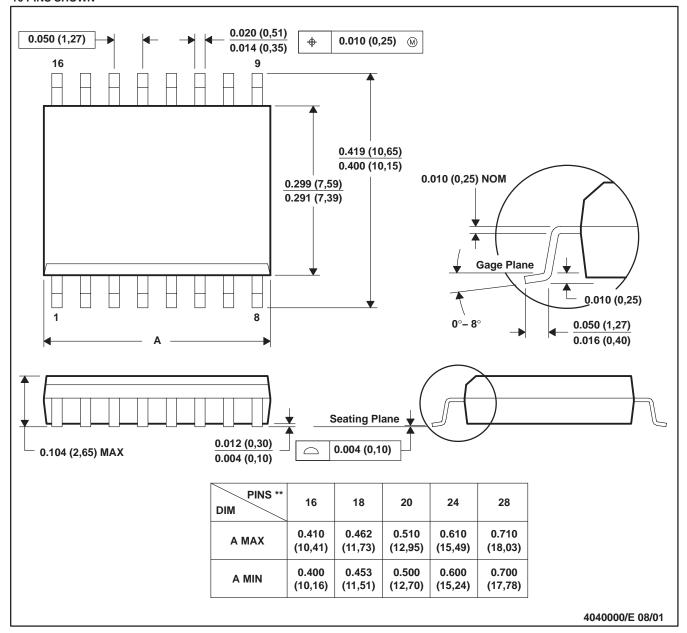

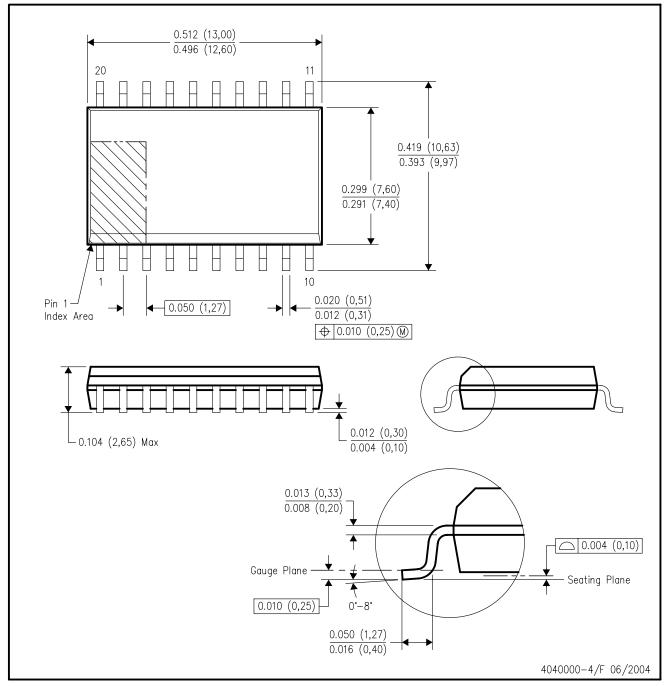

#### **MECHANICAL DATA**

#### DW (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

#### **16 PINS SHOWN**

NOTES: A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013

i.com 16-Mar-2007

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| UCC28521DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28521DWG4     | ACTIVE                | SOIC            | DW                 | 20   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28521DWR      | ACTIVE                | SOIC            | DW                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28521DWRG4    | ACTIVE                | SOIC            | DW                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28528DW       | ACTIVE                | SOIC            | DW                 | 20   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28528DWG4     | ACTIVE                | SOIC            | DW                 | 20   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28528DWR      | ACTIVE                | SOIC            | DW                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

| UCC28528DWRG4    | ACTIVE                | SOIC            | DW                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-1-260C-UNLIM           |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

11-Mar-2008

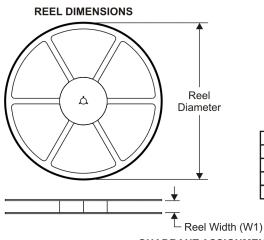

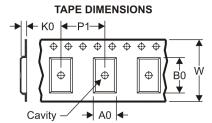

#### TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

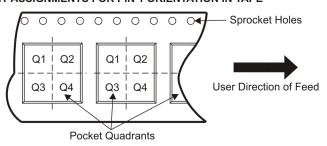

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device      | Package<br>Type | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|-------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| UCC28521DWR | SOIC            | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8    | 13.0    | 2.7     | 12.0       | 24.0      | Q1               |

| UCC28528DWR | SOIC            | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8    | 13.0    | 2.7     | 12.0       | 24.0      | Q1               |

## PACKAGE MATERIALS INFORMATION

11-Mar-2008

#### \*All dimensions are nominal

| Device      | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|-------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UCC28521DWR | SOIC         | DW              | 20   | 2000 | 346.0       | 346.0      | 41.0        |

| UCC28528DWR | SOIC         | DW              | 20   | 2000 | 346.0       | 346.0      | 41.0        |

## DW (R-PDSO-G20)

## PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AC.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

#### **Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mamt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

| www.ti.com/audio          |

|---------------------------|

| www.ti.com/automotive     |

| www.ti.com/broadband      |

| www.ti.com/digitalcontrol |

| www.ti.com/medical        |

| www.ti.com/military       |

| www.ti.com/opticalnetwork |

| www.ti.com/security       |

| www.ti.com/telephony      |

| www.ti.com/video          |

| www.ti.com/wireless       |

|                           |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2008, Texas Instruments Incorporated