UC1638 UC2638 UC3638

# Advanced PWM Motor Controller

#### **FEATURES**

- Single or Dual Supply Operation

- Accurate High Speed Oscillator

- Differential X5 Current Sense Amplifier

- Bidirectional Pulse-by-Pulse Current Limiting

- Programmable Oscillator Amplitude and PWM Deadband

- Dual 500mA Totem Pole Output Drivers

- Dual 60V, 50mA Open Collector Drivers

- Undervoltage Lockout

#### DESCRIPTION

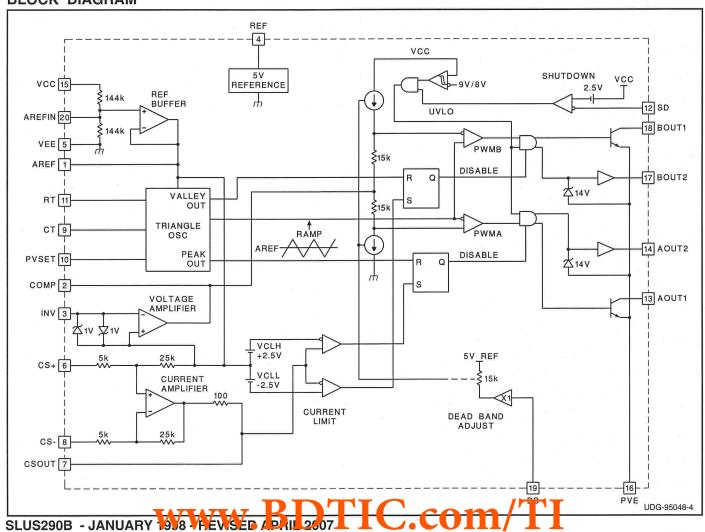

The UC1638 family of integrated circuits are advanced pulse width modulators intended for a variety of PWM motor drive and amplifier applications requiring either uni-directional or bi-directional drive circuits. Similar in architecture to the UC1637, all necessary circuitry is included to generate an analog error signal and modulate two bi-directional pulse train outputs in proportion to the error signal magnitude and polarity.

Key features of the UC1638 include a programmable high speed triangle oscillator, a 5X differential current sensing amplifier, a high slew rate error amplifier, high speed PWM comparators, and two 50mA open collector as well as two  $\pm 500$ mA totem pole output stages. The individual circuit blocks are designed to provide practical operation to switching frequencies of 500kHz.

Significant improvements in circuit speed, elimination of many external programming components, and the inclusion of a differential current sense amplifier, allow this controller to be specified for higher performance applications, yet maintain the flexibility of the UC1637. The current sense amplifier in conjunction with the error amplifier can be configured for average current feedback. The additional open collector outputs provide a drive signal

continued

#### **BLOCK DIAGRAM**

#### **DESCRIPTION** (cont.)

for the highside switches in a full bridge configuration. The programmable AREFIN pin allows for single or dual supply operation. Oscillator ramp amplitude and PWM deadband are programmable by tapping a voltage divider off the 5V reference to the appropriate programming input (PVSET or DB).

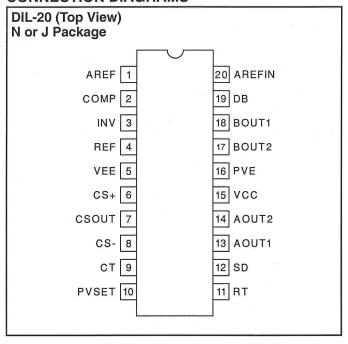

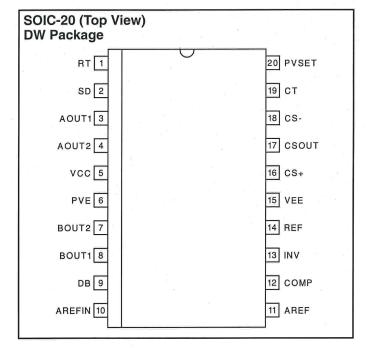

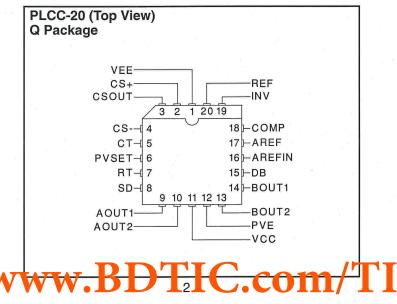

Additional features include a precision externally available 5V reference, undervoltage lockout, pulse-by-pulse peak current limiting, and a remote shutdown port. The UC1638 family is available in the 20 pin N, DW and J packages. Consult the factory for other packaging options.

#### ABSOLUTE MAXIMUM RATINGS

| Supply Voltage VCC (referenced to VEE)40V                        |

|------------------------------------------------------------------|

| Output Drivers (AOUT2, BOUT2)                                    |

| Currents (continuous)                                            |

| Currents (peak)                                                  |

| REF Output Current Internally Limited                            |

| PVSET, DB, RT, INV, REF, CSOUT 0.3 to 10V                        |

| CS+, CSVEE-1V to VCC                                             |

| CT, AREF, AREFIN, COMP, SD VEE - 0.3                             |

| Output Voltage (AOUT1, BOUT1) 60V                                |

| Storage temperature65°C to +150°C                                |

| Junction Temperature55°C to +150°C                               |

| Lead temperature (soldering, 10 sec.)+300°C                      |

| Currents are positive into, negative out of the specified termi- |

| nal. Consult packaging section of data book for thermal limita-  |

| tion considerations of packages.                                 |

#### **CONNECTION DIAGRAMS**

#### **ELECTRICAL CHARACTERISTICS**

Unless otherwise specified; VCC = 15V, VEE =-15V, CT = 680pF, RT = 3k, VPVSET = 1.5V, VCOMP = 0V, VCSOUT = 0V, VDB = REF, VEXTREF = 0V, VSD = VCC - 3V, TA =  $-55^{\circ}$ C to 125 $^{\circ}$ C for the UC1638,  $-25^{\circ}$ C to 85 $^{\circ}$ C for the UC2638, 0 $^{\circ}$ C to 70 $^{\circ}$ C for the UC3638. TA = TJ.

|                                       | $0^{\circ}$ C to $70^{\circ}$ C for the UC3638. TA = TJ. |       |       | r     |       |

|---------------------------------------|----------------------------------------------------------|-------|-------|-------|-------|

| PARAMETER                             | TEST CONDITIONS                                          | MIN   | TYP   | MAX   | UNITS |

| Overall                               |                                                          |       |       |       |       |

| Supply Current, Operating             |                                                          |       | 15    | 23    | mA    |

| UVLO Threshold                        | Reference to VEE                                         |       | 9     | 10    | V     |

| UVLO Hysteresis                       | Reference to VEE                                         |       | 1     |       | V     |

| Voltage Amplifier                     |                                                          |       |       |       |       |

| Input Offset Voltage                  | COMP = 0V                                                | -20   | 0     | 20    | mV    |

| VSENSE Bias Current                   |                                                          | 0     | 0.5   | 2     | μΑ    |

| Open Loop Gain                        | COMP = -5V  to  +5V                                      | 75    | 100   | 2 2   | dB    |

| CMRR                                  | Vcm = -5V to +5V                                         | 70    | 100   |       | dB    |

| PSRR                                  | VCM = 0V, $VCC - VEE = 10V$ to $36V$                     | 70    | 90    | 1     | dB    |

| Vout High                             | INV = -0.1V, $RL = 10k$                                  | 13    | 13.6  |       | V     |

| Vout Low                              | INV = +0.1V, $RL = 10k$                                  |       | -13.8 | -13   | V     |

| Slew Rate Rising and Falling          | Overdrive = ±1V                                          |       | 12    |       | V/µs  |

| Output Source Current                 | COMP Shorted to VEE                                      | 5     | 15    |       | mA    |

| Output Sink Current                   | COMP Shorted to VCC                                      | 15    | 40    | 1     | mA    |

| Gain Bandwidth Product                | Fin = 100kHz, 10mV p-p                                   | 1     | 5     |       | MHz   |

| 5V Reference                          |                                                          |       |       |       |       |

| Output Voltage                        | IREF = −1mA, TA = 25°C                                   | 4.925 | 5     | 5.075 | ٧     |

| Output Voltage                        | IREF = -1mA                                              | 4.875 | 5     | 5.125 | V     |

| Load Regulation                       | IREF = -1mA to -10mA                                     | -15   | 2     | 15    | mV    |

| Line Regulation                       | VCC - VEE = 10V to 36V                                   | _15   | 2     | 15    | mV    |

| Short Circuit Current                 | VREF = 0V                                                | 15    | 70    |       | mΑ    |

| Oscillator                            |                                                          |       |       |       |       |

| Initial Accuracy                      | $TA = 0^{\circ}C - 70^{\circ}C$                          | 86    | 98    | 110   | kHz   |

| Voltage Stability                     | VCC - VEE = 10V to 36V                                   |       | 2     |       | %     |

| Total Variation                       | Line, Temperature                                        | 76    | 98    | 120   | kHz   |

| PVSET Input Bias Current              |                                                          |       | 0.5   | 3     | μΑ    |

| PVSET Input Voltage Range             | (Note 1)                                                 | 0.5   | 1     | VREF  | V     |

| Amplitude Limit                       | (Note 1)                                                 | VEE+3 |       | VCC-3 | ٧     |

| AOUT1, BOUT1 Output Drivers           |                                                          |       |       |       |       |

| Output Low Voltage                    | IOUT = 1mA, Ref. to PVE, PVE = 0V                        |       | 0.9   | 1.3   | V     |

|                                       | IOUT = 50mA                                              | 1     | 1.2   | 1.8   | V     |

| Leakage Current                       | Output Voltage = 50V                                     |       | 0.1   | 50    | μА    |

| AOUT2, BOUT2 Output Drivers           |                                                          | Si    |       |       |       |

| Output High Voltage                   | IOUT = -20mA, Ref. to PVE, PVE = 0V                      | 12.2  | 13.5  |       | V     |

|                                       | IOUT = -100mA, Ref. to PVE, PVE = 0V                     | 12    | 13.5  |       | V     |

| Output High Clamp Level               | IOUT = -20mA, Ref. to PVE, PVE = VEE                     |       | 14.4  | 16.5  | V     |

| Output Low Voltage                    | IOUT = 20mA, Ref. to PVE, PVE = 0V                       |       | 0.4   | 1     | V     |

| · · · · · · · · · · · · · · · · · · · | IOUT = 100mA, Ref. to PVE, PVE = 0V                      |       | 0.6   | 2.2   | V     |

| Output Rise Time                      | COUT = 1nF                                               |       | 50    | 100   | ns    |

| Output Fall Time                      | Cout = 1nF                                               |       | 50    | 100   | ns    |

# www.BDTIC.com/TI

# **ELECTRICAL CHARACTERISTICS** (continued)

Unless otherwise specified; VCC = 15V, VEE =-15V, CT = 680pF, RT = 3k, VPVSET = 1.5V, VCOMP = 0V, VCSOUT = 0V, VDB = REF, VEXTREF = 0V, VSD = VCC -3V, TA =  $-55^{\circ}$ C to 125 $^{\circ}$ C for the UC1638,  $-25^{\circ}$ C to 85 $^{\circ}$ C for the UC2638, 0 $^{\circ}$ C to 70 $^{\circ}$ C for the UC3638. TA = TJ.

| PARAMETER                    | TEST CONDITIONS              | MIN   | TYP    | MAX   | UNITS   |

|------------------------------|------------------------------|-------|--------|-------|---------|

| X5 Amplifier                 |                              | 1     |        |       |         |

| Gain                         | VID = 100mV to 400mV         | 4.75  | 5      | 5.25  | V/V     |

| Common Mode Rejection        | Vcs+, Vcs- = AREF ±5V        | 50    | 65     |       | dB      |

| -3dB Bandwidth               |                              | 300   | 400    |       | kHz     |

| Slew Rate Rising             |                              | .75   | 1.5    |       | V/μs    |

| Slew Rate Falling            |                              | .75   | 1.5    |       | V/μs    |

| Shutdown                     |                              |       |        |       |         |

| Threshold                    | Ref. to VCC                  | - 1.9 | - 2.25 | - 2.5 | , V     |

| Input Bias Current           | VsD = SD Threshold           |       | -0.5   | -10   | μА      |

| Current Limit                |                              |       |        |       | * , * . |

| Threshold Positive           | Measured Between CS+ and CS- | 400   | 500    | 600   | mV      |

| Threshold Negative           | Measured Between CS+ and CS- | - 600 | - 500  | - 400 | mV      |

| Propagation Delay to Outputs | Overdrive = 200mV            |       | 150    | 250   | ns      |

| Deadband Adjust              |                              |       |        |       |         |

| Maximum Deadband             | VDB = 0V                     |       | ±5     |       | V       |

| Zero Deadband                | VDB = REF                    | e e   | 0      | 1     | V       |

| Deadband Adjustment Gain     | VDB = 1V to 4V (Note 2)      | ± 0.9 | ±1     | ± 1.2 | V/V     |

| Input Bias Current           | VDB = VREF                   |       | 3      | 15    | μΑ      |

| AREF Buffer                  |                              |       |        | 101   |         |

| Gain                         | AREF / VCC – VEE             | 0.49  | 0.5    | 0.51  | V/V     |

| Offset                       | (Note 3)                     |       | 30     | 100   | mV      |

Note 1: Oscillator triangle amplitude =  $2.5 \cdot PV \pm AREF$ .

Note 2: Deadband =  $\pm$ (REF - DB), referenced to COMP.

Note 3: Offset = AREFIN - AREF.

#### PIN DESCRIPTIONS

**AOUT1, BOUT1:** AOUT1 and BOUT1 are open collector output drivers capable of sinking 50mA. These outputs can be pulled up to 60V maximum. With a few external components, these outputs can drive the opposite high side switches in a full bridge arrangement.

**AOUT2, BOUT2:** AOUT2 and BOUT2 are totem pole output drivers capable of driving external power MOS-FETs directly. The peak current ratings are ±500mA. An integrated zener clamp limits the drive output amplitude to approximately 14V to prevent MOSFET gate oxide overstress. These outputs are configured to drive the opposite low side switches in a full bridge arrangement.

AREF: The voltage on AREF is simply a buffered version of the voltage on AREFIN. In single supply applications, AREF should be bypassed to VEE with a 0.1µF ceramic capacitor to provide a stable reference level for the internal circuitry.

AREFIN: The voltage on AREFIN is generated internally by a 50% voltage divider tied between VCC and VEE. As such, it provides the mid supply reference needed for the oscillator, voltage amplifier, current amplifier and current limit comparators when operating in single supply mode. A buffer amplifier is connected between AREFIN and AREF. In bipolar supply applications AREFIN is usually connected to VEE, which disables the buffer amplifier, and AREF is connected to 0V.

**COMP:** This is the output of the high slew rate error amplifier. The level on COMP modulates the controller duty cycle via the PWM comparators and the oscillator ramp. Compensation and DC gain setting resistors are connected between COMP and INV.

www.BDTIC.com/TI

#### PIN DESCRIPTIONS (cont.)

CS-: This is the inverting input to the X5 current sense amplifier. The common mode input range for this pin extends from VEE-1V to VCC-4V. A low value resistor in series with the source or emitter of the low side switch in the full bridge develops the signal that is applied to this pin. At differential inputs of ±500mV typical (referenced to CS+)the controller reaches the current limit level, which truncates the output pulse.

**CS+:** This is the non-inverting input to the X5 current sense amplifier. The common mode input range for this pin extends from VEE-1V to VCC-4V. The characteristics for this pin are identical to CS-.

CSOUT: This is the output of the X5 current sense amplifier. Voltage levels greater than  $\pm 2.5 V$  referenced to AREF will cause the device to enter current limit. When the CT voltage gets to within a diode drop of its peak the BouT current limit latch gets reset and conversely when CT ramp gets to within a diode drop of the valley the AouT current limit latch gets reset. An internal  $100\text{-}\Omega$  resistor between the amplifier output and CSOUT is provided to create a high frequency noise filter with an external capacitor to VEE. When used for average current feedback, CSOUT is summed into INV.

CT: A capacitor from CT to VEE will set the triangle oscillator frequency according to the following equation:

$$F = \frac{1}{5 \cdot RT \cdot CT}$$

The waveform on CT is symmetrical about the voltage on AREF and is applied internally to the inputs of hte PWM comparators. Use a high quality ceramic capacitor with low ESL and ESR for best results. A minimum CT value of 200 pF insures good accuracy and less susceptibility to circuit layout parasitics. The oscilator and PWM are designed to provide practical operation to 500kHz.

**DB:** This high impedance input programs output pulse train deadtime. A stable DC voltage between 0V and REF will set a bi-directional deadband centered about the level on COMP. The deadband level is equal to: 5V – VDB. That is, 1V on DB will program ±4V of deadband centered about the COMP pin level. A convenient method for generating the programming level is a voltage divider tap off of REF.

INV: This is the inverting input to the Voltage amplifier. The common mode input range for this pin extends from VEE+2V to VCC-1V. It can be tied to a command signal generated by a rate feedback element or to a position control signal. In average current feedback applications, this input is tied to the output of the X5 current sensing amplifier (CSOUT).

**PVE:** This is the high current ground for the IC. The external MOSFET driver transistors are referenced to this ground. Internal level shifting circuitry gives the option of tying this pin to VEE, or the system ground in split supply applications.

**PVSET:** A DC voltage on PVSET programs the upper and lower thresholds for the oscillator by the following relationship:

VPK - VVLY = 5 • VPVSET.

The input voltage range on PVSET is 0.5V to REF.

**REF:** REF is the output of the precision reference. The output is capable of supplying 15mA to peripheral circuitry and is internally short circuit current limited. Bypass REF to VEE with a  $0.1\mu F$  ceramic capacitor for best performance.

RT: A single resistor from RT to VEE sets the charging and discharging currents for the triangle oscillator. The actual charge and discharge is 2X the current programmed by RT and PVSET. For best performance the current out of RT should be limited to 1mA. The voltage level on the RT pin is a buffered version of the PVSET pin voltage. Therefore, if the PVSET voltage divider is tied between VCC and VEE to incorporate line feedforward, the triangle waveform frequency will remain constant.

**SD:** A voltage on SD within 2.5V (typical) of VCC will cause the UC3638 to enter a UVLO condition which disables all of the driver outputs. With an external voltage divider across VCC and VEE, and a capacitor between SD and VCC, a delayed turn-on characteristic can be generated. Since the 2.5V threshold is temperature stabilized it can also be used as a higher UVLO threshold for applications which require a starting voltage higher than the internal 9V UVLO threshold.

**VEE:** All voltages are measured with respect to this pin. All bypass capacitors and timing components except those listed under the PVE section should be connected to this pin. Component leads should be as short and direct as possible. VEE is generally connected to the most negative voltage supply in the system. In single supply applications, VEE is tied to the system ground.

VCC: Positive supply rail for the IC. Bypass this pin to VEE and PVE with 0.1 to  $1\mu F$  low ESL, ESR ceramic capacitor(s). The maximum voltage for VCC is 40V referenced to VEE. The turn on voltage level on VCC is 9V with 1V of hysteresis.

# www.BDT<sub>5</sub>IC.com/TI

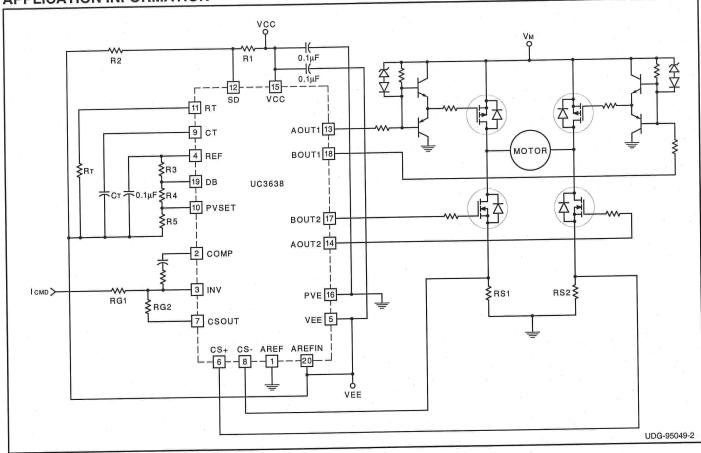

#### APPLICATION INFORMATION

Figure 1. Average Motor Current Control Loop

The UC3638 is designed to provide pulse width modulation control of DC brush motors in applications requiring precision torque, velocity, or position control. Due to its high frequency capability, other high power applications such as switch mode audio amplifiers can also be addressed. Through a combination of circuit sophistication and integration, the designer can maintain a high level of flexibility, while reducing cost compared to solutions using other PWM ICs.

Figure 1 shows a typical application circuit for the UC3638. By taking advantage of the UC3638's many integrated functions, a low cost and compact average current mode motor controller can be designed. Depending on the level of complexity, as many as 15 discrete components and an additional high bandwidth amplifier can be saved compared to a similar circuit using the UC3637 PWM controller.

### Oscillator Section and Modulation Scheme

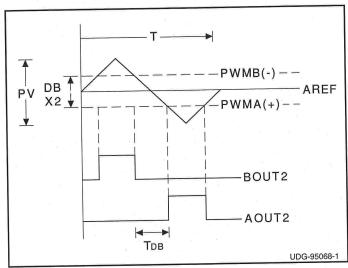

Figure 2 depicts the UC3638 oscillator and PWM waveforms for the condition where the output of the voltage amplifier (COMP) is at the null point (same voltage as AREF). For applications using split voltage supply rails. AREF will normally be into the system grand. This re-

sults in a voltage null point of zero volts. For this condition, AREFIN should be tied to the negative voltage supply rail (VEE), which disables the internal voltage buffer, allowing AREF to be tied to ground. For a single supply system, AREFIN should be left open circuit, and AREF should be decoupled to VEE (system ground) with at least  $0.1\mu F$ . The resulting voltage null point for this case

Figure 2, Oscillator and PWM Waveforms

### **APPLICATION INFORMATION (cont.)**

will be half way between ground and VCC, and will automatically track changes in VCC. For cases where a different null point is desired, AREF can be tied to any voltage between VEE + 2V and VCC - 2V. Of course the user must also allow sufficient headroom for the triangle waveform.

Once the system null point has been chosen, the triangle wave amplitude and PWM deadband must be programmed. The amplitude of the triangle wave is determined by trading off noise immunity and gain requirements. In general, the larger the triangle wave amplitude, the greater the immunity to premature termination of PWM pulses due to switching noise. However, high amplitude triangle waves require a greater voltage swing at the output of the voltage amplifier which ultimately reduces forward loop gain.

Programming the PWM deadband allows the user to trade off gain linearity requirements with power amplifier efficiency. If the modulator is configured as in Figure 1, motor current is alternately pulsed by diagonally opposite drive FETs when the servo loop is at null. By adjusting the deadband, the user can program the offset voltage at the input of the PWM comparators. This offset results in deadtime, or time when neither PWM signal is active.

A minimum amount of deadtime is always recommended to provide cross conduction protection at the power amplifier. Setting the deadtime to this minimum level will provide the maximum motor stiffness or holding torque, at the expense of power losses in the output stage. These losses result from the fact that the power amplifier is always sourcing motor current, even at null. As deadtime is increased, amplifier losses at null become less, at the expense of nonlinearity in the gain function. Eventually, if the deadband voltage is increased to equal the amplitude of the triangle wave, error voltages at the null point will result in no PWM pulsing, or a dead zone. After the triangle waveform amplitude and deadband are selected, the operating frequency is easily set by proper selection of CT and RT.

Referring to Figure 1, if the voltage supply rails are  $\pm 15V$ , and the desired triangle wave oscillator amplitude is 6V p-p, PVSET is set by:

$$VPK - VVLY = 5 \cdot VPVSET$$

$VPVSET = \frac{6}{5} = 1.2V$

If 1V of deadband is chosen:

$$5 - VDB = 1V$$

$VDB = 4V$

In order to select the programming resistors, a source current for the reference is first selected. For a 1mA source current:

R3 + R4 + R5 =

$$\frac{5}{\text{ISOURCE}} = \frac{5}{1\text{mA}} = 5\text{k}$$

R3 =  $\frac{5 \cdot \text{VDB}}{\text{ISOURCE}} = \frac{1\text{V}}{1\text{mA}} = 1\text{k}$

R4 =  $\frac{\text{VDB} \cdot \text{VPVSET}}{\text{ISOURCE}} = \frac{4\text{V} \cdot 1.2\text{V}}{1\text{mA}} = 2.8\text{k}$

R5 = 5k - 1k - 2.8k = 1.2k

All of the voltages described by these equations are referenced to the negative supply rail. In other words, for a split supply system, VREF is actually a negative voltage referenced to ground.

The oscillator frequency is programmed by proper selection of RT and CT. If 220pF is chosen for CT, and an operating frequency of 30kHz is desired, RT is chosen by:

$$F = \frac{1}{5 \cdot RT \cdot CT}$$

$$30kHz = \frac{1}{5 \cdot 220pF \cdot RT}$$

$$RT = 30k$$

With RT = 30k, the charge current out of the RT pin is limited to

$$\frac{1.2V}{30k} = 40\mu A$$

which is well within the specified maximum of 1mA.

To calculate the actual deadtime or minimum time between PWM pulses (TDB), the ratio of the deadband voltage to the triangle wave amplitude is multiplied by half the oscillator period:

TDB =

$$\frac{DB}{VPK - VVLY} \cdot \frac{1}{f}$$

=  $\frac{5 - VDB}{5 \cdot VPVSET} \cdot (5 \cdot RT \cdot CT)$

=  $\frac{(5 - VDB) \cdot RT \cdot CT}{VPVSET}$

For this example the deadtime is:

$$TDB = \frac{1 \cdot 30k \cdot 220pF}{1.2} = 5.5 \mu sec$$

If voltage feedforward is desired, PVSET should be derived off of the supply rails instead of VREF. This way changes in the supply voltage will linearly regulate the modulator gain, which decreases control loop susceptibility to line voltage variations. Since the voltage on the RT pin is a buffered version of PVSET, charge current tacks oscillar ramplitude and therefore the frequency

#### **APPLICATION INFORMATION (cont.)**

remains constant, preventing low frequency oscillator modulation in the presence of line voltage changes.

#### **Output Drivers**

The output driver section provides separate output drivers for high and low side drive of both PWM signals. For many applications, the 500mA peak output current capability of the low side drivers (AOUT2 and BOUT2) is sufficient to directly connect to the appropriate low side MOSFETs of the H-bridge. A current limiting gate resistor may be used to control switching time if high levels of dv/dt or di/dt are expected at the drains of the MOSFETs. If more current drive capability is required, the PWM drive signals can be buffered with bipolar transistors.

The open collector high side drivers (AOUT1 and BOUT1) are designed to control high side P-channel MOSFETs. Depending on voltage and speed requirements, the driver stage can be simplified from the one shown on Figure 1. If high side N-channel MOSFETs are desired, a boot strap or charge pump based drive circuit can be used as long as 100% duty cycle operation is not required.

#### **Average Current Control**

The UC3638 incorporates all of the necessary features for precise average current loop control of a DC motor. In the circuit shown in Figure 1, motor current is sensed differentially across two current sense resistors. By using two current sense resistors both the current sourced from the motor voltage supply (Vm) and the flyback current are sensed in the correct polarity to provide true torque control. If only one current sensed resistor is used, the flyback current will circulate through the body diodes of the lower MOSFETs and bypass the current sense resistor. The result will be a duty cycle dependent error term in the loop torque control function. In order to prevent high frequency spikes from contributing excessive error to the current control loop, the switching speed of the MOSFETs must be controlled so that significant transient current spikes do not couple across the drain to source capacitance of the MOSFETs.

The X5 current amplifier multiplies the current signal by a factor of 5 and feeds the average current signal into the error amplifier. A window comparator detects if the peak current signal at the output of the current amplifier has a magnitude greater than 2.5V in either polarity and provides pulse-by-pulse peak current limiting. The loop should be designed so that peak motor current never reaches this level during normal operation.

With integral compensation, the average current loop will have very high DC gain, resulting in effectively no average DC motor current error. For stability purposes, the high frequency gain of the voltage error amplifier must be designed such that magnitude of the slope of the error amplifier output (COMP) must be less than or equal to the magnitude of the slope of the triangle waveform.

If RS1 = RS2 = RS, the DC gain of the current control loop can be calculated as:

$$\frac{\text{IMOTOR}}{\text{ICMD}} = \frac{\text{RG2}}{5 \cdot \text{RS}}$$

If the UC3638 is set up in a simple velocity or position control loop, the feedback voltage (speed or position) is summed directly into the voltage error amplifier, and the current sense amplifier is only used for peak current limit control. The motor can also be replaced by another high power device, such as an audio speaker, and the same type of amplifier can be used. In the case of audio however, a higher switching frequency will probably be desired to prevent switching noise from infiltrating the audio frequency range.

#### **UVLO** and Shutdown

The UC3638 contains undervoltage lockout (UVLO) circuitry to prevent unwanted bridge turn-on before sufficient supply voltage is available. The open collector drivers (AOUT1 and BOUT1) are held off (no sink current) and the totem pole drivers (AOUT 2 and BOUT2) are pulled low until the voltage between VCC and VEE reaches 9V typical. The UVLO circuitry becomes active at approximately 1V, and before this level the totem pole drivers are held low with passive pull down resistors.

The shutdown pin holds the output drivers in their inactive state unless it is pulled 2.5V below VCC. An open collector gate or transistor can be used as an external enable signal, or a turn-on voltage higher than UVLO can be programmed with a resistive divider. In the case of Figure 1, the turn on voltage VSTART can be calculated as:

$$VSTART = \frac{2.5 \bullet (R1 + R2)}{R1}$$

If a delayed start is desired, a capacitor can be placed in parallel with R1 to slow down the change in voltage at the shutdown pin, and thus provide a user programmable startup time.

#### PACKAGE OPTION ADDENDUM

www.ti.com 6-May-2009

#### **PACKAGING INFORMATION**

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp (3)   |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|---------------------|

| UC2638DW         | NRND                  | SOIC            | DW                 | 20   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| UC2638DWG4       | NRND                  | SOIC            | DW                 | 20   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| UC2638DWTR       | NRND                  | SOIC            | DW                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| UC2638DWTRG4     | NRND                  | SOIC            | DW                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| UC2638N          | NRND                  | PDIP            | N                  | 20   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type  |

| UC2638NG4        | NRND                  | PDIP            | N                  | 20   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type  |

| UC3638DW         | ACTIVE                | SOIC            | DW                 | 20   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| UC3638DWG4       | ACTIVE                | SOIC            | DW                 | 20   | 25             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| UC3638DWTR       | ACTIVE                | SOIC            | DW                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| UC3638DWTRG4     | ACTIVE                | SOIC            | DW                 | 20   | 2000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR |

| UC3638N          | ACTIVE                | PDIP            | N                  | 20   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type  |

| UC3638NG4        | ACTIVE                | PDIP            | N                  | 20   | 20             | Green (RoHS & no Sb/Br)   | CU NIPDAU        | N / A for Pkg Type  |

| UC3638Q          | ACTIVE                | PLCC            | FN                 | 20   | 46             | Green (RoHS & no Sb/Br)   | CU SN            | Level-2-260C-1 YEAR |

| UC3638QG3        | ACTIVE                | PLCC            | FN                 | 20   | 46             | Green (RoHS & no Sb/Br)   | CU SN            | Level-2-260C-1 YEAR |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is

#### PACKAGE OPTION ADDENDUM

www.ti.com 6-May-2009

provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### OTHER QUALIFIED VERSIONS OF UC3638:

Military: UC1638

NOTE: Qualified Version Definitions:

• Military - QML certified for Military and Defense Applications

### PACKAGE MATERIALS INFORMATION

www.ti.com 21-Apr-2009

#### TAPE AND REEL INFORMATION

|    | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

| B0 | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

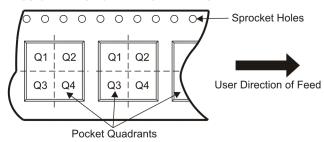

#### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

#### \*All dimensions are nominal

| Device     |      | Package<br>Drawing |    |      | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|------------|------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| UC2638DWTR | SOIC | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8    | 13.0    | 2.7     | 12.0       | 24.0      | Q1               |

| UC3638DWTR | SOIC | DW                 | 20 | 2000 | 330.0                    | 24.4                     | 10.8    | 13.0    | 2.7     | 12.0       | 24.0      | Q1               |

# PACKAGE MATERIALS INFORMATION

www.ti.com 21-Apr-2009

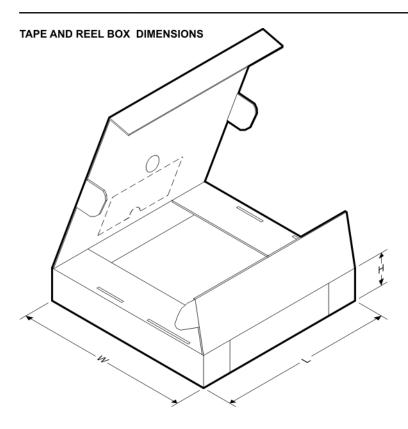

#### \*All dimensions are nominal

| Device     | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|------------|--------------|-----------------|------|------|-------------|------------|-------------|

| UC2638DWTR | SOIC         | DW              | 20   | 2000 | 346.0       | 346.0      | 41.0        |

| UC3638DWTR | SOIC         | DW              | 20   | 2000 | 346.0       | 346.0      | 41.0        |

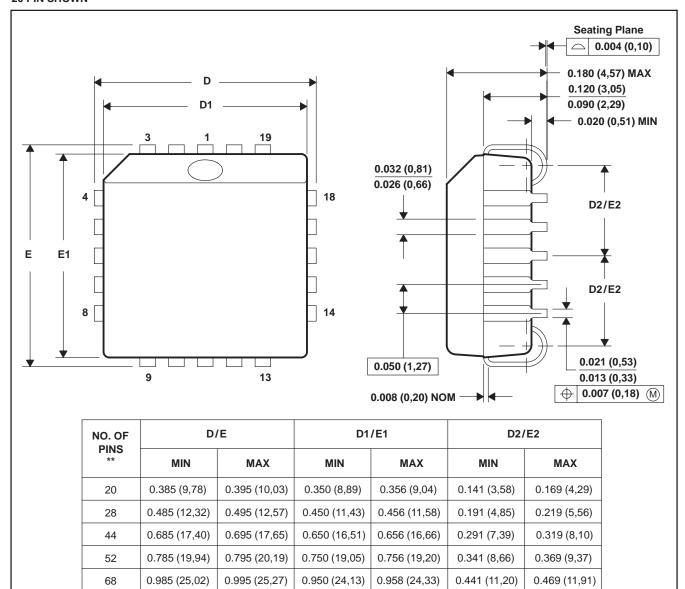

#### FN (S-PQCC-J\*\*)

#### 20 PIN SHOWN

#### PLASTIC J-LEADED CHIP CARRIER

NOTES: A. All linear dimensions are in inches (millimeters).

B. This drawing is subject to change without notice.

1.185 (30,10)

1.195 (30,35)

C. Falls within JEDEC MS-018

84

1.150 (29,21)

1.158 (29,41)

0.541 (13,74)

0.569 (14,45)

4040005/B 03/95

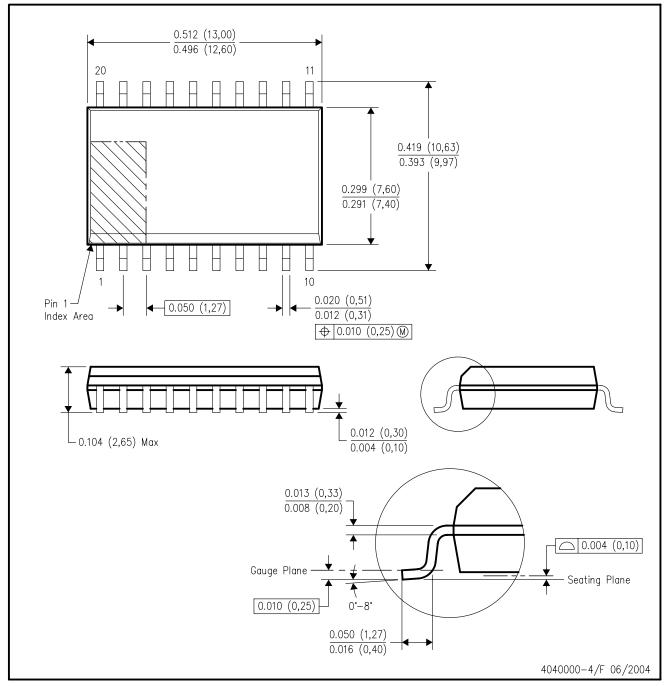

# DW (R-PDSO-G20)

# PLASTIC SMALL-OUTLINE PACKAGE

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- D. Falls within JEDEC MS-013 variation AC.

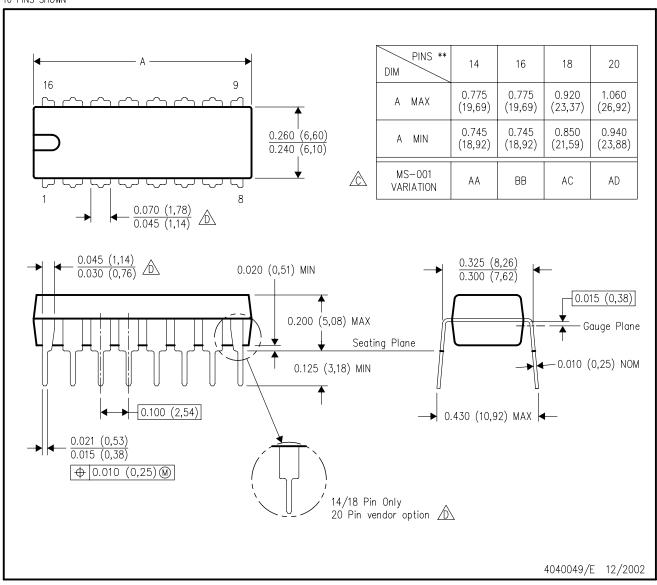

# N (R-PDIP-T\*\*)

#### PLASTIC DUAL-IN-LINE PACKAGE

16 PINS SHOWN

NOTES:

- A. All linear dimensions are in inches (millimeters).

- B. This drawing is subject to change without notice.

- Falls within JEDEC MS-001, except 18 and 20 pin minimum body length (Dim A).

- The 20 pin end lead shoulder width is a vendor option, either half or full width.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Products Amplifiers** amplifier.ti.com Data Converters dataconverter.ti.com **DLP® Products** www.dlp.com DSP dsp.ti.com Clocks and Timers www.ti.com/clocks Interface interface.ti.com Logic logic.ti.com Power Mgmt power.ti.com Microcontrollers microcontroller.ti.com www.ti-rfid.com RF/IF and ZigBee® Solutions www.ti.com/lprf

Applications Audio www.ti.com/audio Automotive www.ti.com/automotive Broadband www.ti.com/broadband Digital Control www.ti.com/digitalcontrol Medical www.ti.com/medical Military www.ti.com/military Optical Networking www.ti.com/opticalnetwork Security www.ti.com/security Telephony www.ti.com/telephony Video & Imaging www.ti.com/video Wireless www.ti.com/wireless

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated