### **FEATURES**

Low power, pin-compatible octal DACs

AD5668: 16 bits

AD5628: 12 bits

AD5668/AD5628 in 16-lead LFCSP

On-chip 1.25 V/2.5 V, 5 ppm/°C reference

Power down to 400 nA @ 5 V, 200 nA @ 3 V

2.7 V to 5.5 V power supply

Guaranteed monotonic by design

Power-on reset to zero scale or midscale

3 power-down functions

Hardware LDAC and LDAC override function

CLR function to programmable code

Rail-to-rail operation

#### **APPLICATIONS**

Optical transceivers

Power Amp control

Data acquisition systems

Digital gain and offset adjustment

### **GENERAL DESCRIPTION**

The AD5628/AD5668 devices are low power, octal, 12-/16-bit, buffered voltage-output DACs. All devices operate from a single 2.7 V to 5.5 V supply and are guaranteed monotonic by design.

The AD5628/AD5668 have an on-chip reference with an internal gain of 2. The AD5628/AD5648/AD5668-1 have a 1.25 V 5 ppm/°C reference, giving a full-scale output range of 2.5 V; the AD5628/AD5668-2, -3 have a 2.5 V 5 ppm/°C reference, giving a full-scale output range of 5 V. The on-board reference is off at power-up, allowing the use of an external reference. The internal reference is enabled via a software write.

The part incorporates a power-on reset circuit that ensures that the DAC output powers up to 0 V (AD5628/AD5668-1, -2) or midscale (AD5668-3) and remains powered up at this level until a valid write takes place. The part contains a power-down feature that reduces the current consumption of the device to 400 nA at 5 V and provides software-selectable output loads while in power-down mode for any or all DAC channels.

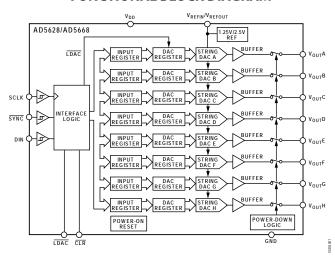

### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

The outputs of all DACs can be updated simultaneously using the LDAC function, with the added functionality of user-selectable DAC channels to simultaneously update. There is also an asynchronous CLR that updates all DACs to a user-programmable code—zero scale, midscale, or full scale.

The AD5628/AD5668 utilize a versatile 3-wire serial interface that operates at clock rates of up to 50 MHz and is compatible with standard SPI\*, QSPI™, MICROWIRE™, and DSP interface standards. The on-chip precision output amplifier enables rail-to-rail output swing.

### **PRODUCT HIGHLIGHTS**

- Octal, 12-/16-bit DAC.

- 2. On-chip 1.25 V/2.5 V, 5 ppm/°C reference.

- 3. Available in 16-lead LFCSP.

- 4. Power-on reset to 0 V or midscale.

- 5. Power-down capability. When powered down, the DAC typically consumes 200 nA at 3 V and 400 nA at 5 V.

## www.BDTIC.com/ADI/

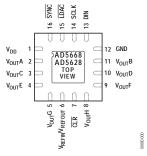

## PIN CONFIGURATIONS AND FUNCTION DESCRIPTIONS

Figure 2. 16-Lead LFCSP (CP-16-17)

**Table 1. Pin Function Descriptions**

| 16-Lead |                        |                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LFCSP   | Mnemonic               | Description                                                                                                                                                                                                                                                                                                                                                                                                             |

| 15      | LDAC                   | Pulsing this pin low allows any or all DAC registers to be updated if the input registers have new data. This allows all DAC outputs to simultaneously update. Alternatively, this pin can be tied permanently low.                                                                                                                                                                                                     |

| 16      | SYNC                   | Active Low Control Input. This is the frame synchronization signal for the input data. When SYNC goes low, it powers on the SCLK and DIN buffers and enables the input shift register. Data is transferred in on the falling edges of the next 32 clocks. If SYNC is taken high before the 32 <sup>nd</sup> falling edge, the rising edge of SYNC acts as an interrupt and the write sequence is ignored by the device. |

| 1       | V <sub>DD</sub>        | Power Supply Input. These parts can be operated from 2.7 V to 5.5 V, and the supply should be decoupled with a 10 $\mu$ F capacitor in parallel with a 0.1 $\mu$ F capacitor to GND.                                                                                                                                                                                                                                    |

| 2       | V <sub>OUT</sub> A     | Analog Output Voltage from DAC A. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                      |

| 11      | V <sub>OUT</sub> B     | Analog Output Voltage from DAC B. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                      |

| 3       | V <sub>OUT</sub> C     | Analog Output Voltage from DAC C. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                      |

| 10      | V <sub>OUT</sub> D     | Analog Output Voltage from DAC D. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                      |

| 6       | $V_{REFIN}/V_{REFOUT}$ | The AD5628/AD5648/AD5668 have a common pin for reference input and reference output. When using the internal reference, this is the reference output pin. When using an external reference, this is the reference input pin. The default for this pin is as a reference input.                                                                                                                                          |

| 7       | CLR                    | Asynchronous Clear Input. The <u>CLR</u> input is falling edge sensitive. When <u>CLR</u> is low, all <u>LDAC</u> pulses are ignored. When <u>CLR</u> is activated, the input register and the DAC register are updated with the data contained in the <u>CLR</u> code register—zero, midscale, or full scale. Default setting clears the output to 0 V.                                                                |

| 4       | V <sub>OUT</sub> E     | Analog Output Voltage from DAC E. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                      |

| 9       | V <sub>OUT</sub> F     | Analog Output Voltage from DAC F. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                      |

| 5       | V <sub>OUT</sub> G     | Analog Output Voltage from DAC G. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                      |

| 8       | V <sub>out</sub> H     | Analog Output Voltage from DAC H. The output amplifier has rail-to-rail operation.                                                                                                                                                                                                                                                                                                                                      |

| 12      | GND                    | Ground Reference Point for All Circuitry on the Part.                                                                                                                                                                                                                                                                                                                                                                   |

| 13      | DIN                    | Serial Data Input. This device has a 32-bit shift register. Data is clocked into the register on the falling edge of the serial clock input.                                                                                                                                                                                                                                                                            |

| 14      | SCLK                   | Serial Clock Input. Data is clocked into the input shift register on the falling edge of the serial clock input. Data can be transferred at rates of up to 50 MHz.                                                                                                                                                                                                                                                      |

# www.BDTIC.com/ADI/

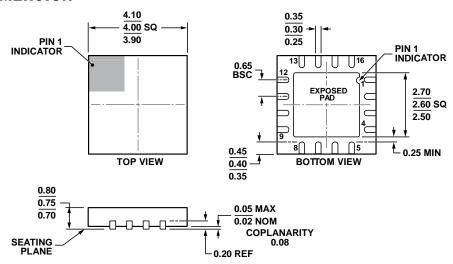

### **OUTLINE DIMENSION**

COMPLIANT TO JEDEC STANDARDS MO-220-WGGC.

Figure 2. 16-Lead Frame Chip Scale Package [LFCSP] (CP-16-17) Dimensions shown in millimeters

### **ORDERING GUIDE**

|                   |                   |                        | Package  | Power-On      |             | Internal  |

|-------------------|-------------------|------------------------|----------|---------------|-------------|-----------|

| Model             | Temperature Range | Package Description    | Option   | Reset to Code | Accuracy    | Reference |

| AD5628ACPZ-1      | -40°C to +105°C   | 16-Lead LFCSP          | CP-16-17 | Zero          | ±2 LSB INL  | 1.25V     |

| AD5628ACPZ-2      | -40°C to +105°C   | 16-Lead LFCSP          | CP-16-17 | Zero          | ±2 LSB INL  | 2.5V      |

| AD5628BCPZ-2      | -40°C to +105°C   | 16-Lead LFCSP          | CP-16-17 | Zero          | ±1 LSB INL  | 2.5V      |

| AD5668ACPZ-2      | −40°C to +105°C   | 16-Lead LFCSP          | CP-16-17 | Zero          | ±32 LSB INL | 2.5V      |

| AD5668ACPZ-3      | -40°C to +105°C   | 16-Lead LFCSP          | CP-16-17 | Midscale      | ±32 LSB INL | 2.5V      |

| AD5668BCPZ-1      | -40°C to +105°C   | 16-Lead LFCSP          | CP-16-17 | Zero          | ±16 LSB INL | 1.25V     |

| AD5668BCPZ-2      | -40°C to +105°C   | 16-Lead LFCSP          | CP-16-17 | Zero          | ±16 LSB INL | 2.5V      |

| EVAL-AD5668EBZ-CP |                   | LFCSP Evaluation board |          |               |             |           |

|                   |                   |                        |          |               |             |           |

9-60e