# DICE/DWF SPECIFICATION

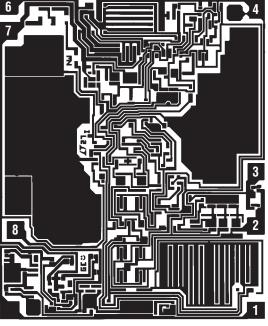

## LT1007 Low Noise, High Speed Precision Op Amp

$\begin{array}{l} 99 \text{mils} \times 83 \text{mils}, \\ 12 \text{mils thick} \end{array}$

#### PAD FUNCTION

- 1. V<sub>OS</sub> TRIM

- 2. –IN 3. +IN

- 4. V<sup>−</sup>

- 5. NO CONNECT

- 6. OUT

- 7. V<sup>+</sup>

- 8. V<sub>OS</sub> TRIM

Backside (substrate) is an alloyed gold layer. Connect to V<sup>-</sup>

### **DIE CROSS REFERENCE**

| LTC Finished<br>Part Number | Order<br>Part Number |

|-----------------------------|----------------------|

| LT1007C                     | LT1007CDICE          |

| LT1007C                     | LT1007CDWF*          |

Please refer to LTC standard product data sheet for other applicable product information. \*DWF = DICE in wafer form.

**Δ**, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

## **DICE/DWF ELECTRICAL TEST LIMITS** $V_{S} = \pm 15V$ , $V_{CM} = 0V$ , $T_{A} = 25^{\circ}C$ .

| SYMBOL           | PARAMETER                    | CONDITIONS                                                                                  | MIN            | MAX | UNITS        |

|------------------|------------------------------|---------------------------------------------------------------------------------------------|----------------|-----|--------------|

| V <sub>OS</sub>  | Input Offset Voltage         | (Note 1)                                                                                    |                | 60  | μV           |

| I <sub>OS</sub>  | Input Offset Current         |                                                                                             |                | 50  | nA           |

| I <sub>B</sub>   | Input Bias Current           |                                                                                             |                | ±55 | nA           |

|                  | Input Voltage Range          |                                                                                             | ±11.0          |     | V            |

| CMRR             | Common Mode Rejection Ratio  | V <sub>CM</sub> = ±11                                                                       | 110            |     | dB           |

| PSRR             | Power Supply Rejection Ratio | $V_{\rm S} = \pm 4 V \text{ to } \pm 18 V$                                                  | 106            |     | dB           |

| A <sub>VOL</sub> | Large-Signal Voltage Gain    | $\begin{array}{l} R_L \geq 2k, \ V_0 = \pm 12V \\ R_L \geq 1k, \ V_0 = \pm 10V \end{array}$ | 5<br>3.5       |     | V/μV<br>V/μV |

| V <sub>OUT</sub> | Maximum Output Voltage Swing | $\begin{array}{l} R_L \geq 2k \\ R_L \geq 600 \Omega \end{array}$                           | ±12.5<br>±10.5 |     | V<br>V       |

| SR               | Slew Rate                    | $R_L \ge 2k$                                                                                | 1.7            |     | V/µs         |

| I <sub>S</sub>   | Supply Current               |                                                                                             |                | 4.7 | mA           |

**Note 1:** Input offset voltage measurements are performed by automatic equipment, approximately 0.5 seconds after application of power.

# LT1007

2

Wafer level testing is performed per the indicated specifications for dice. Considerable differences in performance can often be observed for dice versus packaged units due to the influences of packaging and assembly on certain devices and/or parameters. Please consult factory for more information on dice performance and lot qualifications via lot sampling test procedures.

Dice data sheet subject to change. Please consult factory for current revision in production.

1007dice/dwffa