# 12ns, Single Supply Ground-Sensing Comparator

## **FEATURES**

- Ultra Fast (12ns Typ)

- Operates off Single 5V Supply or ±5V

- Input Common Mode Extends to Negative Supply

- No Minimum Input Slew Rate Requirement

- Complementary TTL Output

- Inputs Can Exceed the Positive Supply Up to 15V without Damaging the Comparator

- Low Offset Voltage

- Pin-Compatible with LT1016

- Output Latch Capability

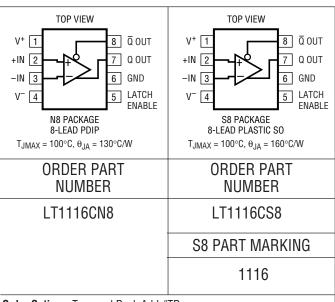

- Available in 8-Lead PDIP and SO Packages

### **APPLICATIONS**

- High Speed A/D Converters

- Zero Crossing Detectors

- Current Sense for Switching Regulators

- Extended Range V to F Converters

- Fast Pulse Height/Width Discriminators

- High Speed Triggers

- Line Receivers

- High Speed Sampling Circuits

(T, LTC, LT and LTM are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

## DESCRIPTION

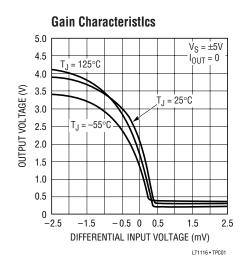

The LT $^{\odot}$ 1116 is an ultra fast (12ns) comparator designed for sensing signals near the negative supply. The input common mode range extends from 2.5V below the positive supply down to the negative supply rail. Like the LT1016, this comparator is specifically designed to interface directly to TTL logic with complementary outputs. The comparator may operate from either a single 5V supply or dual  $\pm$ 5V supplies. Tight offset voltage specifications and high gain allow the LT1116 to be used in precision applications.

The LT1116 is designed for improved speed and stability for a wide range of operating conditions. The output stage provides active drive in both directions for maximum speed into TTL logic or passive loads, yet it has minimal cross-conduction current. Unlike other fast comparators, the LT1116 remains stable even for slow transitions through the active region, which eliminates the need to specify a minimum input slew rate.

The LT1116 has an internal, TTL compatible latch for retaining data at the outputs. The latch holds data as long as the latch pin is held high. Device parameters such as gain, offset, and negative power supply current are not significantly affected by variations in negative supply voltage.

## TYPICAL APPLICATION

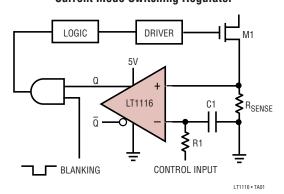

Fast Current Comparator for Current Mode Switching Regulator

## **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Supply Voltage (V+) to GND                | 7V                     |

|-------------------------------------------|------------------------|

| Negative Supply Voltage (V <sup>-</sup> ) |                        |

| Voltage                                   |                        |

| Differential Input Voltage                | ±15V                   |

| Inputs Voltage (Either Input)             | $(V^{-})$ -0.3V to 15V |

| Latch Pin Voltage                         | . Equal to Supplies    |

| Output Current (Continuous)               | ±20mA                  |

| Operating Temperature Range               | 0°C to 70°C            |

| Storage Temperature Range                 | 65°C to 150°C          |

| Lead Temperature (Soldering, 10 sec)      | 300°C                  |

## PACKAGE/ORDER INFORMATION

Order Options Tape and Reel: Add #TR

Lead Free: Add #PBF Lead Free Tape and Reel: Add #TRPBF Lead Free Part Marking: http://www.linear.com/leadfree/

Lead Free Part Marking: http://www.iinear.com/leadiree/

Consult LTC Marketing for parts specified with wider operating temperature ranges.

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ .  $V^+ = 5V$ ,  $V^- = 5V$ ,  $V_{OUT}(Q) = 1.4V$ , LATCH = 0V. Specifications for  $V_{OS}$ ,  $I_B$ , CMRR, and Voltage Gain are valid for single supply operation,  $V^+ = 5V$ ,  $V^- = 0V$ , unless noted.

| SYMBOL                           | PARAMETERS                   | CONDITIONS                                                                        |   | MIN        | TYP        | MAX                           | UNITS    |

|----------------------------------|------------------------------|-----------------------------------------------------------------------------------|---|------------|------------|-------------------------------|----------|

| V <sub>0S</sub>                  | Input Offset Voltage         | $R_S \le 100\Omega$ (Note 2)                                                      | • |            | 1.0        | ±3.0<br>3.5                   | mV<br>mV |

| $\frac{\Delta V_{0S}}{\Delta T}$ | Input Offset Voltage Drift   |                                                                                   | • |            | 5          |                               | μV/°C    |

| I <sub>OS</sub>                  | Input Offset Current         | (Note 2)                                                                          | • |            | 0.5        | 2                             | μΑ       |

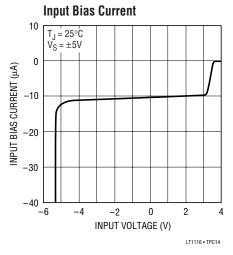

| I <sub>B</sub>                   | Input Bias Current, Sourcing | (Note 3)                                                                          | • |            | 10         | 20                            | μΑ       |

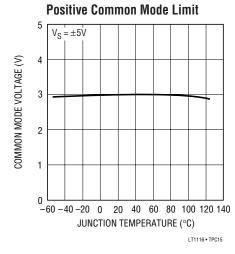

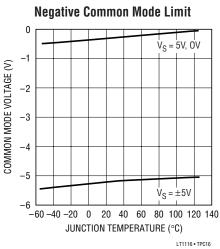

|                                  | Input Voltage Range          | Arbitrary Supply Range<br>Single 5V Supply                                        | • | V-<br>0    |            | (V <sup>+</sup> ) -2.5<br>2.5 | V        |

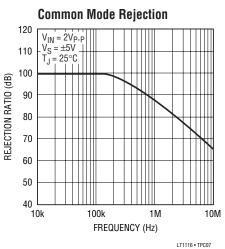

| CMRR                             | Common Mode Rejection Ratio  | $-5V \le V_{CM} \le 2.5V, V_S = \pm 5V$<br>$0V \le V_{CM} \le 2.5V$               | • | 75<br>65   | 90<br>90   |                               | dB<br>dB |

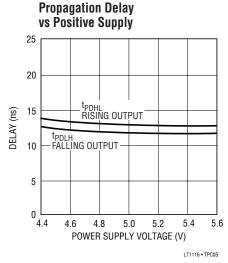

| PSRR                             | Power Supply Rejection Ratio | Positive Supply, $4.6V \le V^+ \le 5.4V$<br>Negative Supply, $-7 \le V^- \le -2V$ | • | 60<br>80   | 75<br>100  |                               | dB<br>dB |

| A <sub>V</sub>                   | Small Signal Voltage Gain    | 1V ≤ V <sub>OUT</sub> ≤ 2V                                                        |   | 1400       | 3000       |                               | V/V      |

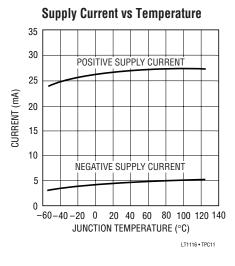

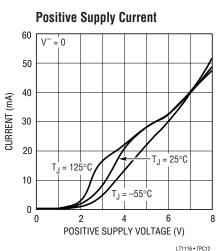

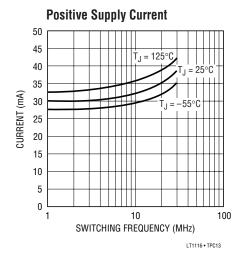

| [+                               | Positive Supply Current      |                                                                                   | • |            | 27         | 38                            | mA       |

| -                                | Negative Supply Current      |                                                                                   | • |            | 5          | 7                             | mA       |

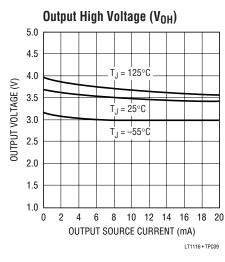

| V <sub>OH</sub>                  | Output High Voltage          | I <sub>SOURCE</sub> = 1mA<br>I <sub>SOURCE</sub> = 10mA                           | • | 2.7<br>2.4 | 3.4<br>3.0 |                               | V        |

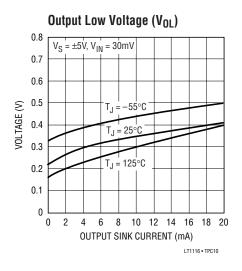

| $V_{OL}$                         | Output Low Voltage           | I <sub>SINK</sub> = 4mA<br>I <sub>SINK</sub> = 10mA                               | • |            | 0.3<br>0.4 | 0.5                           | V        |

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ . $V^+ = 5V$ , $V^+ = -5V$ , $V_{OUT} = (Q) = I$ . 4V, LATCH = 0V, unless noted.

| SYMBOL              | PARAMETERS                     | CONDITIONS                                                                  |   | MIN | TYP | MAX  | UNITS |

|---------------------|--------------------------------|-----------------------------------------------------------------------------|---|-----|-----|------|-------|

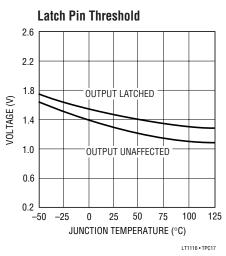

| $\overline{V_{IH}}$ | + Positive Latch Threshold     |                                                                             | • | 2.0 |     |      | V     |

| $V_{IL}$            | – Latch Threshold              |                                                                             | • |     |     | 0.8  | V     |

| I <sub>IL</sub>     | Latch Input Current            | V <sub>LATCH</sub> = 0V                                                     | • |     | -20 | -500 | μΑ    |

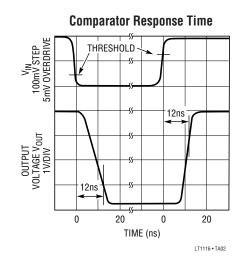

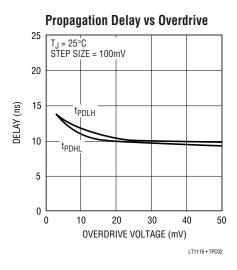

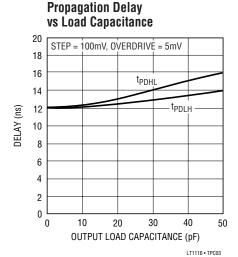

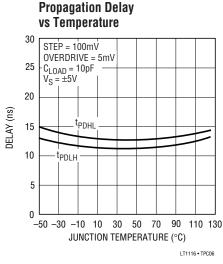

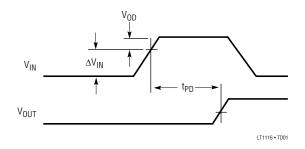

| t <sub>PD</sub>     | Propagation Delay              | $\Delta V_{IN} = 100 \text{mV}, \text{ OD} = 5 \text{mV} \text{ (Note 4)}$  |   |     | 12  | 16   | ns    |

|                     |                                |                                                                             | • |     |     | 18   | ns    |

| t <sub>PD</sub>     | Propagation Delay              | $\Delta V_{IN} = 100 \text{mV}, \text{ OD} = 20 \text{mV} \text{ (Note 4)}$ |   |     | 10  | 14   | ns    |

|                     |                                |                                                                             | • |     |     | 16   | ns    |

| $\Delta t_{PD}$     | Differential Propagation Delay | $\Delta V_{IN} = 100$ mV, OD = 5mV (Note 4)                                 |   |     |     | 3    | ns    |

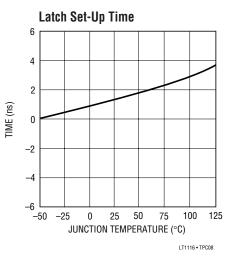

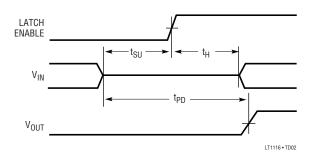

| t <sub>SU</sub>     | Latch Set-Up Time              | (Note 5)                                                                    |   |     | 2   |      | ns    |

| t <sub>H</sub>      | Latch Hold Time                | (Note 5)                                                                    |   |     | 2   |      | ns    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** Input offset voltage is defined as the average of two offset voltages measured by forcing first the Q output to 1.4V then forcing the  $\overline{Q}$  output to 1.4V.

**Note 3:** Input bias current is defined as the average of the two input currents.

**Note 4:**  $t_{PD}$  and  $\Delta t_{PD}$  cannot be measured in automatic handling equipment with low values of overdrive. The LT1116 is sample tested with a 1V step and 500mV overdrive. Correlation tests have shown that  $t_{PD}$  and  $\Delta t_{PD}$  can be guaranteed with this test if additional DC tests are performed to verify internal bias conditions are correct. For low overdrive conditions  $V_{OS}$  is added to the measured overdrive.

**Note 5:** Input latch set-up time,  $t_{SU}$ , is the interval in which the input signal must be stable prior to asserting the latch signal. The hold time,  $t_{H}$ , is the interval after the latch is asserted in which the input signal must be stable.

## TYPICAL PERFORMANCE CHARACTERISTICS

## TYPICAL PERFORMANCE CHARACTERISTICS

LINEAR

# TYPICAL PERFORMANCE CHARACTERISTICS

## TIMING DIAGRAMS

## APPLICATIONS INFORMATION

#### **Common Mode Considerations**

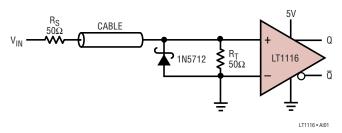

The LT1116 is specified for a common mode range of OV to 2.5V with a single 5V supply, and -5V to 2.5V with  $\pm 5V$ supplies. The common mode range is defined as the DC input for which the output responds correctly to small changes in the input differential. Input signals can exceed the positive common mode limit up to the 15V absolute maximum rating without damaging the comparator. There will, however, be an increase in propagation delay of up to 10ns when the input signal switches back into the common mode range. When input signals fall below the negative common mode limit, the internal PN diode formed with the substrate can turn on (resulting in significant charge flow throughout the die). A Schottky clamp diode, between the input and the negative rail, speeds up recovery from negative overdrive by preventing the substrate diode from turning on. The zero crossing detector in Figure 1 demonstrates the use of a fast clamp diode. Recovery, from 500mV overdrive below V<sup>-</sup>, for this circuit is approximately 18ns.

#### **Input Characteristics**

Each input to the LT1116 is buffered with a fast PNP follower—input bias current therefore does not vary significantly throughout the common mode range. When either input exceeds the positive common mode limit, the bias current drops to zero. Inputs that fall more than one diode and drop below V<sup>-</sup> will forward bias the substrate or clamp diode, causing large input current to flow.

#### **Fast Zero Crossing Detector**

Figure 1. The Zero Crossing Detector Terminates the Transmission Line At Its  $50\Omega$  Characteristic Impedance. Negative Inputs Should Not Fall Below –2V to keep the Signal Current Within the Clamp Diode's Maximum Forward Rating. Positive Inputs Should not Exceed the Devices Absolute Maximum Ratings nor the Power Rating on the Terminating Resistor

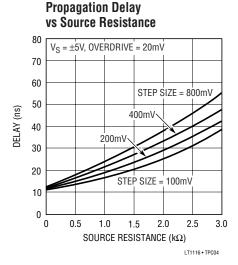

Single ended input resistance is about  $5M\Omega$ , and remains roughly constant over the input common mode range. The common mode resistance is about  $2.5M\Omega$  with zero differential input voltage, and does not change significantly with the absolute value of differential input.

Effective input capacitance, typically 5pF, is determined by measuring the resulting change in propagation delay for a  $1k\Omega$  change in source resistance.

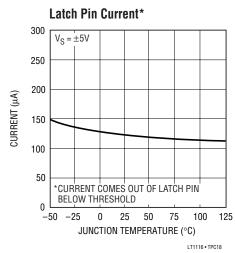

#### **Latch Pin Dynamics**

The internal latch uses local regenerative feedback to shorten set-up and hold times. Driving the latch pin high retains the output state. The latch pin floats to a high state when disconnected, so it must be driven low for flow-through operation. The set-up time required to guarantee detecting a given transition of the inputs is 2ns. The inputs must also remain stable for a 2ns hold time after latch is asserted. New data will appear at the output approximately 10ns to 12ns after the latch goes low. The latch pin has no built-in hysteresis, and is designed to be driven from TTL or CMOS logic gates.

#### **Additional Information**

Linear Technology's Application Note 13 provides an extensive discussion of design techniques for high speed comparators.

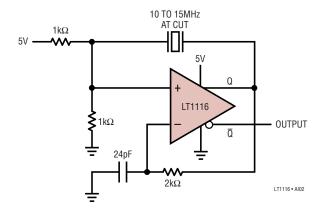

#### Single Supply Crystal Oscillator 10MHZ to 15MHz

Figure 2. This Single Supply Crystal Oscillator Utilizes Crystals From 10MHz To 15MHz Without Component Changes

## APPLICATIONS INFORMATION

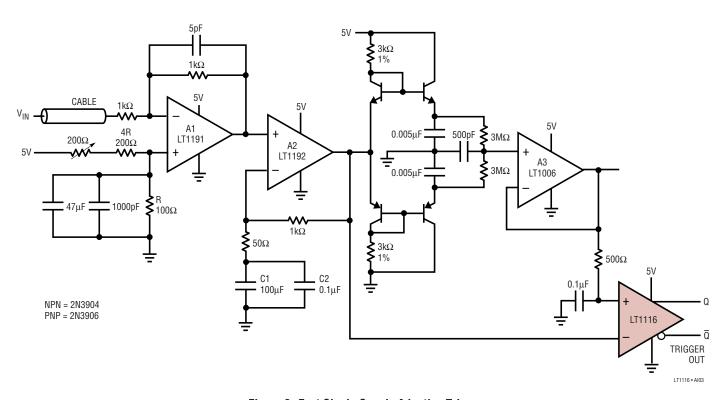

#### **High Speed Adaptive Trigger Circuit**

Line receivers often require an adaptive trigger to compensate for variations in signal amplitude and DC offsets. The circuit in Figure 3 triggers on 2mV to 200mV signals from 100Hz to 10MHz from a single 5V rail. The trigger level is the average of the input signal's positive and negative peaks stored on  $0.005\mu F$  capacitors. Pairs of NPN and PNP transistors are used instead of diodes to temperature compensate the peak detector.

To achieve single supply operation, the input signal must be shifted into the pre-amplifier's common mode range. The input amplifier A1 adds a 1V level shift, while A2 provides a gain of 20 for high frequency signals. Capacitors C1 and C2 insure that low frequency signals see unity gain. Bandwidth limiting in A1 and A2 does not affect triggering because the adaptive trigger threshold varies ratiometrically to maintain circuit output.

Figure 3. Fast Single Supply Adaptive Trigger

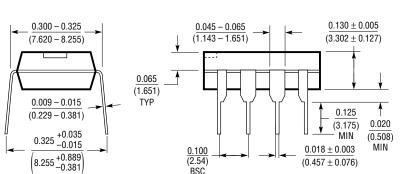

## PACKAGE DESCRIPTION

#### N8 Package 8-Lead PDIP (Narrow .300 Inch) (Reference LTC DWG # 05-08-1510)

\*THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.010 INCH (0.254mm)

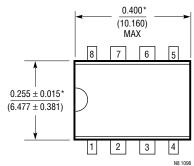

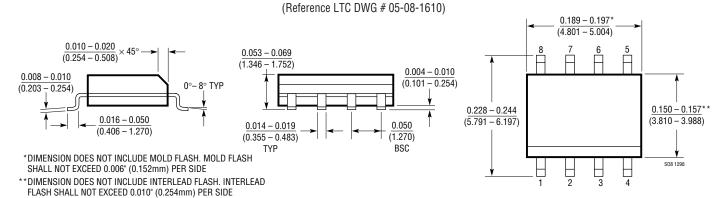

#### S8 Package 8-Lead Plastic Small Outline (Narrow .150 Inch)

# **RELATED PARTS**

| PART NUMBER   | DESCRIPTION                    | COMMENTS                                                |

|---------------|--------------------------------|---------------------------------------------------------|

| LT1016        | 10ns Precision Comparator      | Complementary Outputs with Latch, LT1116 Pinout         |

| LT1394        | 7ns Single Supply Comparator   | 6mA, 100MHz Toggle Rate, LT1116 Pinout                  |

| LT1671        | 60ns Single Supply Comparator  | 450μA, 0.8mV Offset, LT1116 Pinout                      |

| LT1713/LT1714 | 7ns Single/Dual Comparator     | Rail-to-Rail Input and Output, 2.7V to + 5.5V Operation |

| LT1715        | 4ns Dual Comparator            | Independent Input/Output Supplies, 150MHz Toggle Rate   |

| LT1719        | 4.5ns Single Supply Comparator | Independent Input/Output Supplies, 3V/5V                |

| LT1720/LT1721 | 4.5ns Dual/Quad Comparator     | 4mA per Comparator, Input 100mV Below V –, 3V/5V        |