# LTC 1405 12-Bit, 5Msps, Sampling ADC

# FEATURES

- 5Msps Sample Rate

- Low Power Dissipation: 115mW

- Single 5V Supply or ±5V Supplies

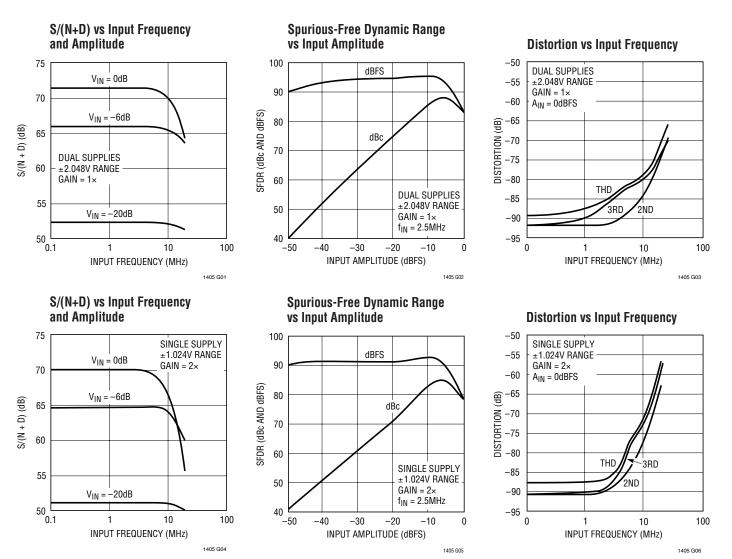

- 71.3dB S/(N + D) and 85dB SFDR at Nyquist

- 100MHz Full-Power Bandwidth Sampling

- Input PGA

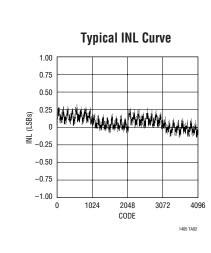

- Integral Nonlinearity Error <0.35LSB</p>

- Differential Nonlinearity <0.25LSB</li>

- ±2.048V, ±1.024V and ±0.512V Bipolar Input Range

- Out-of-Range Indicator

- True Differential Inputs with 75dB CMRR

- Pin-Compatible 10Msps Version (LTC1420)

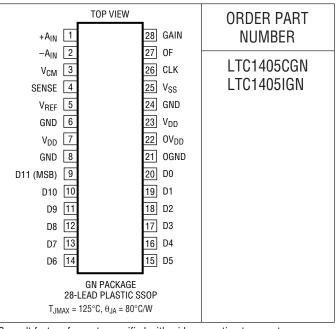

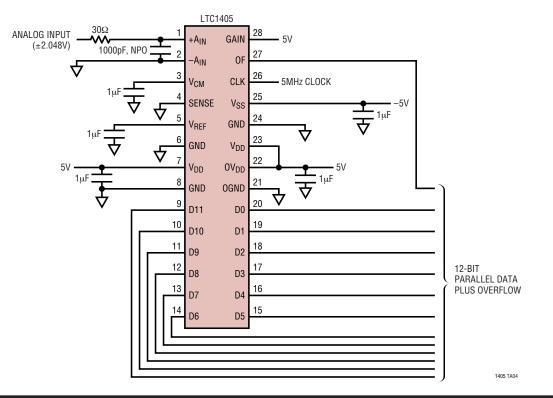

- 28-Pin Narrow SSOP Package

# **APPLICATIONS**

- Telecommunications

- Digital Signal Processing

- Multiplexed Data Acquisition Systems

- High Speed Data Acquisition

- Spectral Analysis

- Imaging Systems

$\mathcal{T}$ , LTC and LT are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

# DESCRIPTION

The LTC<sup>®</sup>1405 is a 5Msps, 12-bit sampling A/D converter that draws only 115mW from either single 5V or dual ±5V supplies. This easy-to-use device includes a high dynamic range sample-and-hold, a precision reference and a PGA input circuit.

The LTC1405 has a flexible input circuit that allows full-scale input ranges of  $\pm 2.048V$ ,  $\pm 1.024V$  and  $\pm 0.512V$ . The input common mode range is rail-to-rail and a common mode bias voltage is provided for single supply applications. The input PGA has a digitally selectable 1x or 2x gain.

Maximum DC specs include  $\pm 1LSB$  INL and  $\pm 1LSB$  DNL over temperature. Outstanding AC performance includes 71.3dB S/(N + D) and 85dB SFDR at the Nyquist input frequency of 2.5MHz.

The unique differential input sample-and-hold can acquire single-ended or differential input signals up to its 100MHz bandwidth. The 75dB common mode rejection allows users to eliminate ground loops and common mode noise by measuring signals differentially from the source. A separate output logic supply allows direct connection to 3V components.

# **ABSOLUTE MAXIMUM RATINGS**

| $0V_{DD} = V_{DD} (Notes 1, 2)$                                |

|----------------------------------------------------------------|

| Supply Voltage (V <sub>DD</sub> ) 6V                           |

| Negative Supply Voltage (V <sub>SS</sub> )6V                   |

| Total Supply Voltage (V <sub>DD</sub> to V <sub>SS</sub> ) 12V |

| Analog Input Voltage                                           |

| (Note 3) $(V_{SS} - 0.3V)$ to $(V_{DD} + 0.3V)$                |

| Digital Input Voltage                                          |

| (Note 4) $(V_{SS} - 0.3V)$ to $(V_{DD} + 0.3V)$                |

| Digital Output Voltage $(V_{SS} - 0.3V)$ to $(V_{DD} + 0.3V)$  |

| Power Dissipation                                              |

| Operating Temperature Range                                    |

| LTC1405C                                                       |

| LTC1405I –40°C to 85°C                                         |

| Storage Temperature Range –65°C to 150°C                       |

| Lead Temperature (Soldering, 10 sec)                           |

|                                                                |

# PACKAGE/ORDER INFORMATION

Consult factory for parts specified with wider operating temperature ranges.

# **CONVERTER CHARACTERISTICS**

The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. With Internal 4.096V Reference. Specifications are guaranteed for both dual supply and single supply operation. (Note 5)

| PARAMETER                     | CONDITIONS         |   | MIN | ТҮР   | MAX      | UNITS      |

|-------------------------------|--------------------|---|-----|-------|----------|------------|

| Resolution (No Missing Codes) |                    | • | 12  |       |          | Bits       |

| Integral Linearity Error      | (Note 7)           | • |     | ±0.35 | ±1       | LSB        |

| Differential Linearity Error  |                    | • |     | ±0.25 | ±1       | LSB        |

| Offset Error                  | (Note 8)           | • |     | ±5    | 12<br>16 | LSB<br>LSB |

| Full-Scale Error              |                    |   |     | ±10   | 30       | LSB        |

| Full-Scale Tempco             | $I_{OUT(REF)} = 0$ |   |     | ±15   |          | ppm/°C     |

# **ANALOG INPUT** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. Specifications are guaranteed for both dual supply and single supply operation. (Note 5)

| SYMBOL           | PARAMETER                                                             | CONDITIONS                                                                                                                                                                                                                       |   | MIN | ТҮР                                                | MAX | UNITS                 |

|------------------|-----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|----------------------------------------------------|-----|-----------------------|

| V <sub>IN</sub>  | Analog Input Range (Note 9)<br>+A <sub>IN</sub> – (–A <sub>IN</sub> ) | $V_{REF} = 4.096V (SENSE = 0V), GAIN = 5V$ $V_{REF} = 4.096V (SENSE = 0V), GAIN = 0V$ $V_{REF} = 2.048V (SENSE = V_{REF}), GAIN = 5V$ $V_{REF} = 2.048V (SENSE = V_{REF}), GAIN = 0V$ External $V_{REF}$ (SENSE = 5V), GAIN = 5V |   |     | ±2.048<br>±1.024<br>±0.512<br>±V <sub>REF</sub> /2 |     | V<br>V<br>V<br>V<br>V |

| IIN              | Analog Input Leakage Current                                          | External V <sub>REF</sub> (SENSE = 5V), GAIN = 0V                                                                                                                                                                                | • |     | $\pm V_{REF}/4$                                    | ±10 | ν<br>μΑ               |

| C <sub>IN</sub>  | Analog Input Capacitance                                              | Between Conversions<br>During Conversions                                                                                                                                                                                        |   |     | 12<br>6                                            |     | pF<br>pF              |

| t <sub>ACQ</sub> | Sample-and-Hold Acquisition Time                                      |                                                                                                                                                                                                                                  |   |     | 50                                                 |     | ns                    |

# **ANALOG INPUT** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. Specifications are guaranteed for both dual supply and single supply operation. (Note 5)

| SYMBOL              | YMBOL         PARAMETER         CONDITIONS |                                          | MIN | ТҮР | MAX  | UNITS |    |

|---------------------|--------------------------------------------|------------------------------------------|-----|-----|------|-------|----|

| t <sub>AP</sub>     | Sample-and-Hold Aperture Delay Time        |                                          |     |     | -250 |       | ps |

| t <sub>jitter</sub> | Sample-and-Hold Aperture Delay Time Jitter |                                          |     |     | 0.6  |       | ps |

| CMRR                | Analog Input Common Mode Rejection Ratio   | $-2.048V < (-A_{IN} = +A_{IN}) < 2.048V$ |     |     | 75   |       | dB |

# **DYNAMIC ACCURACY** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. V<sub>DD</sub> = 5V, V<sub>SS</sub> = -5V, f<sub>SAMPLE</sub> = 5MHz, V<sub>REF</sub> = 4.096V. + A<sub>IN</sub> = -0.1dBFS single ended input, -A<sub>IN</sub> = 0V. (Note 6)

| SYMBOL    | PARAMETER                             | CONDITIONS                                                                     |   | MIN          | ТҮР          | MAX            | UNITS                                    |

|-----------|---------------------------------------|--------------------------------------------------------------------------------|---|--------------|--------------|----------------|------------------------------------------|

| S/(N + D) | Signal-to-Noise Plus Distortion Ratio | 1MHz Input Signal<br>2.5MHz Input Signal                                       | • | 69.0<br>68.7 | 71.6<br>71.3 |                | dB<br>dB                                 |

| THD       | Total Harmonic Distortion             | 1MHz Input Signal, First 5 Harmonics<br>2.5MHz Input Signal, First 5 Harmonics | • |              | -87<br>-83   | -78.5<br>-77.0 | dB<br>dB                                 |

| SFDR      | Peak Harmonic or Spurious Noise       | 1MHz Input Signal<br>2.5MHz Input Signal                                       | • |              | -89<br>-85   | -79.5<br>-78.0 | dB<br>dB                                 |

| IMD       | Intermodulation Distortion            | f <sub>IN1</sub> = 29.37kHz, f <sub>IN2</sub> = 32.446kHz                      |   |              | -80          |                | dB                                       |

|           | Full-Power Bandwidth                  |                                                                                |   |              | 100          |                | MHz                                      |

|           | Input Referred Noise                  | ±2.048V Input Range<br>±1.024V Input Range, 2x Mode (SENSE = GAIN = 0V)        |   |              | 0.22<br>0.33 |                | LSB <sub>RMS</sub><br>LSB <sub>RMS</sub> |

# INTERNAL REFERENCE CHARACTERISTICS

$T_A = 25^{\circ}C$ . Specifications are guaranteed for both dual supply and single supply operation. (Note 5)

| PARAMETER                         | CONDITIONS                                                                          | MIN   | ТҮР                                                         | MAX   | UNITS        |

|-----------------------------------|-------------------------------------------------------------------------------------|-------|-------------------------------------------------------------|-------|--------------|

| V <sub>CM</sub> Output Voltage    | I <sub>OUT</sub> = 0                                                                | 2.475 | 2.500                                                       | 2.525 | V            |

| V <sub>CM</sub> Output Tempco     | I <sub>OUT</sub> = 0                                                                |       | ±15                                                         |       | ppm/°C       |

| V <sub>CM</sub> Line Regulation   | $4.75V \le V_{DD} \le 5.25V$<br>-5.25V $\le V_{SS} \le -4.75V$                      |       | 0.6<br>0.03                                                 |       | mV/V<br>mV/V |

| V <sub>CM</sub> Output Resistance | $0.1\text{mA} \le  I_{\text{OUT}}  \le 0.1\text{mA}$                                |       | 8                                                           |       | Ω            |

| V <sub>REF</sub> Output Voltage   | SENSE = GND, $I_{OUT} = 0$<br>SENSE = $V_{REF}$ , $I_{OUT} = 0$<br>SENSE = $V_{DD}$ |       | 4.096<br>2.048<br>Drive V <sub>REF</sub> v<br>xternal Refer |       | V<br>V<br>V  |

| V <sub>REF</sub> Output Tempco    |                                                                                     |       | ±15                                                         |       | ppm/°C       |

# **DIGITAL INPUTS AND OUTPUTS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. Specifications are guaranteed for both dual supply and single supply

temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. Specifications are guaranteed for both dual supply and single supply operation. (Note 5)

| SYMBOL          | PARAMETER                            | CONDITIONS                      |   | MIN | ТҮР | MAX | UNITS |

|-----------------|--------------------------------------|---------------------------------|---|-----|-----|-----|-------|

| V <sub>IH</sub> | High Level Input Voltage (Clock Pin) | $V_{DD} = 5.25V, V_{SS} = 0V$   | • | 2.4 |     |     | V     |

|                 |                                      | $V_{DD} = 5.25V, V_{SS} = -5V$  | • | 3.5 |     |     | V     |

| V <sub>IL</sub> | Low Level Input Voltage (Clock Pin)  | $V_{DD} = 4.75 V, V_{SS} = 0 V$ | • |     |     | 0.8 | V     |

|                 |                                      | $V_{DD} = 4.75V, V_{SS} = -5V$  | • |     |     | 1   | V     |

**DIGITAL INPUTS AND OUTPUTS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Specifications are guaranteed for both dual supply and single supply operation. (Note 5)

| SYMBOL            | PARAMETER                 | CONDITIONS                                                                                                                                                       |   | MIN        | ТҮР                          | MAX        | UNITS            |

|-------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------------|------------------------------|------------|------------------|

| I <sub>IN</sub>   | Digital Input Current     | $V_{IN} = 0V$ to $V_{DD}$                                                                                                                                        | • |            |                              | ±10        | μA               |

| C <sub>IN</sub>   | Digital Input Capacitance |                                                                                                                                                                  |   |            | 1.8                          |            | pF               |

| V <sub>OH</sub>   | High Level Output Voltage | $\begin{array}{c} 0V_{DD}=4.75V,\ I_{O}=-10\mu A\\ 0V_{DD}=4.75V,\ I_{O}=-200\mu A\\ 0V_{DD}=2.7V,\ I_{O}=-10\mu A\\ 0V_{DD}=2.7V,\ I_{O}=-200\mu A \end{array}$ | • | 4.0<br>2.3 | 4.74<br>4.71<br>2.6          |            | V<br>V<br>V<br>V |

| V <sub>OL</sub>   | Low Level Output Voltage  | $\begin{array}{l} 0V_{DD}=4.75V,\ I_{0}=160\mu A\\ 0V_{DD}=4.75V,\ I_{0}=1.6mA\\ 0V_{DD}=2.7V,\ I_{0}=160\mu A\\ 0V_{DD}=2.7V,\ I_{0}=1.6mA \end{array}$         | • |            | 0.05<br>0.10<br>0.05<br>0.10 | 0.4<br>0.4 | V<br>V<br>V<br>V |

| ISOURCE           | Output Source Current     | V <sub>OUT</sub> = 0V                                                                                                                                            |   |            | 50                           |            | mA               |

| I <sub>SINK</sub> | Output Sink Current       | V <sub>OUT</sub> = V <sub>DD</sub>                                                                                                                               |   |            | 35                           |            | mA               |

**POWER REQUIREMENTS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Specifications are guaranteed for both dual supply and single supply operation. (Note 5)

| SYMBOL          | PARAMETER               | CONDITIONS                             |   | MIN   | ТҮР | MAX   | UNITS  |

|-----------------|-------------------------|----------------------------------------|---|-------|-----|-------|--------|

| V <sub>DD</sub> | Positive Supply Voltage | (Note 10)                              |   | 4.75  |     | 5.25  | V      |

| V <sub>SS</sub> | Negative Supply Voltage | Dual Supply Mode<br>Single Supply Mode |   | -5.25 | 0   | -4.75 | V<br>V |

| I <sub>DD</sub> | Positive Supply Current |                                        | • |       | 23  | 28    | mA     |

| I <sub>SS</sub> | Negative Supply Current |                                        | • |       | 0.8 | 1.2   | mA     |

| P <sub>D</sub>  | Power Dissipation       |                                        | • |       | 115 | 145   | mW     |

TIMING CHARACTERISTICS The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ . Specifications are guaranteed for both dual supply and single supply operation. (Note 5)

| SYMBOL            | PARAMETER                         | CONDITIONS |   | MIN  | ТҮР  | MAX | UNITS |

|-------------------|-----------------------------------|------------|---|------|------|-----|-------|

| <b>f</b> SAMPLE   | Sampling Frequency                |            | • | 0.02 |      | 5   | MHz   |

| t <sub>CONV</sub> | Conversion Time                   |            | • |      | 150  | 180 | ns    |

| t <sub>ACQ</sub>  | Acquisition Time                  |            | • | 20   | 50   |     | ns    |

| t <sub>H</sub>    | CLK High Time                     | (Note 9)   | • | 20   | 100  |     | ns    |

| tL                | CLK Low Time                      | (Note 9)   | • | 20   | 100  |     | ns    |

| t <sub>AD</sub>   | Aperture Delay of Sample-and-Hold |            |   |      | -250 |     | ps    |

Note 1: Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

Note 2: All voltage values are with respect to ground with GND and OGND wired together (unless otherwise noted).

Note 3: When these pin voltages are taken below  $V_{SS}$  or above  $V_{DD}$ , they will be clamped by internal diodes. This product can handle input currents greater than 100mA below V<sub>SS</sub> or above V<sub>DD</sub> without latchup.

Note 4: When these pin voltages are taken below  $V_{SS}$  they will be clamped by internal diodes. This product can handle input currents greater than 100mA below  $V_{\text{SS}}$  without latchup. GAIN is not clamped to  $V_{\text{DD}}.$  When CLK is taken above  $V_{DD}$ , it will be clamped by an internal diode. The CLK pin can handle input currents of greater than 100mA above  $V_{\text{DD}}$  without latchup.

Note 5:  $V_{DD}$  = 5V,  $V_{SS}$  = -5V or 0V,  $f_{SAMPLE}$  = 5MHz,  $t_r$  =  $t_f$  = 5ns unless otherwise specified.

# **ELECTRICAL CHARACTERISTICS**

**Note 6:** Dynamic specifications are guaranteed for dual supply operation with a single-ended +  $A_{IN}$  input and  $-A_{IN}$  grounded. For single supply dynamic specifications, refer to the Typical Performance Characteristics. **Note 7:** Integral nonlinearity is defined as the deviation of a code from a straight line passing through the actual endpoints of the transfer curve. The deviation is measured from the center of the quantization band.

**Note 8:** Bipolar offset is the offset voltage measured from -0.5LSB when the output code flickers between 0000 0000 0000 and 1111 1111 1111.

**Note 9:** Guaranteed by design, not subject to test. **Note 10:** Recommended operating conditions.

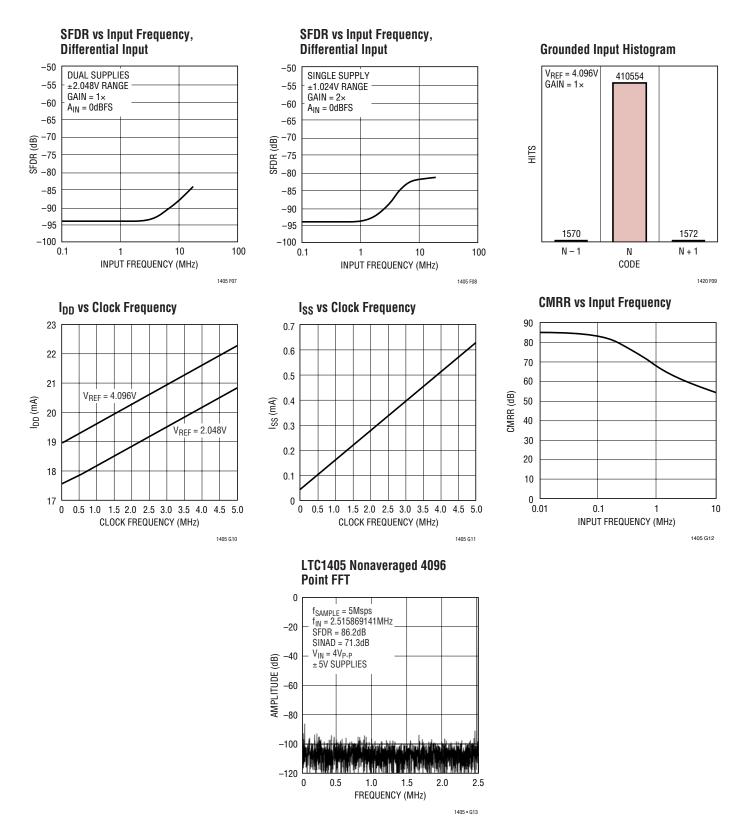

### **TYPICAL PERFORMANCE CHARACTERISTICS**

# **TYPICAL PERFORMANCE CHARACTERISTICS**

www.BDTIC.com/Linear

### PIN FUNCTIONS

+AIN (Pin 1): Positive Analog Input.

-AIN (Pin 2): Negative Analog Input.

$V_{CM}$  (Pin 3): 2.5V Reference Output.Optional input common mode for single supply operation. Bypass to GND with a 1µF to 10µF ceramic.

**SENSE (Pin 4):** Reference Programming Pin. Ground selects  $V_{REF} = 4.096V$ . Short to  $V_{REF}$  for 2.048V. Connect SENSE to  $V_{DD}$  to drive  $V_{REF}$  with an external reference.

$V_{REF}$  (Pin 5): DAC Reference. Bypass to GND with a 1 $\mu$ F to 10 $\mu$ F ceramic.

**GND (Pin 6):** DAC Reference Ground.

$V_{DD}$  (Pin 7): Analog 5V Supply. Bypass to GND with a 1µF to 10µF ceramic.

GND (Pin 8): Analog Power Ground.

**D11 to D0 (Pins 9 to 20):** Data Outputs. The output format is two's complement.

OGND (Pin 21): Output Logic Ground. Tie to GND.

$OV_{DD}$  (Pin 22): Positive Supply for the Output Logic. Connect to Pin 23 for 5V logic. If not shorted to Pin 23, bypass to GND with a 1µF ceramic.

$V_{DD}$  (Pin 23): Analog 5V Supply. Bypass to GND with a  $1\,\mu F$  ceramic.

GND (Pin 24): Analog Power Ground.

$V_{SS}$  (Pin 25): Negative Supply. Can be – 5V or 0V. If  $V_{SS}$  is not shorted to GND, bypass to GND with a 1µF ceramic.

**CLK (Pin 26):** Conversion Start Signal. This active high signal starts a conversion on its rising edge.

**OF (Pin 27):** Overflow Output. This signal is high when the digital output is 01111111111 or 10000000000.

**GAIN (Pin 28):** Gain Select for Input PGA. 5V selects an input gain of 1, 0V selects a gain of 2.

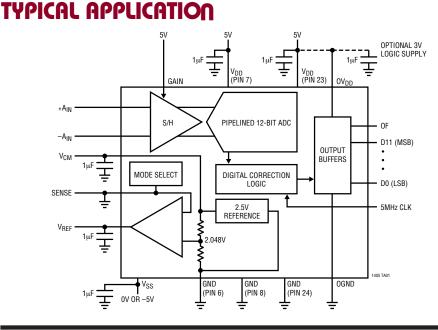

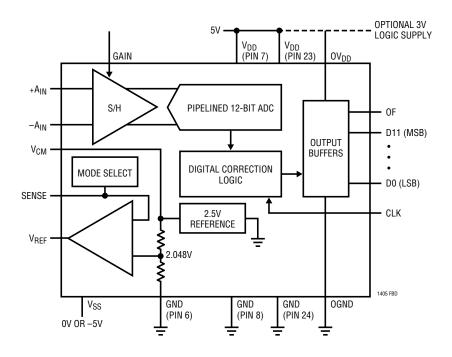

# FUNCTIONAL BLOCK DIAGRAM

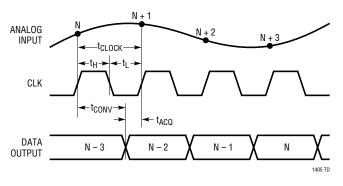

# TIMING DIAGRAM

### **Conversion Details**

The LTC1405 is a high performance 12-bit A/D converter that operates up to 5Msps. It is a complete solution with an on-chip sample-and-hold, a 12-bit pipelined CMOS ADC, a low drift programmable reference and an input programmable gain amplifier. The digital output is parallel, with a 12-bit two's complement format and an out-of-range (overflow) bit.

The rising edge of the CLK begins the conversion. The differential analog inputs are simultaneously sampled and passed on to the pipelined A/D. After two more conversion starts (plus a 150ns conversion time) the digital outputs are updated with the conversion result and will be ready for capture on the third rising clock edge. Thus even though a new conversion is begun every time CLK goes high, each result takes three clock cycles to reach the output.

The analog signals that are passed from stage to stage in the pipelined A/D are stored on capacitors. The signals on these capacitors will be lost if the delay between conversions is too long. For accurate conversion results, the part should be clocked faster than 20kHz.

In some pipelined A/D converters if there is no clock present, dynamic logic on the chip will droop and the power consumption sharply increases. The LTC1405 doesn't have this problem. If the part is not clocked for 1ms, an internal timer will refresh the dynamic logic. Thus the clock can be turned off for long periods of time to save power.

### **Power Supplies**

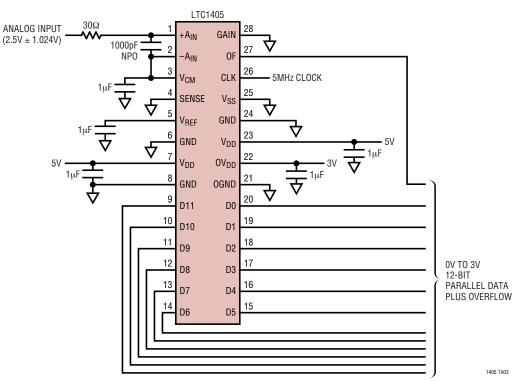

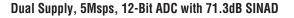

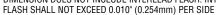

The LTC1405 will operate from either a single 5V or dual  $\pm$ 5V supply, making it easy to interface the analog input to single or dual supply systems. The digital output drivers have their own power supply pin (OV<sub>DD</sub>) which can be set from 3V to 5V, allowing direct connection to either 3V or 5V digital systems. For single supply operation, V<sub>SS</sub> should be connected to analog ground. For dual supply operation, V<sub>SS</sub> should be connected to – 5V. Both V<sub>DD</sub> pins should be connected to a clean 5V analog supply. (Don't connect V<sub>DD</sub> to a noisy system digital supply.)

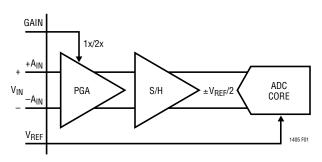

### **Analog Input Ranges**

The LTC1405 has a flexible analog input with a wide selection of input ranges. The input range is always differential and is set by the voltages at the V<sub>REF</sub> and the GAIN pins (Figure 1). The input range of the A/D core is fixed at  $\pm$ V<sub>REF</sub>/2. The reference voltage, V<sub>REF</sub>, is either set by the on-chip voltage reference or directly driven by an external voltage. The GAIN pin is a digital input that controls the gain of a preamplifier in the sample-and-hold circuit. The gain of this PGA can be set to 1x or 2x. Table 1 gives the input range in terms of V<sub>REF</sub> and GAIN.

#### Table 1

| GAIN PIN     | PGA GAIN | $\frac{\text{INPUT RANGE}}{(\text{V}_{\text{IN}} = \text{A}_{\text{IN}}^{+} - \text{A}_{\text{IN}}^{-})}$ |

|--------------|----------|-----------------------------------------------------------------------------------------------------------|

| 5V (Logic H) | 1x       | $-V_{REF}/2 < V_{IN} < V_{REF}/2$                                                                         |

| OV (Logic L) | 2x       | $-V_{\text{REF}}/4 < V_{\text{IN}} < V_{\text{REF}}/4$                                                    |

Figure 1. Analog Input Circuit

#### **Internal Reference**

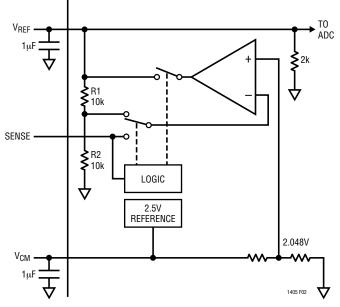

Figure 2 shows a simplified schematic of the LTC1405 reference circuitry. An on-chip temperature compensated bandgap reference ( $V_{CM}$ ) is factory trimmed to 2.500V. The voltage at the  $V_{REF}$  pin sets the input span of the ADC to  $\pm V_{REF}/2$ . An internal voltage divider converts V<sub>CM</sub> to 2.048V, which is connected to a reference amplifier. The reference programming pin, SENSE, controls how the reference amplifier drives the V<sub>RFF</sub> pin. If SENSE is tied to ground, the reference amplifier feedback is connected to the R1/R2 voltage divider, thus making  $V_{BFF} = 4.096V$ . If SENSE is tied to V<sub>RFF</sub>, the reference amplifier feedback is connected to SENSE thus making  $V_{REF} = 2.048V$ . If SENSE is tied to  $V_{DD}$ , the reference amplifier is disconnected from  $V_{\text{REF}}$  and  $V_{\text{REF}}$  can be driven by an external voltage. With two additional resistors, V<sub>RFF</sub> can be set to any voltage between 2.048V and 4.5V.

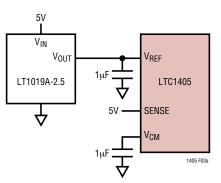

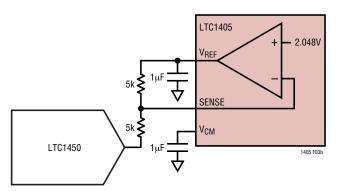

An external reference or a DAC can be used to drive  $V_{REF}$  over a 0V to 5V range (Figures 3a and 3b). The input impedance of the  $V_{REF}$  pin is  $2k\Omega$ , so a buffer may be required for high accuracy. Driving  $V_{REF}$  with a DAC is useful in applications where the peak input signal amplitude may vary. The input span of the ADC can then be adjusted to match the peak input signal, maximizing the signal-to-noise ratio.

Both the  $V_{CM}$  and  $V_{REF}$  pins must be bypassed with capacitors to ground. For best performance,  $1\mu F$  or larger ceramic capacitors are recommended. For the case of external circuitry driving  $V_{REF}$ , a smaller capacitor can be used at  $V_{REF}$  so the input range can be changed quickly. In this case, a  $0.05\mu F$  or larger ceramic capacitor is acceptable.

The V<sub>CM</sub> pin is a low output impedance 2.5V reference that can be used by external circuitry. For single 5V supply applications it is convenient to connect  $A_{IN}^{-}$  directly to the V<sub>CM</sub> pin.

### **Driving the Analog Inputs**

The differential inputs of the LTC1405 are easy to drive. The inputs may be driven differentially or single-ended (i. e., the  $A_{IN}^{-}$  input is held at a fixed value). The  $A_{IN}^{-}$  and  $A_{IN}^{+}$  inputs are simultaneously sampled and any common mode signal is reduced by the high common mode rejection of the sample-and-hold circuit. Any common mode input value is acceptable as long as the input pins stay between  $V_{DD}$  and  $V_{SS}$ . During conversion the analog inputs are high impedance. At the end of conversion the inputs draw a small current spike while charging the sample-and-hold.

For superior dynamic performance in dual supply mode, the LTC1405 should be operated with the analog inputs centered at ground, and in single supply mode the inputs should be centered at 2.5V. If required, the analog inputs can be driven differentially via a transformer. Refer to Table 2 for a summary of the analog input and reference configurations and their relative advantages.

Figure 2. Reference Circuit

Figure 3a. Using the LT1019-2.5 As an External Reference; Input Range = ±1.25V

www.BDTIC.com/Linear

| SUPPLIES | COUPLING            | V <sub>REF</sub> | GAIN | A <sub>IN</sub> + | A <sub>IN</sub> <sup>-</sup> | COMMENTS                                     |

|----------|---------------------|------------------|------|-------------------|------------------------------|----------------------------------------------|

| ±5V      | DC                  | 4.096V           | 1x   | ±2.048            | 0                            | Best SNR, THD                                |

| 5V       | DC                  | 4.096V           | 2x   | 2.5 ± 1.024       | 2.5                          | Best SINAD, THD for Single Supply            |

| 5V       | DC                  | 2.048V           | 1x   | 2.5 ± 1.024       | 2.5                          | Worse Noise than Above Case                  |

| 5V       | DC                  | 4.096V           | 1x   | 2.5 ± 2.048       | 2.5                          | Best Single Supply Noise, THD Is Not Optimal |

| 5V       | DC                  | 4.096V           | 1x   | 0 to 4.096        | 2.048                        | Same As Above                                |

| ±5V      | AC<br>(Transformer) | 4.096V           | 1x   | ±1.024            | ±1.024                       | Very Best SNR, THD                           |

| 5V       | AC<br>(Transformer) | 4.096V           | 1x   | 2.5 ± 1.024       | 2.5 ± 1.024                  | Very Best SNR, THD for Single Supply         |

Table 2. Comparison of Analog Input Configurations

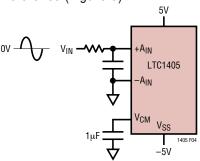

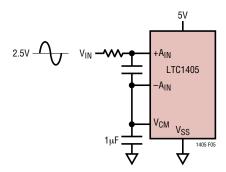

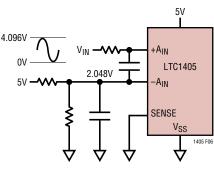

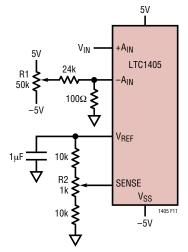

### DC Coupling the Input

In most applications the analog input signal can be directly coupled to the LTC1405 inputs. If the input signal is centered around ground, such as when dual supply op amps are used, simply connect  $A_{IN}^{-}$  to ground and connect  $V_{SS}$  to -5V (Figure 4). In a single power supply system with the input signal centered around 2.5V, connect  $A_{IN}^{-}$  to  $V_{CM}$  and  $V_{SS}$  to ground (Figure 5). If the input signal is not centered around ground or 2.5V, the voltage for  $A_{IN}^{-}$  must be generated externally by a resistor divider or a voltage reference (Figure 6).

Figure 4. DC Coupling a Ground Centered Signal (Dual Supply System)

Figure 5. DC Coupling a Signal Centered Around 2.5V (Single Supply System)

Figure 6. DC Coupling a OV to 4.096V Signal

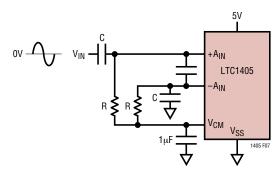

### AC Coupling the Input

The analog inputs to the LTC1405 can also be AC coupled through a capacitor, though in most cases it is simpler to directly couple the input to the ADC. Figure 7 shows an example where the input signal is centered around ground and the ADC operates from a single 5V supply. Note that the performance would improve if the ADC was operated from a dual supply and the input was directly coupled (as in Figure 4). With AC coupling the DC resistance to ground should be roughly matched for  $A_{IN}^+$  and  $A_{IN}^-$  to maintain offset accuracy.

Figure 7. AC Coupling to the LTC1405. Note That the Input Signal Can Almost Always Be Directly Coupled with Better Performance 1405fa

### **Differential Operation**

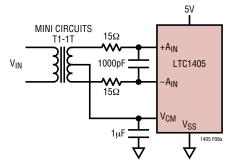

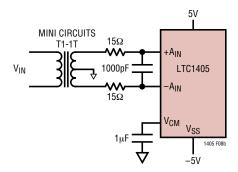

The THD and SFDR performance of the LTC1405 can be improved by using a center tap RF transformer to drive the inputs differentially. Though the signal can no longer be DC coupled, the improvement in dynamic performance makes this an attractive solution for some applications. Typical connections for single and dual supply systems are shown in Figures 8a and 8b. Good choices for transformers are the Mini Circuits T1-1T (1:1 turns ratio) and T4-6T (1:4 turns ratio). For best results the transformer should be located close to the LTC1405 on the printed circuit board.

Figure 8a. Single Supply Transformer Coupled Input

Figure 8b. Dual Supply Transformer Coupled Input

### **Choosing an Input Amplifier**

Choosing an input amplifier is easy if a few requirements are taken into consideration. First, to limit the magnitude of the voltage spike seen by the amplifier from charging the sampling capacitor, choose an amplifier that has a low output impedance (<100 $\Omega$ ) at the closed-loop bandwidth frequency. For example, if an amplifier is used in a gain of 1 and has a unity-gain bandwidth of 50MHz, then the output impedance at 50MHz must be less than 100 $\Omega$ . The second requirement is that the closed-loop bandwidth must be greater than 50MHz to ensure adequate smallsignal settling for full throughput rate. If slower op amps are used, more settling time can be provided by increasing the time between conversions.

The best choice for an op amp to drive the LTC1405 will depend on the application. Generally applications fall into two categories: AC applications where dynamic specifications are most critical and time domain applications where DC accuracy and settling time are most critical.

### **Input Filtering**

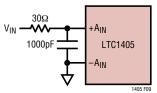

The noise and the distortion of the input amplifier and other circuitry must be considered since they will add to the LTC1405 noise and distortion. The small-signal bandwidth of the sample-and-hold circuit is 100MHz. Any noise or distortion products that are present at the analog inputs will be summed over this entire bandwidth. Noisy input circuitry should be filtered prior to the analog inputs to minimize noise. A simple 1-pole RC filter is sufficient for many applications.

For example, Figure 9 shows a 1000pF capacitor from  $+A_{IN}$  to  $-A_{IN}$  and a 30 $\Omega$  source resistor to limit the input bandwidth to 5.3MHz. The 1000pF capacitor also acts as a charge reservoir for the input sample-and-hold and isolates the amplifier driving V<sub>IN</sub> from the ADC's small current glitch. In undersampling applications, an input capacitor this large may prohibitively limit the input bandwidth. If this is the case, use as large an input capacitance as possible. High quality capacitors and resistors should be used since these components can add distortion. NPO and silver mica type dielectric capacitors have excellent linearity. Carbon surface mount resistors can generate distortion from self-heating and from damage that may occur during soldering. Metal film surface mount resistors are much less susceptible to both problems.

Figure 9. RC Input Filter

### Digital Outputs and Overflow Bit (OF)

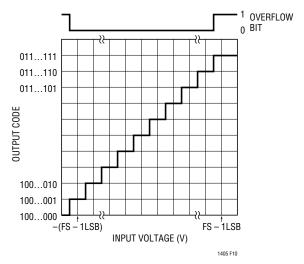

Figure 10 shows the ideal input/output characteristics for the LTC1405. The output data is two's complement binary for all input ranges and for both single and dual supply operation. One LSB =  $V_{REF}/4.096$ . To create a straight binary output, invert the MSB (D11). The overflow bit (OF) indicates when the analog input is outside the input range of the converter. OF is high when the output code is 1000 0000 0000 or 0111 1111 1111.

Figure 10. LTC1405 Transfer Characteristics

#### Full-Scale and Offset Adjustment

In applications where absolute accuracy is important, offset and full-scale errors can be adjusted to zero. Offset error should be adjusted before full-scale error. Figure 11 shows a method for error adjustment for a dual supply, 4.096V application. For zero offset error apply -0.5mV (i. e., -0.5LSB) at + A<sub>IN</sub> and adjust R1 until the output code flickers between 0000 0000 0000 and 1111 1111 1111. For full-scale adjustment, apply an input voltage of 2.0465V (FS -1.5LSBs) at + A<sub>IN</sub> and adjust R2 until the output code flickers between 0111 1111 1110 and 0111 1111 1111.

### **Digital Output Drivers**

The LTC1405 output drivers can interface to logic operating from 3V to 5V by setting  $OV_{DD}$  to the logic power supply. If 5V output is desired,  $OV_{DD}$  can be shorted to  $V_{DD}$  and share its decoupling capacitor. Otherwise,  $OV_{DD}$  requires its own 1µF decoupling capacitor. To prevent digital

noise from affecting performance, the load capacitance on the digital outputs should be minimized. If large capacitive loads are required, (>30pF) external buffers or  $100\Omega$  resistors in series with the digital outputs are suggested.

Figure 11. Offset and Full-Scale Adjust Circuit

### Timing

The conversion start is controlled by the rising edge of the CLK pin. Once a conversion is started it cannot be stopped or restarted until the conversion cycle is complete. Output data is updated at the end of conversion, or about 150ns after a conversion is begun. There is an additional two cycle pipeline delay, so the data for a given conversion is output two full clock cycles plus 150ns after the convert start. Thus output data can be latched on the third CLK rising edge after the rising edge that samples the input.

### **Clock Input**

The LTC1405 only uses the rising edge of the CLK pin for internal timing, and CLK doesn't necessarily need to have a 50% duty cycle. For optimal AC performance the rise time of the CLK should be less than 5ns. If the available clock has a rise time slower than 5ns, it can be locally sped up with a logic gate. With single supply operation the clock can be driven with 5V CMOS, 3V CMOS or TTL logic levels. With dual power supplies the clock should be driven with 5V CMOS levels.

As with all fast ADCs, the noise performance of the LTC1405 is sensitive to clock jitter when high speed inputs

are present. The SNR performance of an ADC when the performance is limited by jitter is given by:

$SNR = -20\log (2\pi f_{IN}t_J)dB$

where  $f_{IN}$  is the frequency of an input sine wave and  $t_J$  is the root-mean-square jitter due to the clock, the analog input and the A/D aperture jitter. To minimize clock jitter, use a clean clock source such as a crystal oscillator, treat the clock signals as sensitive analog traces and use dedicated packages with good supply bypassing for any clock drivers.

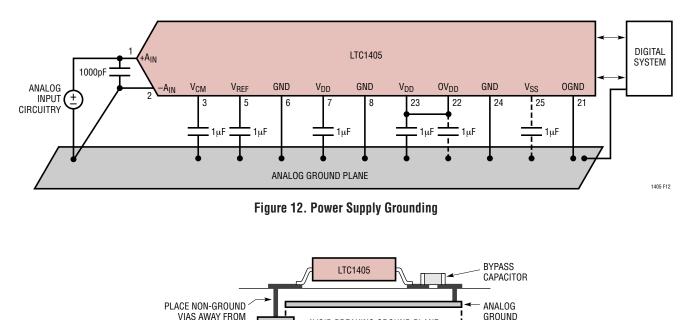

### **Board Layout**

To obtain the best performance from the LTC1405, a printed circuit board with a ground plane is required. Layout for the printed circuit board should ensure that digital and analog signal lines are separated as much as possible. In particular, care should be taken not to run any digital track alongside an analog signal track.

An analog ground plane separate from the logic system ground should be placed under and around the ADC. Pins 6, 8 and 24 (GND), Pin 21 (OGND) and all other analog grounds should be connected to this ground plane. In single supply mode, Pin 25 ( $V_{SS}$ ) should also be

GROUND PLANE AND

BYPASS CAPACITORS

connected to this ground plane. All bypass capacitors for the LTC1405 should also be connected to this ground plane (Figure 12). The digital system ground should be connected to the analog ground plane at only one point, near the OGND pin.

The analog ground plane should be as close to the ADC as possible. Care should be taken to avoid making holes in the analog ground plane under and around the part. To accomplish this, we recommend placing vias for power and signal traces outside the area containing the part and the decoupling capacitors (Figure 13).

### **Supply Bypassing**

High quality, low series resistance ceramic  $1\mu$ F capacitors should be used at both  $V_{DD}$  pins,  $V_{CM}$  and  $V_{REF}$ . If  $V_{SS}$  is connected to -5V it should also be bypassed to ground with  $1\mu$ F. In single supply operation  $V_{SS}$  should be shorted to the ground plane as close to the part as possible. If  $OV_{DD}$  is not shorted to Pin 23 ( $V_{DD}$ ) it also requires a  $1\mu$ F decoupling capacitor to ground. Surface mount capacitors such as the AVX 0805ZC105KAT provide excellent bypassing in a small board space. The traces connecting the pins and the bypass capacitors must be kept short and should be made as wide as possible.

PLANE

1405 F13

Figure 13. Cross Section of LTC1405 Printed Circuit Board

AVOID BREAKING GROUND PLANE

IN THIS AREA

www.BDTIC.com/Linear

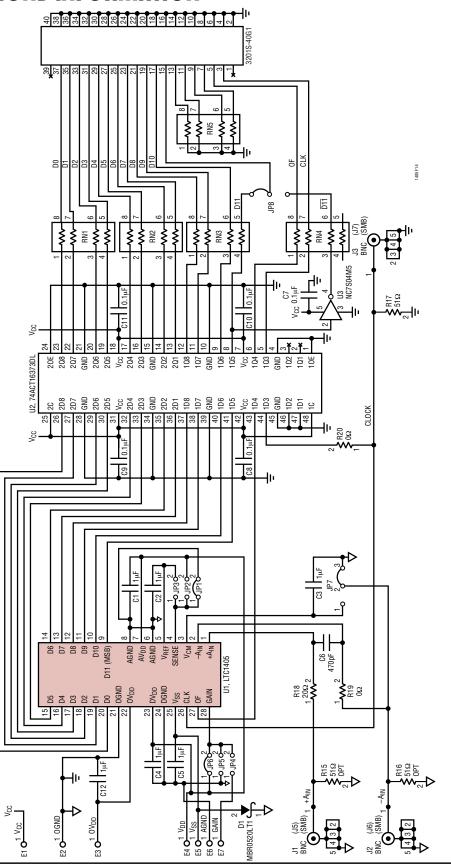

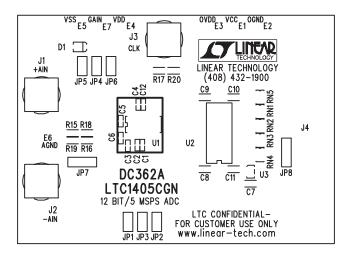

# **APPLICATIONS INFORMATION**

Figure 14. LTC1405 Demo Board Schematic

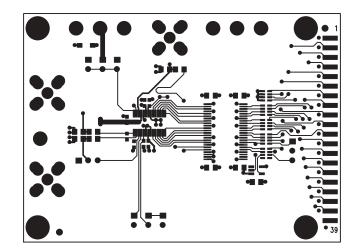

Figure 15. Top Silkscreen Layer for LTC1405/LTC1420 Demo Board

Figure 16. Top Layer for LTC1405/LTC1420 Demo Board

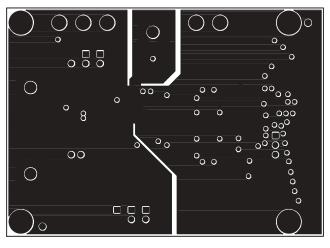

Figure 17. Ground Plane Layer for LTC1405/LTC1420 Demo Board

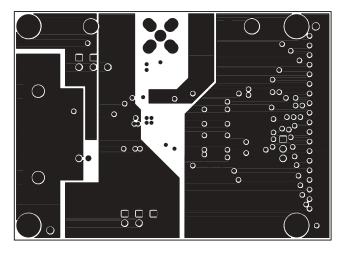

Figure 18. Power Plane Layer for LTC1405/LTC1420 Demo Board

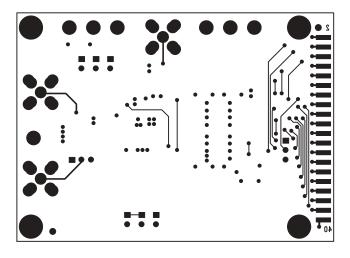

Figure 19. Bottom Layer for LTC1405/LTC1420 Demo Board

# TYPICAL APPLICATION

Single Supply, 5Msps, 12-Bit ADC with 3V Logic Outputs

18

www.BDTIC.com/Linear

### PACKAGE DESCRIPTION

**GN Package**

### **TYPICAL APPLICATION**

### **RELATED PARTS**

| PART NUMBER      | DESCRIPTION                                           | COMMENTS                                             |

|------------------|-------------------------------------------------------|------------------------------------------------------|

| LT1019           | Precision Bandgap Reference                           | 0.05% Max Initial Accuracy, 5ppm/°C Max Drift        |

| LTC1402          | Serial 12-Bit, 2.2 Msps ADC                           | 16-Pin Narrow SSOP Package, 72dB SINAD               |

| LTC1403/LTC1403A | 14-Bit/12-Bit, 2.8Msps Serial ADC                     | 3V, 14mW, Differential Input, MSOP Package           |

| LTC1407/LTC1407A | 14-Bit/12-Bit, 3Msps Simultaneous Sampling Serial ADC | 3V, 14mW, 2-Channel Differential Input, MSOP Package |

| LTC1412          | 12-Bit, 3Msps, Sampling ADC with Parallel Output      | Best Dynamic Performance, SINAD = 72dB at Nyquist    |

| LTC1415          | Single 5V, 12-Bit, 1.25Msps with Parallel Output      | 55mW Power Dissipation, 72dB SINAD                   |

| LTC1420          | 12-Bit, 10Msps, Sampling ADC                          | Pin Compatible with LTC1405                          |

| LTC1668          | 16-Bit, 50Msps DAC                                    | 87dB SFDR, 1.5LSB DNL, Low Power                     |

| LTC2225          | 12-Bit, 10Msps ADC                                    | 60mW, 71dB SNR, 5mm x 5mm QFN                        |

| LTC2226          | 12-Bit, 25Msps ADC                                    | 75mW, 71dB SNR, 5mm x 5mm QFN                        |

| LTC2227          | 12-Bit, 40Msps ADC                                    | 125mW, 71dB SNR, 5mm x 5mm QFN                       |

| LTC2228          | 12-Bit, 65Msps ADC                                    | 210mW, 71dB SNR, 5mm x 5mm QFN                       |

| LTC2236          | 10-Bit, 25Msps ADC                                    | 75mW, 61dB SNR, 5mm x 5mm QFN                        |

| LTC2237          | 10-Bit, 40Msps ADC                                    | 125mW, 61dB SNR, 5mm x 5mm QFN                       |

| LTC2238          | 10-Bit, 65Msps ADC                                    | 210mW, 61dB SNR, 5mm x 5mm QFN                       |

| LTC2245          | 14-Bit, 10Msps ADC                                    | 60mW, 74.4dB SNR, 5mm x 5mm QFN                      |

| LTC2246          | 14-Bit, 25Msps ADC                                    | 75mW, 74dB SNR, 5mm x 5mm QFN                        |

| LTC2247          | 14-Bit, 40Msps ADC                                    | 125mW, 74dB SNR, 5mm x 5mm QFN                       |

| LTC2248          | 14-Bit, 65Msps ADC                                    | 210mW, 74dB SNR, 5mm x 5mm QFN                       |

20 Li

Linear Technology, Corport of TIC.com/Linear 1630 McCarthy Blvd., Milpitas, CA 95035-7417 (408) 432-1900 • FAX: (408) 434-0507 • www.linear.com

LT/TP 1204 1K REV A • PRINTED IN USA