# LTC 1873

Dual 550kHz Synchronous 2-Phase Switching Regulator Controller with 5-Bit VID

## FEATURES

- Two Independent PWM Controllers in One Package

- Side 1 Output Is Compliant with Intel Desktop VRM 8.4 Specifications (Includes 5-Bit VID DAC)

- 1.3V to 3.5V Output Voltage with 50mV/100mV Steps

- Two Sides Run Out-of-Phase to Minimize C<sub>IN</sub>

- All N-Channel External MOSFET Architecture

- No External Current Sense Resistors Required

- Precison Internal 0.8V ±1% Reference

- 550kHz Switching Frequency Minimizes External Component Size

- Very Fast Transient Response

- Up to 25A Output Current per Channel

- Low Shutdown Current: < 100µA</p>

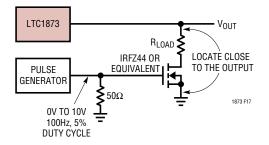

- Small 28-Pin SSOP Package

## **APPLICATIONS**

- Microprocessor Core and I/O Supplies

- Multiple Logic Supply Generator

- High Efficiency Power Conversion

- Chipset Power Supply

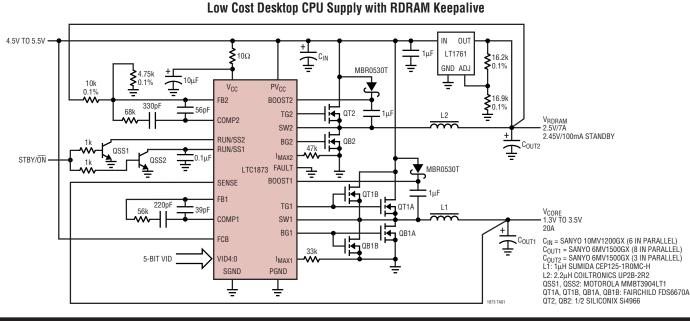

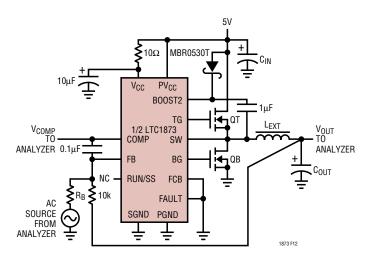

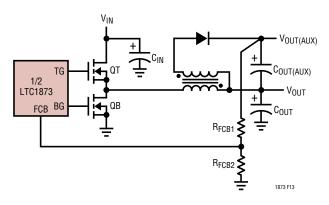

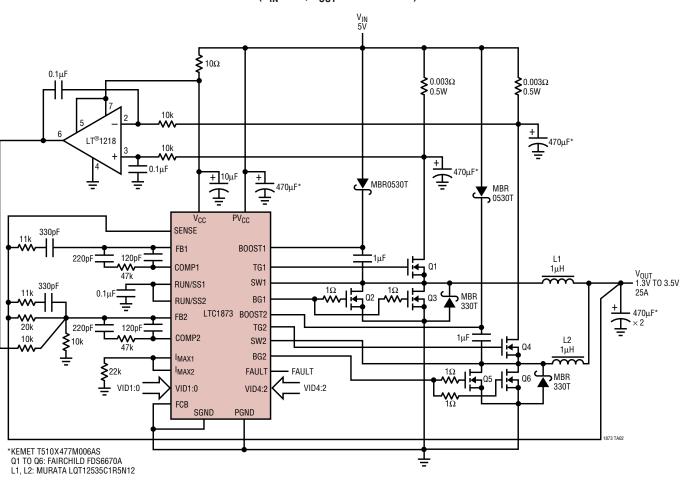

# TYPICAL APPLICATION

# DESCRIPTION

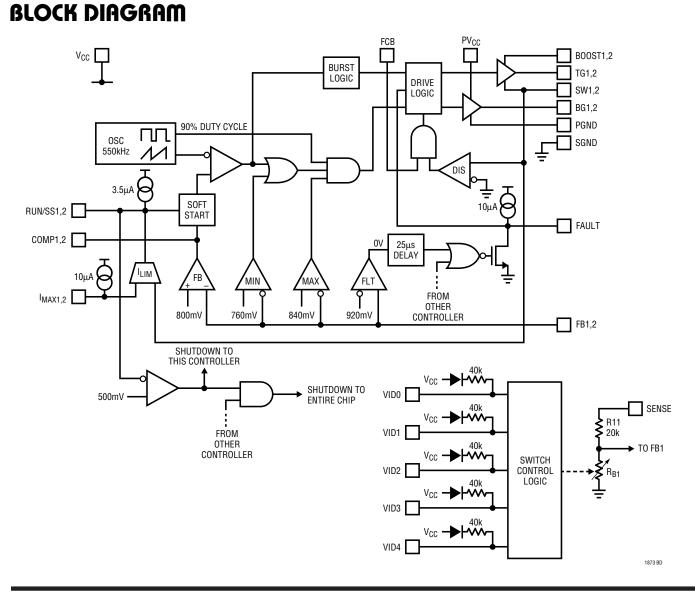

The LTC<sup>®</sup>1873 is a dual switching regulator controller optimized for high efficiency with low input voltages. It includes two complete, on-chip, independent switching regulator controllers. Each is designed to drive a pair of external N-channel MOSFETs in a voltage mode feedback, synchronous buck configuration. The LTC1873 includes digital output voltage adjustment on side 1 that conforms to the Intel Desktop VID specification. A constant-frequency, true PWM design minimizes external component size and cost and optimizes load transient performance. The synchronous buck architecture automatically shifts to discontinuous and then to Burst Mode<sup>TM</sup> operation as the output load decreases, ensuring maximum efficiency over a wide range of load currents.

The LTC1873 features an onboard reference trimmed to 1% and delivers better than 1.5% regulation at the converter outputs over all combinations of line, load and temperature. Each channel can be enabled independently; with both channels disabled, the LTC1873 shuts down and supply current drops below  $100\mu$ A.

CT, LTC and LT are registered trademarks of Linear Technology Corporation. Burst Mode is a trademark of Linear Technology Corporation.

# **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| Supply Voltage                                     |

|----------------------------------------------------|

| V <sub>CC</sub>                                    |

| BOOST <i>n</i>                                     |

| BOOST <i>n</i> – SW <i>n</i>                       |

| Input Voltage                                      |

| SW <i>n</i> –1V to 8V                              |

| VID <i>n</i> –0.3V to 7V                           |

| All Other Inputs $-0.3V$ to V <sub>CC</sub> + 0.3V |

| Peak Output Current < 10µs                         |

| TG <i>n</i> , BG <i>n</i> 5A                       |

| Operating Temperature Range                        |

| (Note 2)40°C to 85°C                               |

| Storage Temperature Range –65°C to 150°C           |

| Lead Temperature (Soldering, 10 sec)               |

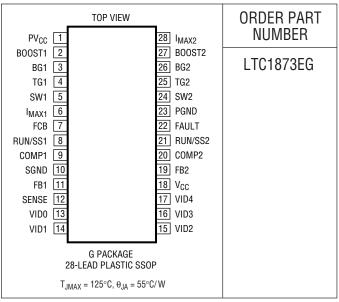

## PACKAGE/ORDER INFORMATION

Consult factory for Industrial and Military grade parts.

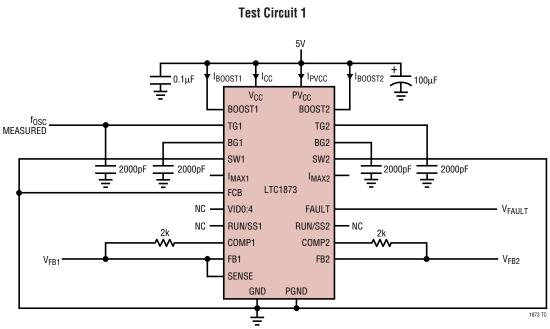

## **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are T<sub>A</sub> = 25°C. V<sub>CC</sub> = 5V unless otherwise specified. (Note 4)

| SYMBOL             | PARAMETER                        | CONDITIONS                                                 |   | MIN   | ТҮР        | MAX      | UNITS    |

|--------------------|----------------------------------|------------------------------------------------------------|---|-------|------------|----------|----------|

| Main Control Loop  |                                  |                                                            |   |       |            |          |          |

| V <sub>CC</sub>    | V <sub>CC</sub> Supply Voltage   |                                                            | • | 3     |            | 7        | V        |

| PV <sub>CC</sub>   | PV <sub>CC</sub> Supply Voltage  | (Note 3)                                                   | • | 3     |            | 7        | V        |

| BV <sub>CC</sub>   | BOOST Pin Voltage                | V <sub>BOOST</sub> – V <sub>SW</sub> (Note 3)              | • | 2.7   |            | 7        | V        |

| I <sub>CC</sub>    | V <sub>CC</sub> Supply Current   | Test Circuit 1<br>RUN/SS1 = RUN/SS2 = 0V (Note 6)          | • |       | 2.2<br>30  | 8<br>100 | mA<br>μA |

| IPV <sub>CC</sub>  | PV <sub>CC</sub> Supply Current  | Test Circuit 1 (Note 5)<br>RUN/SS1 = RUN/SS2 = 0V (Note 6) | • |       | 2.2<br>6   | 6<br>100 | mA<br>μA |

| I <sub>BOOST</sub> | BOOST Pin Current                | Test Circuit 1 (Note 5)<br>RUN/SS1 = RUN/SS2 = 0V          | • |       | 1.3<br>0.1 | 3<br>10  | mA<br>μA |

| V <sub>FB</sub>    | Feedback Voltage                 | Test Circuit 1                                             | • | 0.790 | 0.800      | 0.810    | V        |

| $\Delta V_{FB}$    | Feedback Voltage Line Regulation | V <sub>CC</sub> = 3V to 7V                                 | • |       | ±0.005     | ±0.05    | %/V      |

| I <sub>FB</sub>    | Feedback Current                 | FB2 Only (Note 7)                                          | • |       | ±0.001     | ±1       | μA       |

| V <sub>FCB</sub>   | FCB Threshold                    |                                                            | • | 0.75  | 0.8        | 0.85     | V        |

| $\Delta V_{FCB}$   | FCB Feedback Hysteresis          |                                                            |   |       | 20         |          | mV       |

| I <sub>FCB</sub>   | FCB Pin Current                  |                                                            | • |       | ±0.001     | ±1       | μA       |

| V <sub>RUN</sub>   | RUN/SS Pin RUN Threshold         |                                                            | • | 0.45  | 0.55       | 0.65     | V        |

| I <sub>SS</sub>    | Soft Start Source Current        | RUN/SSn = 0V                                               |   | -1.5  | -3.5       | -5.5     | μA       |

## **ELECTRICAL CHARACTERISTICS**

The  $\bullet$  denotes specifications which apply over the full operating temperature range, otherwise specifications are T<sub>A</sub> = 25°C. V<sub>CC</sub> = 5V unless otherwise specified. (Note 4)

| SYMBOL                          | PARAMETER                        | CONDITIONS                                                                                                        |   | MIN  | ТҮР        | MAX | UNITS            |

|---------------------------------|----------------------------------|-------------------------------------------------------------------------------------------------------------------|---|------|------------|-----|------------------|

| Switching Cha                   | iracteristics                    | · · ·                                                                                                             |   |      |            |     |                  |

| V <sub>OSC</sub>                | Oscillator Amplitude             |                                                                                                                   |   |      | 1          |     | V <sub>P-P</sub> |

| f <sub>OSC</sub>                | Oscillator Frequency             | Test Circuit 1                                                                                                    | • | 475  | 550        | 750 | kHz              |

| $\Phi_{0SC2}$                   | Controller 2 Oscillator Phase    | Relative to Controller 1                                                                                          |   |      | 180        |     | DEG              |

| DC <sub>MIN1</sub>              | Minimum Duty Cycle               | V <sub>FB</sub> < V <sub>MAX</sub>                                                                                | • | 7    | 10         |     | %                |

| DC <sub>MIN2</sub>              | Minimum Duty Cycle               | $V_{FB} > V_{MAX}$                                                                                                | • | 0    |            |     | %                |

| DC <sub>MAX</sub>               | Maximum Duty Cycle               |                                                                                                                   | • | 87   | 90         | 93  | %                |

| t <sub>NOV</sub>                | Driver Nonoverlap                | Test Circuit 1 (Note 9)                                                                                           | • |      | 40         | 100 | ns               |

| t <sub>r</sub> , t <sub>f</sub> | Driver Rise/Fall Time            | Test Circuit 1 (Note 9)                                                                                           | • |      | 12         | 80  | ns               |

| Feedback Am                     | plifier                          |                                                                                                                   |   |      |            |     |                  |

| A <sub>VFB</sub>                | FB DC Gain                       |                                                                                                                   |   | 74   | 85         |     | dB               |

| GBW                             | FB Gain Bandwidth                |                                                                                                                   |   |      | 25         |     | MHz              |

| I <sub>ERR</sub>                | FB Sink/Source Current           | COMP <sub>N</sub> Output                                                                                          | • | ±3   | ±10        |     | mA               |

| V <sub>MIN</sub>                | MIN Comparator Threshold         |                                                                                                                   | • |      | 760        | 785 | mV               |

| V <sub>MAX</sub>                | MAX Comparator Threshold         |                                                                                                                   | • | 815  | 840        |     | mV               |

| <b>Current Limit</b>            | Loop                             |                                                                                                                   |   |      |            |     |                  |

| A <sub>VILIM</sub>              | I <sub>LIM</sub> Gain            |                                                                                                                   |   |      | 40         |     | dB               |

| IIMAX                           | I <sub>MAX</sub> Source Current  | I <sub>MAX</sub> = 0V                                                                                             | • | -7   | -10        | -14 | μA               |

| Status Output                   | S                                |                                                                                                                   |   |      |            |     |                  |

| V <sub>FAULT</sub>              | FAULT Trip Point                 | $V_{FB}$ Relative to Regulated $V_{OUT}$                                                                          |   | +10  | + 15       | +20 | %                |

| V <sub>OLF</sub>                | FAULT Output Low Voltage         | I <sub>FAULT</sub> = 1mA                                                                                          | • |      | 0.03       | 0.1 | V                |

| I <sub>FAULT</sub>              | FAULT Output Current             | $V_{FAULT} = 0V$                                                                                                  |   |      | -10        |     | μA               |

| t <sub>FAULT</sub>              | FAULT Delay Time                 | $V_{FB} > V_{FAULT}$ to FAULT $\oint$ (Note 9)                                                                    |   |      | 25         |     | μs               |

| VID Inputs                      |                                  |                                                                                                                   |   |      |            |     |                  |

| R1                              | Resistance Between SENSE and FB1 | Side 1 Only                                                                                                       |   |      | 20         |     | kΩ               |

| V <sub>OUT</sub> Error %        | Output Voltage Accuracy          | Programmed from 1.3V to 3.5V                                                                                      |   | -1.5 |            | 1.5 | %                |

| R <sub>PULLUP</sub>             | VID Input Pull-Up Resistance     | V <sub>DIODE</sub> = 0.6V (Note 8)                                                                                |   |      | 40         |     | kΩ               |

| VID <sub>T</sub>                | VID Input Voltage Threshold      | $ \begin{array}{l} V_{IL} \; (2.7V \leq V_{CC} \leq 5.5V) \\ V_{IH} \; (2.7V \leq V_{CC} \leq 5.5V) \end{array} $ |   | 1.6  |            | 0.4 | V<br>V           |

| I <sub>VID-LEAK</sub>           | VID Input Leakage Current        | $V_{CC} < VID < 7V$ (Note 8)                                                                                      |   |      | 0.01       | ±1  | μA               |

| V <sub>PULLUP</sub>             | VID Pull-Up Voltage              | V <sub>CC</sub> = 3.3V<br>V <sub>CC</sub> = 5V                                                                    |   |      | 2.8<br>4.5 |     | V<br>V           |

**Note 1:** Absolute Maximum Ratings are those values beyond which the life of a device may be impaired.

**Note 2:** The LTC1873 is guaranteed to meet performance specifications from 0°C to 70°C. Specifications over the -40°C to 85°C operating temperature range are assured by design, characterization and correlation with statistical process controls.

**Note 3:**  $PV_{CC}$  and  $BV_{CC}$  ( $V_{BOOST} - V_{SW}$ ) must be greater than  $V_{GS(ON)}$  of the external MOSFETs used to ensure proper operation.

**Note 4:** All currents into device pins are positive; all currents out of device pins are negative. All voltages are referenced to ground unless otherwise specified.

**Note 5:** Supply current in normal operation is dominated by the current needed to charge and discharge the external MOSFET gates. This current will vary with supply voltage and the external MOSFETs used.

**Note 6:** Supply current in shutdown is dominated by external MOSFET leakage and may be significantly higher than the quiescent current drawn by the LTC1873, especially at elevated temperature.

**Note 7:** Feedback current at FB1 will be higher due to internal VID resistors.

**Note 8:** Each built-in pull-up resistor attached to the VID inputs also has a series diode connected to  $V_{CC}$  to allow input voltages higher than the  $V_{CC}$  supply without damage or clamping. (See Block Diagram.)

**Note 9:** Rise and fall times are measured at 20% to 80% levels. Delay and nonoverlap times are measured using 50% levels.

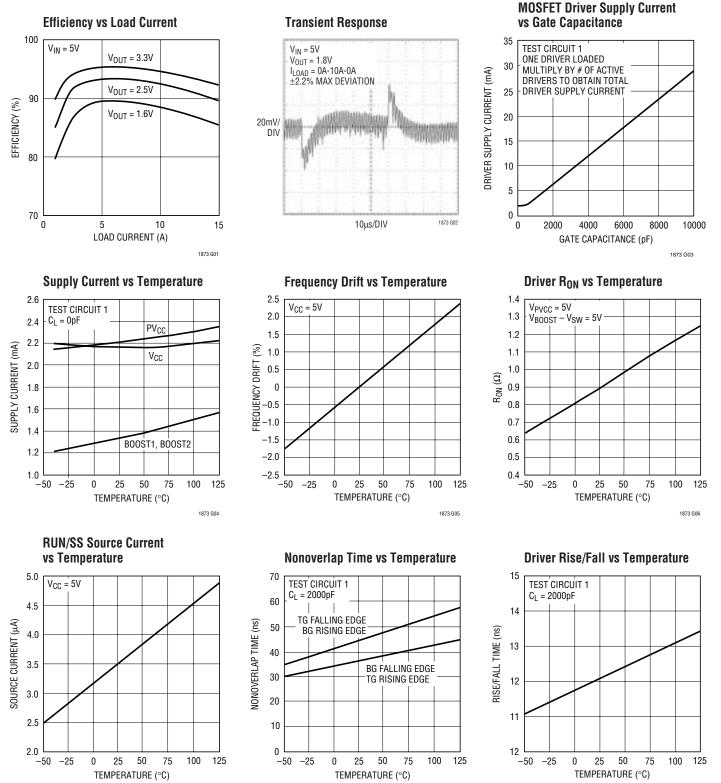

# TYPICAL PERFORMANCE CHARACTERISTICS

www.BDTIC.com/Linear

1873 G08

1873 G07

### PIN FUNCTIONS

**PV<sub>CC</sub> (Pin 1):** Driver Power Supply Input.  $PV_{CC}$  provides power to the two BG*n* output drivers.  $PV_{CC}$  must be connected to a voltage high enough to fully turn on the external MOSFETs QB1 and QB2.  $PV_{CC}$  should generally be connected directly to V<sub>IN</sub>.  $PV_{CC}$  requires at least a 1µF bypass capacitor directly to PGND.

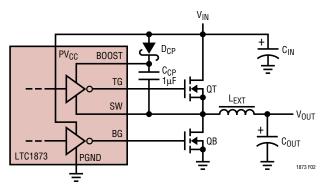

**BOOST1 (Pin 2):** Controller 1 Top Gate Driver Supply. The BOOST1 pin supplies power to the floating TG1 driver. BOOST1 should be bypassed to SW1 with a 1 $\mu$ F capacitor. An additional Schottky diode from V<sub>IN</sub> to BOOST1 pin will create a complete floating charge-pumped supply at BOOST1. No other external supplies are required.

**BG1 (Pin 3):** Controller 1 Bottom Gate Drive. The BG1 pin drives the gate of the bottom N-channel synchronous switch MOSFET, QB1. BG1 is designed to drive up to 10,000pF of gate capacitance directly. If RUN/SS1 goes low, BG1 will go low, turning off QB1. If FAULT mode is tripped, BG1 will go high and stay high, keeping QB1 on until the power is cycled.

**TG1 (Pin 4):** Controller 1 Top Gate Drive. The TG1 pin drives the gate of the top N-channel MOSFET, QT1. The TG1 driver draws power from the BOOST1 pin and returns to the SW1 pin, providing true floating drive to QT1. TG1 is designed to drive up to 10,000pF of gate capacitance directly. In shutdown or fault modes, TG1 will go low.

**SW1 (Pin 5):** Controller 1 Switching Node. SW1 should be connected to the switching node of converter 1. The TG1 driver ground returns to SW1, providing floating gate drive to the top N-channel MOSFET switch, QT1. The voltage at SW1 is compared to I<sub>MAX1</sub> by the current limit comparator while the bottom MOSFET, QB1, is on.

**I**<sub>MAX1</sub> (Pin 6): Controller 1 Current Limit Set. The I<sub>MAX1</sub> pin sets the current limit comparator threshold for controller 1. If the voltage drop across the bottom MOSFET, QB1, exceeds the magnitude of the voltage at I<sub>MAX1</sub>, controller 1 will go into current limit. The I<sub>MAX1</sub> pin has an internal 10µA current source pull-up, allowing the current threshold to be set with a single external resistor to PGND. This current setting resistor should be Kelvin connected to the source of QB1. See the Current Limit Programming section for more information on choosing R<sub>IMAX</sub>.

**FCB (Pin 7):** Force Continuous Bar. The FCB pin forces both converters to maintain continuous synchronous operation regardless of load when the voltage at FCB drops below 0.8V. FCB is normally tied to  $V_{CC}$ . To force continuous operation, tie FCB to SGND. FCB can also be connected to a feedback resistor divider from a secondary winding on one converter's inductor to generate a third regulated output voltage. Do not leave FCB floating.

**RUN/SS1 (Pin 8):** Controller 1 Run/Soft-Start. Pulling RUN/SS1 to SGND will disable controller 1 and turn off both of its external MOSFET switches. Pulling both RUN/SS pins down will shut down the entire LTC1873, dropping the quiescent supply current below 50 $\mu$ A. A capacitor from RUN/SS1 to SGND will control the turn-on time and rate of rise of the controller 1 output voltage at power-up. An internal 3.5 $\mu$ A current source pull-up at RUN/SS1 pin sets the turn-on time at approximately 50ms/ $\mu$ F.

**COMP1 (Pin 9):** Controller 1 Loop Compensation. The COMP1 pin is connected directly to the output of the first controller's error amplifier and the input to the PWM comparator. An RC network is used at the COMP1 pin to compensate the feedback loop for optimum transient response.

**SGND (Pin 10):** Signal Ground. All internal low power circuitry returns to the SGND pin. Connect to a low impedance ground, separated from the PGND node. All feedback, compensation and soft-start connections should return to SGND. SGND and PGND should connect only at a single point, near the PGND pin and the negative plate of the  $C_{IN}$  bypass capacitor.

**FB1 (Pin 11):** Controller 1 Feedback Input. The loop compensation network for controller 1 should be connected to FB1. FB1 is connected internally to the VID resistor network to set the output voltage at side 1.

SENSE (Pin 12): Output Sense. Connect to V<sub>OUT1</sub>.

**VID0 to VID4 (Pins 13 to 17):** VID Programming Inputs. These are logic inputs that set the output voltage at side 1 to a preprogrammed value (see Table 1). VID4 is the MSB, VID0 is the LSB. The codes selected by the VID*n* inputs correspond to the Intel Desktop VID specification. Each

## PIN FUNCTIONS

VID*n* pin includes an on-chip  $40k\Omega$  pull-up resistor in series with a diode (see Block Diagram).

$V_{CC}$  (Pin 18): Power Supply Input. All internal circuits except the output drivers are powered from this pin.  $V_{CC}$  should be connected to a low noise power supply voltage between 3V and 7V and should be bypassed to SGND with at least a 1  $\mu$ F capacitor in close proximity to the LTC1873.

**FB2 (Pin 19):** Controller 2 Feedback Input. FB2 should be connected through a resistor divider network to  $V_{OUT2}$  to set the ouput voltage. The loop compensation network for controller 2 also connects to FB2.

**COMP2 (Pin 20):** Controller 2 Loop Compensation. See COMP1.

**RUN/SS2 (Pin 21):** Controller 2 Run/Soft-Start. See RUN/SS1.

**FAULT (Pin 22):** Output Overvoltage Fault (Latched). The FAULT pin is an open-drain output with an internal  $10\mu$ A pull-up. If either regulated output voltage rises more than 15% above its programmed value for more than 25µs, the FAULT output will go high and the entire LTC1873 will be

disabled. When FAULT is high, both BG pins will go high, turning on the bottom MOSFET switches and pulling down the high output voltage. The LTC1873 will remain latched in this state until the power is cycled. When FAULT mode is active, the FAULT pin will be pulled up with an internal  $10\mu$ A current source. Tying FAULT directly to SGND will disable latched FAULT mode and will allow the LTC1873 to resume normal operation when the overvoltage fault is removed.

**PGND (Pin 23):** Power Ground. The BG*n* drivers return to this pin. Connect PGND to a high current ground node in close proximity to the sources of external MOSFETs, QB1 and QB2, and the  $V_{IN}$  and  $V_{OUT}$  bypass capacitors.

SW2 (Pin 24): Controller 2 Switching Node. See SW1.

TG2 (Pin 25): Controller 2 Top Gate Drive. See TG1.

BG2 (Pin 26): Controller 2 Bottom Gate Drive. See BG1.

**BOOST2 (Pin 27):** Controller 2 Top Gate Driver Supply. See BOOST1.

IMAX2 (Pin 28): Controller 2 Current Limit Set. See IMAX1.

## **TEST CIRCUIT**

### **OVERVIEW**

The LTC1873 is a dual, step-down (buck), voltage mode feedback switching regulator controller. It is designed to be used in a synchronous switching architecture with two external N-channel MOSFETs per channel. It is intended to operate from a low voltage input supply (7V maximum) and provide a high power, high efficiency, precisely regulated output voltage. Several features make it particularly suited for microprocessor supply regulation. Output regulation is extremely tight, with DC line and load regulation and initial accuracy better than 1.5%, and total regulation including transient response inside of 3.5% with a prop-

erly designed circuit. The 550kHz switching frequency allows the use of physically small, low value external components without compromising performance. An onboard DAC sets the output voltage at channel 1, consistent with the Intel desktop VID specification (Table 1).

The LTC1873's internal feedback amplifier is a 25MHz gain-bandwidth op amp, allowing the use of complex multipole/zero compensation networks. This allows the feedback loop to maintain acceptable phase margin at higher frequencies than traditional switching regulator controllers allow, improving stability and maximizing transient response. The 800mV internal reference at channel 2

Table 1. VID Inputs and Corresponding Output Voltage for Channel 1

| CODE  | VID4 | VID3  | VID2  | VID1  | VIDO  | V <sub>OUT1</sub> |

|-------|------|-------|-------|-------|-------|-------------------|

| 00000 | GND  | GND   | GND   | GND   | GND   | 2.05V             |

| 00001 | GND  | GND   | GND   | GND   | Float | 2.00V             |

| 00010 | GND  | GND   | GND   | Float | GND   | 1.95V             |

| 00011 | GND  | GND   | GND   | Float | Float | 1.90V             |

| 00100 | GND  | GND   | Float | GND   | GND   | 1.85V             |

| 00101 | GND  | GND   | Float | GND   | Float | 1.80V             |

| 00110 | GND  | GND   | Float | Float | GND   | 1.75V             |

| 00111 | GND  | GND   | Float | Float | Float | 1.70V             |

| 01000 | GND  | Float | GND   | GND   | GND   | 1.65V             |

| 01001 | GND  | Float | GND   | GND   | Float | 1.60V             |

| 01010 | GND  | Float | GND   | Float | GND   | 1.55V             |

| 01011 | GND  | Float | GND   | Float | Float | 1.50V             |

| 01100 | GND  | Float | Float | GND   | GND   | 1.45V             |

| 01101 | GND  | Float | Float | GND   | Float | 1.40V             |

| 01110 | GND  | Float | Float | Float | GND   | 1.35V             |

| 01111 | GND  | Float | Float | Float | Float | 1.30V             |

\* 11111 is defined by Intel to signify "no CPU." The LTC1873 will generate the output voltage shown when this codes is selected.

allows regulated output voltages as low as 800mV without external level shifting amplifiers.

The LTC1873's synchronous switching logic transitions automatically into Burst Mode operation, maximizing efficiency with light loads. An onboard overvoltage (OV) fault flag indicates when an OV fault has occurred. The OV flag can be set to latch the device off when an OV fault has occurred, or to automatically resume operation when the fault is removed.

### 2-Phase Operation

The LTC1873 dual switching regulator controller offers considerable benefits using 2-phase operation. Circuit benefits include lower input filtering requirements, reduced electromagnetic interference (EMI) and increased efficiency associated with 2-phase operation.

Why the need for 2-phase operation? Until recently, constant-frequency dual switching regulators operated both channels in phase (i.e., single-phase operation). This means that both topside MOSFETs turned on at the same time, causing current pulses of up to twice the amplitude of those for one regulator to be drawn from the input

| CODE   | VID4  | VID3  | VID2  | VID1  | VIDO  | V <sub>OUT1</sub> |

|--------|-------|-------|-------|-------|-------|-------------------|

| 10000  | Float | GND   | GND   | GND   | GND   | 3.50V             |

| 10001  | Float | GND   | GND   | GND   | Float | 3.40V             |

| 10010  | Float | GND   | GND   | Float | GND   | 3.30V             |

| 10011  | Float | GND   | GND   | Float | Float | 3.20V             |

| 10100  | Float | GND   | Float | GND   | GND   | 3.10V             |

| 10101  | Float | GND   | Float | GND   | Float | 3.00V             |

| 10110  | Float | GND   | Float | Float | GND   | 2.90V             |

| 10111  | Float | GND   | Float | Float | Float | 2.80V             |

| 11000  | Float | Float | GND   | GND   | GND   | 2.70V             |

| 11001  | Float | Float | GND   | GND   | Float | 2.60V             |

| 11010  | Float | Float | GND   | Float | GND   | 2.50V             |

| 11011  | Float | Float | GND   | Float | Float | 2.40V             |

| 11100  | Float | Float | Float | GND   | GND   | 2.30V             |

| 11101  | Float | Float | Float | GND   | Float | 2.20V             |

| 11110  | Float | Float | Float | Float | GND   | 2.10V             |

| 11111* | Float | Float | Float | Float | Float | 2.00V             |

capacitor. These large amplitude current pulses increased the total RMS current flowing from the input capacitor, requiring the use of more expensive input capacitors and increasing both EMI and losses in the input capacitor and input power supply.

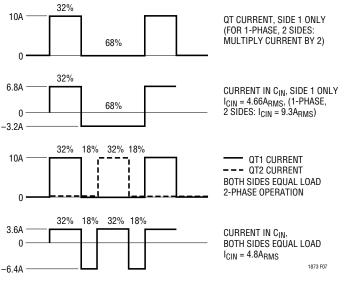

With 2-phase operation, the two channels of the LTC1873 are operated 180 degrees out of phase. This effectively interleaves the current pulses coming from the switches, greatly reducing the overlap time where they add together. The result is a significant reduction in total RMS input current, which in turn allows less expensive input capacitors to be used, reduces shielding requirements for EMI and improves real world operating efficiency.

Figure 7 shows example waveforms for a single switching regulator channel versus a 2-phase LTC1873 system with both sides switching. A single-phase dual regulator with both sides operating would exhibit double the single side numbers. In this example, 2-phase operation reduced the RMS input current from 9.3A<sub>RMS</sub> (2 × 4.66A<sub>RMS</sub>) to 4.8A<sub>RMS</sub>. While this is an impressive reduction in itself, remember that the power losses are proportional to  $I_{RMS}^2$ , meaning that the actual power wasted is reduced by a

factor of 3.75. The reduced input ripple voltage also means less power is lost in the input power path, which could include batteries, switches, trace/connector resistances and protection circuitry. Improvements in both conducted and radiated EMI also directly accrue as a result of the reduced RMS input current and voltage.

### Small Footprint

The LTC1873 operates at a 550kHz switching frequency, allowing it to use low value inductors without generating excessive ripple currents. Because the inductor stores less energy per cycle, the physical size of the inductor can be reduced without risking core saturation, saving PCB board space. The high operating frequency also means less energy is stored in the output capacitors between cycles, minimizing their required value and size. The remaining components, including the SSOP-28 LTC1873, are tiny, allowing an entire dual-output LTC1873 circuit to be constructed in 1.5in<sup>2</sup> of PCB space. Further, this space is generally located right next to the microprocessor or in some similarly congested area, where PCB real estate is at a premium.

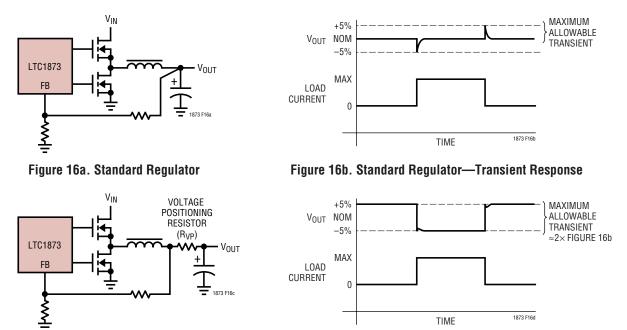

### Fast Transient Response

The LTC1873 uses a fast 25MHz GBW op amp as an error amplifier. This allows the compensation network to be designed with several poles and zeros in a more flexible configuration than with a typical  $g_m$  feedback amplifier. The high bandwidth of the amplifier, coupled with the high switching frequency and the low values of the external inductor and output capacitor, allow very high loop crossover frequencies. The low inductor value is the other half of the equation—with a typical value on the order of  $1\mu$ H, the inductor allows very fast di/dt slew rates. The result is superior transient response compared with conventional solutions.

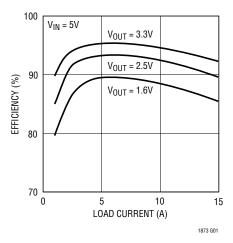

### High Efficiency

The LTC1873 uses a synchronous step-down (buck) architecture, with two external N-channel MOSFETs per output. A floating topside driver and a simple external charge pump provide full gate drive to the upper MOSFET.

The voltage mode feedback loop and MOSFET  $V_{DS}$  current limit sensing remove the need for an external current sense resistor, eliminating an external component and a source of power loss in the high current path. Properly designed circuits using low gate charge MOSFETs are capable of efficiencies exceeding 90% over a wide range of output voltages.

### VID Programming

The LTC1873 includes an onboard feedback network that programs the output voltage at side 1 in accordance with the Intel Desktop VID specification (Table 1). The network includes a 20k resistor (R1) connected from SENSE to FB1, and a variable value resistor (R<sub>B</sub>) from FB1 to SGND, with the value set by the digital code present at the VID0:4 pins. SENSE should be connected to  $V_{OUT1}$  to allow the network to monitor the output voltage. No additional feedback components are required to set the output voltage at controller 1, although loop compensation components are still required. Each VID*n* pin includes an internal 40k pull-up resistor, allowing it to float high if left unconnected. The pull-up resistors are connected to V<sub>CC</sub> through diodes (see Block Diagram), allowing the VID*n* pins to be pulled above V<sub>CC</sub> without damage.

Note that code 11111, defined by Intel to indicate "no CPU present," does generate an output voltage at  $V_{OUT1}$  (2.00V). Note also that controller 2 on the LTC1873 is not connected to the VID circuitry, and works independently from controller 1.

### **ARCHITECTURE DETAILS**

The LTC1873 dual switching regulator controller includes two independent regulator channels. The two sides of the chip and their corresponding external components act independently of each other with the exception of the common input bypass capacitor, the VID circuitry at side 1, and the FCB and FAULT pins, which affect both channels. In the following discussions, when a pin is referred to without mentioning which side is involved, that discussion applies equally to both sides.

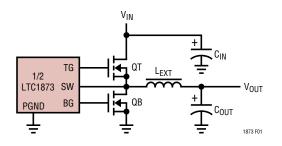

#### Switching Architecture

Each half of the LTC1873 is designed to operate as a synchronous buck converter (Figure 1). Each channel includes two high power MOSFET gate drivers to control external N-channel MOSFETs QT and QB. These drivers have  $0.5\Omega$  output impedances and can carry well over an amp of continuous current with peak currents up to 5A to slew large MOSFET gates quickly. The external MOSFETs are connected with the drain of QT attached to the input supply and the source of QT at the switching node SW. QB is the synchronous rectifier with its drain at SW and its source at PGND. SW is connected to  $V_{OUT}$ . The output capacitor is connected from  $V_{OUT}$  to PGND.

When a switching cycle begins, QB is turned off and QT is turned on. SW rises almost immediately to  $V_{IN}$  and the inductor current begins to increase. When the PWM pulse finishes, QT turns off and one nonoverlap interval later, QB turns on. Now SW drops to PGND and the inductor current decreases. The cycle repeats with the next tick of the master clock. The percentage of time spent in each mode is controlled by the duty cycle of the PWM signal, which in turn is controlled by the feedback amplifier. The master clock runs at a 550kHz rate and turns QT once every 1.8µs. In a typical application with a 5V input and a 1.5V output, the duty cycle will be set at  $1.5/5 \times 100\%$  or 30% by the feedback loop. This will give roughly a 540ns on-time for QT and a 1.26µs on-time for QB.

This constant frequency operation brings with it a couple of benefits. Inductor and capacitor values can be chosen with a precise operating frequency in mind and the feedback loop components can be similarly tightly specified. Noise generated by the circuit will always be in a known frequency band with the 550kHz frequency designed to leave the 455kHz IF band free of interference. Subharmonic oscillation and slope compensation, common headaches with constant frequency current mode switchers, are absent in voltage mode designs like the LTC1873.

During the time that QT is on, its source (the SW pin) is at  $V_{IN}$ .  $V_{IN}$  is also the power supply for the LTC1873. However, QT requires  $V_{IN} + V_{GS(ON)}$  at its gate to achieve minimum  $R_{ON}$ . This presents a problem for the LTC1873 it needs to generate a gate drive signal at TG higher than its highest supply voltage. To accomplish this, the TG driver runs from floating supplies, with its negative supply attached to SW and its power supply at BOOST. This allows it to slew up and down with the source of QT. In combination with a simple external charge pump (Figure 2), this allows the LTC1873 to completely enhance the gate of QT without requiring an additional, higher supply voltage.

The two channels of the LTC1873 run from a common clock, with the phasing chosen to be 180° from side 1 to side 2. This has the effect of doubling the frequency of the switching pulses seen by the input bypass capacitor, significantly lowering the RMS current seen by the capacitor and reducing the value required (see the 2-Phase section).

#### **Feedback Amplifier**

Each side of the LTC1873 senses the output voltage at  $V_{OUT}$  with an internal feedback op amp (see Block Diagram). This is a real op amp with a low impedance output, 85dB open-loop gain and 25MHz gain-bandwidth product. The positive input is connected internally to an 800mV reference, while the negative input is connected to the FB

Figure 1. Synchronous Buck Architecture

pin. The output is connected to COMP, which is in turn connected to the soft-start circuitry and from there to the PWM generator.

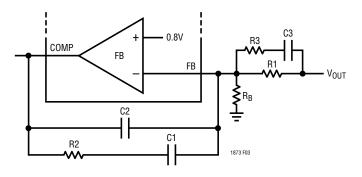

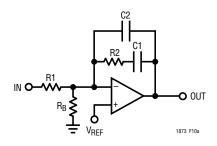

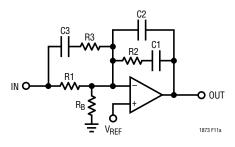

Unlike many regulators that use a resistor divider connected to a high impedance feedback input, the LTC1873 is designed to use an inverting summing amplifier topology with the FB pin configured as a virtual ground. This allows flexibility in choosing pole and zero locations not available with simple  $g_m$  configurations. In particular, it allows the use of "type 3" compensation, which provides a phase boost at the LC pole frequency and significantly improves loop phase margin (see Figure 3). The Feedback Loop/Compensation section contains a detailed explanation of type 3 feedback loops. Note that side 1 of the LTC1873 includes R1 and R<sub>B</sub> internally as part of the VID DAC circuitry.

Figure 3. "Type 3" Feedback Loop (Side 2 Shown)

#### **MIN/MAX COMPARATORS**

Two additional feedback loops keep an eye on the primary feedback amplifier and step in if the feedback node moves  $\pm 5\%$  from its nominal 800mV value. The MAX comparator (see Block Diagram) activates whenever FB rises more than 5% above 800mV. It immediately turns the top MOSFET (QT) off and the bottom MOSFET (QB) on and keeps them that way until FB falls back within 5% of its nominal value. This pulls the output down as fast as possible, preventing damage to the (often expensive) load. If FB rises because the output is shorted to a higher supply, QB will stay on until the short goes away, the higher supply current limits or QB dies trying to save the load. This behavior provides maximum protection against overvoltage faults at the output, while allowing the circuit to resume normal operation when the fault is removed. The overvoltage protection circuit can optionally be set to latch the output off permanently (see the Overvoltage Fault section).

The MIN comparator (see Block Diagram) trips whenever FB is more than 5% below 800mV and immediately forces the switch duty cycle to 90% to bring the output voltage back into range. It releases when FB is within the 5% window. MIN is disabled when the soft-start or current limit circuits are active—the only two times that the output should legitimately be below its regulated value.

Notice that the FB pin is the virtual ground node of the feedback amplifier. A typical compensation network does not include local DC feedback around the amplifier, so that the DC level at FB will be an accurate replica of the output voltage, divided down by R1 and  $R_B$  (Figure 3). However, the compensation capacitors will tend to attenuate AC signals at FB, especially with low bandwidth type 1 feedback loops. This creates a situation where the MIN and MAX comparators do not respond immediately to shifts in the output voltage, since they monitor the output at FB. Maximizing feedback loop bandwidth will minimize these delays and allow MIN and MAX to operate properly. See the Feedback Loop/Compensation section.

#### SHUTDOWN/SOFT-START

Each half of the LTC1873 has a RUN/SS pin. The RUN/SS pins perform two functions: when pulled to ground, each shuts down its half of the LTC1873, and each acts as a conventional soft-start pin, enforcing a maximum duty cycle limit proportional to the voltage at RUN/SS. An internal 3.5µA current source pull-up is connected to each RUN/SS pin, allowing a soft-start ramp to be generated with a single external capacitor to ground. The 3.5µA current sources are active even when the LTC1873 is shut down, ensuring the device will start when any external pull-down at RUN/SS is released. Either side can be shut down without affecting the operation of the other side. If both sides are shut down at the same time, the LTC1873 goes into a micropower sleep mode, and quiescent current drops typically below 50µA. Entering sleep mode also resets the FAULT latch, if it was set.

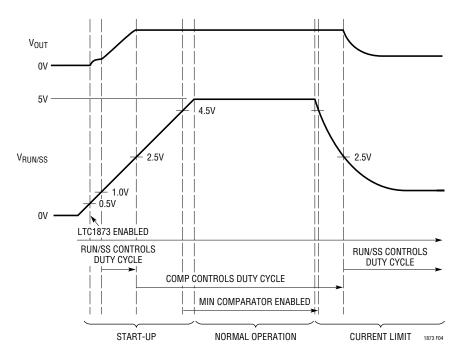

Each RUN/SS pin shuts down its half of the LTC1873 when it falls below about 0.5V (Figure 4). Between 0.5V and about 1V, that half is active, but the maximum duty cycle is limited to 10%. The maximum duty cycle limit increases linearly between 1V and 2.5V, reaching its final value of 90% when RUN/SS is above 2.5V. Somewhere before this point, the feedback amplifier will assume control of the loop and the output will come into regulation. When RUN/SS rises to 0.5V below  $V_{CC}$ , the MIN feedback comparator is enabled, and the LTC1873 is in full operation.

### **CURRENT LIMIT**

The LTC1873 includes an onboard current limit circuit that limits the maximum output current to a user-programmed level. It works by sensing the voltage drop across QB during the time that QB is on and comparing that voltage to a user-programmed voltage at  $I_{MAX}$ . Since QB looks like a low value resistor during its on-time, the voltage drop across it is proportional to the current flowing in it. In a buck converter, the average current in the inductor is equal to the output current. This current also flows through QB during its on-time. Thus, by watching the voltage across QB, the LTC1873 can monitor the output current. Any time QB is on and the current flowing to the output is reasonably large, the SW node at the drain of QB will be somewhat negative with respect to PGND. The LTC1873 senses this voltage and inverts it to allow it to compare the sensed voltage with a positive voltage at the I<sub>MAX</sub> pin. The I<sub>MAX</sub> pin includes a trimmed 10µA pull-up, enabling the user to set the voltage at I<sub>MAX</sub> with a single resistor, R<sub>IMAX</sub>, to ground. The LTC1873 compares the two inputs and begins limiting the output current when the magnitude of the negative voltage at the SW pin is greater than the voltage at I<sub>MAX</sub>.

The current limit detector is connected to an internal  $g_m$  amplifier that pulls a current from the RUN/SS pin proportional to the difference in voltage magnitudes between the SW and  $I_{MAX}$  pins. This current begins to discharge the soft-start capacitor at RUN/SS, reducing the duty cycle and controlling the output voltage until the current drops below the limit. The soft-start capacitor needs to move a fair amount before it has any effect on the duty cycle, adding a delay until the current limit takes effect (Figure 4). This allows the LTC1873 to experience brief overload conditions without affecting the output voltage regulation. The delay also acts as a pole in the current limit loop to

Figure 4. Soft-Start Operation in Start-Up and Current Limit

enhance loop stability. Larger overloads cause the softstart capacitor to pull down quickly, protecting the output components from damage. The current limit  $g_m$  amplifier includes a clamp to prevent it from pulling RUN/SS below 0.5V and shutting off the device.

Power MOSFET  $R_{DS(ON)}$  varies from MOSFET to MOSFET, limiting the accuracy obtainable from the LTC1873 current limit loop. Additionally, ringing on the SW node due to parasitics can add to the apparent current, causing the loop to engage early. The LTC1873 current limit is designed primarily as a disaster prevention, "no blow up" circuit, and is not useful as a precision current regulator. It should typically be set around 50% above the maximum expected normal output current to prevent component tolerances from encroaching on the normal current range. See the Current Limit Programming section for advice on choosing a valve for  $R_{IMAX}$ .

### DISCONTINUOUS/Burst Mode OPERATION

### Theory of operation

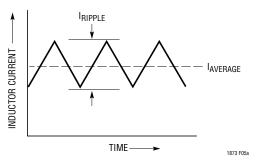

The LTC1873 switching logic has three modes of operation. Under heavy loads, it operates as a fully synchronous, continuous conduction switching regulator. In this mode of operation ("continuous" mode), the current in the inductor flows in the positive direction (toward the output) during the entire switching cycle, constantly supplying current to the load. In this mode, the synchronous switch (QB) is on whenever QT is off, so the current always flows through a low impedance switch, minimizing voltage drop and power loss. This is the most efficient mode of operation at heavy loads, where the resistive losses in the power devices are the dominant loss term.

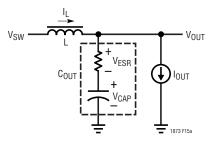

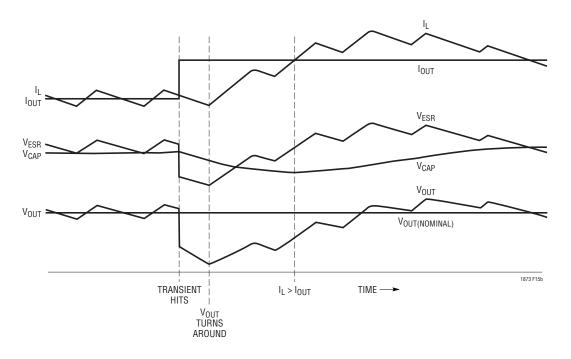

Continuous mode works efficiently when the load current is greater than half of the ripple current in the inductor. In a buck converter like the LTC1873, the average current in the inductor (averaged over one switching cycle) is equal to the load current. The ripple current is the difference between the maximum and the minimum current during a switching cycle (see Figure 5a). The ripple current depends on inductor value, clock frequency and output voltage, but is constant regardless of load as long as the LTC1873 remains in continuous mode. See the Inductor Selection section for a detailed description of ripple current.

As the output load current decreases in continuous mode, the average current in the inductor will reach a point where it drops below half the ripple current. At this point, the current in the inductor will reverse during a portion of the switching cycle, or begin to flow from the output back to the input. This does not adversely affect regulation, but does cause additional losses as a portion of the inductor current flows back and forth through the resistive power switches, giving away a little more power each time and lowering the efficiency. There are some benefits to allowing this reverse current flow: the circuit will maintain regulation even if the load current drops below zero (the load supplies current to the LTC1873) and the output ripple voltage and frequency remain constant at all loads, easing filtering requirements. Circuits that take advantage of this behavior can force the LTC1873 to operate in continuous mode at all loads by tying the FCB (Force Continuous Bar) pin to ground.

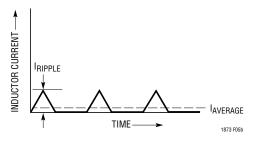

### **Discontinuous Mode**

To minimize the efficiency loss due to reverse current flow at light loads, the LTC1873 switches to a second mode of operation: discontinuous mode (Figure 5b). In discontinuous mode, the LTC1873 detects when the inductor current approaches zero and turns off QB for the remainder of the switch cycle. During this time, the voltage at the SW pin will float about  $V_{OUT}$ , the voltage across the inductor will be zero, and the inductor current remains zero until the next switching cycle begins and QT turns on again. This prevents current from flowing backwards in QB, eliminating that power loss term. It also reduces the ripple current in the inductor as the output current approaches zero.

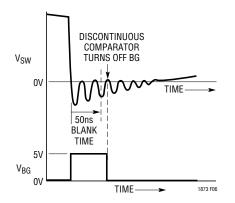

The LTC1873 detects that the inductor current has reached zero by monitoring the voltage at the SW pin while QB is on. Since QB acts like a resistor, SW should ideally be right at 0V when the inductor current reaches zero. In reality, the SW node will ring to some degree immediately after it is switched to ground by QB, causing some uncertainty as to the actual moment the average current in QB goes to zero. The LTC1873 minimizes this effect by ignoring the SW node for a fixed 50ns after QB turns on when the ringing

is most severe, and by including a few millivolts offset in the comparator that monitors the SW node. Despite these precautions, some combinations of inductor and layout parasitics can cause the LTC1873 to enter discontinuous mode erratically. In many cases, the time that QB turns off will correspond to a peak in the ringing waveform at the SW pin (Figure 6). This erratic operation isn't pretty, but retains much of the efficiency benefit of discontinuous mode and maintains regulation at all times.

Figure 5a. Continuous Mode

Figure 5b. Discontinuous Mode

Figure 6. Ringing at SW Causes Discontinuous Comparator to Trip Early

### **Burst Mode Operation**

Discontinuous mode removes a loss term due to resistive drop in QB, but the LTC1873 is still switching QT and QB on and off once a cycle. Each time an external MOSFET is turned on, the internal driver must charge its gate to  $V_{CC}$ . Each time it is turned off, that charge is lost to ground. At the high switching frequencies that the LTC1873 operates at, the charge lost to the gates can add up to tens of milliamps from  $V_{CC}$ . As the load current continues to drop, this quickly become the dominant power loss term, reducing efficiency once again.

Once again, the LTC1873 switches to a new mode to minimize efficiency loss: Burst Mode operation. As the circuit goes deeper and deeper into discontinuous mode, the total time QT and QB are on reduces. However, the ratio of the time that QT is on to the time that QB is on must remain constant for the output to stay in regulation. An internal timer circuit forces QT to stay on for at least 10% of a normal switching cycle. When the load drops to the point that the output requires less than 10% on-time at QT, the output voltage will begin to rise. The LTC1873 senses this rise and shuts both QT and QB off completely, skipping several switching cycles until the output falls back into range. It then resumes switching in discontinuous mode with QT at 10% duty cycle and the burst sequence repeats. The total deviation from the regulated output is within the 1.5% regulation tolerance of the LTC1873.

In Burst Mode operation, both resistive loss and switching loss are minimized while keeping the output in regulation. The ripple current will be set by the 10% QT on-time and the input supply voltage and is the lowest of all three operating modes. As the load current falls to zero in Burst Mode operation, the most significant loss term becomes the 3mA quiescent current drawn by each side of the LTC1873—usually much less than the minimum load current in a typical low voltage logic system. Burst Mode operation maximizes efficiency at low load currents, but can cause low frequency ripple in the output voltage as the cycle-skipping circuitry switches on and off.

#### FCB Pin

In some circumstances, it is desirable to control or disable discontinuous and Burst Mode operations. The FCB (Force Continuous Bar) pin allows the user to do this. When the FCB pin is high, the LTC1873 is allowed to enter discontinuous and Burst Mode operations at either side as required. If FCB is taken low, discontinuous and Burst Mode operations are disabled and both sides of the LTC1873 run in continuous mode regardless of load. This does not affect output regulation but does reduce efficiency at low output currents. The FCB pin threshold is specified at 0.8V  $\pm$ 50mV, and includes 20mV of hysteresis, allowing it to be used as a precision small-signal comparator.

#### **Paralleling Outputs**

Synchronous regulators (like the LTC1873) are known for their bullheadedness when their outputs are paralleled with other regulators. In particular, a synchronous regulator paralleled with another regulator whose output is slightly higher (perhaps just by millivolts) will happily sink amps of current attempting to pull its own output back down to what it thinks is the right value.

The LTC1873 discontinuous mode allows it to be paralleled with another regulator without fighting. A typical system might use the LTC1873 as a primary regulator and a small LDO as a backup regulator to keep SRAM alive when the main power is off. When the LTC1873 is shut down (by pulling RUN/SS to ground), both QT and QB turn off and the output goes into a high impedance state, allowing the smaller regulator to support the output voltage. However, if the LTC1873 is powered back up in continuous mode, it will begin a soft-start cycle with a low duty cycle, pulling the output down and corrupting the data stored in SRAM. The solution is to tie FCB high, allowing the device to start in discontinuous mode. Any reverse current flow in QB will trip the discontinuous mode circuitry, preventing the LTC1873 from pulling down the output.

### **OVERVOLTAGE FAULT**

The LTC1873 includes a single overvoltage fault flag for both channels: FAULT. FAULT is an open-drain output with an internal 10µA pull-up. If either FB pin rises more than 15% above the nominal 800mV value for more than 25us, the overvoltage comparator will trip, setting an internal latch. This latch releases the pull-down at FAULT, allowing the 10µA pull-up to take it high. When FAULT goes high, the LTC1873 stops all switching, turns both QB (bottom synchronous) MOSFETs on continuously and remains in this state until both RUN/SS pins are pulled low simultaneously, the power supply is recycled, or the FAULT pin is pulled low externally. This behavior is intended to protect a potentially expensive load from overvoltage damage at all costs. Under some conditions. this behavior can cause the output voltage to undershoot below ground. If latched FAULT mode is used, a Schottky diode should be added with its cathode at the output and its anode at ground to clamp the negative voltage to a safe level and prevent possible damage to the load and the output capacitors.

Note that in overvoltage conditions, the MAX comparator will kick in at just +5%, turning QB on continuously long before the output reaches +15%. Under most fault conditions, this is adequate to bring the output back down without firing the fault latch. Additionally, if MAX successfully keeps the output below +15%, the LTC1873 will resume normal regulation as soon as the output overvoltage fault is resolved.

In some circuits, the OV latch can be a liability. Consider a circuit where the output voltage at one channel may be changed on the fly by changing the VID code or switching in different feedback resistors. A downward adjustment of greater than 15% will fire the fault latch, disabling both sides of the LTC1873 until the power is recycled. In circuits such as this, the fault latch can be disabled by grounding the FAULT pin. The internal latch will still be set the first time the output exceeds +15%, but the 10 $\mu$ A current source pull-up will not be able to pull FAULT high, and the LTC1873 will ignore the latch and continue

normal operation. The MAX comparator will act as usual, turning on QB until output is within range and then allowing the loop to resume normal operation. FAULT can also be pulled down with external open-collector logic to restart a fault-latched LTC1873 as an alternative to recycling the power. Note that this will not reset the internal latch; if the external pull-down is released, the LTC1873 will reenter FAULT mode. To reset the latch, pull both RUN/ SS pins low simultaneously or cycle the power.

### **VID Considerations**

Some applications change the VID codes at channel 1 on the fly. This is possible with the LTC1873, but care must be taken to avoid tripping the overvoltage fault circuit. Stepping the voltage upwards abruptly is safe, but stepping down quickly by more than 15% can leave the system in a state where the output voltage is still at the old higher level, but the feedback node is set to expect a new, substantially lower voltage. If this condition persists for more than  $25\mu$ s, the overvoltage fault circuitry will activate and latch off the LTC1873.

The simplest solution is to disable the fault circuit by grounding the FAULT pin. Systems that must keep the fault circuit active should ensure that the output voltage is never programmed to step down by more than 15% in any single step. A safe strategy is to step the output down by 10% or less at a time and wait for the output to settle to the new value before taking subsequent steps. Regardless of the state of the FAULT pin, the load is always protected against overvoltage faults by the +5% MAX comparator.

### **EXTERNAL COMPONENT SELECTION**

### **POWER MOSFETs**

Getting peak efficiency out of the LTC1873 depends strongly on the external MOSFETs used. The LTC1873 requires at least two external MOSFETs per side—more if one or more of the MOSFETs are paralleled to lower on-resistance. To work efficiently, these MOSFETs must exhibit low  $R_{DS(ON)}$  at 5V V<sub>GS</sub> (3.3V V<sub>GS</sub> if the PV<sub>CC</sub> input supply is 3.3V) to minimize resistive power loss while they are conducting current. They must also have low gate charge to minimize transition losses during switching. On the other hand, voltage breakdown requirements in a typical LTC1873 circuit are pretty tame: the 7V maximum input voltage limits the  $V_{DS}$  and  $V_{GS}$  the MOSFETs can see to safe levels for most devices.

### Low R<sub>DS(ON)</sub>

$R_{DS(ON)}$  calculations are pretty straightforward.  $R_{DS(ON)}$  is the resistance from the drain to the source of the MOSFET when the gate is fully on. Many MOSFETs have  $R_{DS(ON)}$ specified at 4.5V gate drive—this is the right number to use in LTC1873 circuits running from a 5V supply. As current flows through this resistance while the MOSFET is on, it generates  $I^2R$  watts of heat, where I is the current flowing (usually equal to the output current) and R is the MOSFET  $R_{DS(ON)}$ . This heat is only generated when the MOSFET is on. When it is off, the current is zero and the power lost is also zero (and the other MOSFET is busy losing power).

This lost power does two things: it subtracts from the power available at the output, costing efficiency, and it makes the MOSFET hotter—both bad things. The effect is worst at maximum load when the current in the MOSFETs and thus the power lost are at a maximum. Lowering  $R_{DS(ON)}$  improves heavy load efficiency at the expense of additional gate charge (usually) and more cost (usually). Proper choice of MOSFET  $R_{DS(ON)}$  becomes a trade-off between tolerable efficiency loss, power dissipation and cost. Note that while the lost power has a significant effect on system efficiency, it only adds up to a watt or two in a typical LTC1873 circuit, allowing the use of small, surface mount MOSFETs without heat sinks.

### **Gate Charge**

Gate charge is the amount of charge (essentially, the number of electrons) that the LTC1873 needs to put into the gate of an external MOSFET to turn it on. The easiest way to visualize gate charge is to think of it as a capacitance from the gate pin of the MOSFET to SW (for QT) or to PGND (for QB). This capacitance is composed of MOSFET channel charge, actual parasitic drain-source capacitance and Miller-multiplied gate-drain capacitance, but can be approximated as a single capacitance from gate to source. Regardless of where the charge is going, the fact remains

that it all has to come out of  $V_{CC}$  to turn the MOSFET gate on, and when the MOSFET is turned back off, that charge all ends up at ground. In the meanwhile, it travels through the LTC1873's gate drivers, heating them up. More power lost!

In this case, the power is lost in little bite-sized chunks, one chunk per switch per cycle, with the size of the chunk set by the gate charge of the MOSFET. Every time the MOSFET switches, another chunk is lost. Clearly, the faster the clock runs, the more important gate charge becomes as a loss term. Old-fashioned switchers that ran at 20kHz could pretty much ignore gate charge as a loss term; in the 550kHz LTC1873, gate charge loss can be a significant efficiency penalty. Gate charge loss can be the dominant loss term at medium load currents, especially with large MOSFETs. Gate charge loss is also the primary cause of power dissipation in the LTC1873 itself.

### TG Charge Pump

There's another nuance of MOSFET drive that the LTC1873 needs to get around. The LTC1873 is designed to use N-channel MOSFETs for both QT and QB, primarily because N-channel MOSFETs generally cost less and have lower R<sub>DS(ON)</sub> than similar P-channel MOSFETs. Turning QB on is no big deal since the source of QB is attached to PGND; the LTC1873 just switches the BG pin between PGND and V<sub>CC</sub>. Driving QT is another matter. The source of QT is connected to SW which rises to V<sub>CC</sub> when QT is on. To keep QT on, the LTC1873 must get TG one MOSFET  $V_{GS(ON)}$  above  $V_{CC}$ . It does this by utilizing a floating driver with the negative lead of the driver attached to SW (the source of QT) and the V<sub>CC</sub> lead of the driver coming out separately at BOOST. An external  $1\mu$ F capacitor (C<sub>CP</sub>) connected between SW and BOOST (Figure 2) supplies power to BOOST when SW is high, and recharges itself through D<sub>CP</sub> when SW is low. This simple charge pump keeps the TG driver alive even as it swings well above  $V_{CC}$ . The value of the bootstrap capacitor C<sub>CP</sub> needs to be at least 100 times that of the total input capacitance of the topside MOSFET(s). For very large external MOSFETs (or multiple MOSFETs in parallel), C<sub>CP</sub> may need to be increased beyond the 1µF value.

### **INPUT SUPPLY**

The BiCMOS process that allows the LTC1873 to include large MOSFET drivers on-chip also limits the maximum input voltage to 7V. This limits the practical maximum input supply to a loosely regulated 5V or 6V rail. The LTC1873 will operate properly with input supplies down to about 3V, so a typical 3.3V supply can also be used if the external MOSFETs are chosen appropriately (see the Power MOSFETs section).

At the same time, the input supply needs to supply several amps of current without excessive voltage drop. The input supply must have regulation adequate to prevent sudden load changes from causing the LTC1873 input voltage to dip. In most typical applications where the LTC1873 is generating a secondary low voltage logic supply, all of these input conditions are met by the main system logic supply when fortified with an input bypass capacitor.

### **INPUT BYPASS CAPACITOR**

A typical LTC1873 circuit running from a 5V logic supply might provide 1.6V at 10A at one of its outputs. 5V to 1.6V implies a duty cycle of 32%, which means QT is on 32% of each switching cycle. During QT's on-time, the current drawn from the input equals the load current and during the rest of the cycle, the current drawn from the input is near zero. This 0A to 10A, 32% duty cycle pulse train adds up to  $4.7A_{RMS}$  at the input. At 550kHz, switching cycles last about  $1.8\mu$ s—most system logic supplies have no hope of regulating output current with that kind of speed. A local input bypass capacitor is required to make up the difference and prevent the input supply from dropping drastically when QT kicks on. This capacitor is usually chosen for RMS ripple current capability and ESR as well as value.

The input bypass capacitor in an LTC1873 circuit is common to both channels. Consider our 10A example case with the other side of the LTC1873 disabled. The input bypass capacitor gets exercised in three ways: its ESR must be low enough to keep the initial drop as QT turns on within reason (100mV or so); its RMS current capability must be adequate to withstand the 4.7 $A_{RMS}$  ripple current at the input and the capacitance must be large enough to

maintain the input voltage until the input supply can make up the difference. Generally, a capacitor that meets the first two parameters will have far more capacitance than is required to keep capacitance-based droop under control. In our example, we need  $0.01\Omega$  ESR to keep the input drop under 100mV with a 10A current step and 4.7A<sub>RMS</sub> ripple current capacity to avoid overheating the capacitor. These requirements can be met with multiple low ESR tantalum or electrolytic capacitors in parallel, or with a large monolithic ceramic capacitor.

The two sides of the LTC1873 run off a single master clock and are wired 180° out of phase with each other to significantly reduce the total capacitance/ESR needed at the input. Assuming 100mV of ripple and 10A output current, we needed an ESR of  $0.01\Omega$  and 4.7A ripple current capability for one side. Now, assume both sides are running simultaneously with identical loading. If the two sides switched in phase, all the loading conditions would double and we'd need enough capacitance for  $9.4A_{\text{RMS}}$  and  $0.005\Omega$  ESR. With the two sides out of phase, the input current is 4.8A<sub>BMS</sub>—barely larger than the single case (Figure 7)! The peak current deltas are still only 10A, requiring the same  $0.01\Omega$  ESR rating. As long as the capacitor we chose for the single side application can support the slightly higher 4.8A<sub>BMS</sub> current, we can add the second channel without changing the input capacitor at all. As a general rule, an input bypass capacitor capable of supporting the larger output current channel

Figure 7. Current Waveforms

#### Calculating RMS Current in CIN

A buck regulator like the LTC1873 draws pulses of current from the input capacitor during normal operation. The input capacitor sees this as AC current, and dissipates power proportional to the RMS value of the input current waveform. To properly specify the capacitor, we need to know the RMS value of the input current. Calculating the approximate RMS value of a pulse train with a fixed duty cycle is straightforward, but the LTC1873 complicates matters by running two sides simultaneously and out of phase, creating a complex waveform at the input.

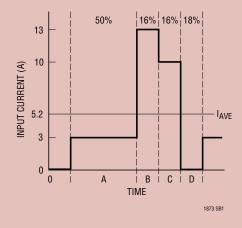

To calculate the approximate RMS value of the input current, we first need to calculate the average DC value with both sides of the LTC1873 operating at maximum load. Over a single period, the system will spend some time with one top switch on and the other off, perhaps some time with both switches on, and perhaps some time with both switches off. During the time each top switch is on, the current will equal that side's full load output current. When both switches are on, the total current will be the sum of the two full load currents, and when both are off, the current is effectively zero. Multiply each current value by the percentage of the period that the current condition lasts, and sum the results—this is the average DC current value.

As an example, consider a circuit that takes a 5V input and generates 3.3V at 3A at side 1 and 1.6V at 10A at side 2. When a cycle starts, TG1 turns on and 3A flows

Figure SB1. Average Current Calculation

from  $C_{IN}$  (time point A). 50% of the way through, TG2 turns on and the total current is 13A (time point B). Shortly thereafter, TG1 turns off and the current drops to 10A (time point C). Finally, TG2 turns off and the current spends a short time at 0 before TG1 turns on again (time point D).

$$I_{AVG} = (3A \cdot 0.5) + (13A \cdot 0.16) + (10A \cdot 0.16) + (0A \cdot 0.18) = 5.18A$$

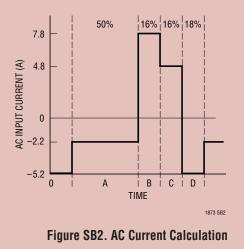

Now we can calculate the RMS current. Using the same waveform we used to calculate the average DC current, subtract the average current from each of the DC values. Square each current term and multiply the squares by the same period percentages we used to calculate the average DC current. Sum the results and take the square root. The result is the approximate RMS current as seen by the input capacitor with both sides of the LTC1873 at full load. Actual RMS current will differ due to inductor ripple

can support both channels running simultaneously (see the 2-Phase Operation section for more information). Details on how to calculate the maximum RMS input current can be found in Application Note 77.

Tantalum capacitors are a popular choice as input capacitors for LTC1873 applications, but they deserve a special caution here. Generic tantalum capacitors have a destructive failure mechanism when they are subjected to large RMS currents (like those seen at the input of a LTC1873). current and resistive losses, but this approximate value is adequate for input capacitor calculation purposes.

$$I_{\text{RMS}} = \sqrt{ \left( -2.18^2 \cdot 0.5 \right) + \left( 7.82^2 \cdot 0.16 \right) + }$$

$$= 4.55 A_{\text{RMS}}$$

If the circuit is likely to spend time with one side operating and the other side shut down, the RMS current will need to be calculated for each possible case (side 1 on, side 2 off; side 1 off, side 2 on; both sides on). The capacitor must be sized to withstand the largest RMS current of the three—sometimes this occurs with one side shut down!

Side1only:

$$I_{AVE1} = (3A \cdot 0.67) + (0A \cdot 0.33) = 2.01A$$

$$I_{RMS1} = \sqrt{(1^2 \cdot 0.67) + (-2^2 \cdot 0.33)} = 1.42A_{RMS}$$

Side 2 only:

$$I_{AVE2} = (10A \cdot 0.32) + (0A \cdot 0.68) = 3.2A$$

$$I_{RMS2} = \sqrt{(6.8^2 \cdot 0.32) + (-3.2^2 \cdot 0.68)}$$

$$= 4.66A_{RMS} > 4.55A_{RMS}$$

Consider the case where both sides are operating at the same load, with a 50% duty cycle at each side. The RMS current with both sides running is near zero, while the RMS current with one side active is 1/2 the total load current of that side.

At some random time after they are turned on, they can blow up for no apparent reason. The capacitor manufacturers are aware of this and sell special "surge tested" tantalum capacitors specifically designed for use with switching regulators. When choosing a tantalum input capacitor, make sure that it is rated to carry the RMS current that the LTC1873 will draw. If the data sheet doesn't give an RMS current rating, chances are the capacitor isn't surge tested. Don't use it!

### **OUTPUT BYPASS CAPACITOR**

The output bypass capacitor has guite different requirements from the input capacitor. The ripple current at the output of a buck regulator like the LTC1873 is much lower than at the input, due to the fact that the inductor current is constantly flowing at the output whenever the LTC1873 is operating in continuous mode. The primary concern at the output is capacitor ESR. Fast load current transitions at the output will appear as voltage across the ESR of the output bypass capacitor until the feedback loop in the LTC1873 can change the inductor current to match the new load current value. This ESR step at the output is often the single largest budget item in the load regulation calculation. As an example, our hypothetical 1.6V, 10A switcher with a  $0.01\Omega$  ESR output capacitor would experience a 100mV step at the output with a 0 to 10A load step—a 6.3% output change!

Usually the solution is to parallel several capacitors at the output. For example, to keep the transient response inside of 3% with the previous design, we'd need an output ESR better than  $0.0048\Omega$ . This can be met with three  $0.014\Omega$ ,  $470\mu$ F tantalum capacitors in parallel.

### INDUCTOR

The inductor in a typical LTC1873 circuit is chosen primarily for value and saturation current. The inductor value sets the ripple current, which is commonly chosen at around 30% of the anticipated full load current. Ripple current is set by:

$$I_{RIPPLE} = \frac{t_{ON(QB)}(V_{OUT})}{L}$$

In our hypothetical 1.6V, 10A example, we'd set the ripple current to 30% of 10A or 3A, and the inductor value would be:

$$\begin{split} L &= \frac{t_{ON(QB)}(V_{OUT})}{I_{RIPPLE}} = \frac{(1.2\mu s)(1.6V)}{4A} = 0.5\mu H\\ \text{with } t_{ON(QB)} &= \left(1 - \frac{1.6V}{5V}\right) / 550 \text{kHz} = 1.2\mu s \end{split}$$

The inductor must not saturate at the expected peak current. In this case, if the current limit was set to 15A, the

inductor should be rated to withstand 15A  $\,$  + 1/2  $I_{RIPPLE},$  or 16.5A without saturating.

### FEEDBACK LOOP/COMPENSATION<sup>1</sup>

### Feedback Loop Types

In a typical LTC1873 circuit, the feedback loop consists of the modulator, the external inductor and output capacitor, and the feedback amplifier and its compensation network. All of these components affect loop behavior and need to be accounted for in the loop compensation. The modulator consists of the internal PWM generator, the output MOSFET drivers and the external MOSFETs themselves. From a feedback loop point of view, it looks like a linear voltage transfer function from COMP to SW and has a gain roughly equal to the input voltage. It has fairly benign AC behavior at typical loop compensation frequencies with significant phase shift appearing at half the switching frequency.

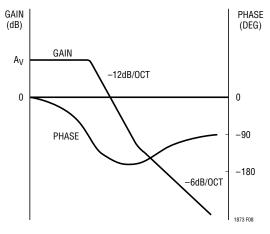

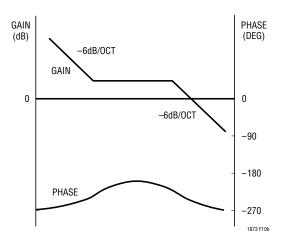

The external inductor/output capacitor combination makes a more significant contribution to loop behavior. These components cause a second order LC roll-off at the output, with the attendant 180° phase shift. This roll-off is what filters the PWM waveform, resulting in the desired DC output voltage, but the phase shift complicates the loop compensation if the gain is still higher than unity at the pole frequency. Eventually (usually well above the LC pole frequency), the reactance of the output capacitor will approach its ESR, and the roll-off due to the capacitor will stop, leaving 6dB/octave and 90° of phase shift (Figure 8).

<sup>1</sup>The information in this section is based on the paper "The K Factor: A New Mathematical Tool for Stability Analysis and Synthesis" by H. Dean Venable, Venable Industries, Inc. For complete paper, see "Reference Reading #4" at www.linear-tech.com.

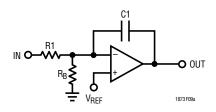

Figure 8. Ideal Transfer Function of Buck Modulator

So far, the AC response of the loop is pretty well out of the user's control. The modulator is a fundamental piece of the LTC1873 design, and the external L and C are usually chosen based on the regulation and load current requirements without considering the AC loop response. The feedback amplifier, on the other hand, gives us a handle with which to adjust the AC response. The goal is to have 180° phase shift at DC (so the loop regulates) and something less than 360° phase shift at the point that the loop gain falls to 0dB. The simplest strategy is to set up the feedback amplifier as an inverting integrator, with the 0dB frequency lower than the LC pole (Figure 9). This "type 1" configuration is stable but transient response will be less than exceptional if the LC pole is at a low frequency.

Figure 9a. Type 1 Amplifier Schematic Diagram

Figure 9b. Type 1 Amplifier Transfer Function

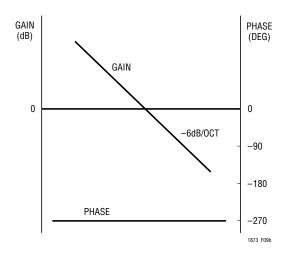

Figure 10 shows an improved "type 2" circuit that uses an additional pole-zero pair to temporarily remove  $90^{\circ}$  of phase shift. This allows the loop to remain stable with  $90^{\circ}$  more phase shift in the LC section, provided the loop reaches 0dB gain near the center of the phase "bump."

Figure 10a. Type 2 Amplifier Schematic Diagram

Figure 10b. Type 2 Amplifier Transfer Function

Type 2 loops work well in systems where the ESR zero in the LC roll-off happens close to the LC pole, limiting the total phase shift due to the LC. The additional phase compensation in the feedback amplifier allows the OdB point to be at or above the LC pole frequency, improving loop bandwidth substantially over a simple type 1 loop. It has limited ability to compensate for LC combinations where low capacitor ESR keeps the phase shift near 180° for an extended frequency range. LTC1873 circuits using conventional switching grade electrolytic output capacitors can often get acceptable phase margin with type 2 compensation.

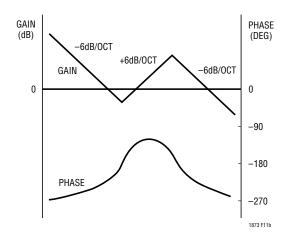

"Type 3" loops (Figure 11) use two poles and two zeros to obtain a 180° phase boost in the middle of the frequency band. A properly designed type 3 circuit can maintain acceptable loop stability even when low output capacitor ESR causes the LC section to approach 180° phase shift well above the initial LC roll-off. As with a type 2 circuit, the

Figure 11a. Type 3 Amplifier Schematic Diagram

Figure 11b. Type 3 Amplifier Transfer Function

loop should cross through 0dB in the middle of the phase bump to maximize phase margin. Many LTC1873 circuits using low ESR tantalum or OS-CON output capacitors need type 3 compensation to obtain acceptable phase margin with a high bandwidth feedback loop.

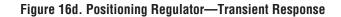

### Feedback Component Selection

Selecting the R and C values for a typical type 2 or type 3 loop is a nontrivial task. The applications shown in this data sheet show typical values, optimized for the power components shown. They should give acceptable performance with similar power components, but can be way off if even one major power component is changed significantly. Applications that require optimized transient response will need to recalculate the compensation values specifically for the circuit in question. The underlying mathematics are complex, but the component values can be calculated in a straightforward manner if we know the gain and phase of the modulator at the crossover frequency. Modulator gain and phase can be measured directly from a breadboard, or can be simulated if the appropriate parasitic values are known. Measurement will give more accurate results, but simulation can often get close enough to give a working system. To measure the modulator gain and phase directly, wire up a breadboard with an LTC1873 and the actual MOSFETs, inductor, and input and output capacitors that the final design will use. This breadboard should use appropriate construction techniques for high speed analog circuitry: bypass capacitors located close to the LTC1873, no long wires connecting components, appropriately sized ground returns, etc. Wire the feedback amplifier as a simple type 1 loop, with a 10k resistor from  $V_{OUT}$  to FB and a 0.1µF feedback capacitor from COMP to FB. Choose the bias resistor (R<sub>B</sub>) as required to set the desired output voltage. Disconnect R<sub>B</sub> from ground and connect it to a signal generator or to the source output of a network analyzer (Figure 12) to inject a test signal into the loop. Measure the gain and phase from the COMP pin to the output node at the positive terminal of the output capacitor. Make sure the analyzer's input is AC coupled so that the DC voltages present at both the COMP and  $V_{OUT}$ nodes don't corrupt the measurements or damage the analyzer.

If breadboard measurement is not practical, a SPICE simulation can be used to generate approximate gain/ phase curves. Plug the expected capacitor, inductor and MOSFET values into the following SPICE deck and generate an AC plot of  $V(V_{OUT})/V(COMP)$  in dB and phase of

V(OUT) in degrees. Refer to your SPICE manual for details of how to generate this plot.

```

*1873 modulator gain/phase

*©1999 Linear Technology

*this file written to run with PSpice 8.0

*may require modifications for other SPICE

simulators

*MOSFETs

rfet mod sw 0.02

;MOSFET rdson

*inductor

lext sw outl lu

;inductor value

rl out1 out 0.005

; inductor series R

*output cap