## EN55022B Compliant 36V<sub>IN</sub>, 15V<sub>OUT</sub>, 5A, DC/DC µModule Regulator

#### **FEATURES**

- Complete Low EMI Switch Mode Power Supply

- EN55022 Class B Compliant

- Wide Input Voltage Range: 5V to 36V

- 3.3V to 15V Output Voltage Range

- 5A DC, 7A Peak Output Current

- Low Input and Output Referred Noise

- Output Voltage Tracking and Margining

- Power Good Tracks with Margining

- PLL Frequency Synchronization

- ±1.5% Set Point Accuracy

- Current Foldback Protection (Disabled at Start-Up)

- Parallel/Current Sharing

- Ultrafast Transient Response

- Current Mode Control

- Programmable Soft-Start

- Output Overvoltage Protection

- -55°C to 125°C Operating Temperature Range (LTM4612MPV)

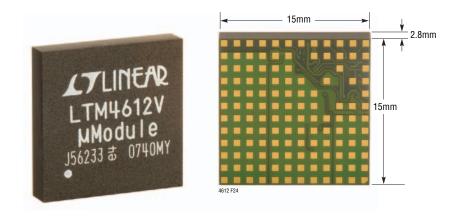

- Small Surface Mount Footprint, Low Profile (15mm × 15mm × 2.8mm) LGA Package

### **APPLICATIONS**

- Telecom and Networking Equipment

- Industrial and Avionic Equipment

- RF Systems

### DESCRIPTION

The LTM®4612 is a EN55022 Class B certified high voltage input and output, 5A switching mode DC/DC power supply. Included in the package are the switching controller, power FETs, inductor and all support components. Operating over an input voltage range of 5V to 36V, the LTM4612 supports an output voltage range of 3.3V to 15V, set by a single resistor. Only bulk input and output capacitors are needed to finish the design.

High switching frequency and an adaptive on-time current mode architecture enables a very fast transient response to line and load changes without sacrificing stability.

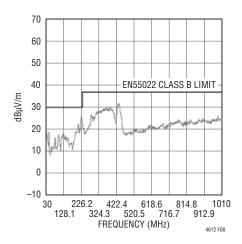

The onboard input filter and noise cancellation circuits achieve low noise coupling, thus effectively reducing the electromagnetic interference (EMI)—see Figures 4 and 8. Furthermore, the DC/DC  $\mu$ Module® regulator can be synchronized with an external clock to reduce undesirable frequency harmonics and allow PolyPhase® operation for high load currents.

The LTM4612 is offered in a space saving and thermally enhanced  $15\text{mm} \times 15\text{mm} \times 2.8\text{mm}$  LGA package, which enables utilization of unused space on the bottom of PC boards for high density point-of-load regulation. The LTM4612 is Pb-free and RoHS compliant.

$m{\mathcal{L}}$ , LT, LTC, LTM, Linear Technology, the Linear logo, PolyPhase and  $\mu$ Module are registered trademarks and LTpowerCAD is a trademark of Linear Technology Corporation. All other trademarks are the property of their respective owners.

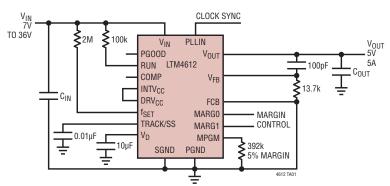

## TYPICAL APPLICATION

5V/5A Ultralow Noise µModule with 7V to 36V Input

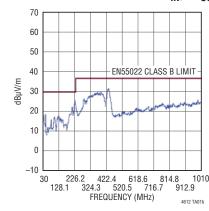

#### Radiated Emission Scan at 24V<sub>IN</sub>, 5V<sub>OUT</sub>/5A

### **ABSOLUTE MAXIMUM RATINGS**

#### (Note 1)

| (11010 1)                             |                                      |

|---------------------------------------|--------------------------------------|

| INTV <sub>CC.</sub> DRV <sub>CC</sub> | 0.3V to 6V                           |

| V <sub>OUT</sub>                      |                                      |

| PLLIN, FCB, TRACK/SS, MPGM, I         | MARG0,                               |

| MARG1, PGOOD                          | -0.3V to INTV <sub>CC</sub> + $0.3V$ |

| RUN                                   | 0.3V to 5V                           |

| V <sub>FB</sub> , COMP                |                                      |

| V <sub>IN</sub> , V <sub>D</sub>      | 0.3V to 36V                          |

| Internal Operating Temperature R      | ange (Note 2)                        |

| E and I Grades                        |                                      |

| MP Grade                              | 55°C to 125°C                        |

| Junction Temperature                  | 125°C                                |

| Storage Temperature Range             | 55°C to 125°C                        |

|                                       |                                      |

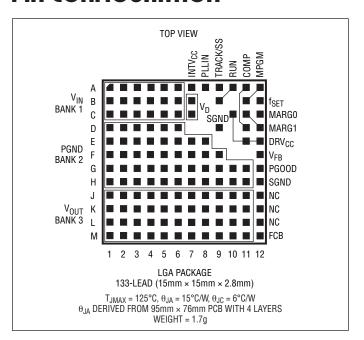

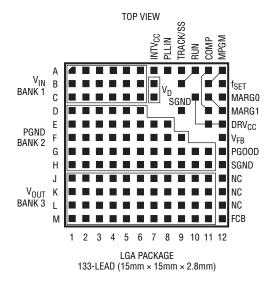

### PIN CONFIGURATION

## ORDER INFORMATION

| LEAD FREE FINISH | TRAY           | PART MARKING* | PACKAGE DESCRIPTION                | TEMPERATURE RANGE |

|------------------|----------------|---------------|------------------------------------|-------------------|

| LTM4612EV#PBF    | LTM4612EV#PBF  | LTM4612V      | 133-Lead (15mm × 15mm × 2.8mm) LGA | -40°C to 125°C    |

| LTM4612IV#PBF    | LTM4612IV#PBF  | LTM4612V      | 133-Lead (15mm × 15mm × 2.8mm) LGA | -40°C to 125°C    |

| LTM4612MPV#PBF   | LTM4612MPV#PBF | LTM4612MPV    | 133-Lead (15mm × 15mm × 2.8mm) LGA | -55°C to 125°C    |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container. For more information on lead free part marking, go to: http://www.linear.com/leadfree/

This product is only offered in trays. For more information go to: http://www.linear.com/packaging/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified internal operating temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ , $V_{IN} = 24V$ , unless otherwise noted (Note 2). Per Typical Application (front page) configuration.

| SYMBOL                   | PARAMETER                        | CONDITIONS                                                                                                                                                                       |   | MIN            | TYP            | MAX            | UNITS  |

|--------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----------------|----------------|----------------|--------|

| V <sub>IN(DC)</sub>      | Input DC Voltage                 |                                                                                                                                                                                  | • | 5              |                | 36             | V      |

| V <sub>OUT(DC)</sub>     | Output Voltage                   | $C_{IN} = 10 \mu F \times 3$ , $C_{OUT} = 300 \mu F$ ; $FCB = 0$<br>$V_{IN} = 24 V$ , $V_{OUT} = 12 V$ , $I_{OUT} = 0 A$<br>$V_{IN} = 36 V$ , $V_{OUT} = 12 V$ , $I_{OUT} = 0 A$ | • | 11.83<br>11.83 | 12.07<br>12.07 | 12.31<br>12.31 | V      |

| Input Specificati        | ions                             |                                                                                                                                                                                  |   |                |                |                |        |

| V <sub>IN(UVLO)</sub>    | Undervoltage Lockout Threshold   | I <sub>OUT</sub> = 0A                                                                                                                                                            |   |                | 3.2            | 4.8            | V      |

| I <sub>INRUSH(VIN)</sub> | Input Inrush Current at Start-Up | $I_{OUT}$ = 0A; $C_{IN}$ = 10 $\mu$ F × 2, $C_{OUT}$ = 200 $\mu$ F; $V_{OUT}$ = 12V $V_{IN}$ = 24V $V_{IN}$ = 36V                                                                |   |                | 0.6<br>0.7     |                | A<br>A |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified internal operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ,  $V_{IN} = 24V$ , unless otherwise noted (Note 2). Per Typical Application (front page) configuration.

| SYMBOL                                 | PARAMETER                             | CONDITIONS                                                                                                                                                                                                                                                                                                                              |   | MIN   | TYP            | MAX        | UNITS             |

|----------------------------------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-------|----------------|------------|-------------------|

| I <sub>Q(VIN)</sub>                    | Input Supply Bias Current             | $V_{\text{IN}}$ = 36V, $V_{\text{OUT}}$ = 12V, Switching Continuous $V_{\text{IN}}$ = 24V, $V_{\text{OUT}}$ = 12V, Switching Continuous Shutdown, RUN = 0, $V_{\text{IN}}$ = 36V                                                                                                                                                        |   |       | 57<br>48<br>50 |            | mA<br>mA<br>μA    |

| I <sub>S(VIN)</sub>                    | Input Supply Current                  | $V_{IN} = 36V$ , $V_{OUT} = 12V$ , $I_{OUT} = 5A$<br>$V_{IN} = 24V$ , $V_{OUT} = 12V$ , $I_{OUT} = 5A$                                                                                                                                                                                                                                  |   |       | 1.85<br>2.72   |            | A<br>A            |

| V <sub>INTVCC</sub>                    | Internal V <sub>CC</sub> Voltage      | V <sub>IN</sub> = 36V, RUN > 2V, I <sub>OUT</sub> = 0A                                                                                                                                                                                                                                                                                  |   | 4.7   | 5              | 5.3        | V                 |

| Output Specifica                       | tions                                 |                                                                                                                                                                                                                                                                                                                                         |   |       |                |            |                   |

| I <sub>OUT(DC)</sub>                   | Output Continuous Current Range       | V <sub>IN</sub> = 24V, V <sub>OUT</sub> = 12V (Note 4)                                                                                                                                                                                                                                                                                  |   | 0     |                | 5          | А                 |

| $\frac{\Delta V_{OUT(LINE)}}{V_{OUT}}$ | Line Regulation Accuracy              | $V_{OUT}$ = 12V, FCB = 0V, $V_{IN}$ = 22V to 36V, $I_{OUT}$ = 0A                                                                                                                                                                                                                                                                        | • |       | 0.05           | 0.3        | %                 |

| $\frac{\Delta V_{OUT(LOAD)}}{V_{OUT}}$ | Load Regulation Accuracy              | $V_{OUT}$ = 12V, FCB = 0V, $I_{OUT}$ = 0A to 5A (Note 4) $V_{IN}$ = 36V $V_{IN}$ = 24V                                                                                                                                                                                                                                                  | • |       | 0.3<br>0.3     | 0.6<br>0.6 | %<br>%            |

| V <sub>IN(AC)</sub>                    | Input Ripple Voltage                  | $\label{eq:loss_section} \begin{split} I_{OUT} &= 0\text{A}, \\ C_{IN} &= 2 \times 10 \mu\text{F X5R Ceramic and } 1 \times 100 \mu\text{F} \\ \text{Electrolytic, } 1 \times 10 \mu\text{F X5R Ceramic on } V_D \text{ Pins} \\ V_{IN} &= 24\text{V, } V_{OUT} = 5\text{V} \\ V_{IN} &= 24\text{V, } V_{OUT} = 12\text{V} \end{split}$ |   |       | 7.2<br>3.4     |            | mV <sub>P-P</sub> |

| V <sub>OUT(AC)</sub>                   | Output Ripple Voltage                 | $I_{OUT} = 0A,$<br>$C_{OUT} = 2 \times 22 \mu F, 2 \times 47 \mu F X5R$ Ceramic<br>$V_{IN} = 24V, V_{OUT} = 5V$<br>$V_{IN} = 24V, V_{OUT} = 12V$                                                                                                                                                                                        |   |       | 17.5<br>12.5   |            | mV <sub>P-P</sub> |

| $f_S$                                  | Output Ripple Voltage Frequency       | $I_{OUT} = 1A$ , $V_{IN} = 24V$ , $V_{OUT} = 12V$                                                                                                                                                                                                                                                                                       |   |       | 940            |            | kHz               |

| $\Delta V_{OUT(START)}$                | Turn-On Overshoot,<br>TRACK/SS = 10nF | $C_{OUT} = 200 \mu F, V_{OUT} = 12 V, I_{OUT} = 0 A$<br>$V_{IN} = 36 V$<br>$V_{IN} = 24 V$                                                                                                                                                                                                                                              |   |       | 20<br>20       |            | mV<br>mV          |

| tstart                                 | Turn-On Time, TRACK/SS = Open         | C <sub>OUT</sub> = 300μF, V <sub>OUT</sub> = 12V, I <sub>OUT</sub> = 1A<br>Resistive Load<br>V <sub>IN</sub> = 36V<br>V <sub>IN</sub> = 24V                                                                                                                                                                                             |   |       | 0.5<br>0.5     |            | ms<br>ms          |

| $\Delta V_{OUT(LS)}$                   | Peak Deviation for Dynamic Load       | Load: 0% to 50% to 0% of Full Load<br>C <sub>OUT</sub> = 2 × 22µF Ceramic, 150µF Bulk<br>V <sub>IN</sub> = 24V, V <sub>OUT</sub> = 12V                                                                                                                                                                                                  |   |       | 153            |            | mV                |

| t <sub>SETTLE</sub>                    | Settling Time for Dynamic Load Step   | Load: 0% to 50% to 0% of Full Load, V <sub>IN</sub> = 24V                                                                                                                                                                                                                                                                               |   |       | 37             |            | μs                |

| I <sub>OUT(PK)</sub>                   | Output Current Limit                  | $C_{OUT} = 200 \mu F$<br>$V_{IN} = 36 V$ , $V_{OUT} = 12 V$<br>$V_{IN} = 24 V$ , $V_{OUT} = 12 V$                                                                                                                                                                                                                                       |   |       | 9<br>9         |            | A<br>A            |

| Control Section                        |                                       |                                                                                                                                                                                                                                                                                                                                         |   |       |                |            |                   |

| $V_{FB}$                               | Voltage at V <sub>FB</sub> Pin        | I <sub>OUT</sub> = 0A, V <sub>OUT</sub> = 12V                                                                                                                                                                                                                                                                                           | • | 0.591 | 0.6            | 0.609      | V                 |

| V <sub>RUN</sub>                       | RUN Pin On/Off Threshold              |                                                                                                                                                                                                                                                                                                                                         |   | 1     | 1.5            | 1.9        | V                 |

| I <sub>SS/TRACK</sub>                  | Soft-Start Charging Current           | V <sub>SS/TRACK</sub> = 0V                                                                                                                                                                                                                                                                                                              |   | -1    | -1.5           | -2         | μА                |

| V <sub>FCB</sub>                       | Forced Continuous Threshold           |                                                                                                                                                                                                                                                                                                                                         |   | 0.57  | 0.6            | 0.63       | V                 |

| I <sub>FCB</sub>                       | Forced Continuous Pin Current         | V <sub>FCB</sub> = 0V                                                                                                                                                                                                                                                                                                                   |   |       | -1             | -2         | μА                |

| t <sub>ON(MIN)</sub>                   | Minimum On-Time                       | (Note 3)                                                                                                                                                                                                                                                                                                                                |   |       | 50             | 100        | ns                |

| t <sub>OFF(MIN)</sub>                  | Minimum Off-Time                      | (Note 3)                                                                                                                                                                                                                                                                                                                                |   |       | 250            | 400        | ns                |

| R <sub>PLLIN</sub>                     | PLLIN Input Resistor                  |                                                                                                                                                                                                                                                                                                                                         |   |       | 50             |            | kΩ                |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified internal operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$ ,  $V_{IN} = 24V$ , unless otherwise noted (Note 2). Per Typical Application (front page) configuration.

| SYMBOL                                  | PARAMETER                                                  | CONDITIONS                                    | MIN  | TYP  | MAX   | UNITS |

|-----------------------------------------|------------------------------------------------------------|-----------------------------------------------|------|------|-------|-------|

| I <sub>DRVCC</sub>                      | Current into DRV <sub>CC</sub> Pin                         | V <sub>OUT</sub> = 12V, I <sub>OUT</sub> = 1A |      | 22   | 30    | mA    |

| R <sub>FBHI</sub>                       | Resistor Between V <sub>OUT</sub> and V <sub>FB</sub> Pins |                                               | 99.5 | 100  | 100.5 | kΩ    |

| $\overline{V_{MPGM}}$                   | Margin Reference Voltage                                   |                                               |      | 1.18 |       | V     |

| V <sub>MARG0</sub> , V <sub>MARG1</sub> | MARG0, MARG1 Voltage Thresholds                            |                                               |      | 1.4  |       | V     |

| PG00D                                   |                                                            |                                               |      |      |       |       |

| $\Delta V_{FBH}$                        | PGOOD Upper Threshold                                      | V <sub>FB</sub> Rising                        | 7    | 10   | 13    | %     |

| $\Delta V_{FBL}$                        | PGOOD Lower Threshold                                      | V <sub>FB</sub> Falling                       | -7   | -10  | -13   | %     |

| $\Delta V_{FB(HYS)}$                    | PGOOD Hysteresis                                           | V <sub>FB</sub> Returning                     |      | 1.5  |       | %     |

| $\overline{V_{PGL}}$                    | PGOOD Low Voltage                                          | I <sub>PGOOD</sub> = 5mA                      |      | 0.15 | 0.4   | V     |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTM4612E is guaranteed to meet performance specifications over the 0°C to 125°C internal operating temperature range. Specifications over the -40°C to 125°C internal operating temperature range are assured by design, characterization and correlation with statistical process controls. The LTM4612I is guaranteed to meet specifications over the

-40°C to 125°C internal operating temperature range. The LTM4612MP is guaranteed and tested over the full –55°C to 125°C internal operating temperature range. Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal resistance and other environmental factors.

Note 3: 100% tested at die level only.

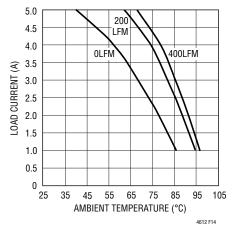

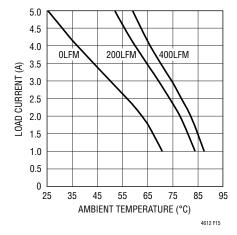

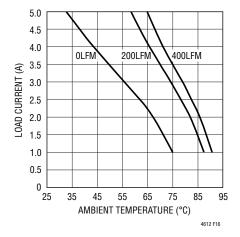

Note 4: See the Output Current Derating curves for different  $V_{\text{IN}},\,V_{\text{OUT}}$  and  $T_{\text{A}}.$

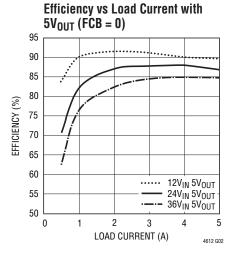

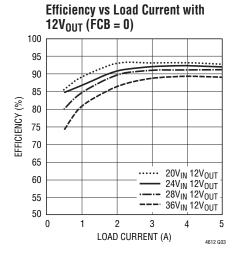

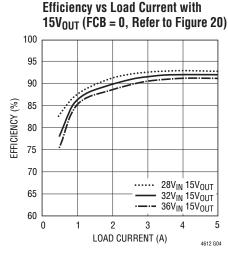

## TYPICAL PERFORMANCE CHARACTERISTICS (Refer to Figure 18)

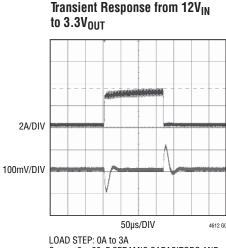

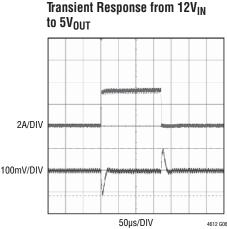

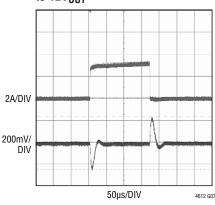

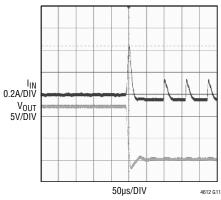

LOAD STEP: 0A to 3A  $C_{OUT} = 2 \times 22 \mu F$  CERAMIC CAPACITORS AND  $2 \times 47 \mu F$  CERAMIC CAPACITORS

LOAD STEP: 0A to 3A  $$C_{OUT}=2\times22\mu F$  CERAMIC CAPACITORS AND  $2\times47\mu F$  CERAMIC CAPACITORS

## Transient Response from 24 $V_{IN}$ to 12 $V_{OUT}$

LOAD STEP: 0A to 3A  $C_{OUT}$  =  $2\times22\mu F$  CERAMIC CAPACITORS AND  $2\times47\mu F$  CERAMIC CAPACITORS

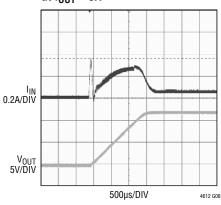

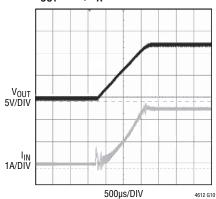

## Start-Up with 24V<sub>IN</sub> to 12V<sub>OUT</sub> at I<sub>OUT</sub> = 0A

SOFT-START CAPACITOR: 3.9nf  $C_{IN}=3\times10\mu F$  CERAMIC CAPACITORS AND  $1\times47\mu F$  OSCON CAPACITOR

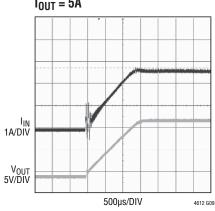

## Start-Up with $24V_{IN}$ to $12V_{OUT}$ at $I_{OUT} = 5A$

SOFT-START CAPACITOR: 3.9nf CIN =  $3 \times 10 \mu F$  CERAMIC CAPACITORS AND  $1 \times 47 \mu F$  OSCON CAPACITOR

## TYPICAL PERFORMANCE CHARACTERISTICS

## Start-Up with 24V $_{IN}$ to 12V $_{OUT}$ at $I_{OUT}$ = 5A, $T_A$ = -55°C

SOFT-START CAPACITOR: 3.9nf  $C_{IN}=3\times10\mu\text{F}$  CERAMIC CAPACITORS AND  $1\times47\mu\text{F}$  OSCON CAPACITOR

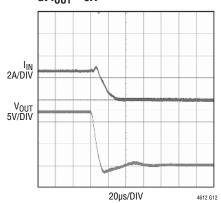

## Short-Circuit with 24V $_{IN}$ to 12V $_{OUT}$ at I $_{OUT}$ = 0A

$C_{OUT}$  =  $2\times22\mu\text{F}$  CERAMIC CAPACITORS AND  $2\times47\mu\text{F}$  CERAMIC CAPACITORS

## Short-Circuit with 24V $_{IN}$ to 12V $_{OUT}$ at $I_{OUT}$ = 5A

$C_{OUT}$  = 2 × 22µF CERAMIC CAPACITORS AND 2 × 47µF CERAMIC CAPACITORS

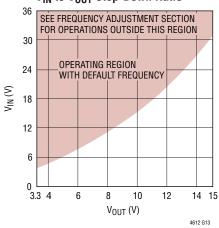

#### V<sub>IN</sub> to V<sub>OUT</sub> Step-Down Ratio

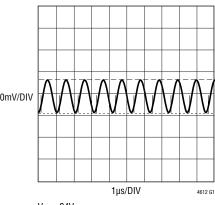

#### Input Ripple

$V_{IN}$  = 24V  $V_{OUT}$  = 12V AT 5A RESISTIVE LOAD  $C_{IN}$  = 3  $\times$  10 $\mu F$  50V CERAMIC 1  $\times$  100 $\mu F$  BULK

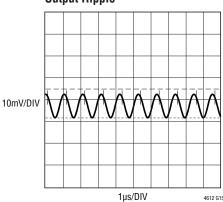

#### **Output Ripple**

$V_{IN}=24V$   $V_{OUT}=12V$  AT 5A RESISTIVE LOAD  $C_{OUT}=2\times22\mu F$  16V CERAMIC AND  $2\times47\mu F$  16V CERAMIC

## PIN FUNCTIONS (See Package Description for Pin Assignments)

$V_{IN}$  (Bank 1): Power Input Pins. Apply input voltage between these pins and PGND pins. Recommend placing input decoupling capacitance directly between  $V_{IN}$  pins and PGND pins.

**PGND (Bank 2):** Power Ground Pins for Both Input and Output Returns.

**V<sub>OUT</sub>** (**Bank 3**): Power Output Pins. Apply output load between these pins and PGND pins. Recommend placing output decoupling capacitance directly between these pins and GND pins (see the LTM4612 Pin Configuration below).

$V_D$  (Pins B7, C7): Top FET Drain Pins. Add more capacitors between  $V_D$  and ground to handle the input RMS current and reduce the input ripple further.

**DRV**<sub>CC</sub> (**Pins C10**, **E11**, **E12**): These pins normally connect to INTV<sub>CC</sub> for powering the internal MOSFET drivers. They can be biased up to 6V from an external supply with about 50mA capability. This improves efficiency at higher input voltages by reducing power dissipation in the module.

**INTV<sub>CC</sub> (Pin A7):** This pin is for additional decoupling of the 5V internal regulator.

**PLLIN (Pin A8):** External Clock Synchronization Input to the Phase Detector. This pin is internally terminated to SGND with a 50k resistor. Apply a clock above 2V and below INTV $_{CC}$ . See the Applications Information section.

**FCB (Pin M12):** Forced Continuous Input. Connect this pin to SGND to force continuous synchronization operation at low load, to  $INTV_{CC}$  to enable discontinuous mode operation at low load or to a resistive divider from a secondary output when using a secondary winding.

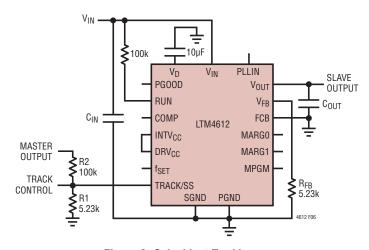

**TRACK/SS (Pin A9):** Output Voltage Tracking and Soft-Start Pin. When the module is configured as a master output, then a soft-start capacitor is placed on this pin to ground to control the master ramp rate. A soft-start capacitor can be used for soft-start turn-on as a standalone regulator. Slave operation is performed by putting a resistor divider from the master output to the ground, and connecting the center point of the divider to this pin. See the Applications Information section.

MPGM (Pins A12, B11): Programmable Margining Input. A resistor from these pins to ground sets a current that is equal to 1.18V/R. This current multiplied by 10k will equal a value in millivolts that is a percentage of the 0.6V reference voltage. May be left open if margining is not desired. See the Applications Information section. To parallel LTM4612s, each requires an individual MPGM resistor. Do not tie MPGM pins together.

**f<sub>SET</sub>** (**Pin B12**): Frequency Set Internally to ~850kHz to 900kHz at 12V Output. An external resistor can be placed from this pin to ground to increase frequency. See the Applications Information section for frequency adjustment.

LTM4612 Pin Configuration

#### PIN FUNCTIONS

$V_{FB}$  (Pin F12): The Negative Input of the Error Amplifier. Internally, this pin is connected to  $V_{OUT}$  with a 100k 0.5% precision resistor. Different output voltages can be programmed with an additional resistor between the  $V_{FB}$  and SGND pins. See the Applications Information section.

**MARGO (Pin C12):** LSB Logic Input for the Margining Function. Together with the MARG1 pin, the MARG0 pin will determine if a margin high, margin low, or no margin state is applied. The pin has an internal pull-down resistor of 50k. See the Applications Information section.

**MARG1 (Pins C11, D12):** MSB Logic Input for the Margining Function. Together with the MARG0 pin, the MARG1 pin will determine if a margin high, margin low, or no margin state is applied. The pins have an internal pull-down resistor of 50k. See the Applications Information section.

**SGND (Pins D9, H12):** Signal Ground Pins. These pins connect to PGND at output capacitor point.

**COMP** (Pins A11, D11): Current Control Threshold and Error Amplifier Compensation Point. The current comparator threshold increases with this control voltage. The voltage ranges from 0V to 2.4V with 0.7V corresponding to zero sense voltage (zero current).

**PGOOD (Pin G12):** Output Voltage Power Good Indicator. Open-drain logic output that is pulled to ground when the output voltage is not within  $\pm 10\%$  of the regulation point, after a 25µs power bad mask timer expires.

**RUN (Pins A10, B9):** Run Control Pins. A voltage above 1.9V will turn on the module, and below 1V will turn off the module. A programmable UVLO function can be accomplished with a resistor from  $V_{\text{IN}}$  to this pin that is has a 5.1V zener to ground. Maximum pin voltage is 5V.

NC (Pins J12, K12, L12): No Connect Pins. Leave floating.

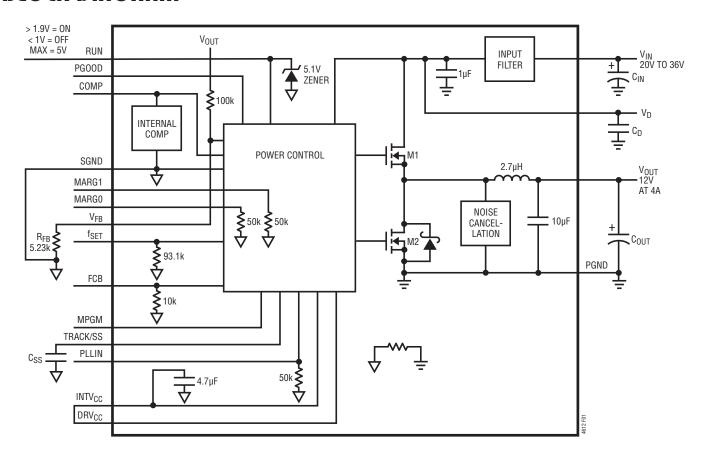

## **BLOCK DIAGRAM**

Figure 1. Simplified Block Diagram

## **DECOUPLING REQUIREMENTS** Specifications are at $T_A = 25$ °C. Use Figure 1 configuration.

| SYMBOL           | PARAMETER                                                                                    | CONDITIONS            | MIN | TYP | MAX | UNITS |

|------------------|----------------------------------------------------------------------------------------------|-----------------------|-----|-----|-----|-------|

| C <sub>IN</sub>  | External Input Capacitor Requirement (V <sub>IN</sub> = 20V to 36V, V <sub>OUT</sub> = 12V)  | I <sub>OUT</sub> = 4A | 20  |     |     | μF    |

| C <sub>OUT</sub> | External Output Capacitor Requirement (V <sub>IN</sub> = 20V to 36V, V <sub>OUT</sub> = 12V) | I <sub>OUT</sub> = 4A | 100 | 150 |     | μF    |

#### **OPERATION**

#### **Power Module Description**

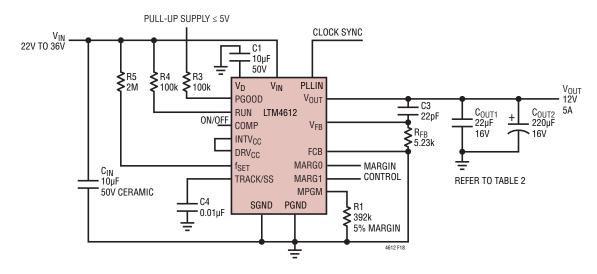

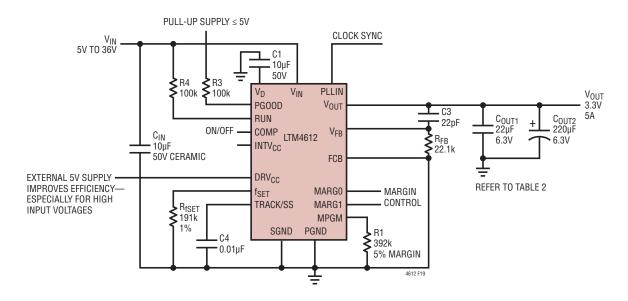

The LTM4612 is a standalone nonisolated switching mode DC/DC power supply. It can deliver 5A of DC output current with some external input and output capacitors. This module provides precisely regulated output voltage programmable via one external resistor from  $3.3V_{DC}$  to  $15V_{DC}$  over a 5V to 36V wide input voltage. The typical application schematic is shown in Figure 18.

The LTM4612 has an integrated constant on-time current mode regulator, ultralow  $R_{DS(0N)}$  FETs with fast switching speed and integrated Schottky diodes. The typical switching frequency is 850kHz at full load at 12V output. With current mode control and internal feedback loop compensation, the LTM4612 module has sufficient stability margins and good transient performance under a wide range of operating conditions and with a wide range of output capacitors, even all ceramic output capacitors.

Current mode control provides cycle-by-cycle fast current limiting. Moreover, foldback current limiting is provided in an overcurrent condition while  $V_{FB}$  drops. Internal overvoltage and undervoltage comparators pull the open-drain PGOOD output low if the output feedback voltage exits a  $\pm 10\%$  window around the regulation point. Furthermore, in an overvoltage condition, internal top FET M1 is turned off and bottom FET M2 is turned on and held on until the overvoltage condition clears.

Input filter and noise cancellation circuitry reduce the noise coupling to I/O sides, and ensure the electromagnetic interference (EMI) meets the limits of EN55022 Class B.

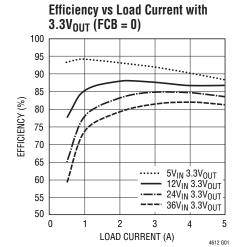

Pulling the RUN pin below 1V forces the controller into its shutdown state, turning off both M1 and M2. At light load currents, discontinuous mode (DCM) operation can be enabled to achieve higher efficiency compared to continuous mode (CCM) by setting FCB pin higher than 0.6V.

When the DRV<sub>CC</sub> pin is connected to INTV<sub>CC</sub>, an integrated 5V linear regulator powers the internal gate drivers. If a 5V external bias supply is applied on DRV<sub>CC</sub> pin, then an efficiency improvement will occur due to the reduced power loss in the internal linear regulator. This is especially true at higher input voltages.

The MPGM, MARGO, and MARG1 pins are used to support output voltage margining, where the percentage of margin is programmed by the MPGM pin, and the MARGO and MARG1 select margining. The PLLIN pin provides frequency synchronization of the device to an external clock. The TRACK/SS pin is used for power supply tracking and soft-start programming.

## APPLICATIONS INFORMATION

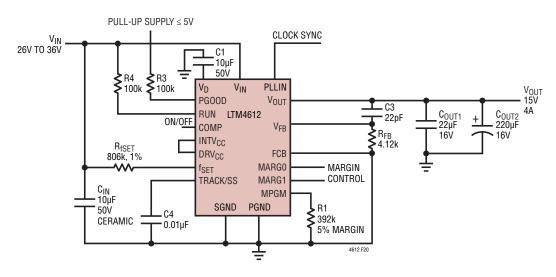

The typical LTM4612 application circuit is shown in Figure 18. External component selection is primarily determined by the maximum load current and output voltage. Refer to Table 2 for specific external capacitor requirements for a particular application.

### V<sub>IN</sub> to V<sub>OLIT</sub> Stepdown Ratios

There are restrictions in the maximum  $V_{IN}$  and  $V_{OUT}$  step down ratio that can be achieved for a given input voltage. These constraints are shown in the Typical Performance Characteristic curve labeled " $V_{IN}$  to  $V_{OUT}$  Step-Down Ratio." Note that additional thermal derating may be applied. See the Thermal Considerations and Output Current Derating section in this data sheet.

LINEAR

#### **Output Voltage Programming and Margining**

The PWM controller has an internal 0.6V reference voltage. As shown in the Block Diagram, a 100k internal feedback resistor connects the  $V_{OUT}$  and  $V_{FB}$  pins together. Adding a resistor,  $R_{FB}$ , from the  $V_{FB}$  pin to the SGND pin programs the output voltage.

$$V_{OUT} = 0.6V \bullet \frac{100k + R_{FB}}{R_{FB}}$$

or equivalently,

$$R_{FB} = \frac{100k}{\frac{V_{OUT}}{0.6V} - 1}$$

Table 1. Reg Standard 1% Resistor Values vs Volit

|                        | עו   |      |    |      |      | 001  |      |      |

|------------------------|------|------|----|------|------|------|------|------|

| V <sub>OUT</sub> (V)   | 3.3  | 5    | 6  | 8    | 10   | 12   | 14   | 15   |

| $R_{FB}$ ( $k\Omega$ ) | 22.1 | 13.7 | 11 | 8.06 | 6.34 | 5.23 | 4.42 | 4.12 |

The MPGM pin programs a current that when multiplied by an internal 10k resistor sets up the 0.6V reference ± offset for margining. A 1.18V reference divided by the

$R_{PGM}$  resistor on the MPGM pin programs the current. Calculate  $V_{OUT(MARGIN)}\colon$

$$V_{OUT(MARGIN)} = \frac{\%V_{OUT}}{100} \cdot V_{OUT}$$

Where  $V_{OUT}$  is the percentage of  $V_{OUT}$  to be margined, and  $V_{OUT(MARGIN)}$  is the margin quantity in volts:

$$R_{PGM} = \frac{V_{OUT}}{0.6V} \cdot \frac{1.18V}{V_{OUT(MARGIN)}} \cdot 10k$$

Where  $R_{PGM}$  is the resistor value to place on the MPGM pin to ground.

The output margining will be  $\pm$  margining of the value. This is controlled by the MARG0 and MARG1 pins. See the truth table below:

| MARG1 | MARGO | MODE        |

|-------|-------|-------------|

| LOW   | LOW   | NO MARGIN   |

| LOW   | HIGH  | MARGIN UP   |

| HIGH  | LOW   | MARGIN DOWN |

| HIGH  | HIGH  | NO MARGIN   |

Table 2. Output Voltage Response vs Component Matrix (Refer to Figure 20)

| TYPICAL MEASURED VALUE |

|------------------------|

|------------------------|

| ITT TONE INLAUGITED VALUE | THI TONE INLINOURLY VILLED     |         |                            |  |  |  |  |  |  |  |

|---------------------------|--------------------------------|---------|----------------------------|--|--|--|--|--|--|--|

| VENDORS                   | PART NUMBER                    | VENDORS | PART NUMBER                |  |  |  |  |  |  |  |

| Murata                    | GRM32ER61C476KEI5L (47μF, 16V) | Murata  | GRM32ER71H106K (10μF, 50V) |  |  |  |  |  |  |  |

| Murata                    | GRM32ER61C226KE20L (22µF, 16V) | TDK     | C3225X5RIC226M (22µF, 16V) |  |  |  |  |  |  |  |

| V <sub>OUT</sub><br>(V) | C <sub>IN</sub><br>(CERAMIC) | C <sub>IN</sub><br>(BULK) | C <sub>OUT1</sub><br>(CERAMIC) | C <sub>OUT2</sub><br>(BULK) | V <sub>IN</sub><br>(V) | DROOP<br>(mV) | PEAK-TO-<br>PEAK (mV) | RECOVERY<br>TIME (µs) | LOAD STEP<br>(A/µs) | $R_{FB}$ (k $\Omega$ ) |

|-------------------------|------------------------------|---------------------------|--------------------------------|-----------------------------|------------------------|---------------|-----------------------|-----------------------|---------------------|------------------------|

| 5                       | 2 × 10µF 50V                 | 100μF 50V                 | 2 × 22μF 16V                   | 150µF 25V                   | 12                     | 86            | 156                   | 26                    | 3                   | 13.7                   |

| 5                       | 2 × 10µF 50V                 | 100μF 50V                 | 4 × 47μF 16V                   | None                        | 12                     | 86            | 178                   | 14.8                  | 3                   | 13.7                   |

| 5                       | 2 × 10μF 50V                 | 100μF 50V                 | 2 × 22μF 16V                   | 150µF 25V                   | 24                     | 83            | 166                   | 27                    | 3                   | 13.7                   |

| 5                       | 2 × 10µF 50V                 | 100μF 50V                 | 4 × 47μF 16V                   | None                        | 24                     | 86            | 169                   | 14.8                  | 3                   | 13.7                   |

| 5                       | 2 × 10µF 50V                 | 100μF 50V                 | 2 × 22μF 16V                   | 150µF 25V                   | 36                     | 86            | 178                   | 25                    | 3                   | 13.7                   |

| 5                       | 2 × 10µF 50V                 | 100μF 50V                 | 4 × 47μF 16V                   | None                        | 36                     | 86            | 172                   | 15.2                  | 3                   | 13.7                   |

| 10                      | 2 × 10µF 50V                 | 100μF 50V                 | 2 × 22μF 16V                   | 150µF 25V                   | 24                     | 111           | 209                   | 30                    | 3                   | 6.34                   |

| 10                      | 2 × 10µF 50V                 | 100μF 50V                 | 4 × 47μF 16V                   | None                        | 24                     | 171           | 325                   | 35                    | 3                   | 6.34                   |

| 10                      | 2 × 10µF 50V                 | 100μF 50V                 | 2 × 22μF 16V                   | 150µF 25V                   | 36                     | 108           | 197                   | 35                    | 3                   | 6.34                   |

| 10                      | 2 × 10µF 50V                 | 100μF 50V                 | 4 × 47μF 16V                   | None                        | 36                     | 153           | 288                   | 39                    | 3                   | 6.34                   |

| 12                      | 2 × 10µF 50V                 | 100μF 50V                 | 2 × 22μF 16V                   | 150µF 25V                   | 24                     | 153           | 281                   | 37                    | 3                   | 5.23                   |

| 12                      | 2 × 10μF 50V                 | 100μF 50V                 | 4 × 47μF 16V                   | None                        | 36                     | 184           | 375                   | 34.4                  | 3                   | 5.23                   |

| 15                      | 2 × 10μF 50V                 | 100μF 50V                 | 2 × 22μF 16V                   | 150µF 25V                   | 28                     | 178           | 338                   | 70                    | 3                   | 4.12                   |

| 15                      | 2 × 10µF 50V                 | 100μF 50V                 | 4 × 47μF 16V                   | None                        | 36                     | 134           | 250                   | 70                    | 3                   | 4.12                   |

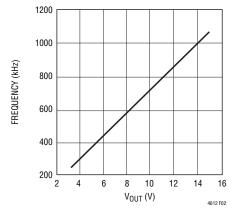

#### **Operating Frequency**

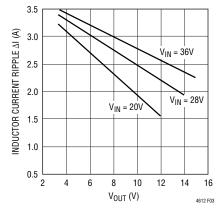

The operating frequency of the LTM4612 is optimized to achieve the compact package size and the minimum output ripple voltage while still providing high efficiency. As shown in Figure 2, the frequency is linearly increased with larger output voltages to keep the low output current ripple. Figure 3 shows the inductor current ripple  $\Delta I$  with different output voltages. In most applications, no additional frequency adjusting is required.

If lower output ripple is required, the operating frequency f can be increased by adding a resistor  $R_{fSET}$  between  $f_{SET}$  pin and SGND, as shown in Figure 19.

$$f = \frac{V_{OUT}}{1.5 \cdot 10^{-10} (R_{fSFT} || 93.1k)}$$

Figure 2. Operating Frequency vs Output Voltage

For output voltages more than 12V, the frequency can be higher than 1MHz, thus reducing the efficiency significantly. Additionally, the 500ns minimum off time (400ns + 100ns for margin) normally limits the operation when the input voltage is close to the output voltage. Therefore, it is recommended to lower the frequency in these conditions by connecting a resistor ( $R_{fSET}$ ) from the  $f_{SET}$  pin to  $V_{IN}$ , as shown in Figure 20.

$$f = \frac{V_{OUT}}{5 \cdot 10^{-11} \left( \frac{3 \cdot R_{fSET} \cdot 93.1k}{R_{fSET} - 2 \cdot 93.1k} \right)}$$

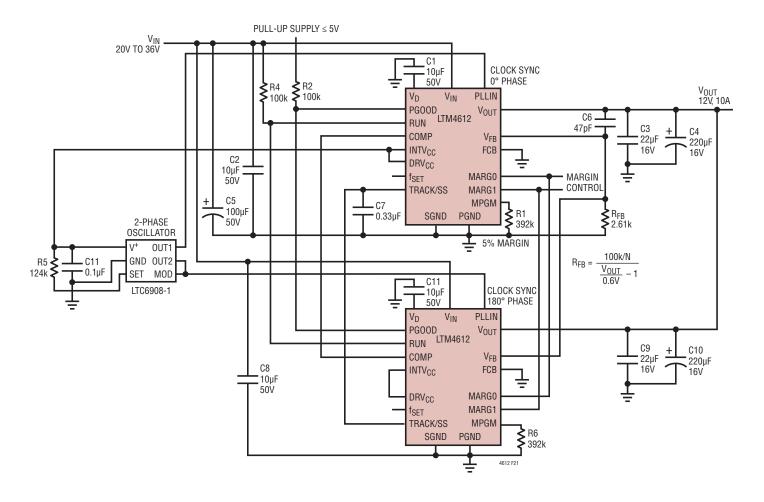

The load current can affect the frequency due to its constant on-time control. If constant frequency is a necessity, the PLLIN pin can be used to synchronize the frequency of the LTM4612 to an external clock, as shown in Figures 21 to 23.

Figure 3. Inductor Current Ripple vs Output Voltage

#### **Input Capacitors**

LTM4612 is designed to achieve the low input radiated EMI noise due to the fast switching of turn-on and turn-off. In the LTM4612, a high-frequency inductor is integrated into the input line for noise attenuation.  $V_D$  and  $V_{IN}$  pins are available for external input capacitors to form a high frequency  $\pi$  filter. As shown in Figure 18, the ceramic capacitor C1 on the  $V_D$  pins is used to handle most of the RMS current into the converter, so careful attention is needed for capacitor C1 selection.

For a buck converter, the switching duty cycle can be estimated as:

$$D = \frac{V_{OUT}}{V_{IN}}$$

Without considering the inductor current ripple, the RMS current of the input capacitor can be estimated as:

$$I_{\text{CIN(RMS)}} = \frac{I_{\text{OUT(MAX)}}}{\eta} \bullet \sqrt{D \bullet (1 - D)}$$

In this equation,  $\eta$  is the estimated efficiency of the power module. Note the capacitor ripple current ratings are often based on temperature and hours of life. This makes it advisable to properly derate the input capacitor, or choose a capacitor rated at a higher temperature than required. Always contact the capacitor manufacturer for derating requirements.

In a typical 5A output application, one very low ESR, X5R or X7R,  $10\mu\text{F}$  ceramic capacitor is recommended for C1. This decoupling capacitor should be placed directly adjacent to the module  $V_D$  pins in the PCB layout to minimize the trace inductance and high frequency AC noise. Each  $10\mu\text{F}$  ceramic is typically good for 2A to 3A of RMS ripple current. Refer to your ceramics capacitor catalog for the RMS current ratings.

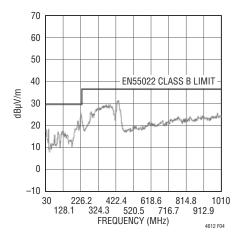

To attenuate the high frequency noise, extra input capacitors should be connected to the  $V_{\text{IN}}$  pads and placed before the high frequency inductor to form the  $\pi$  filter. One of these low ESR ceramic input capacitors is recommended to be close to the connection into the system board. A large bulk  $100\mu\text{F}$  capacitor is only needed if the input source impedance is compromised by long inductive leads or traces. Figure 4 shows the radiated EMI test results to meet the EN55022 Class B limit. For different applications, input capacitance may be varied to meet different radiated EMI limits.

Figure 4. Radiated Emission Scan with  $24V_{IN}$  to  $5V_{OUT}$  at 5A (2  $\times$  10 $\mu$ F Ceramic Capacitors on  $V_{IN}$  Pads and 1  $\times$  10 $\mu$ F Ceramic Capacitor on  $V_D$  Pads)

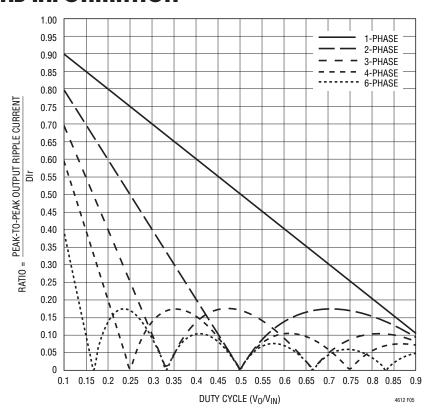

Figure 5. Normalized Output Ripple Current vs Duty Cycle, DIr =  $V_0T/L_1$

#### **Output Capacitors**

The LTM4612 is designed for low output voltage ripple. The bulk output capacitors defined as  $C_{OUT}$  are chosen with low enough effective series resistance (ESR) to meet the output voltage ripple and transient requirements.  $C_{OUT}$  can be low ESR tantalum capacitor, low ESR polymer capacitor or ceramic capacitor. The typical capacitance is  $150\mu F$  if all ceramic output capacitors are used. Additional output filtering may be required by the system designer, if further reduction of output ripple or dynamic transient spike is required. Table 2 shows a matrix of different output voltages and output capacitors to minimize the voltage droop and overshoot during a  $2A/\mu s$  transient. The table optimizes total equivalent ESR and total bulk capacitance to maximize transient performance.

Multiphase operation with multiple LTM4612 devices in parallel will also lower the effective output ripple current due to the phase interleaving operation. Refer to Figure 5 for the normalized output ripple current versus the duty

cycle. Figure 5 provides a ratio of peak-to-peak output ripple current to the inductor ripple current as functions of duty cycle and the number of paralleled phases. Pick the corresponding duty cycle and the number of phases to get the correct output ripple current value. For example, each phase's inductor ripple current DIr at zero duty cycle is  $\sim$ 4.3A for a 36V to 12V design. The duty cycle is about 0.33. The 2-phase curve has a ratio of  $\sim$ 0.33 for a duty cycle of 0.33. This 0.33 ratio of output ripple current to the inductor ripple current DIr at 4.3A equals 1.4A of the output ripple current ( $\Delta$ I<sub>1</sub>).

The output voltage ripple has two components that are related to the amount of bulk capacitance and effective series resistance (ESR) of the output bulk capacitance. The equation is:

$$\Delta V_{OUT(P-P)} \approx \left(\frac{\Delta I_L}{8 \cdot f \cdot N \cdot C_{OUT}}\right) + ESR \cdot \Delta I_L$$

where f is the frequency and N is the number of paralleled phases.

#### Fault Conditions: Current Limit and Overcurrent Foldback

LTM4612 has a current mode controller, which inherently limits the cycle-by-cycle inductor current not only in steady state operation, but also in transient.

To further limit current in the event of an overload condition, the LTM4612 provides foldback current limiting. If the output voltage falls by more than 50%, then the maximum output current is progressively lowered to about one sixth of its full current limit value.

#### **Soft-Start and Tracking**

The TRACK/SS pin provides a means to either soft-start the regulator or track it to a different power supply. A capacitor on this pin will program the ramp rate of the output voltage. A 1.5µA current source will charge up the external soft-start capacitor to 80% of the 0.6V internal voltage reference plus or minus any margin delta. This will control the ramp of the internal reference and the output voltage. The total soft-start time can be calculated as:

$$t_{SOFTSTART} \approx 0.8 \cdot (0.6 \pm 0.6 \cdot V_{OUT} \text{ Margin \%}) \cdot \frac{C_{SS}}{1.5 \mu A}$$

If the RUN pin falls below 2.5V, then the soft-start pin is reset to allow for the proper soft-start again. Current foldback and force continuous mode are disabled during the soft-start process. The soft-start function can also be used to control the output ramp rising time, so that another regulator can be easily tracked.

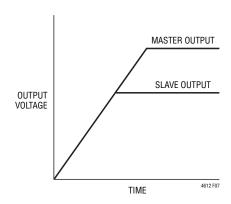

Figure 6. Coincident Tracking

#### **Output Voltage Tracking**

Output voltage tracking can be programmed externally using the TRACK/SS pin. The output can be tracked up and down with another regulator. Figure 6 shows an example of coincident tracking where the master regulator's output is divided down with an external resistor divider that is the same as the slave regulator's feedback divider. Ratiometric modes of tracking can be achieved by selecting different resistor values to change the output tracking ratio. The master output must be greater than the slave output for the tracking to work. Figure 7 shows the coincident output tracking.

Tracking can be achieved by a few simple calculations and the slew rate value applied to the master's TRACK pin. The TRACK pin has a control range from 0 to 0.6V. The master's TRACK pin slew rate is directly equal to the master's output slew rate in Volts/Time. The equation:

$$\frac{MR}{SR} \cdot 100k = R2$$

where MR is the master's output slew rate and SR is the slave's output slew rate in Volts/Time. When coincident tracking is desired, then MR and SR are equal, thus R2 is equal the 100k. R1 is derived from equation:

$$R1 = \frac{0.6V}{\frac{V_{FB}}{100k} + \frac{V_{FB}}{R_{FB}} - \frac{V_{TRACK}}{R2}}$$

Figure 7. Coincident Output Tracking

4612fl

where  $V_{FB}$  is the feedback voltage reference of the regulator, and  $V_{TRACK}$  is 0.6V. Since R2 is equal to the 100k top feedback resistor of the slave regulator in equal slew rate or coincident tracking, then R1 is equal to  $R_{FB}$  with  $V_{FB} = V_{TRACK}$ . Therefore R2 = 100k, and R1 = 5.23k in Figure 6.

In ratiometric tracking, a different slew rate maybe desired for the slave regulator. R2 can be solved for when SR is slower than MR. Make sure that the slave supply slew rate is chosen to be fast enough so that the slave output voltage will reach it final value before the master output.

For example, MR = 1.5V/1ms, and SR = 1.2V/1ms. Then R2 = 125k. Solve for R1 to equal to 5.18k.

Each of the TRACK pins will have the  $1.5\mu A$  current source on when a resistive divider is used to implement tracking on that specific channel. This will impose an offset on the TRACK pin input. Smaller values resistors with the same ratios as the resistor values calculated from the above equation can be used. For example, where the 100k is used then a 10k can be used to reduce the TRACK pin offset to a negligible value.

#### **RUN Enable**

The RUN pin is used to enable the power module. The pin has an internal 5.1V Zener to ground. The pin can be driven with 5V logic levels.

The RUN pin can also be used as an undervoltage lockout (UVLO) function by connecting a resistor divider from the input supply to the RUN pin. The equation for UVLO threshold:

$$V_{UVLO} = \frac{R_A + R_B}{R_B} \bullet 1.5V$$

where  $R_{\mbox{\scriptsize A}}$  is the top resistor, and  $R_{\mbox{\scriptsize B}}$  is the bottom resistor.

#### **Power Good**

The PGOOD pin is an open-drain pin that can be used to monitor valid output voltage regulation. This pin monitors a  $\pm 10\%$  window around the regulation point, and tracks with margining.

#### **COMP Pin**

The pin is the external compensation pin. The module has already been internally compensated for most output voltages. LTpowerCAD™ from Linear Technology is available for more control loop optimization.

#### **FCB Pin**

The FCB pin determines whether the bottom MOSFET remains on when current reverses in the inductor. Tying this pin above its 0.6V threshold enables discontinuous operation where the bottom MOSFET turns off when inductor current reverses. FCB pin below the 0.6V threshold forces continuous synchronous operation, allowing current to reverse at light loads and maintaining high frequency operation.

#### **PLLIN Pin**

The power module has a phase-locked loop comprised of an internal voltage controlled oscillator and a phase detector. This allows the internal top MOSFET turn-on to be locked to the rising edge of the external clock. The frequency range is ±30% around the set operating frequency. A pulse detection circuit is used to detect a clock on the PLLIN pin to turn on the phase-locked loop. The pulse width of the clock has to be at least 400ns. The clock high level must be greater than 1.7V and clock low level below 0.3V. During the start-up of the regulator, the phase-locked loop function is disabled.

#### INTV<sub>CC</sub> and DRV<sub>CC</sub> Connection

An internal low dropout regulator produces an internal 5V supply that powers the control circuitry and  $DRV_{CC}$  for driving the internal power MOSFETs. Therefore, if the system does not have a 5V power rail, the LTM4612 can be directly powered by  $V_{IN}$ . The gate driver current through the LDO is about 20mA. The internal LDO power dissipation can be calculated as:

$$P_{LDO\ LOSS} = 20 \text{mA} \cdot (V_{IN} - 5V)$$

The LTM4612 also provides the external gate driver voltage pin DRV $_{CC}$ . If there is a 5V rail in the system, it is recommended to connect the DRV $_{CC}$  pin to the external 5V rail. This is especially true for higher input voltages. Do not apply more than 6V to the DRV $_{CC}$  pin.

LINEAR

#### **Parallel Operation**

The LTM4612 device is an inherently current mode controlled device. This allows the paralleled modules to have very good current sharing and balanced thermal on the design. Figure 21 shows a schematic of the parallel design. The voltage feedback equation changes with the variable N as modules are paralleled. The equation:

$$R_{FB} = \frac{\frac{100k}{N}}{\frac{V_{OUT}}{0.6V} - 1}$$

N is the number of paralleled modules.

#### **Radiated EMI Noise**

High radiated EMI noise is a disadvantage for switching regulators by nature. Fast switching turn-on and turn-off make the large di/dt change in the converters, which act as the radiation sources in most systems. LTM4612 integrates the feature to minimize the radiated EMI noise to meet the most applications with low noise requirements. An optimized gate driver for the MOSFET and a noise cancellation network are installed inside the LTM4612 to achieve the low radiated EMI noise. Figure 8 shows a typical example for the LTM4612 to meet the Class B of EN55022 radiated emission limit.

Figure 8. Radiated Emission Scan with 24V<sub>IN</sub> to 5V<sub>OUT</sub> at 5A Measured in 10 Meter Chamber

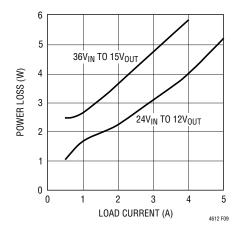

#### Thermal Considerations and Output Current Derating

In different applications, LTM4612 operates in a variety of thermal environments. The maximum output current is limited by the environment thermal condition. Sufficient cooling should be provided to help ensure reliable operation. When the cooling is limited, proper output current derating is necessary, considering ambient temperature, airflow, input/output condition, and the need for increased reliability.

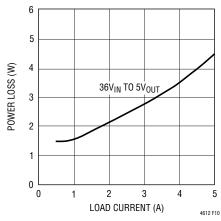

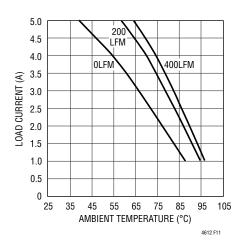

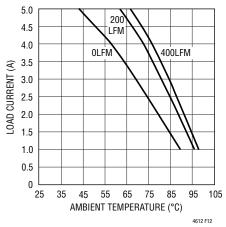

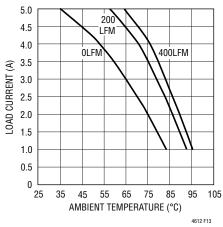

The power loss curves in Figures 9 and 10 can be used in coordination with the load current derating curves in Figures 11 to 16 for calculating an approximate  $\theta_{\text{JA}}$  for the module. Graph designation delineates between no heat sink, and a BGA heat sink. Each of the load current derating curves will lower the maximum load current as a function of the increased ambient temperature to keep the maximum junction temperature of the power module at 125°C maximum. This will maintain the maximum operating temperature below 125°C. Each of the derating curves and the power loss curve that corresponds to the correct output voltage can be used to solve for the approximate  $\theta_{JA}$  of the condition. Each figure has three curves that are taken at three different air flow conditions. Each of the derating curves in Figures 11 to 16 can be used with the appropriate power loss curve in either Figure 9 or Figure 10 to derive an approximate  $\theta_{JA}$ . Table 3 provides the approximate  $\theta_{JA}$  for Figures 11 to 16. A complete explanation of the thermal characteristics is provided in the thermal application note, AN110.

Figure 9. Power Loss at 12V<sub>OUT</sub> and 15V<sub>OUT</sub>

Figure 10. Power Loss at 5V<sub>OUT</sub>

Figure 11. No Heat Sink with 36V<sub>IN</sub> to 5V<sub>OUT</sub>

Figure 12. BGA Heat Sink with 36V<sub>IN</sub> to 5V<sub>OUT</sub>

Figure 13. No Heat Sink with 24V<sub>IN</sub> to 12V<sub>OUT</sub>

Figure 14. BGA Heat Sink with 24V<sub>IN</sub> to 12V<sub>OUT</sub>

Figure 15. No Heat Sink with 36V<sub>IN</sub> to 15V<sub>OUT</sub>

Figure 16. BGA Heat Sink with 36V<sub>IN</sub> to 15V<sub>OUT</sub>

#### Table 3. 12V and 15V Outputs

| DERATING CURVE     | V <sub>IN</sub> (V) | POWER LOSS CURVE | AIR FLOW (LFM) | HEAT SINK     | θ <sub>JA</sub> (°C/W) |

|--------------------|---------------------|------------------|----------------|---------------|------------------------|

| Figures 11, 13, 15 | 24, 36              | Figure 9         | 0              | None          | 13                     |

| Figures 11, 13, 15 | 24, 36              | Figure 9         | 200            | None          | 9.3                    |

| Figures 11, 13, 15 | 24, 36              | Figure 9         | 400            | None          | 8.3                    |

| Figures 12, 14, 16 | 24, 36              | Figure 9         | 0              | BGA Heat Sink | 12.2                   |

| Figures 12, 14, 16 | 24, 36              | Figure 9         | 200            | BGA Heat Sink | 8.6                    |

| Figures 12, 14, 16 | 24, 36              | Figure 9         | 400            | BGA Heat Sink | 7.7                    |

#### Table 4. 5V Output

| iusio ii or output |                     |                  |                |               |                        |

|--------------------|---------------------|------------------|----------------|---------------|------------------------|

| DERATING CURVE     | V <sub>IN</sub> (V) | POWER LOSS CURVE | AIR FLOW (LFM) | HEAT SINK     | θ <sub>JA</sub> (°C/W) |

| Figure 11          | 36                  | Figure 10        | 0              | None          | 14.9                   |

| Figure 11          | 36                  | Figure 10        | 200            | None          | 11.1                   |

| Figure 11          | 36                  | Figure 10        | 400            | None          | 10                     |

| Figure 12          | 36                  | Figure 10        | 0              | BGA Heat Sink | 14                     |

| Figure 12          | 36                  | Figure 10        | 200            | BGA Heat Sink | 10.4                   |

| Figure 12          | 36                  | Figure 10        | 400            | BGA Heat Sink | 9.3                    |

|                    |                     |                  |                |               |                        |

#### **Heat Sink Manufacturer**

| Wakefield Engineering | Part No: LTN20069 | Phone: 603-635-2800 |

|-----------------------|-------------------|---------------------|

#### **Safety Considerations**

The LTM4612 modules do not provide isolation from  $V_{IN}$  to  $V_{OUT}$ . There is no internal fuse. If required, a slow blow fuse with a rating twice the maximum input current needs to be provided to protect each unit from catastrophic failure.

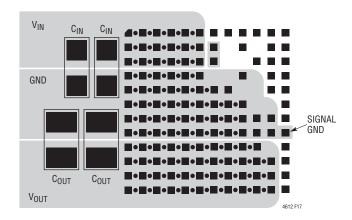

#### Layout Checklist/Example

The high integration of LTM4612 makes the PCB board layout very simple and easy. However, to optimize its electrical and thermal performance, some layout considerations are still necessary.

- Use large PCB copper areas for high current path, including V<sub>IN</sub>, PGND and V<sub>OUT</sub>. It helps to minimize the PCB conduction loss and thermal stress.

- Place high frequency ceramic input and output capacitors next to the V<sub>D</sub>, PGND and V<sub>OUT</sub> pins to minimize high frequency noise.

- Place a dedicated power ground layer underneath the unit.

- Use round corners for the PCB copper layer to minimize the radiated noise.

- To minimize the EMI noise and reduce module thermal stress, use multiple vias for interconnection between top layer and other power layers.

- Do not put vias directly on pads.

- If vias are placed onto the pads, the the vias must be capped.

- Interstitial via placement can also be used if necessary.

- Use a separated SGND ground copper area for components connected to signal pins. Connect the SGND to PGND underneath the unit.

- Place one or more high frequency ceramic capacitors close to the connection into the system board.

Figure 17 gives a good example of the recommended layout.

Figure 17. Recommended PCB Layout

Figure 18. Typical 22V to 36V<sub>IN</sub>, 12V at 5A Design

Figure 19. Typical 5V to 36V<sub>IN</sub>, 3.3V at 5A Design with 400kHz Frequency

Figure 20. 26V to 36V<sub>IN</sub>, 15V at 4A Design with Reduced Frequency

Figure 21. 2-Phase, Parallel 12V at 10A Design

LINEAR TECHNOLOGY

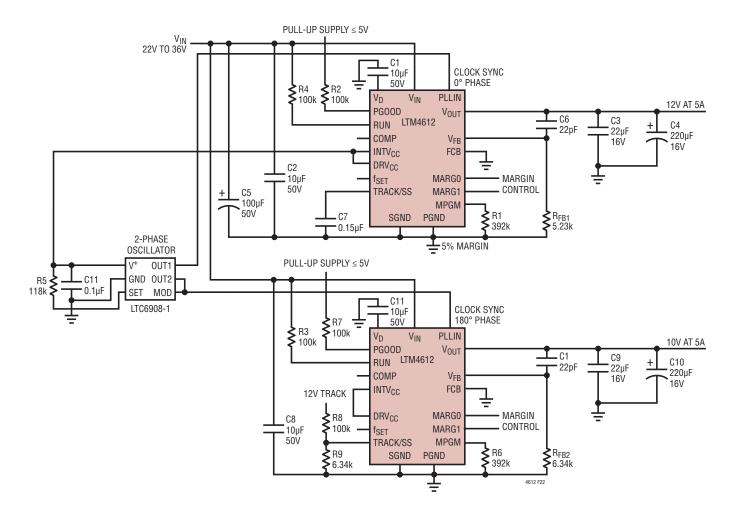

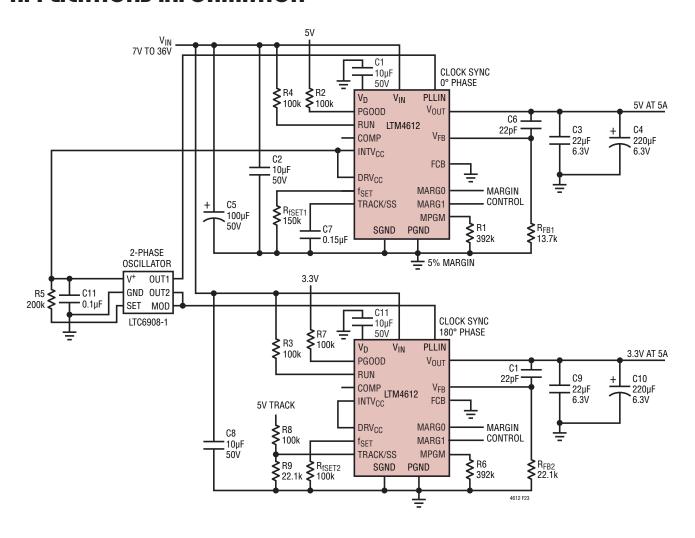

Figure 22. 2-Phase, 12V and 10V at 5A Design

Figure 23. 2-Phase, 5V and 3.3V at 5A Design with 500kHz Frequency

## PACKAGE DESCRIPTION

#### Pin Assignment Tables (Arranged by Pin Function)

| PIN NAME |                 |  |

|----------|-----------------|--|

| A1       | V <sub>IN</sub> |  |

| A2       | V <sub>IN</sub> |  |

| A3       | V <sub>IN</sub> |  |

| A4       | V <sub>IN</sub> |  |

| A5       | V <sub>IN</sub> |  |

| A6       | V <sub>IN</sub> |  |

| B1       | V <sub>IN</sub> |  |

| B2       | V <sub>IN</sub> |  |

| B3       | V <sub>IN</sub> |  |

| B4       | V <sub>IN</sub> |  |

| B5       | V <sub>IN</sub> |  |

| B6       | V <sub>IN</sub> |  |

| C1       | VIN             |  |

| C2       | VIN             |  |

| C3       | VIN             |  |

| C4       | VIN             |  |

| C5       | VIN             |  |

| C6       | VIN             |  |

| PIN NAME                                                         |                                                              |  |  |

|------------------------------------------------------------------|--------------------------------------------------------------|--|--|

| D1<br>D2<br>D3<br>D4<br>D5<br>D6                                 | PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND                 |  |  |

| E1<br>E2<br>E3<br>E4<br>E5<br>E6<br>E7<br>E8                     | PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND |  |  |

| F1<br>F2<br>F3<br>F4<br>F5<br>F6<br>F7<br>F8<br>F9               | PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND |  |  |

| G1<br>G2<br>G3<br>G4<br>G5<br>G6<br>G7<br>G8<br>G9<br>G10<br>G11 | PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND |  |  |

| H1<br>H2<br>H3<br>H4<br>H5<br>H6<br>H7<br>H8<br>H9<br>H10        | PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND<br>PGND |  |  |

| PIN NAME                                                         |                                                              |  |

|------------------------------------------------------------------|--------------------------------------------------------------|--|

| J1<br>J2<br>J3<br>J4<br>J5<br>J6<br>J7<br>J8<br>J9<br>J10<br>J11 | Vout<br>Vout<br>Vout<br>Vout<br>Vout<br>Vout<br>Vout<br>Vout |  |

| K1<br>K2<br>K3<br>K4<br>K5<br>K6<br>K7<br>K8<br>K9<br>K10        | VOUT VOUT VOUT VOUT VOUT VOUT VOUT VOUT                      |  |

| L1<br>L2<br>L3<br>L4<br>L5<br>L6<br>L7<br>L8<br>L9<br>L10        | Vout<br>Vout<br>Vout<br>Vout<br>Vout<br>Vout<br>Vout<br>Vout |  |

| M1<br>M2<br>M3<br>M4<br>M5<br>M6<br>M7<br>M8<br>M9<br>M10<br>M11 | Vout<br>Vout<br>Vout<br>Vout<br>Vout<br>Vout<br>Vout<br>Vout |  |

| PIN NAME                            |                                                                |  |  |

|-------------------------------------|----------------------------------------------------------------|--|--|

| A7<br>A8<br>A9<br>A10<br>A11<br>A12 | INTV <sub>CC</sub><br>PLLIN<br>TRACK/SS<br>RUN<br>COMP<br>MPGM |  |  |

| B7<br>B8<br>B9<br>B10<br>B11<br>B12 | V <sub>D</sub> - RUN - MPGM f <sub>SET</sub>                   |  |  |

| C7<br>C8<br>C9<br>C10<br>C11<br>C12 | V <sub>D</sub> DRV <sub>CC</sub> MARG1 MARG0                   |  |  |

| D7<br>D8<br>D9<br>D10<br>D11<br>D12 | SGND<br>COMP                                                   |  |  |

| E9<br>E10<br>E11<br>E12             | -<br>DRV <sub>CC</sub><br>DRV <sub>CC</sub>                    |  |  |

| F10<br>F11<br>F12                   | -<br>-<br>V <sub>FB</sub>                                      |  |  |

| G12                                 | PGOOD                                                          |  |  |

| H12                                 | SGND                                                           |  |  |

| J12                                 | NC                                                             |  |  |

| K12                                 | NC                                                             |  |  |

| L12                                 | NC                                                             |  |  |

| M12                                 | FCB                                                            |  |  |

|                                     |                                                                |  |  |

## PACKAGE DESCRIPTION

C(0.30) PAD 1 12 Ę LGA 133 1107 REV Ø PACKAGE IN TRAY LOADING ORIENTATION PACKAGE BOTTOM VIEW LTMXXXXXX TRAY PIN 1 BEVEL COMPONENT PIN "A1" 1.27 BSC PADS SEE NOTES 13.97 BSC 0.12 - 0.286 NOTES: 1. DIMENSIONING AND TOLERANCING PER ASME Y14:5M-1994 DETAILS OF PAD #1 IDENTIFIER ARE OPTIONAL,

BUT MUST BE LOCATED WITHIN THE ZONE INDICATED.

THE PAD #1 IDENTIFIER MAY BE EITHER A MOLD OR

MARKED FEATURE 133-Lead (15mm  $\times$  15mm  $\times$  2.82mm) (Reference LTM DWG # 05-08-1766 Rev Ø) 3 LAND DESIGNATION PER JESD MO-222, SPP-010 2.72 - 2.92 DETAIL B 2. ALL DIMENSIONS ARE IN MILLIMETERS 5. PRIMARY DATUM -Z- IS SEATING PLANE 6. THE TOTAL NUMBER OF PADS: 133 --0.27 - 0.37SUBSTRATE ⊕ eee SX Y SYMBOL TOLERANCE 0.10 DETAIL B MOLD 0.630 ±0.025 SQ. 133× Z qqq 🛡 2.45 - 2.55 aaa bbb eee aaa Z 15 BSC SUGGESTED PCB LAYOUT TOP VIEW PACKAGE TOP VIEW 15 BSC 0.000 0.6350 0906.1 3.1750 — 4.4450 — 1.9050 — 5.7150 — 6.9850 — Z aaa Z 0.6350 -0.0000 -0.6350 -5.7150 -4.4450 -3.1750 -6.9850 1.9050 PAD 1

LGA Package

## **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                                                   | PAGE NUMBER    |

|-----|-------|-------------------------------------------------------------------------------|----------------|

| Α   | 03/10 | Changes to Title and Description                                              | 1              |

|     |       | Changes to Absolute Maximum Ratings                                           | 1              |

|     |       | Changes to Electrical Characteristics                                         | 2, 3           |

|     |       | Text Changes to Operation Section                                             | 10             |

|     |       | Text Changes to Applications Information Section                              | 12, 14         |

|     |       | Changes to Figures 18, 19, 20, 21, 22                                         | 19, 20, 21, 22 |

|     |       | Changes to Related Parts                                                      | 26             |

| В   | 05/11 | Changes to the Title, Description, Features and Typical Application sections. | 1              |

|     |       | Changes to "The ● denotes" statement and Note 2.                              | 2, 3, 4        |

|     |       | Changes to the Pin Functions.                                                 | 7, 8           |

|     |       | Changes to the Block Diagram.                                                 | 9              |

|     |       | Text changes to the Operation section.                                        | 10             |

|     |       | Text changes to the Applications Information section.                         | 10–20          |

|     |       | Changes to Figures 17, 19, 21, 22.                                            | 20, 21, 22, 23 |

|     |       | Changes to the Related Parts.                                                 | 28             |

## PACKAGE PHOTOGRAPH

## **RELATED PARTS**

| PART NUMBER      | DESCRIPTION                                                                          | COMMENTS                                                                                                                                                                                       |

|------------------|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LTM4606          | EN55022B Compliant 6A, DC/DC μModule<br>Regulator                                    | EN55022B Compliant with PLL, Output Tracking and Margining, LTM4612 Pin Compatible                                                                                                             |

| LTM4613          | EN55022B Compliant 36V, 8A, Step-Down µModule<br>Regulator with PLL, Output Tracking | $5V \le V_{IN} \le 36V$ , $3.3V \le V_{OUT} \le 15V$ , $15mm \times 15mm \times 4.3mm$ LGA Package                                                                                             |

| LTM4601/LTM4601A | 12A DC/DC µModule Regulator with PLL, Output Tracking/Margining and Remote Sensing   | Synchronizable, PolyPhase Operation, LTM4601-1/LTM4601A-1 Version Has No Remote Sensing, LGA Package                                                                                           |

| LTM4604A         | Low V <sub>IN</sub> 4A DC/DC µModule Regulator                                       | $2.375V \le V_{IN} \le 5.5V$ , $0.8V \le V_{OUT} \le 5V$ , $9mm \times 15mm \times 2.3mm$ LGA Package                                                                                          |

| LTM4608A         | Low V <sub>IN</sub> 8A DC/DC µModule Regulator                                       | $2.7 \text{V} \le \text{V}_{\text{IN}} \le 5.5 \text{V}, \ 0.6 \text{V} \le \text{V}_{\text{OUT}} \le 5 \text{V}, \ 9 \text{mm} \times 15 \text{mm} \times 2.8 \text{mm} \ \text{LGA Package}$ |

| LTM8022/LTM8023  | 36V <sub>IN</sub> , 1A and 2A DC/DC μModule Regulator                                | Pin Compatible, $4.5V \le V_{\text{IN}} \le 36V$ ; $9\text{mm} \times 11.25\text{mm} \times 2.8\text{mm}$ LGA Package                                                                          |

| LTM4627          | 20V <sub>IN</sub> , 15A DC/DC Step-Down μModule Regulator                            | $4.5V \le V_{IN} \le 20V$ , $0.6V \le V_{OUT} \le 5V$ , $15mm \times 15mm \times 4.3mm$ LGA Package                                                                                            |

| LTM4618          | 26V <sub>IN</sub> , 6A DC/DC Step-Down μModule Regulator with PLL, Output Tracking   | 4.5V ≤ V <sub>IN</sub> ≤ 26.5V, 0.8V ≤ V <sub>OUT</sub> ≤ 5V, Synchronizable, 9mm × 15mm × 4.3mm LGA Package                                                                                   |

| LTM8033          | EN55022B Compliant 36V <sub>IN</sub> , 3A DC/DC Step-Down μModule Regulator          | $3.6V \le V_{IN} \le 36V,  0.8V \le V_{OUT} \le 24V,  Synchronizable, \\ 11.25mm \times 15mm \times 4.3mm  LGA  Package$                                                                       |