# ST1335D, ST1336D ST1355D

# 5-Contact Memory Card IC 272-bit EEPROM With Advanced Security Mechanisms and Inlock System

**DATA BRIEF**

- 5 V Single Supply Voltage

- Counting Capability (two options)

- up to 32767 (8<sup>5</sup> -1)

- 8 times reloadable, up to 4095 (8<sup>4</sup>-1)

- Active Authentication Function (ST1335D/55D)

- Cipher Block Chaining Function (ST1355D)

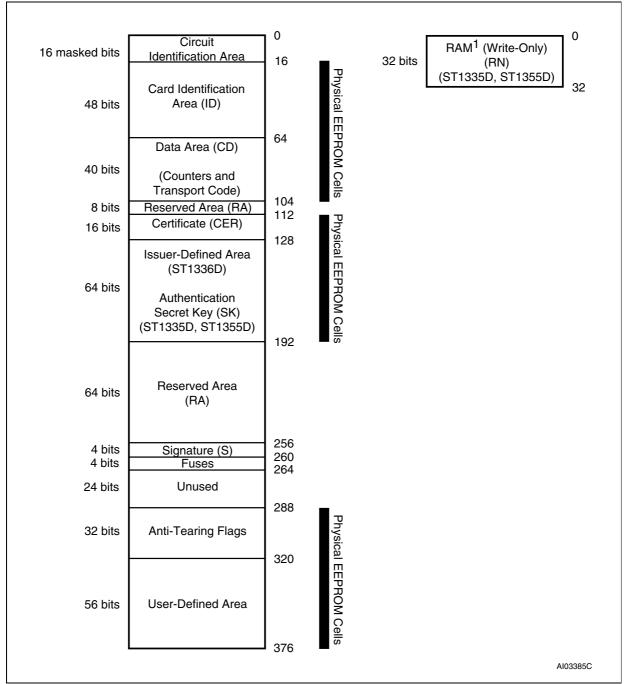

- Memory Divided into :

- 16 bits of Circuit Identification

- 48 bits of Card Identification

- 40 bits of Count Data

- 16 bits for Validation Certificate

- 24 bits of Transport Code

- 64 bits of Issuer Data (ST1336D) or Authentication Secret Key (ST1335D/55D)

- 32 bits of Anti-tearing Flags (optional)

- 56 bits of User data (optionally not erasable)

- More than 500,000 Erase/Write Cycles

- More than 10 Years Data Retention

- 3.5 ms Programming Time at 5 V (typical)

- 500 µA Supply Current at 5 V (typical)

- 250 µA Stand-by Current at 5 V (typical)

### **DESCRIPTION**

The members of the ST1335D/36D/55D family are principally designed for use in prepaid Phonecard applications. Each is a 272-bit EEPROM device, with associated security logic and special fuses to control memory access. The memory is arranged as a matrix of 34 x 8 cells, accessed in a serial bitwise fashion for reading and programming, and in a byte-wise fashion for internal erasing. An on-chip

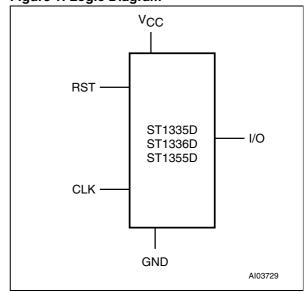

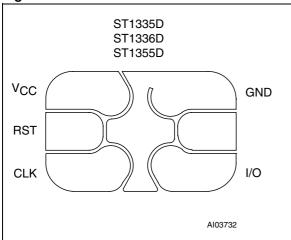

**Table 1. Signal Names**

| CLK | Clock                      |

|-----|----------------------------|

| RST | Reset                      |

| I/O | Serial Data Input / Output |

| Vcc | Supply Voltage             |

| GND | Ground                     |

Figure 1. Logic Diagram

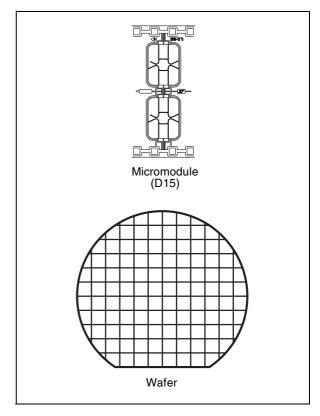

June 2000 1/4

Complete data available under NDA.

Figure 2. D15 Contact Connections

address counter provides an internal address space of up to 512 bits.

Each member of the ST1335D/36D/55D family has an identification data area, unit-counters (with an anti-tearing mechanism for reliable usage in open readers), a post validation certificate, an issuer area (ST1336D) or an authentication secret key area (ST1335D/55D), and a user area. This is summarized in Figure 3.

The validation certificate allows the recognition of the device by the appropriate security module. When the 8 times reloadable option is activated, the certificate and the reload counter (address 64d to 71d) can be used to allow the recognition of the circuit by the appropriate security module. This will allow the development of a reloadable card as the certificate value is refreshed each time the reload counter is incremented.

The anti-tearing mechanism guards against miscounts occurring when the card is prematurely extracted, while an operation is underway, in an open reader.

#### **MODES**

The device works in two distinct modes of operation:

- Issuer Mode: for the card manufacturer. allowing custom data to be written to the device, to initialize it before release to the end user.

- User Mode: for the end user of the card, with restricted, and controlled access to the device.

Before delivery, from ST to the card issuer, the device is placed in the Issuer Mode. This operation is performed by blowing the "test fuse".

#### **OPTIONS**

Three options are available when ordering the device:

- The anti-tearing mechanism can be disconnected. In this case, the anti-tearing flag area from bit 288d to bit 319d is unused (Figure 3).

- The user area, from bit 320d to bit 375d, can be defined as "not erasable" in the User Mode.

- The reload mechanism can be activated. In this case, erasing a bit in the reload counter refreshes the certificate (CER). At this time, the certificate can be programmed with a new value.

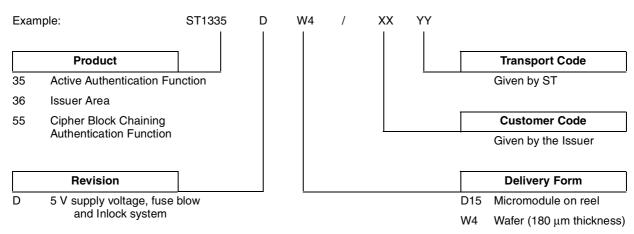

## **ORDERING INFORMATION**

The notation used for the device number is as shown in Table 2. For a list of available options (speed, package, etc.) or for further information on any aspect of this device, please contact your nearest ST Sales Office.

**Table 2. Ordering Information Scheme**

Note: 1. Please contact your nearest ST Sales Office to check on availability

Ly/

2/4

Figure 3. Memory Map

Note: 1. The write-only RAM area (RN) is applicable only for the User Mode.

47/

Information furnished is believed to be accurate and reliable. However, STMicroelectronics assumes no responsibility for the consequences of use of such information nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of STMicroelectronics. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. STMicroelectronics products are not authorized for use as critical components in life support devices or systems without express written approval of STMicroelectronics.

The ST logo is a registered trademark of STMicroelectronics.

All other names are the property of their respective owners

© 2000 STMicroelectronics - All rights reserved BULL CP8 Patents

STMicroelectronics GROUP OF COMPANIES

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States www.st.com

4/4