## **Embedded microprocessors**

## www.BDTIC.com/ST

#### **STMicroelectronics**

## **Overview**

- SPEAr is ST's family of embedded MPUs with state-of-the-art architecture, silicon technology and intellectual property

- Highly-integrated 32-bit ARM<sup>®</sup> MPU cores (ARM926 and ARM Cortex-A9)

- Offers significant processing and connectivity capabilities at lower power consumption

## Why SPEAr<sup>®</sup>?

- Based on an industry-standard ARM<sup>®</sup> core

- Architecture includes proven IPs for connectivity, memory interfaces and high-performance internal bus system

- Customized SPEAr solutions for a specific businesses/applications

- Ready-to-use development kits for full custom project approach

# Highly integrated 32-bit ARM MPU cores

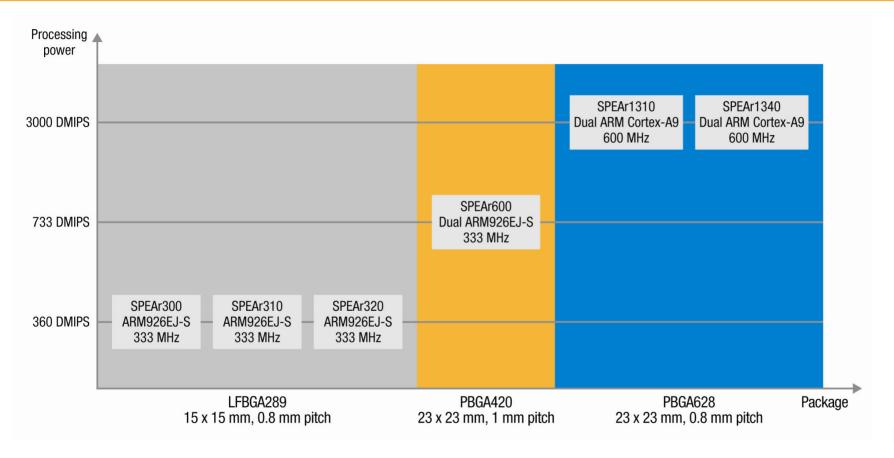

- Clear architecture and technology evolution: ARM926 to Cortex-A9, 90 nm to 40 nm CMOS technology

- High computation power (starting from 366 DMIPS... up to 3000 DMIPS)

- Full capability for high-end operating systems (Linux, VxWORKS, WinCE, Android and more)

- State of the art peripherals/subsystems for high-speed connectivity, high-performance memory interfaces and internal bus systems

**STMicroelectronics**

## **SPEAr<sup>®</sup> eMPU standard products**

**STMicroelectronics**

## www.BDTIC.com/ST

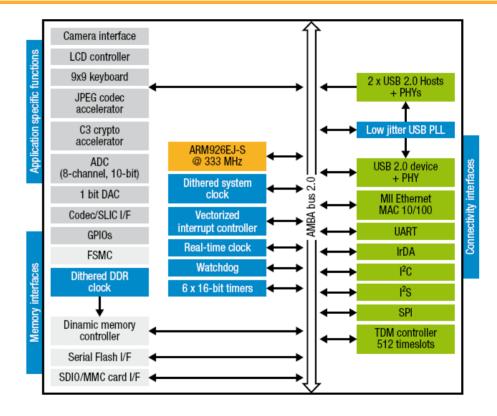

# **SPEAr300: Quick view**

- ARM926EJ-S @ 333 MHz (minimum)

- High-performance 8-channel DMA

- External memories supported:

- LP-DDR, DDR2, SRAM, NAND/NOR Flash

- SDIO/MMC card

- Connectivity

- USB 2.0 with PHYs

- Ethernet MAC

- SPI/I<sup>2</sup>C (up to 8 chip selects)

- I<sup>2</sup>S, UART, IrDA, TDM bus

- Cryptographic engine

- Peripherals

- Camera interface

- LCD panel

- Touchscreen

- 9 x 9 keyboard

- Timeslot management

Package: LFBGA289 (15 x 15 mm, pitch 0.8 mm)

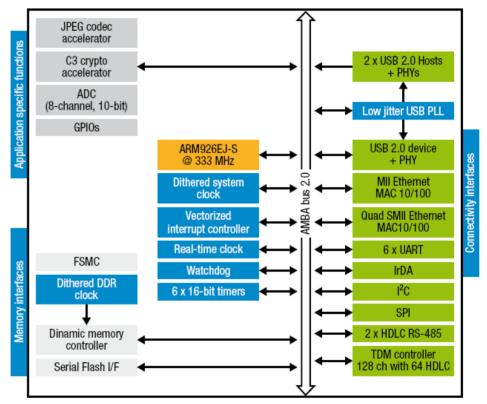

## **SPEAr310: Quick view**

- ARM926EJ-S @ 333 MHz (minimum)

- High-performance 8-channel DMA

- External memories supported

- LP-DDR, DDR2, SRAM, NAND/NOR Flash

- FPGA connections

- Connectivity

- USB 2.0 (2 hosts, 1 device) with PHYs

- 5 Ethernet MACs (MII and 4 x SMII)

- SPI (up to 4 chip selects)

- I<sup>2</sup>S, UART, IrDA, TDM/HDLC bus

- Cryptographic engine

Package: LFBGA289 (15 x 15 mm, pitch 0.8 mm)

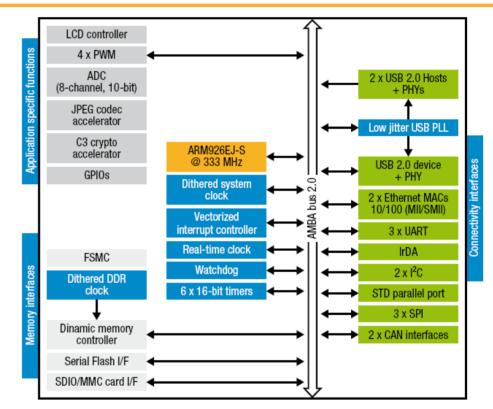

## **SPEAr320: Quick view**

- ARM926EJ-S @ 333 MHz (minimum)

- High-performance 8-channel DMA

- External memories supported

- LP-DDR, DDR2, SRAM, NAND/NOR Flash

- SDIO/MMC card

- FPGA connections

- Connectivity

- USB 2.0 ( 2 hosts, 1 device) with PHYs

- Dual Ethernet MAC (SMII/MII)

- Dual CAN

- SPI/I<sup>2</sup>C (up to 6 chip selects)

- I<sup>2</sup>S, UART, IrDA

- Cryptographic engine

- Peripherals

- LCD panel

- Touchscreen

Package: LFBGA289 (15 x 15 mm, pitch 0.8 mm)

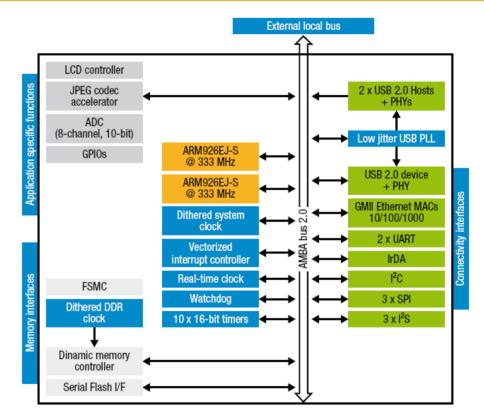

# Dual ARM926EJ-S @ 333 MHz (minimum)

High-performance 8-channel DMA

**SPEAr600: Quick view**

- External memories supported

- DDR, DDR2, NAND/NOR Flash

- Connectivity

- USB 2.0 ( 2 hosts, 1 device) with PHYs

- Giga-Ethernet MAC

- SPI, I<sup>2</sup>S, UART, IrDA

- Peripherals

- LCD panel

- Touchscreen

**STMicroelectronics**

External local bus

Package: PBGA420 (23 x 23 mm, pitch 1 mm)

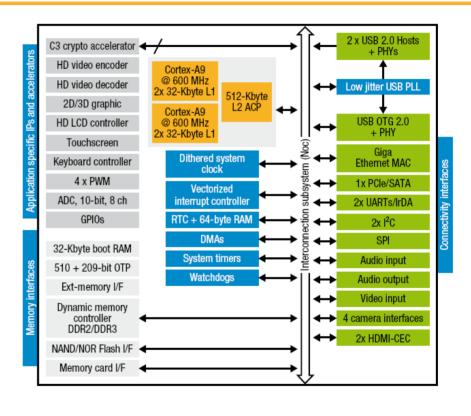

## **SPEAr1310: Quick view**

- Dual ARM Cortex A9 @ 600 MHz

- 2 x 32 KB L1 cache (each core) and 512 KB L2 cache with ECC and accelerator coherency port (ACP)

- High-performance 16-channel DMA

- DDR3/DDR2 support

- Connectivity

- USB 2.0 (2 hosts, 1 OTG) with PHYs

- Giga-Ethernet

- PCIe and SATA

- HDLC and TDM

- Dual CAN

- SPI, I<sup>2</sup>S, I<sup>2</sup>C, UARTs

- Peripherals and hardware accelerators

- HD display controller

- Touchscreen

- External local bus connectivity

- JPEG codec

- Crypto accelerator

### **STMicroelectronics**

#### **EXPI** expansion interface JPEG codec 2 x USB 2.0 Hosts accelerator + PHYsC3 crypto accelerator Cortex-A9 @ 600 MHz ← Low jitter USB PLL HD display controller ECC 2x 32-Kbyte L 512-Kbyte Touchscreen Cortex-A9 ↔ 12 ACP USB OTG 2.0 $\leftrightarrow$ @ 600 MHz Kevboard controller + PHY 2x 32-Kbvte L1 **GPIOs** 2x Giga Ethernet MAC Dithered system ADC. 10-bit. 8 ch clock 3x Ethernet MAC Vectorized 10/100interrupt controller 3x PCIe/SATA RTC + 64-byte RAM PCI32 @ 66 MHz DMAs 32-Kbyte boot RAM Dual CAN $\leftrightarrow$ System timers 510 + 209-bit OTP ←→ 2x HDLC (E1/TDM) Watchdogs Ext-memory I/F 2x HDLC (RS485) ↔ Dynamic memory 6x UARTs $\leftrightarrow$ controller DDR2/DDR3 ECC $2x |^2C$ $\leftrightarrow$ NAND/NOR Flash I/F $2 \times l^2 S$ $\leftrightarrow$ Memory card I/F SPI $\leftrightarrow$

Package: PBGA628 (23 x 23 mm, pitch 0.8 mm)

## www.BDTIC.com/ST

### **STMicroelectronics**

# **SPEAr1340: Quick view**

- Dual ARM Cortex A9 @ 600 MHz

- 2 x 32 KB L1 cache (each core) and 512 KB L2 cache and accelerator coherency port (ACP)

- High-performance 16-channel DMA

- DDR3/DDR2 support

- Connectivity

- USB 2.0 (2 hosts, 1 OTG) with PHYs

- **Giga-Ethernet**

- PCIe and SATA

- SPI, I<sup>2</sup>S, I<sup>2</sup>C, UARTs

- Peripherals and hardware accelerators

- HD display controller

- Touchscreen

- External local bus connectivity

- 1080p video encoder (H.264, JPEG64, JFIF)

- 1080p video decoder (H.263, H.264, MPEG-4, VC-1...

- MALI 200 graphic engine

- Crypto accelerator

Package: PBGA628 (23 x 23 mm, pitch 0.8 mm)