# Differences between W7100 and W7100A

Version 1.1

# What is different between new W7100A and W7100?

© 2011 WIZnet Co., Inc. All Rights Reserved. For more information, visit our website at http://www.wiznet.co.kr

#### 1 Introduction

This document will explain the new features of W7100A and the differences from W7100. The following table briefly illustrates the differences between W7100A and W7100.

| Differences            | W7100         | W7100A                        |  |  |

|------------------------|---------------|-------------------------------|--|--|

| Packaging              | 100pin LQFP   | 100pin LQFP, 64pin QFN        |  |  |

| New SFR                | Х             | Added (refering Section 2.4)  |  |  |

| Powerdown mode         | Not Supported | Supported                     |  |  |

| External memory        | Not Supported | Connectable(100pin LQFP only) |  |  |

| Memory lock function   | Not Supported | Supported                     |  |  |

| GPIO pull-up/down      | Not Supported | Supported                     |  |  |

| User data flash memory | 256Byte       | 255Byte                       |  |  |

Table 1. Differences between W7100 and W7100A

Users who have been using W7100 must be aware of the following facts.

- If there is no additional Pull-up/down circuit for GPIO, the GPIO port of W7100A must be used after setting the pull-up/down register. Users who need to use GPIO port must set pull-up/down of GPIO when initializing W7100A to use normal 0 ~ 3.3V input/output voltage.

- Since the PHY mode setting pins are deleted in the W7100A QFN64pin package, User must set operation mode of W7100A using PHYCONF SFR (Special Function Register).

Set the MODE\_EN bit and MODE[2:0] bit of PHYCONF SFR. Then set the PHY\_RSTn bit of PHYCONF SFR to reset W7100A. For more specific information about operation mode value depending on MODE[2:0] bit, please refer to the PM pin value of W7100A Datasheet "Pin Description" section.

```

PHYCONF = 0x08; // MODE_EN bit enable, MODE2 ~ 0 value is 0 (normal mode)

PHYCONF |= 0x20; // Set the PHY_RSTn bit (reset bit)

```

Delay(); // Delay for reset timing (refer to the section 10 reset timing)

PHYCONF &= ~(0x20); // Clear the PHY\_RSTn bit

#### 2 Differences

In this section the new functions or differences of W7100A will be

- 100pin LQFP & 64pin QFN Package type

- Memory Lock

- Power-down Mode

- External data memory

- GPIO Pull-up/down Configuration

- New SFR

- 255Byte User data flash

Whole pins of W7100 and W7100A are completely compatible; users who have been using W7100 do not need to change the H/W schematic. But only the newly added 64pin QFN package of W7100A has different number of pins and different arrangement of pins than W7100.

# 2.1 Packaging

In W7100A 64 pin package, 34 pins of the existing 100 pins have been deleted.

The table below shows which pins are deleted.

Table 2. The deleted pins of the 64pin package

| Related part         | Deleted pin                    |  |

|----------------------|--------------------------------|--|

| Timer/counter        | T0, T1, GATE0, GATE1, T2, T2EX |  |

| External interrupt   | nINT1, nINT2, nINT3            |  |

| Indicator LED signal | FDXLED, COLLED, RXLED, TXLED   |  |

| External memory      | EXTALE, EXTDATAWR, EXTDATARD   |  |

| GPIO                 | GPIO3[0:7], GPIO2[3:7]         |  |

| PHY mode setting     | PM2, PM1, PM0                  |  |

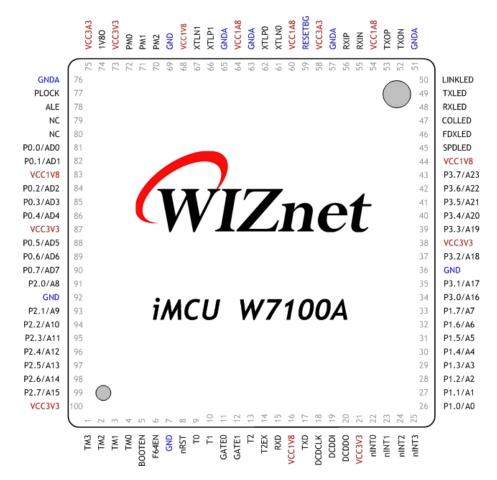

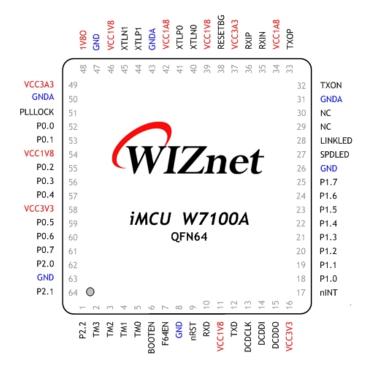

Refer to Fig. 1 below for the image of 100pin package and Fig 2 in the next page for the image of 64pin package.

Please refer to W7100A's data sheet for detailed size information of the 100pin and 64pin package.

Fig 1. W7100A 100pin LQFP package

Fig 2. W7100A 64pin QFN package

#### 2.2 Lock function

The Memory Lock function has been added to W7100A to prevent the invasion into W7100A's data memory or code memory. The Lock function can be individually enable/disable for code memory and data memory. User must be aware of the fact that once the Lock function is set; the memory cannot be read, the W7100 Debugger cannot load the code and data area, and the verify function does not work in WizISP. User must use the WizISP program to enable/disable the lock function. For more details, please refer to the "Wiz ISP Program Guide" document.

#### 2.3 Power-down mode

The Power-down mode has been added to W7100A to minimize the power consumption. The power consumption can be decreased up to 50% when Power-down mode is used. User must be aware of the fact that Ethernet communication was disabled during power-down mode. The MCU core operates even during power-down mode, so if Ethernet is needed, disable the power-down mode during Ethernet is used to minimize the power consumption.

Power-down mode can be set using new PHYCONF SFR (Special Function Register) of W7100A. For more details on this SFR, please refer to W7100A's datasheet.

PHYCONF (0xFE): W7100 PHY operation mode, reset, power down configuration register

| 7 | 6 | 5        | 4        | 3       | 2     | 1     | 0     | Reset |

|---|---|----------|----------|---------|-------|-------|-------|-------|

| - | - | PHY_RSTn | PHY_PWDN | MODE_EN | MODE2 | MODE1 | MODE0 | 0x00  |

# 2.4 External data memory

W7100A LQFP 100pin package has 64Kbyte internal RAM data memory, the data memory can be expanded up to 16Mbyte external data memory. But W7100A QFN 64pin package cannot expand the external data memory. Please refer to the W7100A datasheet 'External Data Memory Access' section for interfacing between W7100A and external memory.

For configuring the external memory access timing, W7100A has EXTWTST and ALECON SFR. About these SFR, please refer to the W7100A datasheet 'SFR definition'.

# 2.5 GPIO pull-up/down

The pull-up/down function has been added to the GPIO of W7100A. The pull-up function

makes the relevant port pin's output voltage to 3.3V and the pull-down function makes the relevant port pin's output voltage to 0V. Each pin from GPIO0 to GPIO3 can be controlled respectively, and user can use new Px\_PU, Px\_PD SFR(x stands for the GPIO# 0~3) for settings.

New W7100A has faster rising time than W7100. Using more faster response speed, we can control various external devices. For more detailed information, please refer to the W7100A datasheet.

- PxPU(0xEB ~ 0xEE): GPIO port x pull-up register ('1': pull-up)

- PxPD(0xE3 ~ 0xE6): GPIO port x pull-down register ('1': pull-down)

# 2.6 Added Special Function Registers

As mentioned earlier, three new SFR has been added besides PHYCONF, Px\_PD/PxPU SFR; INTWTST, EXTWTST, and ALCON.

- INTWTST(0x9C): Configure internal flash, ram, TCPIPCore access time

- Ram WTST: Access timing control of internal Ram

- TCPIPCore WTST: Access timing control of internal TCPIPCore

- Flash WTST: Access timing control of internal Flash

- EXTWTST(0x9D, 0x9E): Access timing control of external device

- ALECON(0x9F): Delay control of ALE signal to control the external device

# 2.7 255Byte User Data Flash

Established W7100 has 256Byte user data flash but new W7100A has 255Byte user data flash. User can use this memory for IP, MAC saving/reading. It is very easy to write/read the user data flash. Please refer to the W7100A application note for more detailed information.

### **Document History Information**

| Version  | Date      | Descriptions                           |

|----------|-----------|----------------------------------------|

| Ver. 1.0 | Mar. 2011 | Release with W7100A launching          |

| Ver. 1.1 | Mar. 2011 | Add a difference of 255Byte Data flash |