**Errata Notification**

### Introduction

Thank you for participating in the Kintex<sup>™</sup>-7 FPGAs Engineering Sample Program. As part of this program, we are pleased to provide to you engineering samples of the devices listed in Table 1. Although Xilinx has made every effort to ensure the highest possible quality, these devices are subject to the limitations described in the following errata.

# Devices

These errata apply to the devices shown in Table 1.

| Table 1: De | vices Affected | by These Errata |

|-------------|----------------|-----------------|

|-------------|----------------|-----------------|

| Product Family | Device       | JTAG ID<br>(Revision Code) | Packages | Speed Grades |

|----------------|--------------|----------------------------|----------|--------------|

| Kintex-7       | XC7K325T CES | 3                          | All      | -1, -2       |

|                | XC7K410T CES | 0                          |          |              |

|                | XC7K480T CES | 1                          |          |              |

### Hardware Errata Details

This section provides a detailed description of each hardware issue known at the release time of this document.

### **Block RAM**

### Single Block RAM Location Not Available (Applies only to XC7K410T Devices)

For only the XC7K410T devices listed in Table 1, the 36K block RAM location at X4Y11 is not available for use. Use the CONFIG PROHIBIT=RAMB36\_X4Y11 constraint in the UCF file to prevent the design tools from using this block RAM location.

# XADC

For improved linearity, a new BitGen option (XADCEnhancedLinearity = ON¦OFF) must be set to ON (see <u>Answer Record</u> <u>45781</u> for more information). The specifications enhanced by this BitGen option are INL, THD, and SNR (see <u>Table 2</u>). By default this BitGen option is set to OFF. Existing XADC designs operate with the OFF setting.

Table 2 also lists errata for XADC DC accuracy specifications of Offset Error, Gain Error, Channel Matching, and On-Chip Reference Variation.

#### Table 2: XADC Errata

|                                    | XADC                       | DS182 (v1.3),<br>Kintov Z EDC As Data Sheat |                                                                                     |

|------------------------------------|----------------------------|---------------------------------------------|-------------------------------------------------------------------------------------|

| Parameter                          | XADCEnhancedLinearity = ON | XADCEnhancedLinearity = OFF                 | Kintex-7 FPGAs Data Sheet:<br>DC and Switching<br>Characteristics<br>Specifications |

| Integral Nonlinearity (INL)        | ±3 LSBs Max                | ±5 LSBs Max                                 | ±2 LSBs Max                                                                         |

| Total Harmonic Distortion<br>(THD) | 65 dB Тур                  | 65 dB Тур                                   | 75 dB Min                                                                           |

© Copyright 2012 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. PCI, PCI Express, PCIe, and PCI-X are trademarks of PCI-SIG. All other trademarks are the property of their respective owners.

#### Table 2: XADC Errata (Cont'd)

|                                               | XADC Errata                |                             | DS182 (v1.3),                                                                                 |  |

|-----------------------------------------------|----------------------------|-----------------------------|-----------------------------------------------------------------------------------------------|--|

| Parameter                                     | XADCEnhancedLinearity = ON | XADCEnhancedLinearity = OFF | <i>Kintex-7 FPGAs Data Sheet:<br/>DC and Switching<br/>Characteristics<br/>Specifications</i> |  |

| Signal to Noise Ratio (SNR)                   | 60 dB Min                  | 60 dB Typ                   | 60 dB Min                                                                                     |  |

| Channel Matching                              | 11 LSBs Max                | 11 LSBs Max                 | 10 LSBs Max                                                                                   |  |

| Offset Error                                  | ±6 LSBs Max                | ±6 LSBs Max                 | ±4 LSBs Max                                                                                   |  |

| Gain Error                                    | ±0.5% Max                  | ±0.5% Max                   | ±0.4% Max                                                                                     |  |

| On-Chip Reference<br>Variation <sup>(1)</sup> | 1.25V ±1.5% Max            | 1.25V ±1.5% Max             | 1.25V ±1.0% Max                                                                               |  |

#### Notes:

1. See <u>Answer Record 44971</u> for more information on the impact to XADC measurements when the on-chip reference source is used.

<u>DS182</u>, *Kintex-7 FPGAs Data Sheet: DC and Switching Characteristics* specifications will be updated to reflect the final device characterization.

## **GTX Transceivers**

### **Out-of-Band Signaling**

The GTX transceiver circuitry for out-of-band (OOB) signaling is always enabled.

#### CPLL Power Down

The GTX transceiver CPLL can become inoperative if conditions (1) and (2) persist for more than 8,000 hours:

- 1. Power has been applied to MGTAVCC and MGTAVTT.

- 2. The device is in one of the following states:

- a. The FPGA is not configured.

- b. The FPGA is configured, but the transceiver is uninstantiated.

- c. The transceiver is instantiated, but the CPLL is held in power-down state.

When the QPLL is being used, enabling each CPLL will consume up to 30 mA on the MGTAVTT supply and 20 mA on MGTAVCC. See <u>Answer Record 45360</u> for more details.

#### GTX Transceiver Power-Up/Power-Down

The GTX transceiver can become inoperative if MGTAVTT is within its recommended operating range and MGTAVCC is at a voltage less than 0.4V for more than 10,000 cumulative hours. An additional 100 mA per transceiver is drawn when MGTAVTT is within its recommended operating range and MGTAVCC is at a voltage less than 0.4V.

#### IEEE Std 1149.6 for GTX Transceivers

In the devices listed in Table 1, IEEE Std 1149.6 (ACJTAG) boundary-scan test commands EXTEST\_PULSE and EXTEST\_TRAIN are not supported.

### Power

#### Static Power

All power supplies can exhibit up to 25% higher static current compared to the static current reported in XPE.

Also, up to an additional 30 mA per used transceiver, and up to an additional 50 mA per powered transceiver quad can be consumed by the MGTAVCC supply. And, up to an additional 50 mA per powered transceiver quad can be consumed by the MGTAVTT supply.

# **Design Software Requirements**

The devices listed in Table 1, unless otherwise specified, require the following Xilinx Design Tools:

- Speed specification v1.03 (or later) of Xilinx® ISE® Design Suite 13.4 (or later) available at http://www.xilinx.com/support/download/.

- For GTX transceiver attribute updates, refer to <u>Answer Record 45360</u>.

- See Kintex-7 FPGA Answer Record 45696 for known issues and work-arounds for Xilinx Design Tools.

### **Operational Guidelines**

Designs targeting DDR3 data rates above 800 Mb/s should include an external V<sub>REF</sub>. For further details, refer to Answer Record 42036.

## Traceability

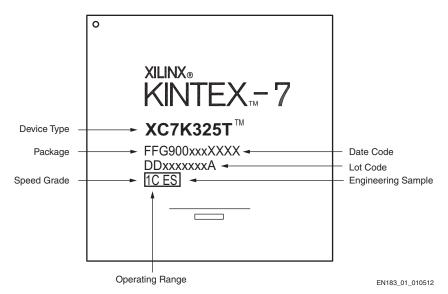

Figure 1 shows an example device top mark for the devices listed in Table 1.

Figure 1: Example Device Top Mark

### **Additional Questions or Clarifications**

For additional questions regarding these errata, contact Xilinx Technical Support: <u>http://www.xilinx.com/support/clearexpress/websupport.htm</u> or your Xilinx Sales Representative: http://www.xilinx.com/company/contact/index.htm.

# **Revision History**

The following table shows the revision history for this document:

| Date     | Version | Description of Revisions                                                                                                                                                                                                                                                                                              |

|----------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 01/17/12 | 1.0     | Initial Xilinx release.                                                                                                                                                                                                                                                                                               |

| 01/18/12 | 1.0.1   | Update document date to 2012.                                                                                                                                                                                                                                                                                         |

| 02/16/12 | 1.1     | Changed title; document pertains to all Kintex-7 CES devices. Updated Table 1 with XC7K480T CES and XC7K480T CES devices. Added Single Block RAM Location Not Available (Applies only to XC7K410T Devices). Removed the Dual Rank for DDR3 and DDR2 errata (no longer a deviation). Updated Table 2 and Static Power. |

## **Notice of Disclaimer**

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="http://www.xilinx.com/warranty.htm#critapps">http://www.xilinx.com/warranty.htm#critapps</a>.

# **Engineering Sample Disclaimer**

ENGINEERING SAMPLE (ES) DEVICES ARE MADE AVAILABLE SOLELY FOR PURPOSES OF RESEARCH, DEVELOPMENT AND PROTOTYPING. ALL ES DEVICES ARE SOLD "AS-IS" WITH NO WARRANTY OF ANY KIND, EITHER EXPRESS OR IMPLIED. XILINX DOES NOT WARRANT THAT ES DEVICES ARE FULLY VERIFIED, TESTED, OR WILL OPERATE IN ACCORDANCE WITH DATA SHEET SPECIFICATIONS. XILINX DISCLAIMS ANY OBLIGATIONS FOR TECHNICAL SUPPORT AND BUG FIXES. XILINX SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING WITHOUT LIMITATION DIRECT, INDIRECT, INCIDENTAL, SPECIAL, RELIANCE, OR CONSEQUENTIAL DAMAGES ARISING FROM OR IN CONNECTION WITH THE USE OF ES DEVICES IN ANY MANNER WHATSOEVER, EVEN IF XILINX HAS BEEN ADVISED OF THE POSSIBILITY THEREOF. XILINX MAKES NO REPRESENTATION THAT ES DEVICES PROVIDE ANY PARTICULAR FUNCTIONALITY, OR THAT ES DEVICES WILL MEET THE REQUIREMENTS OF A PARTICULAR USER APPLICATION. XILINX DOES NOT WARRANT THAT ES DEVICES ARE ERROR-FREE, NOR DOES XILINX MAKE ANY OTHER REPRESENTATIONS OR WARRANTIES, WHETHER EXPRESS OR IMPLIED, STATUTORY OR OTHERWISE, INCLUDING, WITHOUT LIMITATION, IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. THE FOREGOING STATES THE ENTIRE LIABILITY OF XILINX WITH RESPECT TO ES DEVICES.