# 7 Series DSP48E1 Slice

## **User Guide**

UG479 (v1.1) March 28, 2011

The information disclosed to you hereunder (the "Materials") is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials, or to advise you of any corrections or update. You may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at <a href="http://www.xilinx.com/warranty.htm">http://www.xilinx.com/warranty.htm</a>; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: <a href="http://www.xilinx.com/warranty.htm#critapps">http://www.xilinx.com/warranty.htm#critapps</a>.

#### **AUTOMOTIVE APPLICATIONS DISCLAIMER**

XILINX PRODUCTS ARE NOT DESIGNED OR INTENDED TO BE FAIL-SAFE, OR FOR USE IN ANY APPLICATION REQUIRING FAIL-SAFE PERFORMANCE, SUCH AS APPLICATIONS RELATED TO: (I) THE DEPLOYMENT OF AIRBAGS, (II) CONTROL OF A VEHICLE, UNLESS THERE IS A FAIL-SAFE OR REDUNDANCY FEATURE (WHICH DOES NOT INCLUDE USE OF SOFTWARE IN THE XILINX DEVICE TO IMPLEMENT THE REDUNDANCY) AND A WARNING SIGNAL UPON FAILURE TO THE OPERATOR, OR (III) USES THAT COULD LEAD TO DEATH OR PERSONAL INJURY. CUSTOMER ASSUMES THE SOLE RISK AND LIABILITY OF ANY USE OF XILINX PRODUCTS IN SUCH APPLICATIONS.

© Copyright 2011 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners.

## **Revision History**

The following table shows the revision history for this document.

| Date     | Version | Revision                                                                                                                              |

|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------|

| 03/01/11 | 1.0     | Initial Xilinx release.                                                                                                               |

| 03/28/11 | 1.1     | Added Chapter 1, Overview.  Updated DSP48E1 Slice Features. In Table 2-1, removed XC7K30T and added XC7K355T, XC7K420T, and XC7K480T. |

# Table of Contents

| Pre | eface: About This Guide                                     |          |

|-----|-------------------------------------------------------------|----------|

|     | Guide Contents                                              | 5        |

|     | Additional Documentation Resources                          | 5        |

|     | Additional Support Resources                                | 5        |

| Cha | apter 1: Overview                                           |          |

|     | DSP48E1 Slice Overview                                      | 7        |

|     | Features Relative to Prior Generations                      | 8        |

|     | Device Resources                                            | 8        |

|     | Design Recommendations for XST                              | 9        |

| Cha | apter 2: DSP48E1 Description and Specifics                  |          |

|     | DSP48E1 Slice Features                                      | 12       |

|     | Architectural Highlights of the 7 Series FPGA DSP48E1 Slice | 14<br>17 |

|     | DSP48E1 Slice Primitive                                     | 18       |

|     | Simplified DSP48E1 Slice Operation                          |          |

|     | DSP48E1 Slice Attributes                                    |          |

|     | Input Ports Output Ports                                    |          |

|     | Embedded Functions                                          |          |

|     | Single Instruction, Multiple Data (SIMD) Mode               |          |

|     | Pattern Detect Logic                                        | 40       |

| Cha | apter 3: DSP48E1 Design Considerations                      |          |

|     | Designing for Performance (to 600 MHz)                      | 45       |

|     | Designing for Power                                         | 45       |

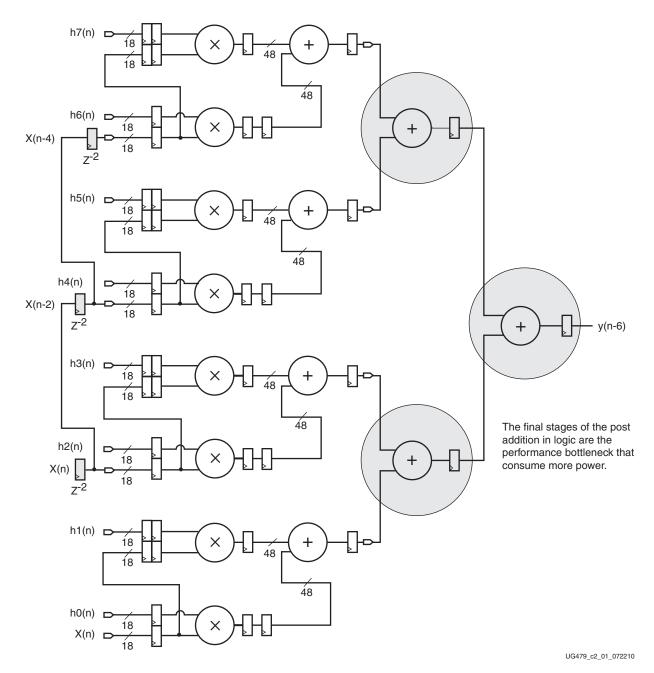

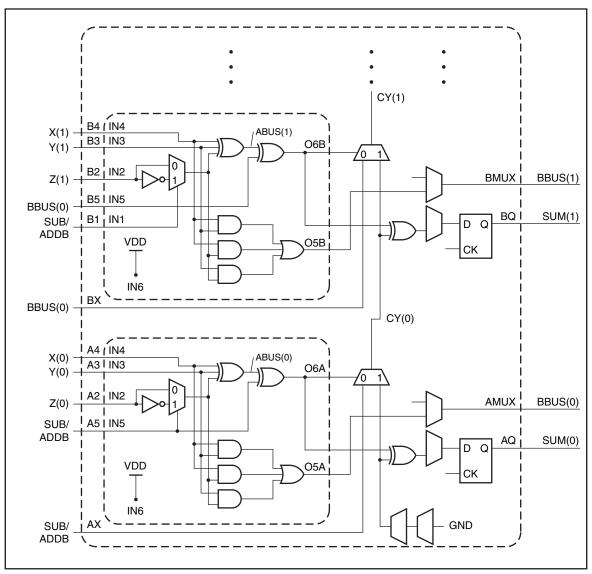

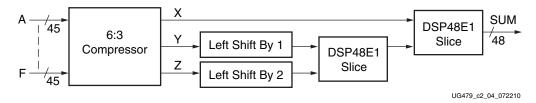

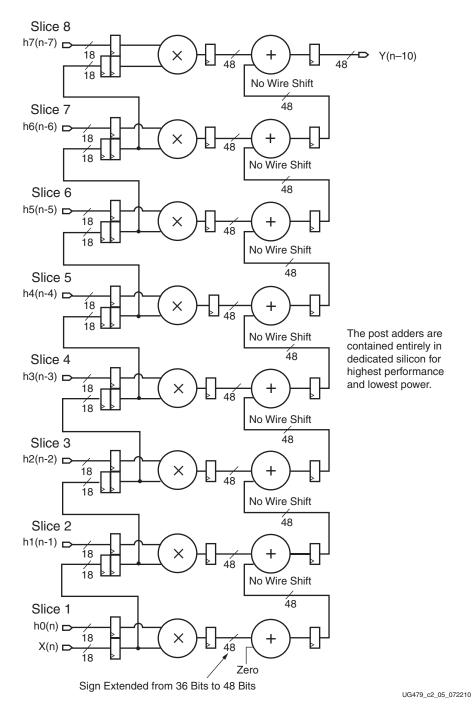

|     | Adder Tree vs. Adder Cascade                                |          |

|     | Adder Tree                                                  |          |

|     | Adder Cascade                                               |          |

|     | Connecting DSP48E1 Slices across Columns                    |          |

|     | Time Multiplexing the DSP48E1 Slice                         |          |

|     | Miscellaneous Notes and Suggestions                         |          |

|     | DSP48E1 Design Resources Pre-Adder Block Applications       |          |

|     | Pre-Adder Block Applications                                |          |

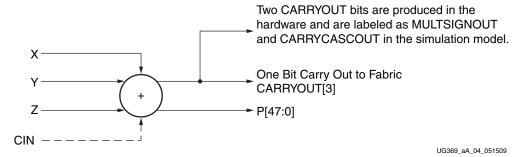

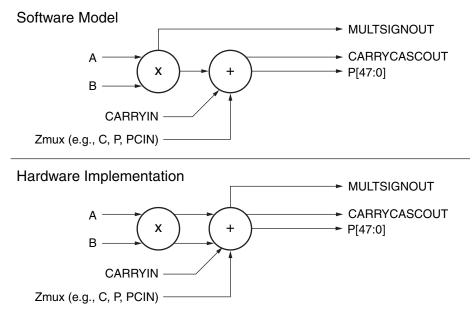

| MULTSIGNOUT and CARRYCASCOUT    | 55 |

|---------------------------------|----|

| Summary                         | 55 |

| Adder/Subtracter-only Operation |    |

| MACC Operation                  | 56 |

## About This Guide

Xilinx® 7 series FPGAs include three unified FPGA families that are all designed for lowest power to enable a common design to scale across families for optimal power, performance, and cost. The Artix<sup>TM</sup>-7 family is optimized for lowest cost and absolute power for the highest volume applications. The Virtex®-7 family is optimized for highest system performance and capacity. The Kintex<sup>TM</sup>-7 family is an innovative class of FPGAs optimized for the best price-performance. This guide serves as a technical reference describing the 7 series FPGAs DSP48E1 slice.

## **Guide Contents**

This manual contains the following chapters:

- Chapter 1, Overview

- Chapter 2, DSP48E1 Description and Specifics

- Chapter 3, DSP48E1 Design Considerations

- Appendix A, CARRYOUT, CARRYCASCOUT, and MULTSIGNOUT

## **Additional Documentation Resources**

The following documents provide useful supplemental material to this guide:

- 1. <u>UG193</u>, Virtex-5 FPGA XtremeDSP Design Considerations User Guide

- 2. DS180, 7 series FPGAs Overview

- 3. <u>UG687</u>, XST User Guide for Virtex-6, Spartan-6, and 7 Series Devices

- 4. 7 Series FPGA Data Sheets http://www.xilinx.com/support/documentation/7\_series.htm

- 5. UG073, XtremeDSP for Virtex-4 FPGAs User Guide

## **Additional Support Resources**

To search the database of silicon and software questions and answers or to create a technical support case in WebCase, see the Xilinx website at:

http://www.xilinx.com/support.

## Overview

#### **DSP48E1 Slice Overview**

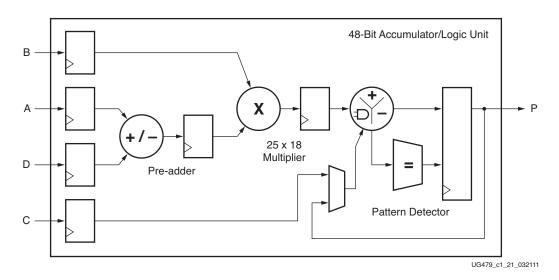

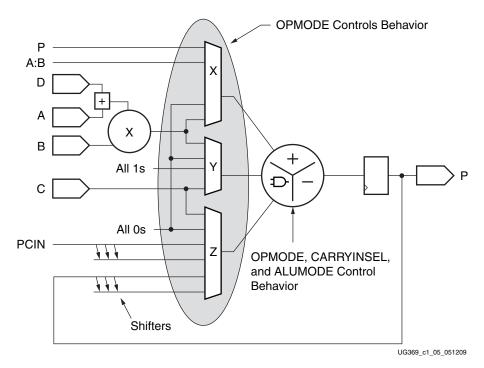

FPGAs are efficient for digital signal processing (DSP) applications because they can implement custom, fully parallel algorithms. DSP applications use many binary multipliers and accumulators that are best implemented in dedicated DSP slices. All 7 series FPGAs have many dedicated, full-custom, low-power DSP slices, combining high speed with small size while retaining system design flexibility. The DSP slices enhance the speed and efficiency of many applications beyond digital signal processing, such as wide dynamic bus shifters, memory address generators, wide bus multiplexers, and memory-mapped I/O register files. The basic functionality of the DSP48E1 slice is shown in Figure 1-1. For complete details, refer to Figure 2-1 and Chapter 2, DSP48E1 Description and Specifics.

Figure 1-1: Basic DSP48E1 Slice Functionality

Some highlights of the DSP functionality include:

- 25 × 18 two's-complement multiplier:

- Dynamic bypass

- 48-bit accumulator:

- Can be used as a synchronous up/down counter

- Power saving pre-adder:

- Optimizes symmetrical filter applications and reduces DSP slice requirements

- Single-instruction-multiple-data (SIMD) arithmetic unit:

- Dual 24-bit or quad 12-bit add/subtract/accumulate

- Optional logic unit:

- Can generate any one of ten different logic functions of the two operands

- Pattern detector:

- Convergent or symmetric rounding

- 96-bit-wide logic functions when used in conjunction with the logic unit

- Advanced features:

- Optional pipelining and dedicated buses for cascading

## **Features Relative to Prior Generations**

The 7 series FPGA DSP48E1 slice is functionally equivalent and fully compatible with the Virtex®-6 FPGA DSP48E1 slice, and a superset of the Virtex-5 FPGA DSP48E slice [Ref 1]. The 7 series FPGA DSP48E1 slice is effectively a superset of the DSP48A1 slice of the Spartan®-6 FPGA family with these differences:

- Wider functionality in DSP48E1 than DSP48A1:

- Multiplier width is improved from 18 x 18 in the Spartan-6 family to 25 x 18 in the 7 series

- The A register width is improved from 17 bits in the Spartan-6 family to 30 bits in the 7 series:

- A and B registers can be concatenated in the 7 series

- The A register feeds the pre-adder in the 7 series instead of the B register

- Cascading capability on both pipeline paths for larger multipliers and larger post-adders

- Unique features in DSP48E1 over DSP48A1:

- Arithmetic logic unit (ALU)

- SIMD mode

- Pattern detector

- 17-bit shifter

Virtex-6 family DSP designs migrate directly to the DSP resources of the 7 series. Migration of designs with cascaded DSP slices should consider the number of DSP slices per column. Spartan-6 family DSP designs also migrate to the 7 series, but designers should examine how to take advantage of the greater capability of the DSP48E1 slice. See UG429, 7 series FPGAs Migration User Guide for more information.

## **Device Resources**

The DSP resources are unified across all the 7 series families, providing a common architecture that improves software efficiency, IP implementation, and design migration. The number of DSP48E1 slices and the ratio between DSP and other device resources differentiates the 7 series families. Migration between the 7 series families does not require any design changes for the DSP48E1.

See Table 2-1 for the available DSP48E1 resources for the Kintex<sup>TM</sup>-7 FPGAs. Refer to 7 *Series FPGAs Overview* [Ref 2] for the most up-to-date information on all the 7 series FPGAs.

## **Design Recommendations for XST**

Many DSP designs are well suited for the 7 series architecture. To obtain best use of the architecture, the underlying features and capabilities need to be understood so that design entry code can take advantage of these resources. DSP48E1 resources are used automatically for most DSP functions and many arithmetic functions. In most cases, DSP resources should be inferred. If XST is used for synthesis, it is suggested to consult the "XST HDL Coding Techniques" chapter of XST User Guide for Virtex-6, Spartan-6, and 7 Series Devices [Ref 3]. Instantiation can be used to directly access specific DSP48E1 slice features. Recommendations for using DSP48E1 slices include:

- Use signed values in HDL source

- Pipeline for performance and lower power, both in the DSP48E1 slice and fabric

- Use the configurable logic block (CLB) carry logic to implement small multipliers, adders, and counters

- Use CLB SRLs, CLB distributed RAM, and/or block RAM to store filter coefficients

- Set USE\_MULT to NONE when using only the adder/logic unit to save power

- Cascade using the dedicated resources rather than fabric, keeping usage to one column for highest performance and lowest power

- Consider using time multiplexing for the design

For more information on design techniques, see Chapter 3, DSP48E1 Design Considerations.

# DSP48E1 Description and Specifics

This chapter provides technical details of the DSP element available in 7 series FPGAs, the DSP48E1 slice.

The DSP48E1 slice provides improved flexibility and utilization, improved efficiency of applications, reduced overall power consumption, and increased maximum frequency. The high performance allows designers to implement multiple slower operations in a single DSP48E1 slice using time-multiplexing methods.

The DSP48E1 slice supports many independent functions. These functions include multiply, multiply accumulate (MACC), multiply add, three-input add, barrel shift, wide-bus multiplexing, magnitude comparator, bit-wise logic functions, pattern detect, and wide counter. The architecture also supports cascading multiple DSP48E1 slices to form wide math functions, DSP filters, and complex arithmetic without the use of general FPGA logic.

This chapter contains the following sections:

- DSP48E1 Slice Features

- Architectural Highlights of the 7 Series FPGA DSP48E1 Slice

- Simplified DSP48E1 Slice Operation

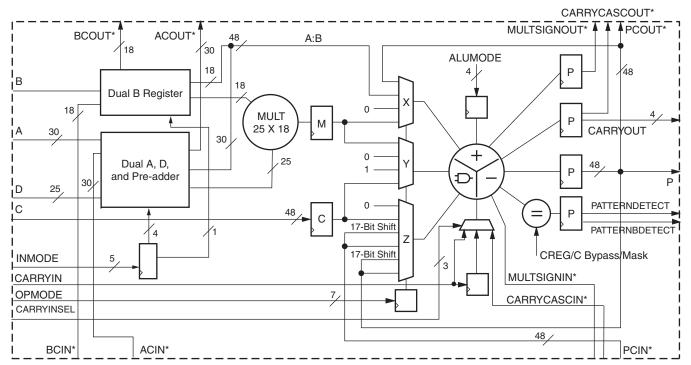

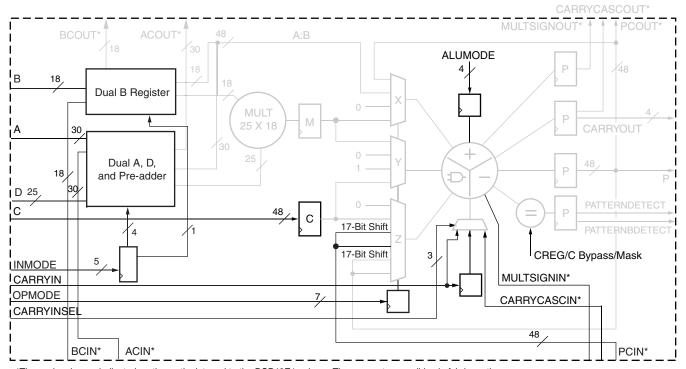

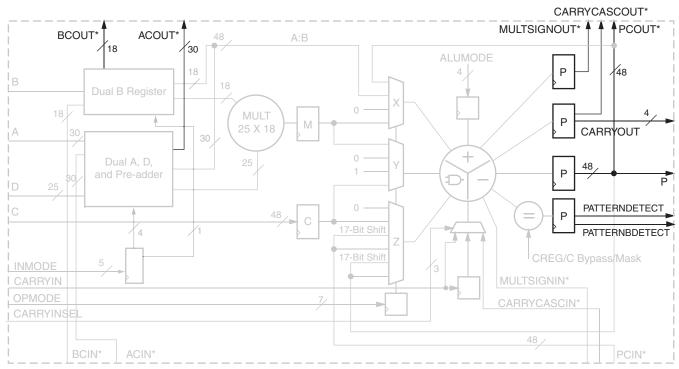

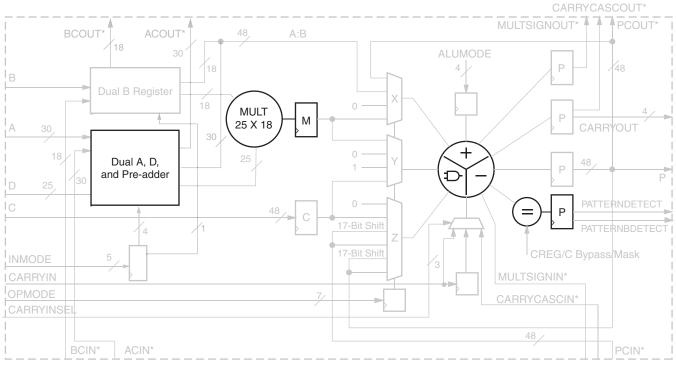

The 7 series FPGA DSP48E1 slice is shown in Figure 2-1. The slice is functionally equivalent to the Virtex®-6 FPGA DSP48E1 slice and is an extension of the DSP48E slice in Virtex-5 devices, described in the *Virtex-5 FPGA XtremeDSP Design Considerations User Guide* [Ref 1].

\*These signals are dedicated routing paths internal to the DSP48E1 column. They are not accessible via fabric routing resources.

UG369\_c1\_01\_052109

Figure 2-1: 7 Series FPGA DSP48E1 Slice

### **DSP48E1 Slice Features**

This section describes the 7 series FPGA DSP48E1 slice features.

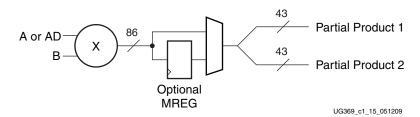

The DSP slice consists of a multiplier followed by an accumulator. At least three pipeline registers are required for both multiply and multiply-accumulate operations to run at full speed. The multiply operation in the first stage generates two partial products that need to be added together in the second stage.

When only one or two registers exist in the multiplier design, the M register should always be used to save power and improve performance.

Add/Sub and Logic Unit operations require at least two pipeline registers (input, output) to run at full speed.

The cascade capabilities of the DSP slice are extremely efficient at implementing highspeed pipelined filters built on the adder cascades instead of adder trees.

Multiplexers are controlled with dynamic control signals, such as OPMODE, ALUMODE, and CARRYINSEL, enabling a great deal of flexibility. Designs using registers and dynamic opmodes are better equipped to take advantage of the DSP slice's capabilities than combinatorial multiplies.

In general, the DSP slice supports both sequential and cascaded operations due to the dynamic OPMODE and cascade capabilities. Fast Fourier Transforms (FFTs), floating point, computation (multiply, add/sub, divide), counters, and large bus multiplexers are some applications of the DSP slice.

Additional capabilities of the DSP slice include synchronous resets and clock enables, dual A input pipeline registers, pattern detection, Logic Unit functionality, single

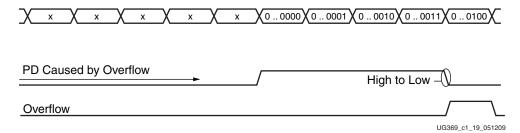

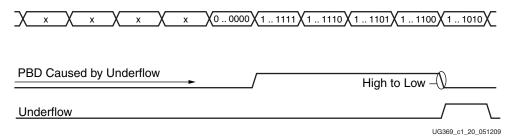

instruction/multiple data (SIMD) functionality, and MACC and Add-Acc extension to 96 bits. The DSP slice supports convergent and symmetric rounding, terminal count detection and auto-resetting for counters, and overflow/underflow detection for sequential accumulators.

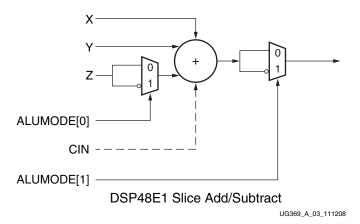

ALU functions are identical in 7 series FPGA DSP48E1 slice as in the Virtex-6 FPGA DSP48E1 slice. See ALUMODE Inputs, page 32 for more information.

## Architectural Highlights of the 7 Series FPGA DSP48E1 Slice

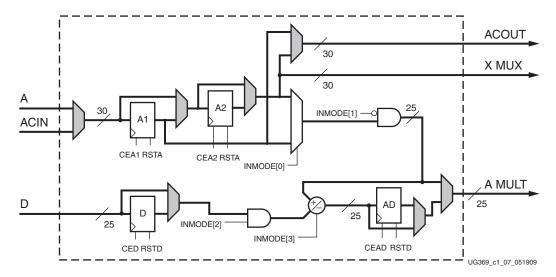

The 7 series FPGA DSP48E1 slice is functionally equivalent to the Virtex-6 FPGA DSP48E1. The 7 series FPGA DSP48E1 slice contains a pre-adder after the A register with a 25-bit input vector called D. The D register can be used either as the pre-adder register or an alternate input to the multiplier. The DSP48E1 specific features are highlighted in Figure 2-2.

Figure 2-2: Hierarchical View of the 7 Series DSP48E1 Slice Input Registers and Pre-adder

The features in the 7 series FPGA DSP48E1 slice are:

- 25-bit pre-adder with D register to enhance the capabilities of the A path

- INMODE control supports balanced pipelining when dynamically switching between multiply (A\*B) and add operations (A:B)

- 25 x 18 multiplier

- 30-bit A input of which the lower 25 bits feed the A input of the multiplier, and the entire 30-bit input forms the upper 30 bits of the 48-bit A:B concatenate internal bus.

- Cascading A and B input

- Semi-independently selectable pipelining between direct and cascade paths

- Separate clock enables two-deep A and B set of input registers

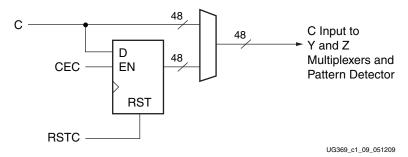

- Independent C input and C register with independent reset and clock enable.

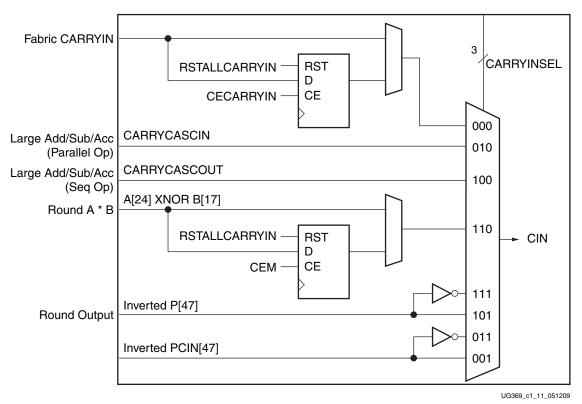

- CARRYCASCIN and CARRYCASCOUT internal cascade signals to support 96-bit accumulators/adders/subtracters in two DSP48E1 slices

- MULTSIGNIN and MULTSIGNOUT internal cascade signals with special OPMODE setting to support a 96-bit MACC extension

- Single Instruction Multiple Data (SIMD) Mode for three-input adder/subtracter which precludes use of multiplier in first stage

- Dual 24-bit SIMD adder/subtracter/accumulator with two separate CARRYOUT signals

- Quad 12-bit SIMD adder/subtracter/accumulator with four separate CARRYOUT signals

- 48-bit logic unit

- Bit-wise logic operations two-input AND, OR, NOT, NAND, NOR, XOR, and XNOR

- Logic unit mode dynamically selectable via ALUMODE

- Pattern detector

- Overflow/underflow support

- Convergent rounding support

- · Terminal count detection support and auto resetting

- Cascading 48-bit P bus supports internal low-power adder cascade

- The 48-bit P bus allows for 12-bit/QUAD or 24-bit/DUAL SIMD adder cascade support

- Optional 17-bit right shift to enable wider multiplier implementation

- Dynamic user-controlled operating modes

- 7-bit OPMODE control bus provides X, Y, and Z multiplexer select signals

- Carry in for the second stage adder

- Support for rounding

- Support for wider add/subtracts

- 3-bit CARRYINSEL multiplexer

- Carry out for the second stage adder

- Support for wider add/subtracts

- Available for each SIMD adder (up to four)

- Cascaded CARRYCASCOUT and MULTSIGNOUT allows for MACC extensions up to 96 bits

- Optional input, pipeline, and output/accumulate registers

- Optional control registers for control signals (OPMODE, ALUMODE, and CARRYINSEL)

- Independent clock enable and resets for greater flexibility

- To save power when the first stage multiplier is not being used, the USE\_MULT attribute allows the customer to gate off internal multiplier logic.

Each DSP48E1 slice has a two-input multiplier followed by multiplexers and a three-input adder/subtracter/accumulator. The DSP48E1 multiplier has asymmetric inputs and accepts an 18-bit two's complement operand and a 25-bit two's complement operand. The multiplier stage produces a 43-bit two's complement result in the form of two partial products. These partial products are sign-extended to 48 bits in the X multiplexer and Y multiplexer and fed into three-input adder for final summation. This results in a 43-bit multiplication output, which has been sign-extended to 48 bits. Therefore, when the multiplier is used, the adder effectively becomes a two-input adder.

The second stage adder/subtracter accepts three 48-bit, two's complement operands and produces a 48-bit, two's complement result when the multiplier is bypassed by setting USE\_MULT attribute to NONE and with the appropriate OPMODE setting. In SIMD mode, the 48-bit adder/subtracter also supports dual 24-bit or quad 12-bit SIMD arithmetic operations with CARRYOUT bits. In this configuration, bitwise logic operations on two 48-bit binary numbers are also supported with dynamic ALUMODE control signals.

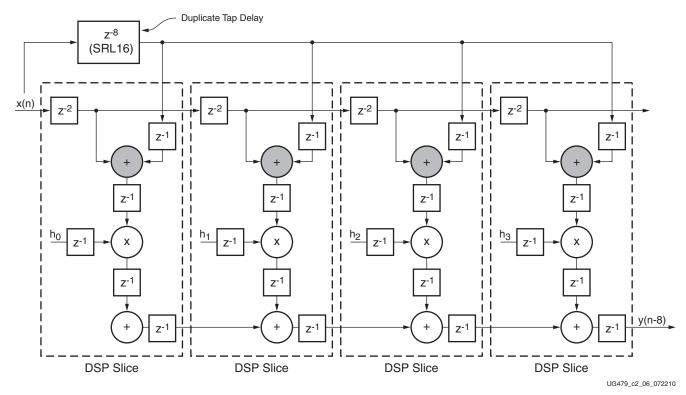

Higher level DSP functions are supported by cascading individual DSP48E1 slices in a DSP48E1 column. Two datapaths (ACOUT and BCOUT) and the DSP48E1 slice outputs (PCOUT, MULTSIGNOUT, and CARRYCASCOUT) provide the cascade capability. The ability to cascade datapaths is useful in filter designs. For example, a Finite Impulse Response (FIR) filter design can use the cascading inputs to arrange a series of input data samples and the cascading outputs to arrange a series of partial output results. The ability to cascade provides a high-performance and low-power implementation of DSP filter functions because the general routing in the fabric is not used.

The C input port allows the formation of many 3-input mathematical functions, such as 3-input addition or 2-input multiplication with an addition. One subset of this function is the valuable support of symmetrically rounding a multiplication toward zero or toward infinity. The C input together with the pattern detector also supports convergent rounding.

For multi-precision arithmetic, the DSP48E1 slice provides a right wire shift by 17. Thus, a partial product from one DSP48E1 slice can be right justified and added to the next partial product computed in an adjacent DSP48E1 slice. Using this technique, the DSP48E1 slices can be used to build bigger multipliers.

Programmable pipelining of input operands, intermediate products, and accumulator outputs enhances throughput. The 48-bit internal bus (PCOUT/PCIN) allows for aggregation of DSP slices in a single column. Fabric logic is needed when spanning multiple columns.

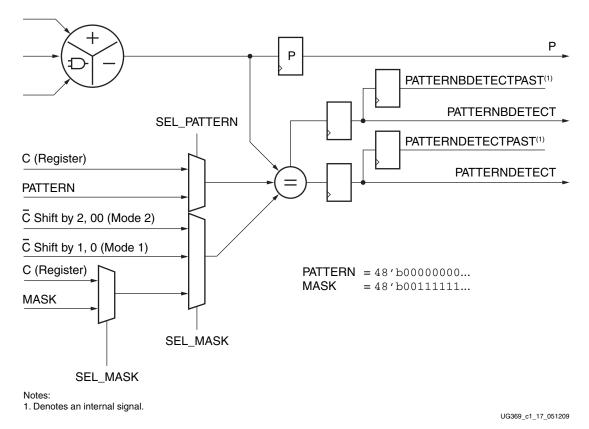

The pattern detector at the output of the DSP48E1 slice provides support for convergent rounding, overflow/underflow, block floating point, and support for accumulator terminal count (counter auto reset). The pattern detector can detect if the output of the DSP48E1 slice matches a pattern, as qualified by a mask.

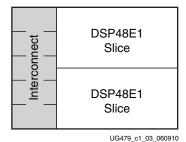

#### DSP48E1 Tile and Interconnect

Two DSP48E1 slices and dedicated interconnect form a DSP48E1 tile (see Figure 2-3). The DSP48E1 tiles stack vertically in a DSP48E1 column. The height of a DSP48E1 tile is the same as five configurable logic blocks (CLBs) and also matches the height of one block RAM. The block RAM in 7 series devices can be split into two 18K block RAMs. Each DSP48E1 slice aligns horizontally with an 18K block RAM. The 7 series devices have from 2 to 22 DSP48E1 columns.

Figure 2-3: DSP48E1 Interconnect and Relative Dedicated Element Sizes

The 7 series devices offer from 40 to 3,500+ DSP slices per device, yielding an impressive processing power in the range of tens of GMACS up to thousands of GMACS (peak), enabling very intensive DSP applications. Table 2-1 shows the number of DSP48E1 slices for each device in the Kintex $^{\text{TM}}$ -7 family. Refer to the product tables on  $\underline{\text{xilinx.com}}$  for information on the Artix $^{\text{TM}}$ -7 and Virtex-7 families.

Table 2-1: Number of DSP48E1 Slices per Kintex-7 Device

| Device   | Total DSP48E1 Slices per<br>Device | Number of DSP48E1 Columns per Device | Number of DSP48E1 Slices per Column |

|----------|------------------------------------|--------------------------------------|-------------------------------------|

| XC7K70T  | 240                                | 3                                    | 80                                  |

| XC7K160T | 600                                | 6                                    | 100                                 |

| XC7K325T | 840                                | 6                                    | 140                                 |

| XC7K355T | 1,440                              | 12                                   | 120                                 |

| XC7K410T | 1,540                              | 11                                   | 140                                 |

| XC7K420T | 1,680                              | 12                                   | 140                                 |

| XC7K480T | 1,920                              | 12                                   | 160                                 |

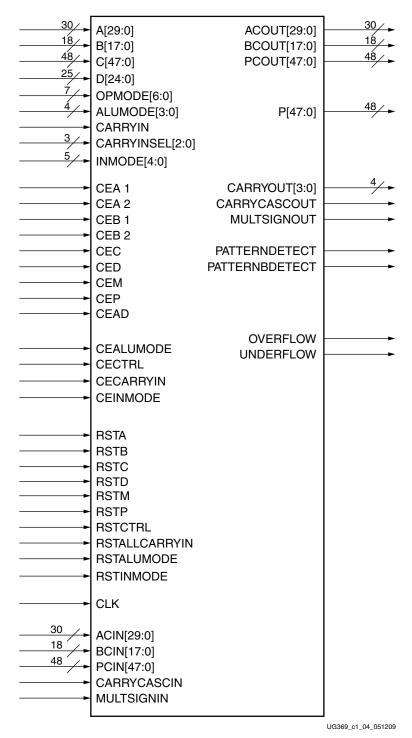

## **DSP48E1 Slice Primitive**

Figure 2-4 shows the DSP48E1 primitive. It also shows the input and output ports of the DSP48E1 slice along with the bit width of each port. The port definitions are in Table 2-2.

Figure 2-4: DSP48E1 Slice Primitive

Table 2-2: DSP48E1 Port Descriptions

| Name                        | Direction | Bit Width | Description                                                                                                                                                                                                          |  |

|-----------------------------|-----------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| A <sup>(1)</sup>            | In        | 30        | A[24:0] is the A input of the multiplier. A[29:0] are the most significant bits (MSBs) of the A:B concatenated input to the second-stage adder/subtracter or logic function or a 25-bit data input to the pre-adder. |  |

| ACIN <sup>(2)</sup>         | In        | 30        | Cascaded data input from ACOUT of previous DSP48E1 slice (muxed with A).                                                                                                                                             |  |

| ACOUT <sup>(2)</sup>        | Out       | 30        | Cascaded data output to ACIN of next DSP48E1 slice.                                                                                                                                                                  |  |

| ALUMODE                     | In        | 4         | Controls the selection of the logic function in the DSP48E1 slice (see Table 2-13, page 39).                                                                                                                         |  |

| B <sup>(1)</sup>            | In        | 18        | The B input of the multiplier. B[17:0] are the least significant bits (LSBs) of the A:B concatenated input to the second-stage adder/subtracter or logic function.                                                   |  |

| BCIN <sup>(2)</sup>         | In        | 18        | Cascaded data input from BCOUT of previous DSP48E1 slice (muxed with B).                                                                                                                                             |  |

| BCOUT <sup>(2)</sup>        | Out       | 18        | Cascaded data output to BCIN of next DSP48E1 slice.                                                                                                                                                                  |  |

| C <sup>(1)</sup>            | In        | 48        | Data input to the second-stage adder/subtracter, pattern detector, or logic function.                                                                                                                                |  |

| CARRYCASCIN <sup>(2)</sup>  | In        | 1         | Cascaded carry input from CARRYCASCOUT of previous DSP48E1 slice.                                                                                                                                                    |  |

| CARRYCASCOUT <sup>(2)</sup> | Out       | 1         | Cascaded carry output to CARRYCASCIN of next DSP48E1 slice. This signal is internally fed back into the CARRYINSEL multiplexer input of the same DSP48E1 slice.                                                      |  |

| CARRYIN                     | In        | 1         | Carry input from the FPGA logic.                                                                                                                                                                                     |  |

| CARRYINSEL                  | In        | 3         | Selects the carry source (see Table 2-11).                                                                                                                                                                           |  |

| CARRYOUT                    | Out       | 4         | 4-bit carry output from each 12-bit field of the accumulate/adder/logic unit. Normal 48-bit operation uses only CARRYOUT3. SIMD operation can use four carry out bits (CARRYOUT[3:0]).                               |  |

| CEA1                        | In        | 1         | Clock enable for the first A (input) register. This port is only used if $AREG = 2$ or $INMODE0 = 1$ .                                                                                                               |  |

| CEA2                        | In        | 1         | Clock enable for the second A (input) register. This port is only used if AREG = 1 or 2.                                                                                                                             |  |

| CEAD                        | In        | 1         | Clock enable for the pre-adder output AD pipeline register.                                                                                                                                                          |  |

| CEALUMODE                   | In        | 1         | Clock enable for ALUMODE (control inputs) registers.                                                                                                                                                                 |  |

| CEB1                        | In        | 1         | Clock enable for the first B (input) register. This port is only used if $BREG = 2$ or $INMODE4 = 1$ .                                                                                                               |  |

| CEB2                        | In        | 1         | Clock enable for the second B (input) register. This port is only used if BREG = 1 or 2.                                                                                                                             |  |

| CEC                         | In        | 1         | Clock enable for the C (input) register.                                                                                                                                                                             |  |

| CECARRYIN                   | In        | 1         | Clock enable for the CARRYIN (input from FPGA logic) register.                                                                                                                                                       |  |

Table 2-2: DSP48E1 Port Descriptions (Cont'd)

| Name                       | Direction | Bit Width | Description                                                                                                                                                                                                       |  |

|----------------------------|-----------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CECTRL                     | In        | 1         | Clock enable for the OPMODE and CARRYINSEL (control inputs) registers.                                                                                                                                            |  |

| CED                        | In        | 1         | Clock enable for the D (input) register.                                                                                                                                                                          |  |

| CEINMODE                   | In        | 1         | Clock enable for the INMODE control input registers.                                                                                                                                                              |  |

| CEM                        | In        | 1         | Clock enable for the post-multiply M (pipeline) register and the internal multiply round CARRYIN register.                                                                                                        |  |

| СЕР                        | In        | 1         | Clock enable for the P (output) register.                                                                                                                                                                         |  |

| CLK                        | In        | 1         | This port is the DSP48E1 input clock, common to all internal registers and flip-flops.                                                                                                                            |  |

| D <sup>(1)</sup>           | In        | 25        | 25-bit data input to the pre-adder or alternative input to the multiplier. The pre-adder implements D $\pm$ A as determined by the INMODE3 signal.                                                                |  |

| INMODE                     | In        | 5         | These five control bits select the functionality of the pre-adder, the A, B, and D inputs, and the input registers. These bits should default to 5 ' b00000 if left unconnected. These are optionally invertible. |  |

| MULTSIGNIN <sup>(2)</sup>  | In        | 1         | Sign of the multiplied result from the previous DSP48E1 slice for MACC extension.                                                                                                                                 |  |

| MULTSIGNOUT <sup>(2)</sup> | Out       | 1         | Sign of the multiplied result cascaded to the next DSP48E1 slice for MACC extension.                                                                                                                              |  |

| OPMODE                     | In        | 7         | Controls the input to the X, Y, and Z multiplexers in the DSP48E1 slice (see Table 2-7, Table 2-8, and Table 2-9).                                                                                                |  |

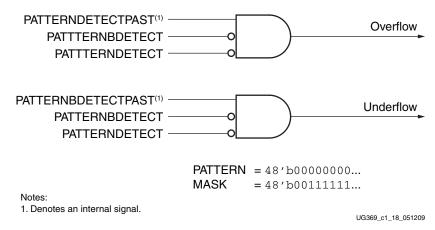

| OVERFLOW                   | Out       | 1         | Overflow indicator when used with the appropriate setting of the pattern detector.                                                                                                                                |  |

| P                          | Out       | 48        | Data output from second stage adder/subtracter or logic function.                                                                                                                                                 |  |

| PATTERNBDETECT             | Out       | 1         | Match indicator between P[47:0] and the pattern bar.                                                                                                                                                              |  |

| PATTERNDETECT              | Out       | 1         | Match indicator between P[47:0] and the pattern.                                                                                                                                                                  |  |

| PCIN <sup>(2)</sup>        | In        | 48        | Cascaded data input from PCOUT of previous DSP48E1 slice to adder.                                                                                                                                                |  |

| PCOUT <sup>(2)</sup>       | Out       | 48        | Cascaded data output to PCIN of next DSP48E1 slice.                                                                                                                                                               |  |

| RSTA                       | In        | 1         | Reset for both A (input) registers.                                                                                                                                                                               |  |

| RSTALLCARRYIN              | In        | 1         | Reset for the Carry (internal path) and the CARRYIN register.                                                                                                                                                     |  |

| RSTALUMODE                 | In        | 1         | Reset for ALUMODE (control inputs) registers.                                                                                                                                                                     |  |

| RSTB                       | In        | 1         | Reset for both B (input) registers.                                                                                                                                                                               |  |

| RSTC                       | In        | 1         | Reset for the C (input) register.                                                                                                                                                                                 |  |

| RSTCTRL                    | In        | 1         | Reset for OPMODE and CARRYINSEL (control inputs) registers.                                                                                                                                                       |  |

| RSTD                       | In        | 1         | Reset for the D (input) register and for the pre-adder (output) AD pipeline register.                                                                                                                             |  |

| RSTINMODE                  | In        | 1         | Reset for the INMODE (control input) registers.                                                                                                                                                                   |  |

Table 2-2: DSP48E1 Port Descriptions (Cont'd)

| Name      | Direction | Bit Width | Description                                                                         |

|-----------|-----------|-----------|-------------------------------------------------------------------------------------|

| RSTM      | In        | 1         | Reset for the M (pipeline) register.                                                |

| RSTP      | In        | 1         | Reset for the P (output) register.                                                  |

| UNDERFLOW | Out       | 1         | Underflow indicator when used with the appropriate setting of the pattern detector. |

#### Notes:

- 1. When these data ports are not in used and to reduce leakage power dissipation, the data port input signals must be tied High, the port input register must be selected, and the CE and RST input control signals must be tied Low. An example of unused C port recommended settings would be setting C[47:0] = all ones, CREG = 1, CEC = 0, and RSTC = 0.

- 2. These signals are dedicated routing paths internal to the DSP48E1 column. They are not accessible via fabric routing resources.

- 3. All signals are active High.

## Simplified DSP48E1 Slice Operation

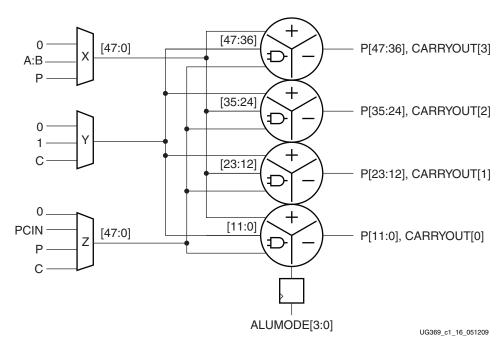

The math portion of the DSP48E1 slice consists of a 25-bit pre-adder, a 25-bit by 18-bit two's complement multiplier followed by three 48-bit datapath multiplexers (with outputs X, Y, and Z). This is followed by a three-input adder/subtracter or two-input logic unit (see Figure 2-5). When using two-input logic unit, the multiplier cannot be used.

The data and control inputs to the DSP48E1 slice feed the arithmetic and logic stages. The A and B data inputs can optionally be registered one or two times to assist the construction of different, highly pipelined, DSP application solutions. The D path and the AD path can each be registered once. The other data inputs and the control inputs can be optionally registered once. Full-speed operation is 600 MHz when using the pipeline registers. More detailed timing information is available in Chapter 3, DSP48E1 Design Considerations.

In its most basic form, the output of the adder/subtracter/logic unit is a function of its inputs. The inputs are driven by the upstream multiplexers, carry select logic, and multiplier array.

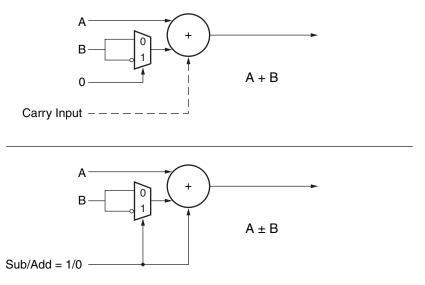

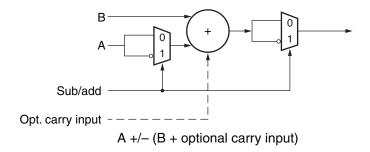

Equation 2-1 summarizes the combination of X, Y, Z, and CIN by the adder/subtracter. The CIN, X multiplexer output, and Y multiplexer output are always added together. This combined result can be selectively added to or subtracted from the Z multiplexer output. The second option is obtained by setting the ALUMODE to 0001.

Adder/Sub Out =

$$(Z \pm (X + Y + CIN))$$

or  $(-Z + (X + Y + CIN) - 1)$  Equation 2-1

A typical use of the slice is where A and B inputs are multiplied and the result is added to or subtracted from the C register. More detailed operations based on control and data inputs are described in later sections. Selecting the multiplier function consumes both X and Y multiplexer outputs to feed the adder. The two 43-bit partial products from the multiplier are sign extended to 48 bits before being sent to the adder/subtracter.

When not using the first stage multiplier, the 48-bit, dual input, bit-wise logic function implements AND, OR, NOT, NAND, NOR, XOR, and XNOR. The inputs to these functions are A:B, C, P, or PCIN selected through the X and Z multiplexers, with the Y multiplexer selecting either all 1s or all 0s depending on logic operation.

The output of the adder/subtracter or logic unit feeds the pattern detector logic. The pattern detector allows the DSP48E1 slice to support Convergent Rounding, Counter Autoreset when a count value has been reached, and Overflow/Underflow/Saturation in accumulators. In conjunction with the logic unit, the pattern detector can be extended to

perform a 48-bit dynamic comparison of two 48-bit fields. This enables functions such as A:B NAND C = 0, or A:B (bit-wise logic) C = 0 Pattern to be implemented.

Figure 2-5 shows the DSP48E1 slice in a very simplified form. The seven OPMODE bits control the selects of X, Y, and Z multiplexers, feeding the inputs to the adder/subtracter or logic unit. In all cases, the 43-bit partial product data from the multiplier to the X and Y multiplexers is sign extended, forming 48-bit input datapaths to the adder/subtracter. Based on 43-bit operands and a 48-bit accumulator output, the number of *guard bits* (i.e., bits available to guard against overflow) is 5. To extend the number of MACC operations, the MACC\_EXTEND feature should be used, which allows the MACC to extend to 96 bits with two DSP48E1 slices. If A port is limited to 18 bits (sign-extended to 25), then there are 12 guard bits for the MACC. The CARRYOUT bits are invalid during multiply operations. Combinations of OPMODE, ALUMODE, CARRYINSEL, and CARRYIN control the function of the adder/subtracter or logic unit.

Figure 2-5: Simplified DSP Slice Operation

## **DSP48E1 Slice Attributes**

The synthesis attributes for the DSP48E1 slice are described in this section. The attributes call out pipeline registers in the control and datapaths. The value of the attribute sets the number of pipeline registers. See Table 2-3.

Table 2-3: Attribute Setting Description

| Attribute Name                   | Settings (Default)                                                                                                                                                                                                                                    | Attribute Description                                                                                                                                                                                                                                          |  |  |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Register Control Attribut        | es                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                |  |  |

| ACASCREG                         | 0, 1, 2 (1)                                                                                                                                                                                                                                           | In conjunction with AREG, selects the number of A input registers on the A cascade path, ACOUT. This attribute must be equal to or one less than the AREG value:  AREG = 0: ACASCREG must be 0  AREG = 1: ACASCREG must be 1  AREG = 2: ACASCREG can be 1 or 2 |  |  |

| ADREG                            | 0, 1 (1)                                                                                                                                                                                                                                              | Selects the number of AD pipeline registers.                                                                                                                                                                                                                   |  |  |

| ALUMODEREG                       | 0, 1 (1)                                                                                                                                                                                                                                              | Selects the number of ALUMODE input registers.                                                                                                                                                                                                                 |  |  |

| AREG                             | 0, 1, 2 (1)                                                                                                                                                                                                                                           | Selects the number of A input registers.                                                                                                                                                                                                                       |  |  |

| BCASCREG                         | 0, 1, 2 (1)  In conjunction with BREG, selects the number of registers on the B cascade path, BCOUT. This attrequal to or one less than the BREG value:  BREG = 0: BCASCREG must be 0  BREG = 1: BCASCREG must be 1  BREG = 2: BCASCREG can be 1 or 2 |                                                                                                                                                                                                                                                                |  |  |

| BREG                             | 0, 1, 2 (1)                                                                                                                                                                                                                                           | Selects the number of B input registers.                                                                                                                                                                                                                       |  |  |

| CARRYINREG                       | 0, 1 (1)                                                                                                                                                                                                                                              | Selects the number of fabric CARRYIN input registers.                                                                                                                                                                                                          |  |  |

| CARRYINSELREG 0, 1 (1)           |                                                                                                                                                                                                                                                       | Selects the number of CARRYINSEL input registers.                                                                                                                                                                                                              |  |  |

| CREG 0, 1 (1)                    |                                                                                                                                                                                                                                                       | Selects the number of C input registers.                                                                                                                                                                                                                       |  |  |

| DREG 0, 1 (1)                    |                                                                                                                                                                                                                                                       | Selects the number of D input registers.                                                                                                                                                                                                                       |  |  |

| INMODEREG                        | 0, 1 (1)                                                                                                                                                                                                                                              | Selects the number of INMODE input registers.                                                                                                                                                                                                                  |  |  |

| MREG                             | 0, 1 (1)                                                                                                                                                                                                                                              | Selects the number of M pipeline registers.                                                                                                                                                                                                                    |  |  |

| OPMODEREG                        | 0, 1 (1)                                                                                                                                                                                                                                              | Selects the number of OPMODE input registers.                                                                                                                                                                                                                  |  |  |

| PREG                             | 0, 1 (1)                                                                                                                                                                                                                                              | Selects the number of P output registers (also used by CARRYOUT/ PATTERN_DETECT/ CARRYCASCOUT/ MULTSIGNOUT, etc.).                                                                                                                                             |  |  |

| Feature Control Attribute        | es                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                |  |  |

| A_INPUT DIRECT, CASCADE (DIRECT) |                                                                                                                                                                                                                                                       | Selects the input to the A port between parallel input (DIRECT) or the cascaded input from the previous slice (CASCADE).                                                                                                                                       |  |  |

| B_INPUT                          | DIRECT, CASCADE<br>(DIRECT)                                                                                                                                                                                                                           | Selects the input to the B port between parallel input (DIRECT) or the cascaded input from the previous slice (CASCADE).                                                                                                                                       |  |  |

| USE_DPORT                        | E_DPORT TRUE, FALSE (FALSE) Determines whether the pre-adder and t not.                                                                                                                                                                               |                                                                                                                                                                                                                                                                |  |  |

Table 2-3: Attribute Setting Description (Cont'd)

| Attribute Name             | Settings (Default)                                         | Attribute Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------|------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| USE_MULT                   | NONE, MULTIPLY,<br>DYNAMIC (MULTIPLY)                      | Selects usage of the multiplier. Set to NONE to save power when using only the Adder/Logic Unit.  The DYNAMIC setting indicates that the user is switching between A*B and A:B operations on the fly and therefore needs to get the worst-case timing of the two paths.                                                                                                                                                                       |

| USE_SIMD                   | ONE48, TWO24, FOUR12<br>(ONE48)                            | Selects the mode of operation for the adder/subtracter. The attribute setting can be one 48-bit adder mode (ONE48), two 24-bit adder mode (TWO24), or four 12-bit adder mode (FOUR12). Selecting ONE48 mode is compatible with Virtex-6 devices DSP48 operation and is not actually a true SIMD mode. Typical Multiply-Add operations are supported when the mode is set to ONE48.                                                            |

|                            |                                                            | When either TWO24 or FOUR12 mode is selected, the multiplier must not be used, and USE_MULT must be set to NONE.                                                                                                                                                                                                                                                                                                                              |

| Pattern Detector Attribute | s                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| AUTORESET_PATDET           | NO_RESET,<br>RESET_MATCH,<br>RESET_NOT_MATCH<br>(NO_RESET) | Automatically resets the P Register (accumulated value or counter value) on the next clock cycle, if a pattern detect event has occurred on this clock cycle. The RESET_MATCH and RESET_NOT_MATCH settings distinguish between whether the DSP48E1 slice should cause an auto reset of the P Register on the next cycle:                                                                                                                      |

|                            |                                                            | if the pattern is matched                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                            |                                                            | <ul> <li>whenever the pattern is not matched on the current cycle but was matched on the previous clock cycle</li> </ul>                                                                                                                                                                                                                                                                                                                      |

| MASK                       | 48-bit field (001111)                                      | This 48-bit value is used to mask out certain bits during a pattern detection. When a MASK bit is set to 1, the corresponding pattern bit is ignored. When a MASK bit is set to 0, the pattern bit is compared.                                                                                                                                                                                                                               |

| PATTERN                    | 48-bit field (0000)                                        | This 48-bit value is used in the pattern detector.                                                                                                                                                                                                                                                                                                                                                                                            |

| SEL_MASK                   | MASK, C,<br>ROUNDING_MODE1,<br>ROUNDING_MODE2<br>(MASK)    | Selects the mask to be used for the pattern detector. The C and MASK settings are for standard uses of the pattern detector (counter, overflow detection, etc.). ROUNDING_MODE1 (C-bar left shifted by 1) and ROUNDING_MODE2 (C-bar left shifted by 2) select special masks based off of the optionally registered C port. These rounding modes can be used to implement convergent rounding in the DSP48E1 slice using the pattern detector. |

| SEL_PATTERN                | PATTERN, C (PATTERN)                                       | Selects the input source for the pattern field. The input source can either be a 48-bit dynamic "C" input or a 48-bit static attribute field.                                                                                                                                                                                                                                                                                                 |

| USE_PATTERN_DETECT         | NO_PATDET, PATDET<br>(NO_PATDET)                           | Selects whether the pattern detector and related features are used (PATDET) or not used (NO_PATDET). This attribute is used for speed specification and Simulation Model purposes only.                                                                                                                                                                                                                                                       |

Table 2-4: Internal Register Descriptions

| Register                     | Description and Associated Attribute                                                                                                                                                                                                                                                                             |  |  |

|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 2-Deep A Registers           | These two optional registers for the A input are selected by AREG, enabled by CEA1 and CEA2, respectively, and reset synchronously by RSTA.                                                                                                                                                                      |  |  |

| 2-Deep B Registers           | Thee two optional registers for the B input are selected by BREG, enabled by CEB1 CEB2, respectively, and reset synchronously by RSTB.                                                                                                                                                                           |  |  |

| AD Register                  | This register for the optional pre-adder result is selected by ADREG, enabled by CEAD and reset synchronously by RSTD.                                                                                                                                                                                           |  |  |

| ALUMODE Register             | This optional pipeline register for the ALUMODE control signal is selected by ALUMODEREG, enabled by CEALUMODE, and reset synchronously by RSTALUMODE.                                                                                                                                                           |  |  |

| C Register                   | This optional register for the C input is selected by CREG, enabled by CEC, and reset synchronously by RSTC.                                                                                                                                                                                                     |  |  |

| CARRYIN Register             | This optional pipeline register for the CARRYIN control signal is selected by CARRYINREG, enabled by CECARRYIN, and reset synchronously by RSTALLCARRYIN.                                                                                                                                                        |  |  |

| CARRYINSEL Register          | This optional pipeline register for the CARRYINSEL control signal is selected by CARRYINSELREG, enabled by CECTRL, and reset synchronously by RSTCTRL.                                                                                                                                                           |  |  |

| D Register                   | This register for the optional D pre-adder input is selected by DREG, enabled by CEI and reset synchronously by RSTD.                                                                                                                                                                                            |  |  |

| INMODE Register              | This 5-bit register selects the pre-adder and its mode, and the sign and the source of the A register feeding the multiplier. This register is selected by INMODEREG, enabled by CEINMODE, and reset synchronously by RSTINMODE.                                                                                 |  |  |

| Internal Mult Carry Register | This optional pipeline register for the Internal Carry signal (used for Multiply Symmetric Rounding Only) is enabled by CEM and reset synchronously by RSTM.                                                                                                                                                     |  |  |

| M Register                   | This optional pipeline register for the output of the multiplier consists of two 43-bit partial products.                                                                                                                                                                                                        |  |  |

|                              | These two partial products are input into the X and Y multiplexers and finally into the adder/subtracter to create the product output.                                                                                                                                                                           |  |  |

|                              | The M register is selected by MREG, enabled by CEM, and reset synchronously by RSTM.                                                                                                                                                                                                                             |  |  |

| OPMODE Register              | This optional pipeline register for the OPMODE control signal is selected by OPMODEREG, enabled by CECTRL, and reset synchronously by RSTCTRL.                                                                                                                                                                   |  |  |

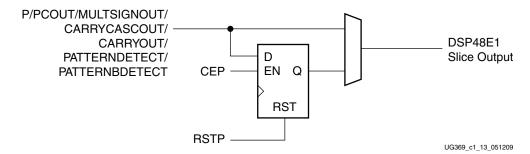

| Output Registers             | This optional register for the P, OVERFLOW, UNDERFLOW, PATTERNDETECT, PATTERNDETECT, and CARRYOUT outputs is selected by PREG, enabled by CEP, and reset synchronously by RSTP. The same register also clocks out PCOUT, CARRYCASCOUT, and MULTSIGNOUT, which are the cascade outputs to the next DSP48E1 slice. |  |  |

### Input Ports

A, B, C, CARRYIN, CARRYINSEL, OPMODE, BCIN, PCIN, ACIN, ALUMODE, CARRYCASCIN, MULTSIGNIN along with the corresponding clock enable inputs and reset inputs, are legacy ports. The D and INMODE ports are unique to the DSP48E1 slice.

This section describes the input ports of the DSP48E1 slice in detail. The input ports of the DSP48E1 slice are highlighted in Figure 2-6.

<sup>\*</sup>These signals are dedicated routing paths internal to the DSP48E1 column. They are not accessible via fabric routing resources.

UG369\_c1\_06\_052109

Figure 2-6: Input Ports in the DSP48E1 Slice

#### A, B, C, and D Ports

The DSP48E1 slice input data ports support many common DSP and math algorithms. The DSP48E1 slice has four direct input data ports labeled A, B, C, and D. The A data port is 30 bits wide, the B data port is 18 bits wide, the C data port is 48 bits wide, and the preadder D data port is 25 bits wide.

The 25-bit A (A[24:0]) and 18-bit B ports supply input data to the 25-bit by 18-bit, two's complement multiplier. With independent C port, each DSP48E1 slice is capable of Multiply-Add, Multiply-Subtract, and Multiply-Round operations.

Concatenated A and B ports (A:B) bypass the multiplier and feed the X multiplexer input. The 30-bit A input port forms the upper 30 bits of A:B concatenated datapath, and the 18-bit B input port forms the lower 18 bits of the A:B datapath. The A:B datapath, together with the C input port, enables each DSP48E1 slice to implement a full 48-bit adder/subtracter provided the multiplier is not used, which is achieved by setting USE\_MULT to NONE (or DYNAMIC).

Each DSP48E1 slice also has two cascaded input datapaths (ACIN and BCIN), providing a cascaded input stream between adjacent DSP48E1 slices. The cascaded path is 30 bits wide for the A input and 18 bits wide for the B input. Applications benefiting from this feature

include FIR filters, complex multiplication, multi-precision multiplication and complex MACCs.

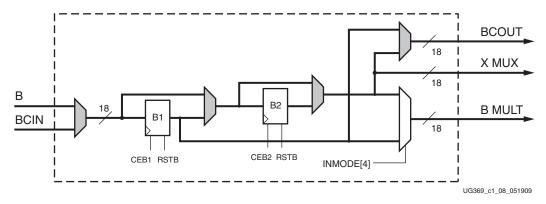

The A and B input port and the ACIN and BCIN cascade port can have 0, 1, or 2 pipeline stages in its datapath. The dual A, D, and pre-adder port logic is shown in Figure 2-7. The dual B register port logic is shown in Figure 2-8. The different pipestages are set using attributes. Attributes AREG and BREG are used to select the number of pipeline stages for A and B direct inputs. Attributes ACASCREG and BCASCREG select the number of pipeline stages in the ACOUT and BCOUT cascade datapaths. The allowed attribute settings are shown in Table 2-3. Multiplexers controlled by configuration bits select flow through paths, optional registers, or cascaded inputs. The data port registers allow users to typically trade off increased clock frequency (i.e., higher performance) vs. data latency.

Figure 2-7: Dual A, D, and Pre-adder Logic

Figure 2-8: Dual B Register Logic

Table 2-5 shows the encoding for the INMODE[3:0] control bits. These bits select the functionality of the pre-adder, the A and D input registers. The USE\_DPORT attribute must be set to TRUE to enable the pre-adder functions described in Table 2-5. INMODE[4], which selects between B1 and B2, is not shown in the table.

In summary, the INMODE and USE\_DPORT attributes control the pre-adder functionality and A, B, and D register bus multipliplexers that precede the multiplier. If the pre-adder is not used, the default of USE\_DPORT is FALSE.

Table 2-5: INMODE[3:0] Functions (when AREG = 1 or 2)

| INMODE[3] | INMODE[2] | INMODE[1] | INMODE[0] | USE_DPORT | Multiplier A Port     |

|-----------|-----------|-----------|-----------|-----------|-----------------------|

| 0         | 0         | 0         | 0         | FALSE     | A2                    |

| 0         | 0         | 0         | 1         | FALSE     | A1                    |

| 0         | 0         | 1         | 0         | FALSE     | Zero                  |

| 0         | 0         | 1         | 1         | FALSE     | Zero                  |

| 0         | 0         | 0         | 0         | TRUE      | A2                    |

| 0         | 0         | 0         | 1         | TRUE      | A1                    |

| 0         | 0         | 1         | 0         | TRUE      | Zero                  |

| 0         | 0         | 1         | 1         | TRUE      | Zero                  |

| 0         | 1         | 0         | 0         | TRUE      | D + A2 <sup>(1)</sup> |

| 0         | 1         | 0         | 1         | TRUE      | D + A1 <sup>(1)</sup> |

| 0         | 1         | 1         | 0         | TRUE      | D                     |

| 0         | 1         | 1         | 1         | TRUE      | D                     |

| 1         | 0         | 0         | 0         | TRUE      | -A2                   |

| 1         | 0         | 0         | 1         | TRUE      | -A1                   |

| 1         | 0         | 1         | 0         | TRUE      | Zero                  |

| 1         | 0         | 1         | 1         | TRUE      | Zero                  |

| 1         | 1         | 0         | 0         | TRUE      | D – A2 <sup>(1)</sup> |

| 1         | 1         | 0         | 1         | TRUE      | D – A1 <sup>(1)</sup> |

| 1         | 1         | 1         | 0         | TRUE      | D                     |

| 1         | 1         | 1         | 1         | TRUE      | D                     |

#### Notes:

INMODE[0] selects between A1 (INMODE[0] = 1) and A2 (INMODE[0] = 0).

INMODE[1] = 1 forces the A input to the pre-adder to 0, and INMODE[2] = 0 forces the D input to the pre-adder to 0.

When INMODE[2] = 0, the D input to the pre-adder is 0.

INMODE[3] provides pre-adder subtract control, where INMODE[3] = 1 indicates subtract and INMODE[3] = 0 indicates add.

<sup>1.</sup> Set the data on the D and the A1/A2 ports so the pre-adder, which does not support saturation, does not overflow or underflow. See Pre-adder, page 37.

INMODE[4] selects the Multiplier B port as shown in Table 2-6.

Table 2-6: INMODE[4] Encoding (when BREG = 1 or 2)

| INMODE[4] | Multiplier B Port |

|-----------|-------------------|

| 0         | B2                |

| 1         | B1                |

The 48-bit C port is used as a general input to the Y and Z multiplexers to perform add, subtract, three-input add/subtract, and logic functions. The C input is also connected to the pattern detector for rounding function implementations. The C port logic is shown in Figure 2-9. The CREG attribute selects the number of pipestages for the C input datapath.

Figure 2-9: C Port Logic

#### OPMODE, ALUMODE, and CARRYINSEL Port Logic

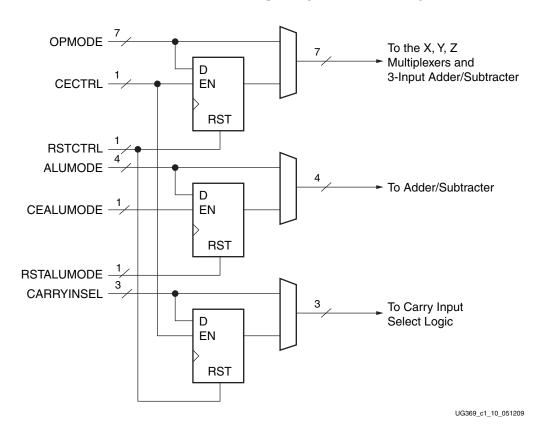

The OPMODE, ALUMODE, and CARRYINSEL port logic supports flow through or registered input control signals. Multiplexers controlled by configuration bits select flow through or optional registers. The control port registers allow users to trade off increased clock frequency (i.e., higher performance) vs. data latency. The registers have independent clock enables and resets. The OPMODE and CARRYINSEL registers are reset by RSTCTRL. The ALUMODE is reset by RSTALUMODE. The clock enables and the OPMODE, ALUMODE, and CARRYINSEL port logic are shown in Figure 2-10.

Figure 2-10: OPMODE, ALUMODE, and CARRYINSEL Port Logic

#### X, Y, and Z Multiplexers

The OPMODE (Operating Mode) control input contains fields for X, Y, and Z multiplexer selects.

The OPMODE input provides a way for the user to dynamically change DSP48E1 functionality from clock cycle to clock cycle (e.g., when altering the internal datapath configuration of the DSP48E1 slice relative to a given calculation sequence).

The OPMODE bits can be optionally registered using the OPMODEREG attribute (as noted in Table 2-3).

Table 2-7, Table 2-8, and Table 2-9 list the possible values of OPMODE and the resulting function at the outputs of the three multiplexers (X, Y, and Z multiplexers). The multiplexer outputs supply three operands to the following adder/subtracter. Not all possible combinations for the multiplexer select bits are allowed. Some are marked in the tables as "illegal selection" and give undefined results. If the multiplier output is selected, then both the X and Y multiplexers are used to supply the multiplier partial products to the adder/subtracter.

Table 2-7: OPMODE Control Bits Select X Multiplexer Outputs

| Z<br>OPMODE[6:4] | Y<br>OPMODE[3:2] | X<br>OPMODE[1:0] | X<br>Multiplexer Output | Notes                             |

|------------------|------------------|------------------|-------------------------|-----------------------------------|

| XXX              | xx               | 0.0              | 0                       | Default                           |

| xxx              | 01               | 01               | M                       | Must select with OPMODE[3:2] = 01 |

| XXX              | xx               | 10               | P                       | Must select with PREG = 1         |

| XXX              | xx               | 11               | A:B                     | 48 bits wide                      |

Table 2-8: OPMODE Control Bits Select Y Multiplexer Outputs