# AN-311 APPLICATION NOTE

ONE TECHNOLOGY WAY . P.O. BOX 9106 . NORWOOD, MASSACHUSETTS 02062-9106 . 617/329-4700

## How to Reliably Protect CMOS Circuits Against Power Supply Overvoltaging by Mike Byrne

#### INTRODUCTION

All IC processes have an intrinsic breakdown voltage associated with them, and this results in a maximum voltage stress which can be applied to any device fabricated on that process. As a result, all IC manufacturers give an Absolute Maximum Ratings specification for their devices. This generally gives the maximum voltage which can be applied to any of the pins on the device. Overvoltaging a device means that stresses or voltages in excess of the absolute maximum ratings are applied to the device. This application note deals in particular with overvoltage of the power supply inputs to CMOS and linear-compatible CMOS devices.

The intrinsic breakdown voltage associated with an IC process means that a transistor, buried Zener or other such element on the process will have a defined breakdown voltage. Obviously, if only one such element appeared between the positive supply input (VDD) and negative power supply input (V<sub>SS</sub>) of a device, the absolute maximum rating voltage, for V<sub>DD</sub> - V<sub>SS</sub>, would be the breakdown voltage of the element. It is not always possible to ensure that V<sub>DD</sub> - V<sub>SS</sub> does not appear across any single element within the IC as it is often compromised by the required IC functionality, die size constraints and other factors. This means that the device manufacturer will be left with a finite voltage which can be applied across the supplies before destruction of the device results. Thus the device manufacturer will determine the limit and specify an absolute maximum rating on the data sheet for the part which is safely inside the breakdown voltage. Users of the part must ensure that the operating voltages applied to the device are within the absolute maximum ratings. So where's the problem?

#### **POWER SUPPLY SPIKES**

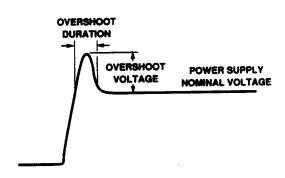

The problem arises, not with the steady-state value of the power supplies which is easily controlled, but with voltage spikes on the power supply lines. The most likely place for these voltage spikes to occur in most systems is during turn-on and turn-off of the power supplies. Other potential sources of voltage spikes are switching mode power supplies or when operating the devices in noisy environments, such as in the presence of large motors. During these times, depending on the output impedance of the power supplies, the load presented to the power supplies and the overall design of the power supply, the power supply voltage may significantly overshoot its nominal value and in doing so exceed the absolute maximum ratings of the device (see Figure 1).

Figure 1. Power Supply Turn-On Spikes

Historically, external clamp elements such as Zener and Schottky diodes have been used to limit voltage spikes to a duration short enough to prevent any damage to the device. However, as geometries of CMOS and linearcompatible CMOS processes shrink, the devices fabricated on them are getting faster. This means that in normal operation there is a significant benefit to the user in terms of speed, bandwidth, etc. However, it also means that elements fabricated on the faster process will respond to much shorter power supply transients. It is not uncommon for devices to respond to power supply transients which are of the order of 1µs duration or less. This means that traditional methods of protecting devices using Zener and Schottky diodes no longer reliably protect the device. This is because their response time to a voltage spike or transient is now, in many cases, slower than what the device's response time is, and therefore they do not provide any protection.

#### TRANSIENT VOLTAGE SUPPRESSORS

In order to provide adequate protection, the protecting element needs to have a very fast response time to voltage spikes or transients. Devices which are ideal for this function are transient voltage suppressors or

nsZorbs.\* TransZorb suppressors are PN Silicon transient voltage suppressors that are characterized by their surge handling capability, their extremely fast response time and low series resistance. Their response time can be as low as 1ns while their clamping ratio (ratio of clamp voltage to nominal voltage) is low. The manner in which the TransZorb is used to protect the device depends on the actual application, and a number of different situations are discussed in the following sections. In all cases, the TransZorb should be placed as close as possible to the device it is protecting to reduce the resistance between the TransZorb and the device.

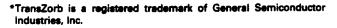

#### Single Supply Systems

The first case is where the CMOS device to be protected is operated from a single power supply rail. Obviously, in this case, the breakdown path is between this single power supply rail and the ground rail of the device. In such cases, a single transient suppressor, connected between the rail and ground as per Figure 2, is sufficient to reliably protect the device from turn-on and turn-off transients. This single TransZorb will protect the device from transients on either the power supply rail or on the ground rail by clamping the voltage differential between them. The TransZorbs come in a variety of different voltage ratings, and Table I gives the recommended

nsZorb part number for some commonly used power sapply voltages.

#### **Dual Supply Systems**

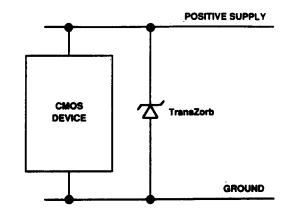

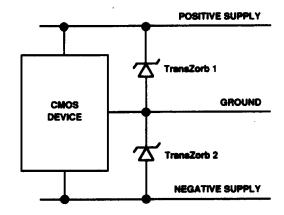

The second case is where the device is powered from two supply rails. In this case, a number of potential breakdown paths exist. The first is between the positive and negative supply rails, the second between the positive supply rail and ground and the third between the negative supply rail and ground. For dual supply systems there are two possible protection schemes.

For some cases, a single TransZorb, connected between the two supply rails as in Figure 3, is sufficient to protect the device. In this case, the TransZorb voltage rating is equal to the sum of the two power supply voltages. This single TransZorb arrangement assumes that when a

Figure 2. Using TransZorbs in Single Supply Systems

Figure 3. Dual Supply, Single TransZorb Arrangement

Figure 4. Dual Supply, Two TransZorb Arrangement

| Power Supply<br>Voltage | TransZorb Part Number (JEDEC Type Number) | Reverse Stand-Off<br>Voltage | Maximum Clamping<br>Voltage @ 1A† | Maximum Clamping<br>Voltage @ 10A† |

|-------------------------|-------------------------------------------|------------------------------|-----------------------------------|------------------------------------|

| +5 V Supply             | 1N6373                                    | +5 V                         | +7.1 V                            | +7.5 V                             |

| -5 V Supply             | 1N6373                                    | -5 V                         | −7.1 V                            | −7.5 V                             |

| +12 V Supply            | 1N6376                                    | +12 V                        | +16.1 V                           | +16.5 V                            |

| -12 V Supply            | 1N6376                                    | -12 V                        | -16.1 V                           | -16.5 V                            |

| +15 V Supply            | 1N6377                                    | +15 V                        | +20.1 V                           | +20.6 V                            |

| -15 V Supply            | 1N6377                                    | -15 V                        | -20.1 V                           | -20.6 V                            |

Table I. Recommended TransZorbs for Figure 2 and Figure 4

†This is the peak pulse current.

| Power Supply<br>Voltage | TransZorb Part Number (JEDEC Type Number) | Reverse Stand-Off<br>Voltage | Maximum Clamping Voltage @ 1A† | Maximum Clamping<br>Voltage @ 10A† |

|-------------------------|-------------------------------------------|------------------------------|--------------------------------|------------------------------------|

| ±5 V                    | 1N6375                                    | 10 V                         | 13.7 V                         | 14.1 V                             |

| +5 V, -12 V             | 1N6378                                    | 18 V                         | 24.2 V                         | 25.2 V                             |

| +5 V, -15 V             | 1N6379                                    | 22 V                         | 29.8 V                         | 32.0 V                             |

| +12 V, -5 V             | 1N6378                                    | 18 V                         | 24.2 V                         | 25.2 V                             |

| ±12 V, -5 V<br>±12 V    | 1N6282A                                   | 25.6 V                       | 32.0 V‡                        | 33.0 V‡                            |

| +15 V, -5 V             | 1N6379                                    | 22 V                         | 29.8 V                         | 32.0 V                             |

| +15 V, -5 V<br>+15 V    | 1N6484A                                   | 30.8 V                       | 38.5 V‡                        | 39.5 V‡                            |

<sup>†</sup>This is the peak pulse current.

Table II. Recommended TransZorbs for Figure 3

spike occurs on one of the supplies that the other supply presents a low output impedance. It also assumes that the supplies are capable of sinking or sourcing the additional current which flows when a spike occurs. If these assumptions hold, then all three breakdown paths are protected when the spikes occur on either of the power supplies. For example, if the positive supply is +5 V and the negative supply is -15 V, the TransZorb rating will be 20 V. Assuming there is a +15 V spike on the +5 V supply, the TransZorb will react to this by absorbing the spike and sinking the current down to the  $-15 \, \text{V}$  supply. This means that the  $-15\,\mathrm{V}$  supply must be able to sink the additional current. If it can, the -15 V supply will not move from its -15 V level during the spike, and the TransZorb will ensure that the positive supply will not be more than 20 V above this. This means that the positive supply does not move above +5 V, the negative supply does not move from -15 V, and all three breakdown paths are protected. Table II gives some examples of recommended TransZorbs for a number of common dual power supply voltages.

There are two situations where the single TransZorb scheme, across the positive and negative supplies, will not always protect the device. The first of these, already mentioned above, is where one of the supplies cannot sink or source the additional current which flows during a spike or when either of the supplies does not present a low output impedance during the spike. It should be noted here that while the power supply may present a low output impedance under steady-state conditions, its impedance during turn-on or turn-off may be different. Using the same example as before, if the -15 V supply cannot sink the required spike current, it means that the negative supply is no longer at -15 V. The TransZorb will still clamp the two supplies together so the breakdown path between the two supplies is protected. However, the absolute value of either supply is no longer clearly defined. If we assume that the -15 V goes to, say, -5 V because it cannot sink the current, it means that the positive supply goes to +15 V. This will possibly exceed the breakdown path between the positive supply and ground and lead to damage to the device.

The second situation is where the spikes occur on the ground line and not on either of the power supply rails. A positive spike of +10 V on the ground line, for example, would not cause the TransZorb to turn on, yet the voltage difference between ground and the negative supply is now 25 V, and this could exceed the breakdown voltage between the negative rail and ground.

In these situations, the two TransZorb scheme, shown in Figure 4, is recommended. This two TransZorb scheme protects against voltage spikes on the ground and also protects the device in cases where either of the supplies is not capable of sinking or sourcing the additional current which flows during the spike. This scheme ensures that each supply is independently protected and the spike current flows to ground. This scheme protects the breakdown path from each supply in the same manner as outlined for single supply systems. By protecting each supply, the breakdown between the two supplies is also protected, and so all three possible breakdown paths are guarded against. Suitable TransZorb values for common power supply voltages are as per Table I.

### SWITCHING-MODE POWER SUPPLIES/NOISY **ENVIRONMENTS**

Another situation, other than power on, where spiking of the supplies can occur is in applications using switchingmode power supplies. Although the switching mode power supply may be regulated, the regulation may not be sufficient to remove spikes as low as 1  $\mu s$  duration. If these spikes have sufficient magnitude and energy, they also can cause damage to the device. Other potential problem areas are applications in environments which are inherently noisy and produce spikes on power supply and ground rails. Examples of this type of application are operating devices in the presence of large motors or operating the devices in industrial environments. The schemes recommended in Figures 2, 3 and 4 for turn-on/turn-off spikes are equally applicable to protecting against switching-mode power supply spikes or power supply spikes generated in noisy environments.

The TransZorb schemes shown in this application note protect the device against overvoltaging of the power supplies. It will not prevent damaged being caused to the device when recommended power supply sequencing is not obeyed. Consult the absolute maximum ratings section in the manufacturer's data sheet to see if there is a particular power supply sequence for a device or if the digital inputs cannot be powered before the supplies.

<sup>‡</sup>These are typical numbers. TransZorbs are available with lower clamping voltages than the JEDEC part numbers given in the table above.