# Ultralow Noise Synthesizers

## Low Noise and Spurious Levels, 350MHz to 6GHz Frequency Synthesizers

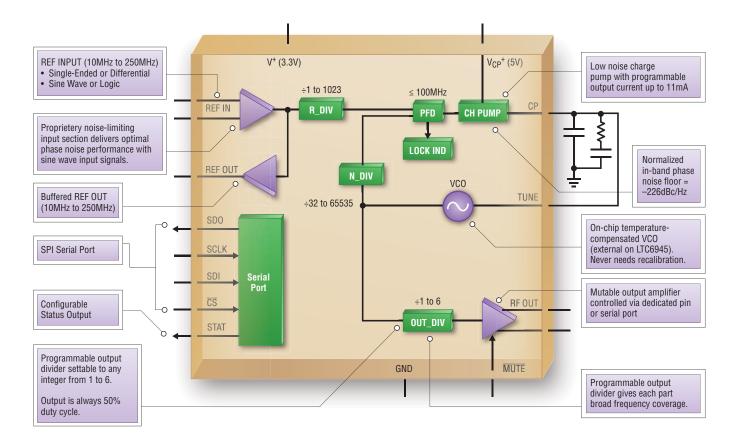

Our new ultralow noise, integer-N frequency synthesizers provide best-in-class phase noise and spurious performance. The LTC®6946 is a complete frequency synthesizer that includes a high performance, low noise, 5.7GHz phase-locked loop (PLL) with a fully integrated, low phase noise VCO. The LTC6945 separates the low 1/f corner PLL core for use with an external VCO up to 6GHz. The free, easy-to-use PLLWizard™ CAD tool quickly and accurately simulates synthesizer performance to ensure an optimal design.

#### Features

- 350MHz to 6GHz VCO Input Range (LTC6945)

- Low –226dBc/Hz Normalized In-Band Phase Noise Floor

- –157dBc/Hz Wideband Output Phase Noise Floor

- Industry's Lowest –274dBc/Hz Normalized In-Band 1/f Noise

- Spurious Levels < -100dBc

- High Current 11mA Output Charge Pump Minimizes Loop Compensation Thermal Noise

- Programmable Output Divider for Wide Operating Frequency Range

- 28-Pin (4mm × 5mm) QFN Packages

| Frequency Coverage Options |                |                |                |

|----------------------------|----------------|----------------|----------------|

|                            | LTC6946-1      | LTC6946-2      | LTC6946-3      |

| VCO Frequency (GHz)        | 2.240 to 3.740 | 3.080 to 4.910 | 3.840 to 5.790 |

| OUT DIV = 1                | 2.240 to 3.740 | 3.080 to 4.910 | 3.840 to 5.790 |

| OUT DIV = 2                | 1.120 to 1.870 | 1.540 to 2.455 | 1.920 to 2.895 |

| OUT DIV = 3                | 0.747 to 1.247 | 1.027 to 1.637 | 1.280 to 1.930 |

| OUT DIV = 4                | 0.560 to 0.935 | 0.770 to 1.228 | 0.960 to 1.448 |

| OUT DIV = 5                | 0.448 to 0.748 | 0.616 to 0.982 | 0.768 to 1.158 |

| OUT DIV = 6                | 0.373 to 0.623 | 0.513 to 0.818 | 0.640 to 0.965 |

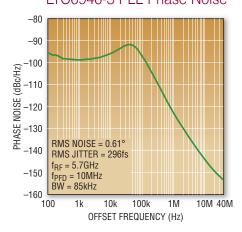

### LTC6946-3 PLL Phase Noise

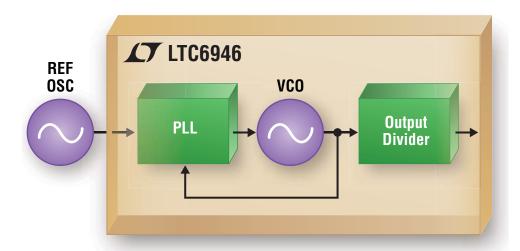

## LTC6946-X Frequency Synthesizer Block Diagram

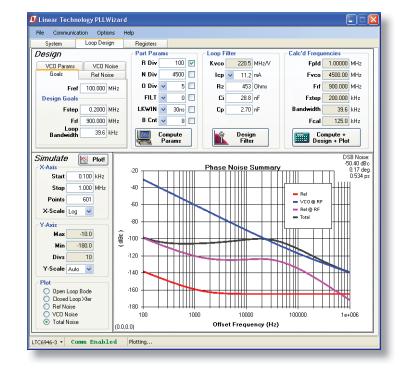

## PLLWizard Tool Provides Design Support

#### **Design Features**

- Find Part Parameters Based on Your Frequency Plan

- Design Noise-Optimized Loop Filters

- Simulate Loop Frequency Response and Stability

- Simulate VCO and Reference Source Noise

- Simulate Output Noise Characteristics and Statistics

#### **Evaluation Features**

- Read and Write All Device Registers

- Configure Using a Block Diagram Programming Interface

- Troubleshoot Common Set-Up Problems

- Receive Alerts Due to Programming Errors