ADI 器件应用丛书

# ADI 模数转换器应用笔记 (第 1 册)

ADI 公司 编译

## 内 容 简 介

由 ADI 工程师亲自参与设计、调试并验证的模数转换器应用笔记。通过这些应用笔记,为许多通用应用提供解决方案。每款模数转换器电路包含详细的设计文档。电路功能和性能已经过硬件验证。

本书将是广大工程技术人员、高等学校师生进行电路设计的参考书。

### 图书在版编目(CIP)数据

ADI 模数转换器应用笔记. 第 1 册 /ADI 公司编译. --

北京: 北京航空航天大学出版社, 2011. 7

ISBN 978 - 7 - 5124 - 0415 - 1

I. ①A… II. ①A… III. ①模-数转换器—研究

IV. ①TP335

中国版本图书馆 CIP 数据核字(2011)第 072420 号

版权所有, 侵权必究。

### ADI 模数转换器应用笔记(第 1 册)

ADI 公司 编译

责任编辑 张 楠 王 松

\*

北京航空航天大学出版社出版发行

北京市海淀区学院路 37 号(邮编 100191) <http://www.buaapress.com.cn>

发行部电话:(010)82317024 传真:(010)82328026

读者信箱: emsbook@gmail.com 邮购电话:(010)82316936

印刷有限公司印装 各地书店经销

\*

开本: 787×960 1/16 印张: 14.75 字数: 330 千字

2011 年 7 月第 1 版 2011 年 7 月第 1 次印刷 印数: 4 000 册

ISBN 978-7-5124-0415-1 定价: 31.0 元

**www.BDTIC.com/ADI**

# 序

# 言

这些年,在与电子技术领域的工程师、学者以及大学师生交流的时候,他们的聪明才智和创新能力给我留下了深刻的印象。而他们所做的设计和项目,无一不让我感觉到中国工程师队伍成长之快,和中国电子行业巨大的发展潜力。但另一方面,他们的经历和成功,也带给了我很多思考。

ADI 在模拟和数字信号领域中已经发展了 40 多年。在这几十年间,我们不断推动技术的创新和进步,不断提高相关领域的各类产品性能以满足客户的广泛需求,包括消费类、通信、医疗、运输和工业等方面。令人欣慰的是,至 2009 年,ADI 已经拥有遍布世界各地的 60 000 余家客户。而通过大学计划、培训、研讨会等活动所积累起来的资源更是不计其数。如何让我们的客户,让 ADI 技术产品的使用者和爱好者,真正准确、有效、快捷地掌握相关知识与设计技巧,是我们需要考虑的,也是我们为所有用户提供的非常重要的服务之一。

经过多年的运行和完善,ADI 已经拥有了一整套对中国工程师以及在校工科类学生的培养计划,如每年一届的中国大学创新设计竞赛,在高校建立的联合实验室,各类线上线下研讨会,还有在多个城市开展的高水平培训课程等等。这些计划架起了 ADI 与用户之间最直接、最有效的沟通桥梁。同时,为了使更多的电子技术领域从业者和爱好者了解数字信号处理和电子产品设计理念,我们还邀请了业内具有较深影响力的专家、学者、教授共同编写并出版一套基于 ADI 模拟和数字产品的应用技术丛书。

该丛书详细介绍了 ADI 产品在医疗电子、通信、工业仪器仪表、汽车电子等行业的应用,以理论与实际案例相结合的方式为读者们讲解了世界先进处理器的设计与使用。

丛书的出版凝聚了来自众多院校老师、专家丰富的经验和智慧。在此,感谢他们对 ADI 出版计划的大力支持。同时,也感谢北京航空航天大学出版社对本丛书的出版所做出的贡献!

衷心希望能得到读者朋友的意见反馈,在你们提出的问题和建议下,我们将不断完善 ADI 器件应用丛书,不断完善 ADI 的产品和技术,与客户们一起共同开拓中国市场。

# 目 录

---

## 第一部分 ADC 产品的应用

|                                                            |     |

|------------------------------------------------------------|-----|

| AN - 0972 应用笔记: AD7329 如何帮助降低成本 .....                      | 3   |

| AN - 0979 应用笔记: 数字滤波器的选择:AD7190、AD7192 .....               | 10  |

| AN - 1011 应用笔记: AD7150 的 EMC 保护 .....                      | 17  |

| AN - 1021 应用笔记: 基于 MMSE 的触摸屏应用多点校准算法 .....                 | 29  |

| AN - 354 应用笔记: 应用工程师问答(1) .....                            | 42  |

| AN - 351 应用笔记: 应用工程师问答(2) .....                            | 44  |

| AN - 586 应用笔记: 高速模数转换器的 LVDS 数据输出 .....                    | 48  |

| AN - 609 应用笔记: $\Sigma\text{-}\Delta$ ADC 上的斩波.....        | 55  |

| AN - 614 应用笔记: 在低功耗应用中使用 AD7782 .....                      | 60  |

| AN - 639 应用笔记: 常见问题解答:Analog Devices 电能计量(ADE)产品 .....     | 63  |

| AN - 665 应用笔记: $\Sigma\text{-}\Delta$ ADC 的通道切换 .....      | 89  |

| AN - 877 应用笔记: 通过 SPI 与高速 ADC 接口 .....                     | 93  |

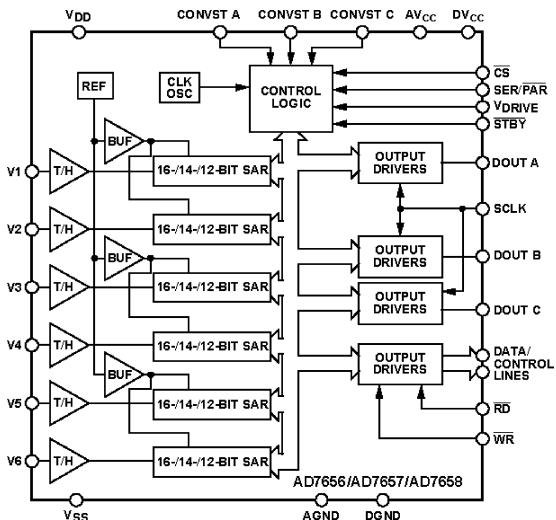

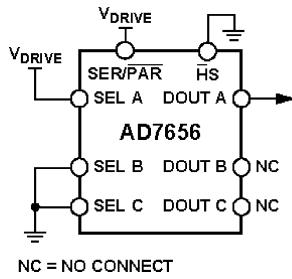

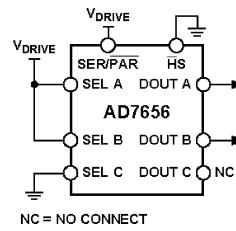

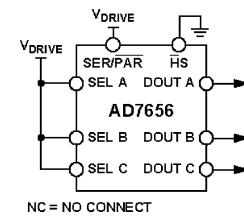

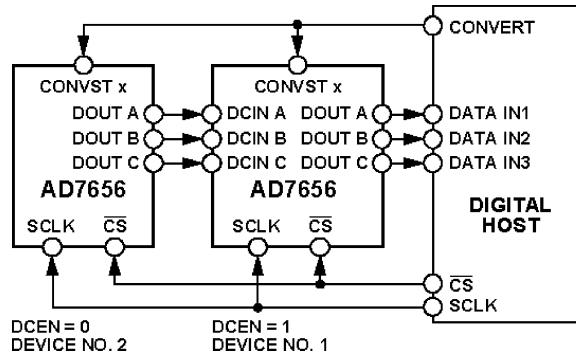

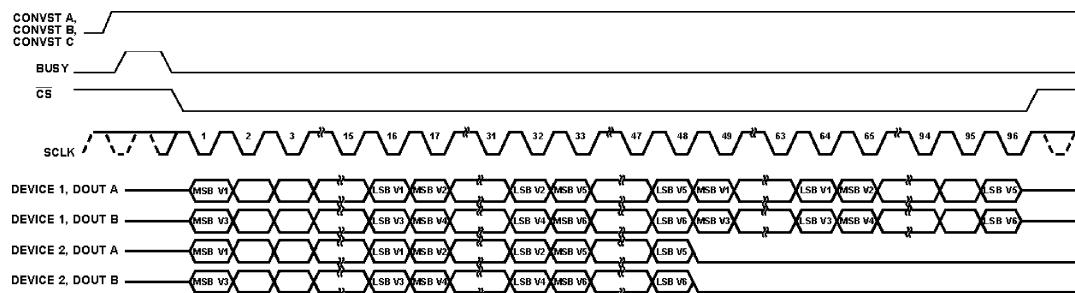

| AN - 893 应用笔记: 将 AD7656/AD7657/AD7658 配置为串行和菊花链接口工作模式..... | 121 |

| AN - 925 应用笔记: AD7147 和 AD7148 CapTouch 控制器应用中的传感器设计 ..... | 127 |

| AN - 935 应用笔记: ADC 变压器耦合前端设计 .....                         | 133 |

## 第二部分 ADC 基本概念指标和测试评估

|                                         |     |

|-----------------------------------------|-----|

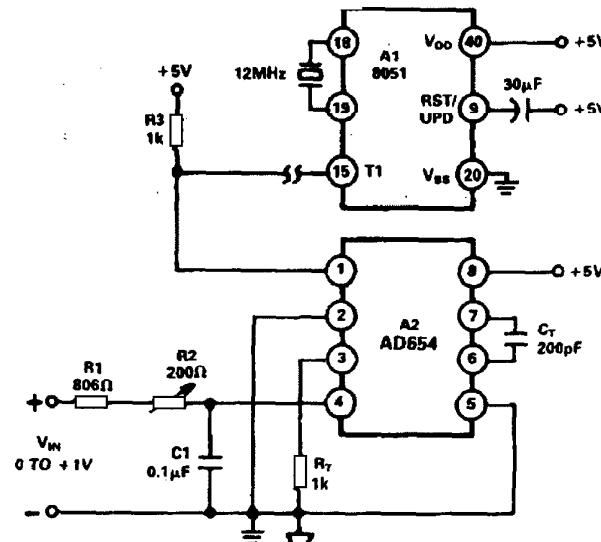

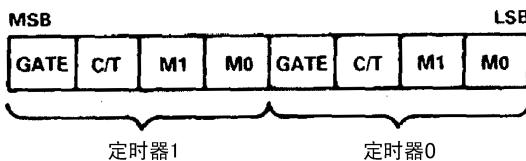

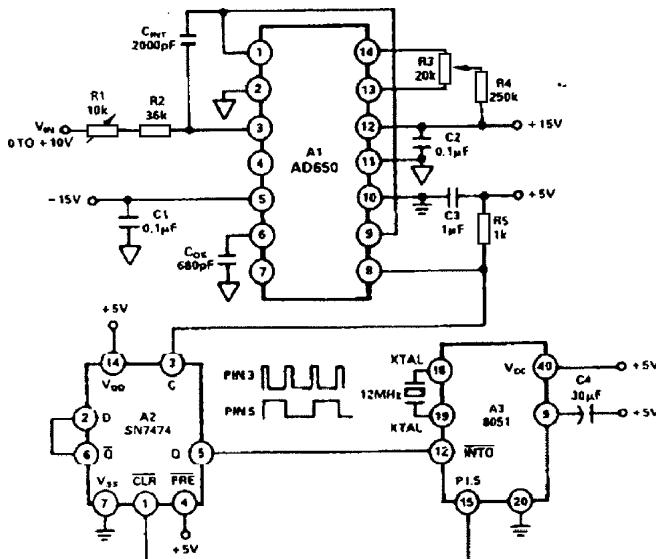

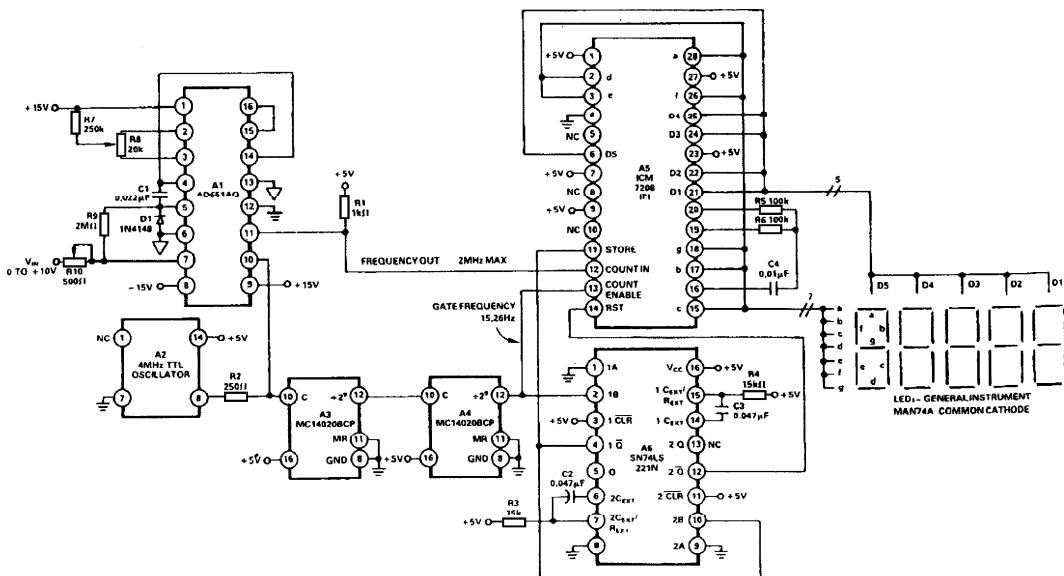

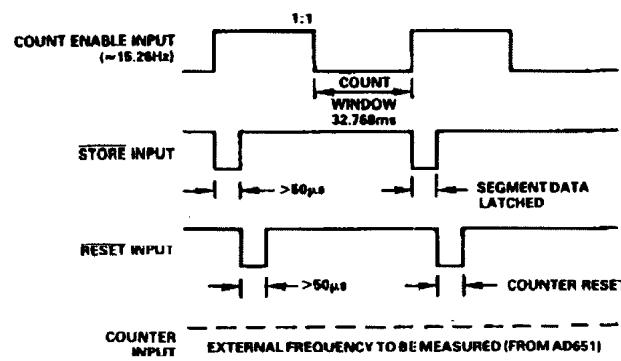

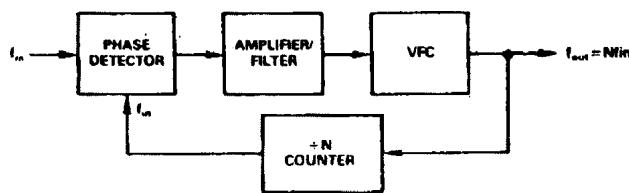

| AN - 276 应用笔记: 使用电压频率转换器实现模数转换 .....    | 145 |

| AN - 282 应用笔记: 采样数据系统基本原理 .....         | 159 |

| AN - 835 应用笔记: 高速 ADC 测试和评估 .....       | 194 |

| AN - 931 应用笔记: 了解 PulSAR ADC 支持电路 ..... | 222 |

# **第一部分 ADC 产品的应用**

**www.BDTIC.com/ADI**

**[www.BDTIC.com/ADI](http://www.BDTIC.com/ADI)**

# AN - 0972 应用笔记 AD7329 如何帮助降低成本

作者 : Claire Croke Jakub Szymczak

## 简介

AD7329 是一款 8 通道、12 位带一个额外符号位的双极性输入 ADC。该器件有 4 种软件可选输入范围:  $\pm 4 \times V_{REF}$ 、 $\pm 2 \times V_{REF}$ 、 $\pm V_{REF}$  和  $0 \sim 4 \times V_{REF}$ 。每个模拟输入通道支持独立编程, 可设为 4 个模拟输入范围之一。AD7329 采用工业 CMOS(iCMOS) 工艺制成, 与当今市场上的其他双极性 ADC 解决方案相比, 这种 ADC 不但可以输入较大的双极性模拟信号, 同时还能提升性能, 降低功耗并减小封装尺寸。

AD7329 采用极其灵活的设计, 可根据多种应用要求进行配置。本应用笔记将简要介绍如何通过 AD7329 实现极高的输入阻抗, 同时保持输入较大的双极性模拟信号的能力。同时还将讨论如何配置 AD7329, 以支持较小输入信号并保持较高性能水平。

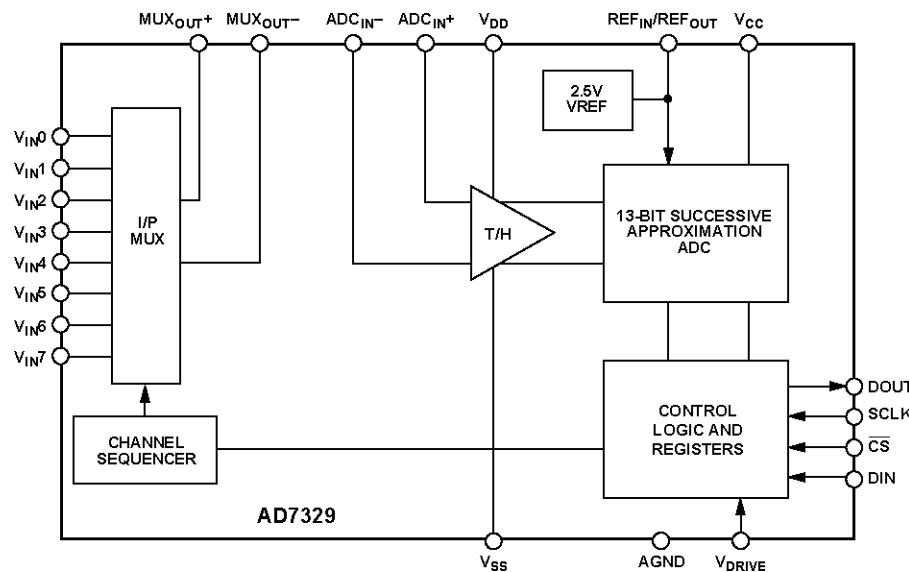

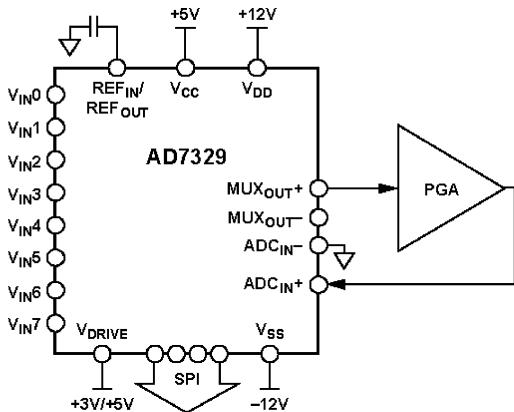

图 1 为 AD7329 功能框图。

## AD7329 模拟输入

AD7329 模拟输入可配置为 8 个单端输入、4 个真差分输入对、7 个伪差分输入或 4 个伪差分输入对。

AD732x 系列 ADC 采用 iCMOS 工艺设计, 可输入真双极性模拟信号。有些双极性输入 ADC 在模拟输入上采用一种电阻式结构, 以便对双极性信号进行缩放和电平转换处理, 使其处于内部 ADC 要求的电压范围之内。这类电阻式模拟输入 ADC 的不足之处在于, 这些模拟输入的驱动源只能实现极低的源阻抗, 因而需要用较大输入电流来驱动这些输入。

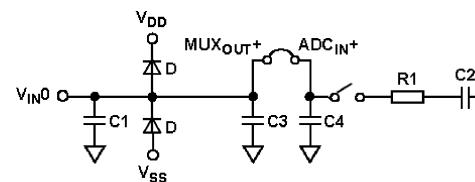

AD7329 的等效模拟输入结构如图 2 所示。AD7329 直接在 ADC 采样电容上对双极性模

# 第一部分 ADC 产品的应用

拟输入信号采样,因此,与电阻式输入 ADC 相比,驱动 AD7329 输入结构只需较少电流。

图 1 AD7329 功能框图

图 2 AD7329 模拟输入结构——单端模式

AD7329 上的模拟输入通道通过一个片内多路复用器,该复用器的输出通向  $\text{MUX}_{\text{OUT}+}$  引脚和  $\text{MUX}_{\text{OUT}-}$  引脚。AD7329 还具有  $\text{ADC}_{\text{IN}+}$  和  $\text{ADC}_{\text{IN}-}$  引脚。通过  $\text{ADC}_{\text{IN}+}$  和  $\text{ADC}_{\text{IN}-}$  两个引脚,可访问 AD7329 采样保持电路和 ADC 上的采样电容。

当  $\text{MUX}_{\text{OUT}+}$  引脚直接连接至  $\text{ADC}_{\text{IN}+}$  引脚时,AD7329 应用与许多其他 ADC 类似。输入信号直接通过采样电容采样。在这种配置中,AD7329 驱动源需提供用于驱动 ADC 输入的电流,并要在 ADC 采样时间(300 ns)内建立至所需精度。

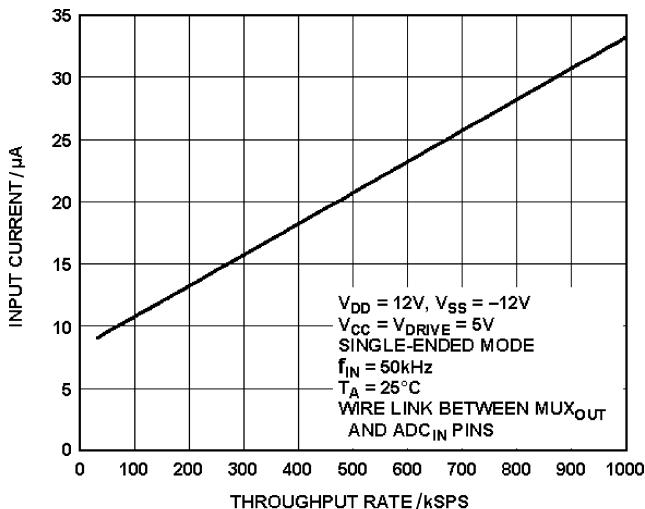

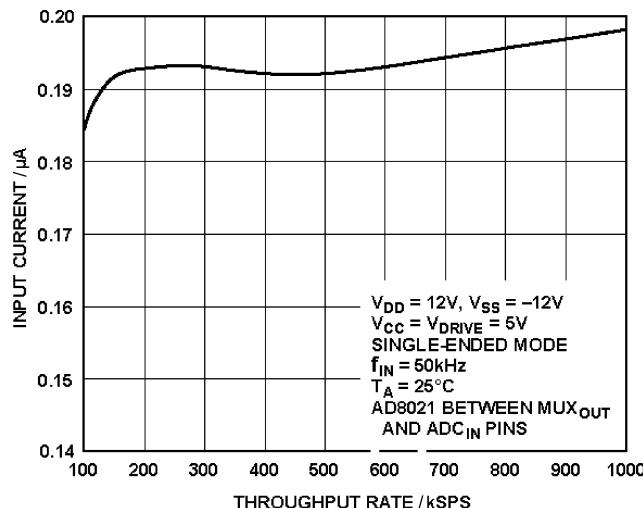

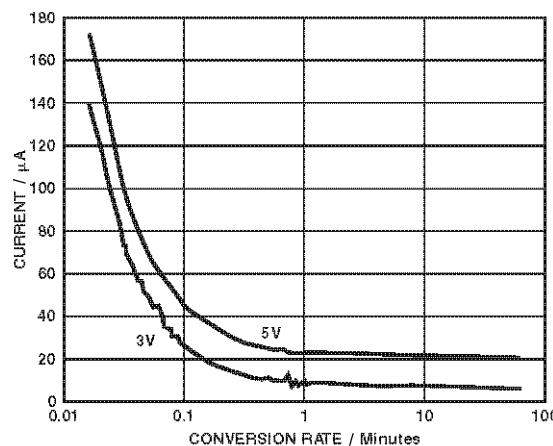

图 3 显示的是当  $\text{MUX}_{\text{OUT}+}$  引脚短接至  $\text{ADC}_{\text{IN}+}$  引脚时 AD7329 模拟输入所需要的驱动电流。从坐标图可以看出,随着采样速率的增加,模拟输入所需驱动电流也随之增加。

与所有 SAR 转换器一样,当内部采样保持开关从保持切换至采样时,ADC 会有瞬时反冲。AD7329 驱动源必须能从该瞬变中恢复过来,并在 ADC 采集时间之内建立至所需精度。对于工作于最大采样频率的应用,可能需要用一个输入缓冲放大器来驱动 ADC,并将驱动源

图 3 直接连接 MUX<sub>OUT</sub> 引脚和 ADC<sub>IN</sub> 引脚时的输入电流与吞吐速率关系曲线

AD7329 设计灵活, 可在 MUX<sub>OUT</sub> 和 ADC<sub>IN</sub> 引脚之间放置一个运算放大器。在这种配置中, AD7329 可实现极高的模拟输入阻抗, 并且运算放大器可使驱动源与 AD7329 输入结构隔离。

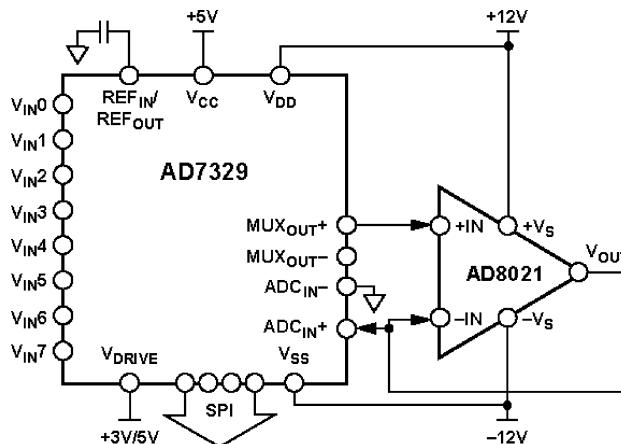

这种配置中使用的运算放大器必须能够接受最高  $\pm 10\text{V}$  的双极性信号。来自 MUX<sub>OUT</sub> 引脚的信号仍为高电压双极性信号。在图 4 中, 采用了 AD8021 低噪声高速放大器。AD8021 可输入较大双极性模拟信号, 同时还能在 ADC 所需采样时间之内建立信号。

此时, 对驱动源来说, AD7329 的输入阻抗为 AD8021 的输入阻抗。这种配置中, AD8021 置于 MUX<sub>OUT</sub> 引脚与 ADC<sub>IN</sub> 引脚之间, 用于驱动 AD7329 的源电流小于  $0.2\ \mu\text{A}$ 。

图 5 显示的是在采用图 4 所示配置时, AD7329 所需要的驱动电流。该输入电流与吞吐速率关系坐标图生成于单通道转换过程中。

这种配置的优势在于, 在最大采样频率下, 8 个模拟输入通道只需一个运算放大器即可。在驱动源看来, AD7329 的模拟输入阻抗是  $M\Omega$  级的, 只需很少电流即可驱动 8 个模拟输入引脚。MUX<sub>OUT</sub> 引脚与 ADC<sub>IN</sub> 引脚之间的运算放大器将驱动源与 ADC 输入端隔离。这种配置可减少元件数量, 减小电路板面积, 降低电路板成本。

根据具体应用要求, 比如模拟输入电压、电源电压和采样频率等, 可在 AD7329 上的 MUX<sub>OUT</sub> 引脚与 ADC<sub>IN</sub> 引脚之间使用其他双极性输入运算放大器。

图 4 在 AD7329 的 MUX<sub>OUT</sub> 与 ADC<sub>IN</sub> 引脚之间加缓冲器图 5 用 AD8021 连接 MUX<sub>OUT</sub> 和 ADC<sub>IN</sub> 引脚时的输入电流与吞吐速率关系曲线

## 双极性模拟输入信号

AD7329 上的模拟输入通道支持独立编程, 可配置为 4 种输入范围之一。AD7329 可输入  $\pm 4 \times V_{REF}$ 、 $\pm 2 \times V_{REF}$ 、 $\pm V_{REF}$  和  $0 \sim 4 \times V_{REF}$  四种信号。采用内部 2.5 V 基准电压时, 这些输入范围即为  $\pm 10$  V、 $\pm 5$  V、 $\pm 2.5$  V 及  $0 \sim +10$  V。AD7329 还允许将一个外部基准电压应用

于  $\text{REF}_{\text{IN}}/\text{REF}_{\text{OUT}}$  引脚。基准电压的输入范围为  $2.5 \sim 3$  V。采用 3 V 外部基准电压时, AD7329 可输入  $\pm 12$  V、 $\pm 6$  V、 $\pm 3$  V 和  $0 \sim +12$  V 的信号。在差分输入模式下,若采用 3 V 外部基准电压,AD7329 可输入  $\pm 24$  V、 $\pm 12$  V、 $\pm 6$  V 和  $0 \sim +24$  V 的差分信号,具体取决于所选范围。在增加 AD7329 基准输入电压以提高模拟输入电压范围时,要保证  $\text{MUX}_{\text{OUT}}$  引脚与  $\text{ADC}_{\text{IN}}$  引脚之间的运算放大器必须能够支持此类较大的双极性输入信号。

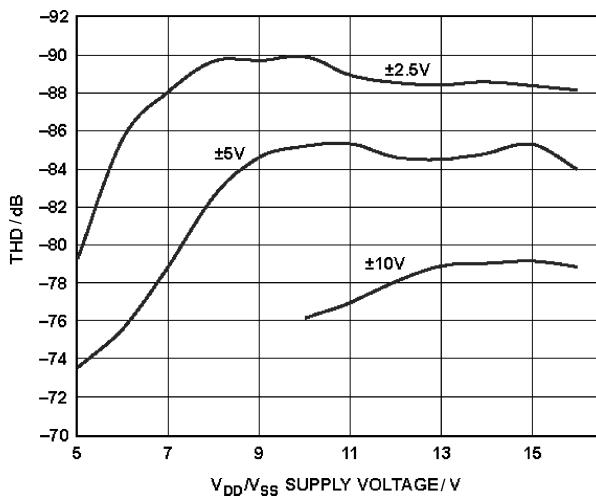

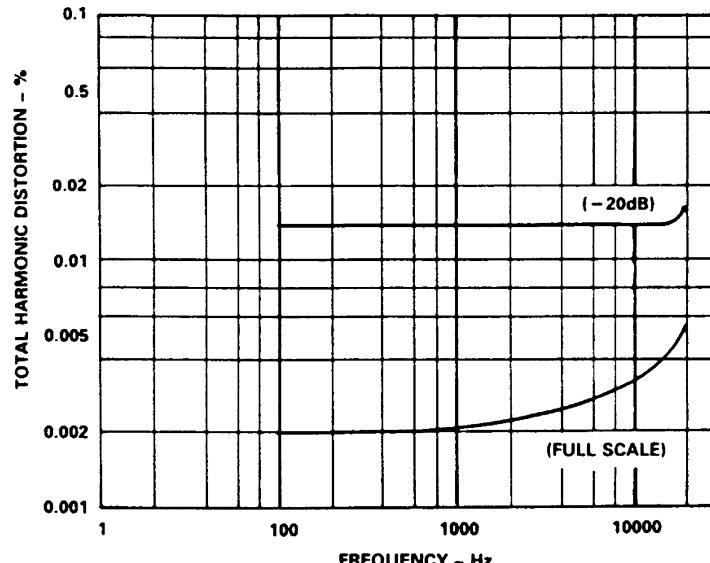

当增加 AD7329 上的模拟输入电压时,  $V_{\text{DD}}$  和  $V_{\text{SS}}$  电源电压应大于等于 ADC 的最大模拟输入电压。在最大采样频率下,随着  $V_{\text{DD}}$  和  $V_{\text{SS}}$  电源电压的降低,AD7329 的总谐波失真性能会随之下降(见图 6)。因此,  $V_{\text{DD}}$  和  $V_{\text{SS}}$  电源电压取决于具体应用所要求的总谐波失真性能。当  $V_{\text{DD}}$  和  $V_{\text{SS}}$  电源电压降低时,输入多路复用器和采样保持开关的导通电阻( $R_{\text{ON}}$ )会增大。当采用对应于模拟输入范围的最低  $V_{\text{DD}}$  和  $V_{\text{SS}}$  电源电压时,为达到额定性能要求,应降低 AD7329 的采样速率。这样允许 ADC 有更多建立时间,以补偿输入多路复用器导通电阻的增加。

图 6 总谐波失真与电源电压关系曲线

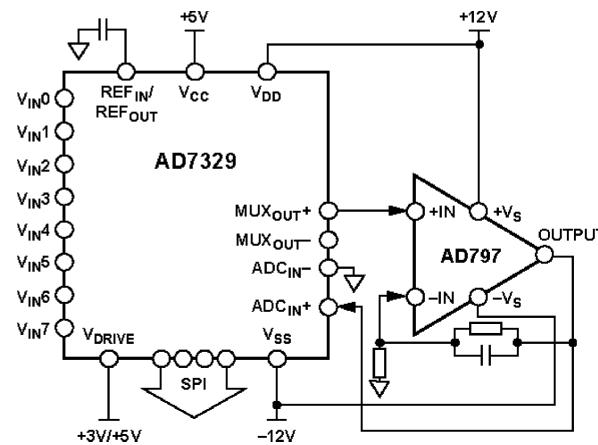

除可以转换较大双极性模拟输入信号外,AD7329 还可以被配置为转换毫伏级信号的 ADC。如图 7 所示,通过运算放大器设置增益,AD7329 可以转换毫伏级小信号。

如使用图 7 所示配置,可将毫伏级的小信号应用于模拟输入;然后通过 AD797 对这些信号进行放大处理。接下来将放大后的信号连接至  $\text{ADC}_{\text{IN}}$  引脚,该引脚再通过采样保持开关连接至内部采样电容。

可选择 AD797 上的增益,以确保应用于  $\text{ADC}_{\text{IN}}$  引脚的信号利用 ADC 的整个动态范围。这样可从 AD7329 获得更好的结果。

表 1 所列性能为当 AD7329 输入范围为  $\pm 10$  V,采样速率为 4 MSIPS 时,用单端模式输入

# 第一部分 ADC 产品的应用

10 kHz 的单音信号,而后改变位于  $\text{MUX}_{\text{OUT}}$  引脚与  $\text{ADC}_{\text{IN}}$  引脚之间运算放大器 AD797 的增益所获得的结果。

图 7 AD7329  $\text{MUX}_{\text{OUT}}$  与  $\text{ADC}_{\text{IN}}$  引脚之间的增益级

表 1 在  $\text{MUX}_{\text{OUT}}$  引脚与  $\text{ADC}_{\text{IN}}$  引脚之间插入不同增益值时的交流特性

8

| 增益/(V/V) | 信噪比(SNR)/dB | 总谐波失真/dB | 有效位数/位 |

|----------|-------------|----------|--------|

| 1        | 73.57       | -80.80   | 11.93  |

| 20       | 73.00       | -79.91   | 11.83  |

| 50       | 72.34       | -79.90   | 11.72  |

| 100      | 72.28       | -79.81   | 11.71  |

| 200      | 71.66       | -78.99   | 11.61  |

| 500      | 71.48       | -78.46   | 11.58  |

| 1000     | 69.94       | -75.38   | 11.32  |

增益越大,信噪比和总谐波失真的性能下降越明显。若采用 AD7329 且按图 7 进行配置,增益设为 1000,转换器仍可取得 11 位以上的有效位数(ENOB)。若在  $\text{MUX}_{\text{OUT}}$  引脚与  $\text{ADC}_{\text{IN}}$  引脚之间的增益级使用此值,则 AD7329 可取得相当于 21 位 ADC 的极宽动态范围。

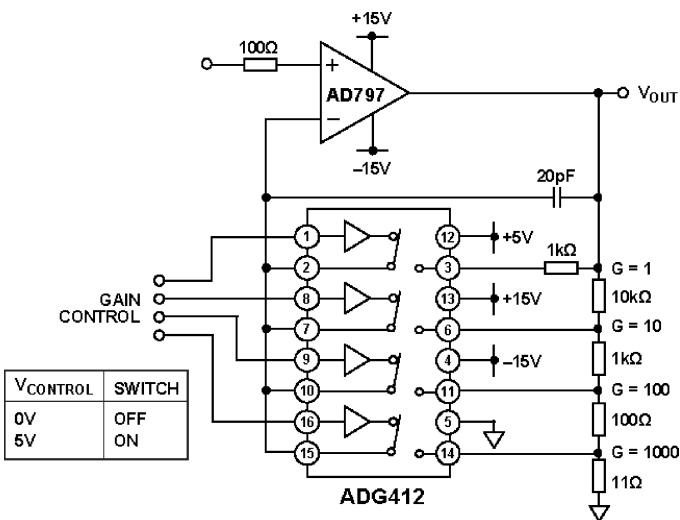

在某些应用中,可能需要改变增益,以适应不同输入通道的信号幅度(见图 8)。这种情况下,可在 AD797 反馈通道中使用一个多路复用器,以允许切换不同的电阻值,从而改变增益设置。对于可编程增益放大器(PGA)设计,建议采用 AD797 和 ADG412。图 9 显示的是针对可编程增益放大器应用的推荐原理图。

图 8 AD7329 MUX<sub>OUT</sub> 与 ADC<sub>IN</sub> 引脚之间的可编程增益放大器

图 9 采用 AD797 和 ADG412 构建的一种极低噪声可编程增益放大器

## 结 论

AD7329 是一款多功能器件。在数据采集系统中,该器件可节省物料,从而显著降低成本。只需一个放大器即可提供 8 个模拟输入通道所需要的高输入阻抗,从而省去了 7 个放大器的费用。采用 AD7329 的数据采集系统可连接至动态范围从毫伏级到±12V 不等的传感器,这可以通过添加一个可编程增益放大器实现。

# AN - 0979 应用笔记

## 数字滤波器的选择:AD7190、AD7192

作者: Mary McCarthy

### 简介

标题所列  $\Sigma - \Delta$  ADC 内置用户可选的 sinc<sup>3</sup> 和 sinc<sup>4</sup> 数字滤波器。本应用笔记将比较这两种滤波器, 明确各自的优点以及使用每种滤波器的影响。

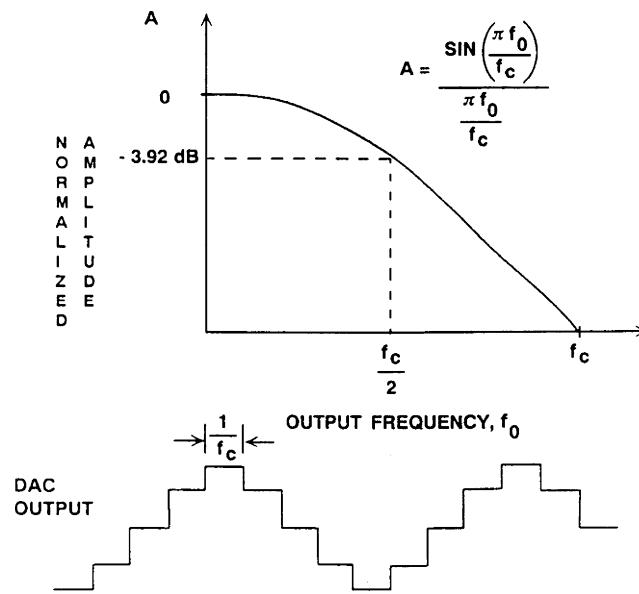

### sinc 滤波器

$\Sigma - \Delta$ ADC 内置一个  $\Sigma - \Delta$  调制器, 后接一个数字滤波器。调制器以高采样速率对模拟输入连续采样, 并输出 1 位数据流。位流中 1 的数量对应于模拟输入电压。然后, 数字滤波器处理位流并执行抽取, 以产生 24 位转换结果。

sinc 滤波器用作所讨论产品的数字滤波器。输出数据速率  $f_{ADC}$ , 即 ADC 在单一通道上连续转换的速率等于:

$$f_{ADC} = f_{CLK} / (1024 \times FS[9:0])$$

式中:

$f_{CLK}$  为主时钟频率(标称值 4.92 MHz)。

$FS[9:0]$  为模式寄存器 FS9 位至 FS0 位中的码的十进制等效值。

这是禁用斩波时输出数据速率的计算公式。请注意, 本应用笔记假设禁用斩波, 除非另有说明。

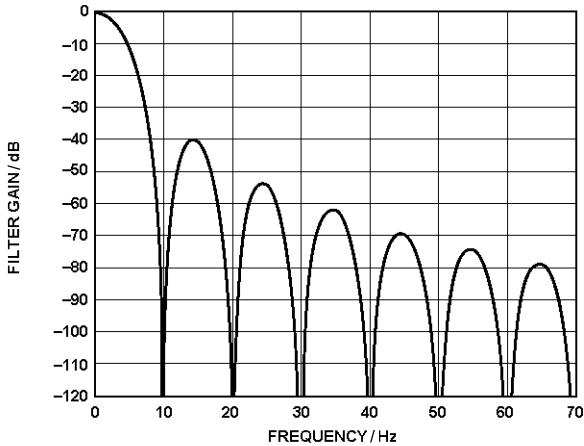

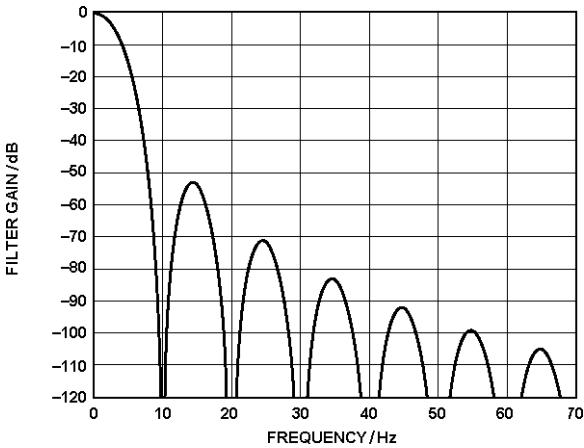

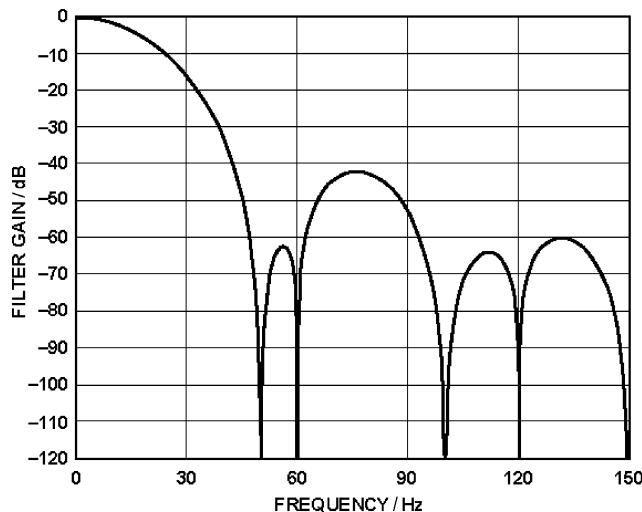

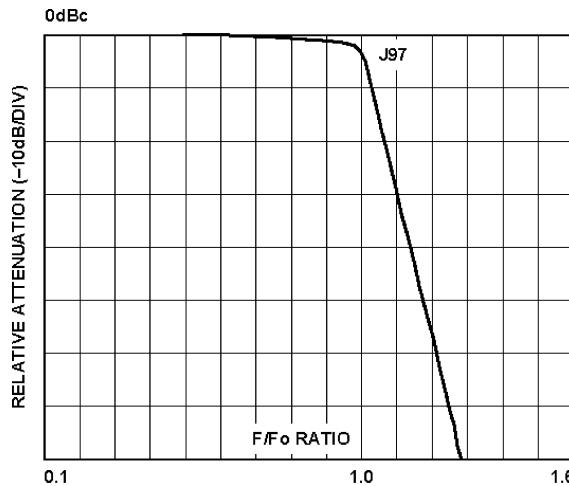

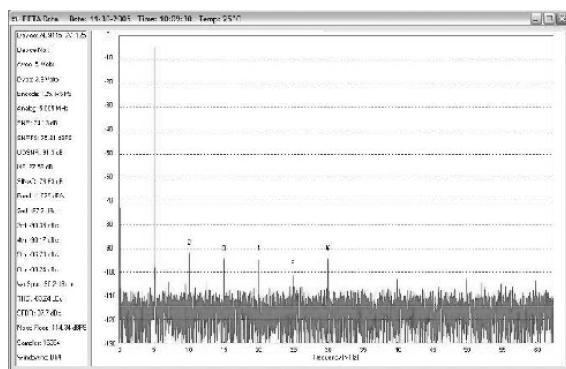

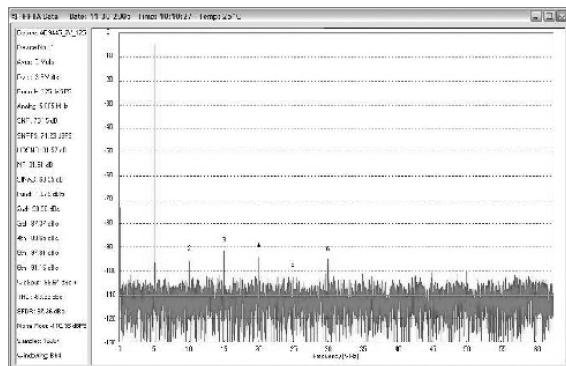

图 1 显示 10 Hz 输出数据速率时 sinc<sup>3</sup> 滤波器的频率响应, 图 2 显示 10 Hz 输出数据速率时 sinc<sup>4</sup> 滤波器的频率响应。陷波位置由输出数据速率决定。陷波宽度取决于滤波器阶数。随着阶数提高, 陷波将变得更宽。因此, 输出数据速率决定陷波位置, 滤波器阶数则决定可以

在陷波周围获得的抑制。随着滤波器阶数提高,滚降、阻带衰减、建立时间和噪声都会受影响。

## 50 Hz /60 Hz 抑制

图 1  $\text{sinc}^3$  滤波器响应 ( $f_{\text{ADC}} = 10 \text{ Hz}$ )

图 2  $\text{sinc}^4$  滤波器响应 ( $f_{\text{ADC}} = 10 \text{ Hz}$ )

图 1 显示输出数据速率为 10 Hz 时  $\text{sinc}^3$  滤波器的频率响应。陷波出现在输出数据速率及其倍数处。因此,陷波位于 10 Hz、20 Hz、30 Hz 等。可以利用此特性来抑制来自电源的

干扰,这是许多应用的关键要求。在世界上的一些地区,需要抑制 50 Hz 干扰,而在另一些地区,则需要抑制 60 Hz 干扰。可以利用 sinc 滤波器的陷波来抑制这种干扰。当输出数据速率为 10 Hz 时,陷波位于 50 Hz 和 60 Hz,因而能够实现 50 Hz 和 60 Hz 同时抑制。终端系统如果需要销往世界上的许多国家和地区,则必须具备此特性。

从图 1 可知,当输出数据速率等于 10 Hz 时,50 Hz $\pm$ 1 Hz 和 60 Hz $\pm$ 1 Hz 抑制超过 100 dB;其前提是系统时钟具有低抖动和漂移,例如利用晶振提供系统时钟。

图 2 显示输出数据速率为 10 Hz 时 sinc<sup>4</sup> 滤波器的频率响应。与 sinc<sup>3</sup> 滤波器一样,陷波位于 10 Hz 和 10 Hz 的倍数。但是,由于陷波更宽,50 Hz $\pm$ 1 Hz 和 60 Hz $\pm$ 1 Hz 抑制超过 120 dB。

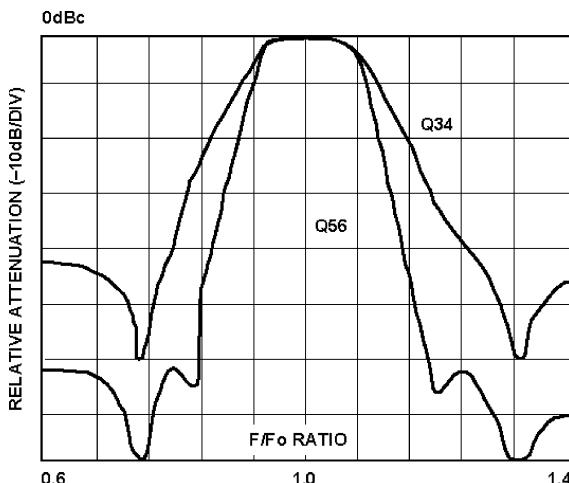

如果只需要 50 Hz 抑制或 60 Hz 抑制,则可以提高输出数据速率;因此,对于仅 50 Hz 抑制,可以使用的最大输出数据速率为 50 Hz。此时,sinc 滤波器的第一陷波位于 50 Hz。同样,60 Hz 输出数据速率将使第一陷波位于 60 Hz。

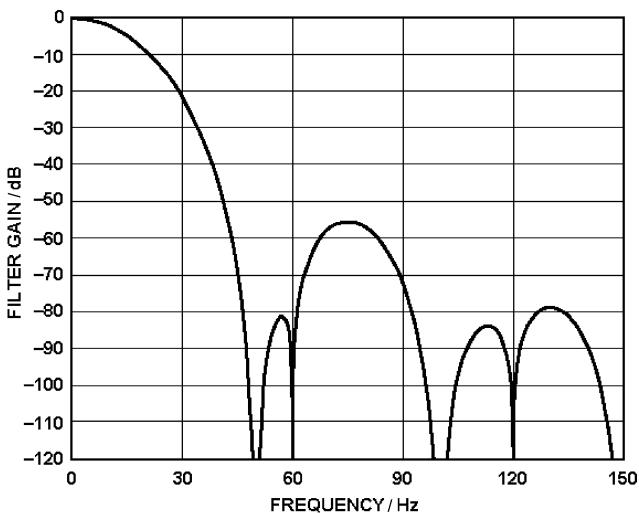

当 ADC 以 50 Hz 输出数据速率工作时,有一个片内特性也能使陷波位于 60 Hz。如果模式寄存器的 REJ60 位设为 1,则当输出数据速率为 50 Hz 时,60 Hz 处也有一个陷波。因此,可以将输出数据速率从 10 Hz 提高到 50 Hz,同时仍然能够获得 50 Hz 和 60 Hz 同时抑制。图 3 显示输出数据速率为 50 Hz 且 REJ60 设为 1 时的滤波器响应。最差情况的 50 Hz $\pm$ 1 Hz 和 60 Hz $\pm$ 1 Hz 抑制为 67 dB。当使用 sinc<sup>4</sup> 滤波器时(见图 4),最差情况的 50 Hz $\pm$ 1 Hz 和 60 Hz $\pm$ 1 Hz 抑制为 82 dB。

图 3 sinc<sup>3</sup> 滤波器响应( $f_{ADC} = 50$  Hz, REJ60=1)

图 4  $\text{sinc}^4$  滤波器响应 ( $f_{\text{ADC}} = 50 \text{ Hz}$ ,  $\text{REJ60} = 1$ )

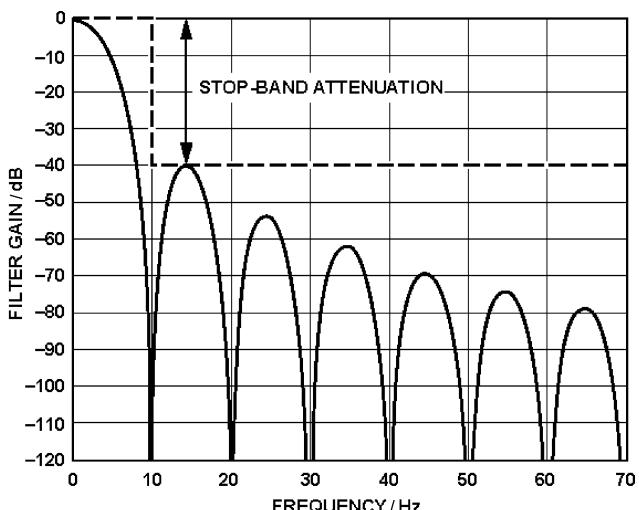

## 阻带衰减

滤波器阶数会引起的滤波器响应变化, 表现为除了影响陷波宽度外, 还会改变阻带衰减和滤波器滚降。阻带衰减是指数字滤波器对第一陷波以上频率的衰减(见图 5)。随着滤波器阶数提高, 阻带衰减将得到改善。 $\text{sinc}^3$  滤波器的阻带衰减为 40 dB,  $\text{sinc}^4$  滤波器则为 53 dB。

## 噪声和分辨率

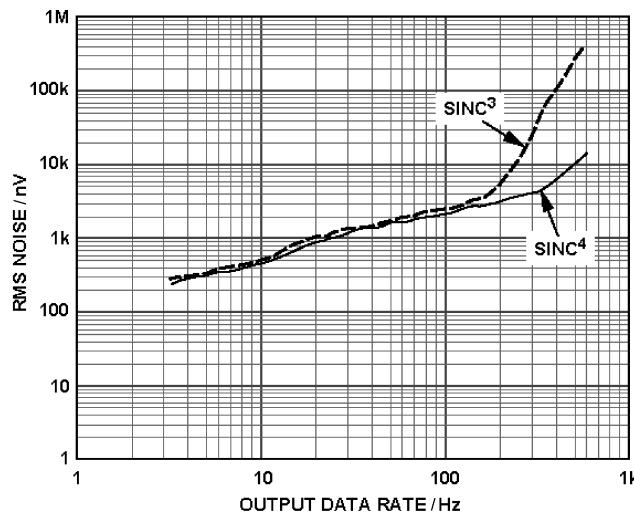

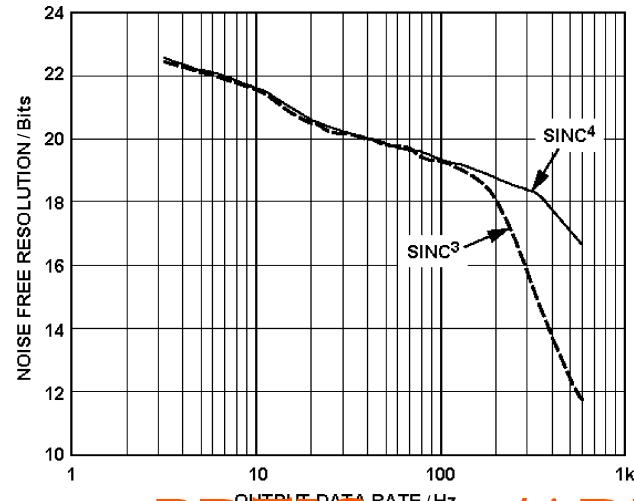

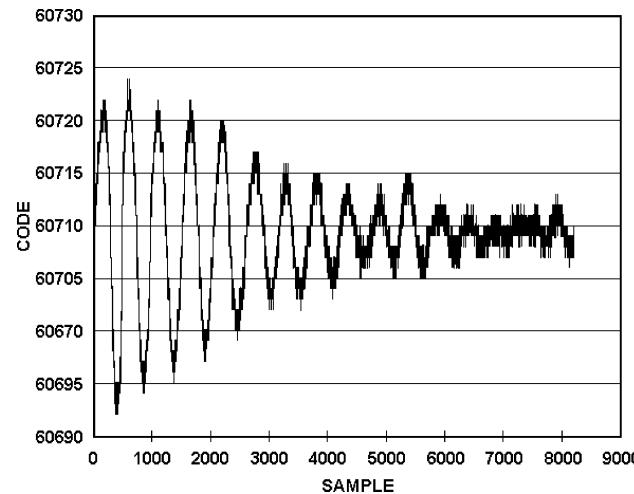

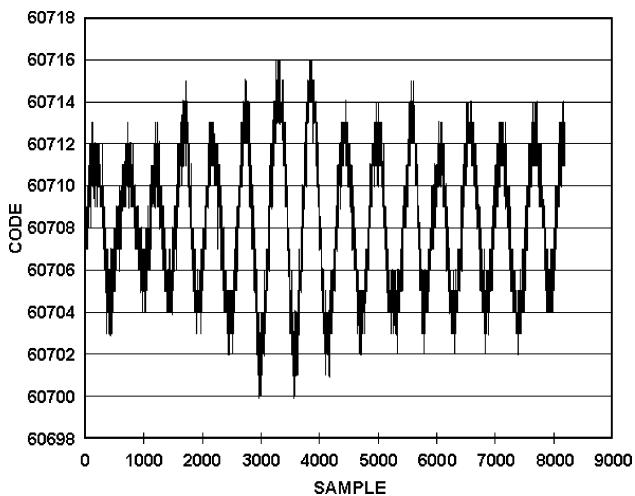

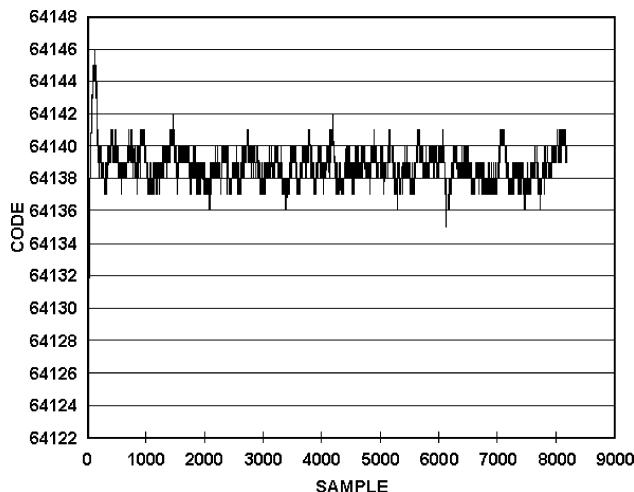

这些器件能够以 4.7 Hz 至 4.8 kHz 的可编程输出数据速率工作。除滤波器阶数外,输出数据速率也会影响噪声,从而影响分辨率。输出数据速率较低时,sinc<sup>3</sup> 与 sinc<sup>4</sup> 滤波器的均方根噪声相似(见图 6)。但是,如果输出数据速率较高(1 kHz 或更高),则 sinc<sup>4</sup> 滤波器的均方根噪声性能更优越。图 7 显示不同输出数据速率时的无噪声(峰峰值)分辨率。

图 6 均方根噪声与输出数据速率的关系( $\text{增益} = 1, V_{\text{REF}} = 5 \text{ V}$ )

图 7 无噪声分辨率与输出数据速率的关系( $\text{增益} = 1, V_{\text{REF}} = 5 \text{ V}$ )

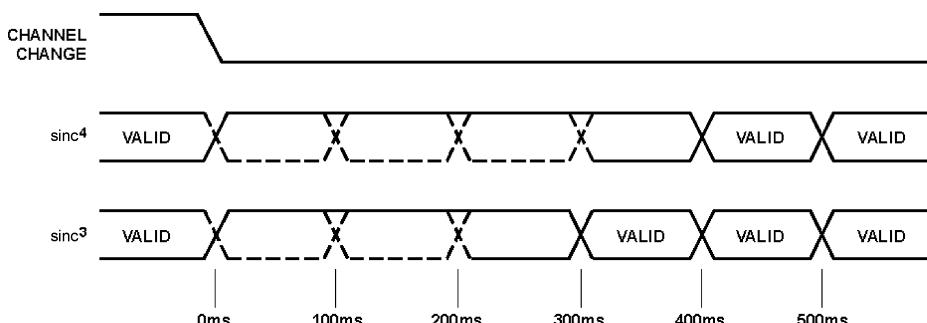

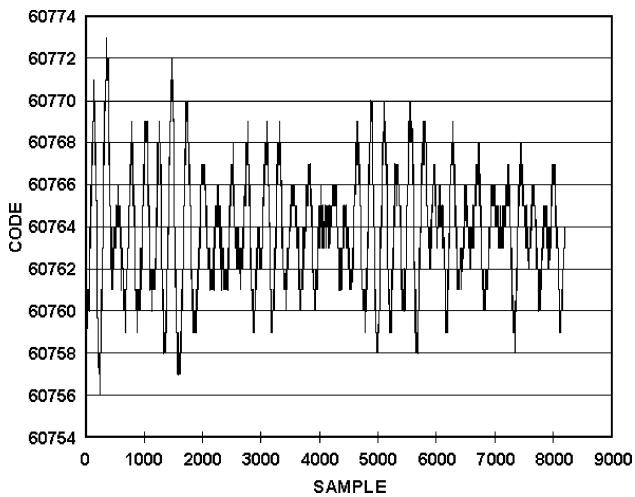

## 建立时间

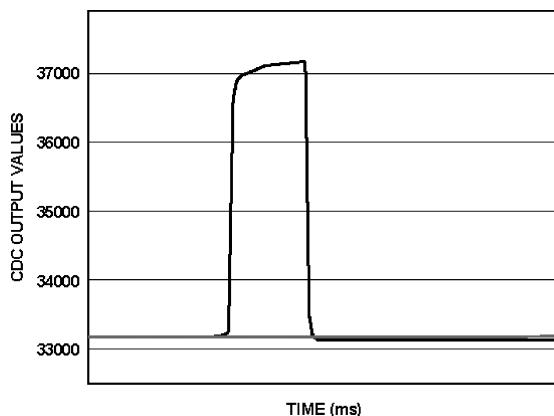

对于多通道应用,建立时间是需要考虑的另一个参数。当在单一通道上连续转换时,如果模拟输入信号是连续的,ADC 将以设定的输出数据速率输出有效转换结果。然而,如果发生配置变更,例如更改通道、增益或输出数据速率等,则配置变更之后的第一次转换需要花费额外的时间。图 8 显示 ADC 以 10 Hz 输出数据速率工作时通道变更的影响。发生通道变更时,调制器和滤波器将复位。然后,ADC 开始对新的模拟输入采样。必须让滤波器完全建立起来,才能产生第一个有效转换结果。对于  $\text{sinc}^3$  滤波器,建立时间  $t_{\text{SETTLE}}$  等于:

$$t_{\text{SETTLE}} = 3/f_{\text{ADC}}$$

对于  $\text{sinc}^4$  滤波器,建立时间等于:

$$t_{\text{SETTLE}} = 4/f_{\text{ADC}}$$

如果 ADC 在单一通道上执行转换,但模拟输入信号发生阶跃变化,则 ADC 需要处理新的模拟输入。如果阶跃变化与转换过程同步,则必须经过建立时间后,才能提供有效转换结果。ADC 并不检测模拟输入的阶跃变化,因此它会以设定的输出数据速率继续输出转换结果。然而,中间转换结果并不准确;它们反映的是模拟输入的变化,同时精度较低。

如果阶跃变化发生在转换过程当中,则必须等待当前转换结束,再经过适当的建立时间后,才能产生有效转换结果。对于  $\text{sinc}^3$  滤波器,总时间延长至  $4/f_{\text{ADC}}$ ;对于  $\text{sinc}^4$  滤波器,产生有效转换结果所需的时间则延长至  $5/f_{\text{ADC}}$ 。

总之,当输出数据速率相同时, $\text{sinc}^3$  滤波器比  $\text{sinc}^4$  滤波器建立得更快。虽然  $\text{sinc}^4$  滤波器的均方根噪声性能和无噪声分辨率高于  $\text{sinc}^3$  滤波器,但前者的建立时间更长。

图 8 建立时间(同步阶跃变化)

## 结 论

sinc 滤波器的阶数影响  $\Sigma - \Delta$  ADC 可实现的性能。高阶 sinc 滤波器可以提供更好的陷波频率抑制和阻带衰减,而且能在高输出数据速率时提供更优的噪声性能和分辨率。缺点是建立时间更长,sinc<sup>4</sup> 滤波器的建立时间比 sinc<sup>3</sup> 滤波器的建立时间长一个转换周期。因此,滤波器选择取决于所需的 50 Hz 和 60 Hz 抑制组合、所用的输出数据速率以及所需的噪声性能和分辨率。对于标题所列  $\Sigma - \Delta$  ADC,表 1 列出了不同数字滤波器影响的多个关键性能的参数。

表 1 sinc<sup>3</sup> 和 sinc<sup>4</sup> 滤波器的一些关键性能参数比较

| 参 数                                                | sinc <sup>3</sup> | sinc <sup>4</sup> |

|----------------------------------------------------|-------------------|-------------------|

| 均方根噪声( $f_{ADC} = 10$ Hz,增益 = 1)                   | 350 nV            | 330 nV            |

| 无噪声分辨率( $f_{ADC} = 10$ Hz,增益 = 1)                  | 22                | 22                |

| 均方根噪声( $f_{ADC} = 4800$ Hz,增益 = 1)                 | 442 $\mu$ V       | 14.3 $\mu$ V      |

| 无噪声分辨率( $f_{ADC} = 4800$ Hz,增益 = 1)                | 11.5              | 16.5              |

| 50±1 Hz 和 60±1 Hz 抑制( $f_{ADC} = 10$ Hz)           | -100 dB           | -120 dB           |

| 50±1 Hz 和 60±1 Hz 抑制( $f_{ADC} = 50$ Hz,REJ60 = 1) | 67 dB             | 82 dB             |

| 阻带衰减                                               | 40 dB             | 53 dB             |

| 建立时间                                               | $3/f_{ADC}$       | $4/f_{ADC}$       |

# AN - 1011 应用笔记 AD7150 的 EMC 保护

作者: Holger Grothe Mary McCarthy

## 简介

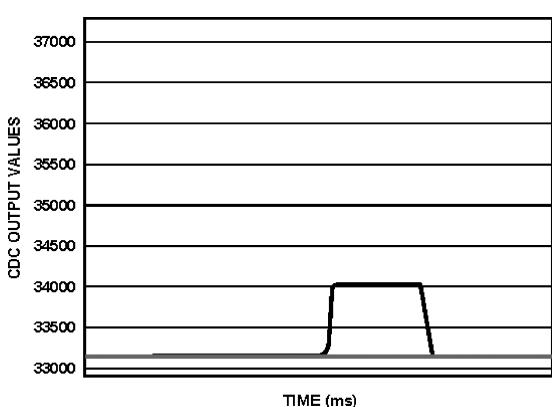

AD7150 是为近程应用而设计的电容转数字的转换器(CDC)。此器件测量两个电极之间的电容并将测量结果与阈值进行比较。如果输入电容发生改变(例如手靠近过来),就会设置一个输出标志,指示电容已超过阈值,表明有物体接近。

电磁干扰会使容性传感器周围的电场失真,从而改变电容值,影响转换结果。为了防止 AD7150 和容性传感器受到电磁干扰,需要使用一些外部滤波。然而,增加滤波器是有挑战性的,因为滤波器会降低电容数字转换的精度。本应用笔记讨论 AD7150 引脚上的外部滤波器能达到的 EMC 性能,以及滤波器对 AD7150 精度的影响。

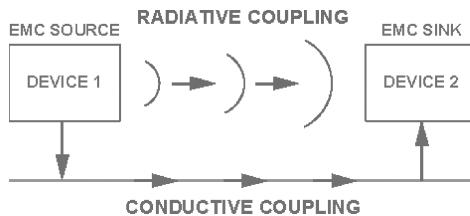

## 什么是 EMC?

电磁兼容性(EMC)是指没有对环境造成电磁辐射并且能在电磁辐射环境中工作的能力。当达到这个目标时,所有的电子设备可以与其他设备一起正常工作。在一个系统中,会有几个 EMC 耦合路径:空间耦合、传导耦合、电感耦合和电容耦合(见图 1)。

当一个系统针对严酷的环境设计时,必须考虑 EMC 并进行 EMC 测试。EMC 测试有不同的级别:系统级测试,子系统级测试和 IC 级测试。测试方法根据每个 EMC 测试级别进行定义。

子系统或者 IC 器件对 EMC 性能的要求取决于器件的功能及其在系统中的位置。例如,在汽车应用中,如果一个器件与汽车电池或底盘连接,那么它必须有较高的 EMC 性能。如果

图 1 EMC 耦合路径

器件局限于印制电路板区域内,那么它对 EMC 级别的要求较少。

AD7150 是一个集成电路;因此,依据国际标准 IEC 62132 第 4 部分,用直接电源注入进行 EMC 测试。AD7150 用于近程传感,例如,无钥匙门禁。它局限于 PCB 区域内并与传感器有局部连接。因此,电磁干扰的级别会较低。

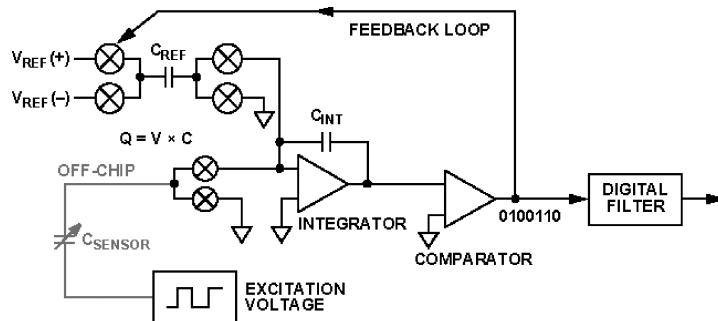

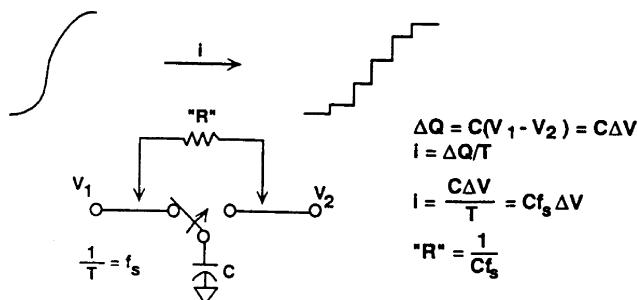

## 电容数字转换器的架构

18

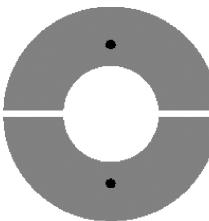

了解电容数字转换器(CDC)的架构有助于理解 EMC 是如何影响 AD7150 工作的。电容数字转换器利用开关电容技术构建电荷平衡电路来测量电容(见图 2)。

图 2 CDC 架构

检测电容  $C_{SENSOR}$  和内部参考电容  $C_{REF}$  以固定采样率进行开关,它们的电荷被输送进入积分器。比较器检测积分器的输出并控制输入开关的相位来关闭反馈环路,从而平衡流过  $C_{SENSOR}$  和参考路径的电荷。

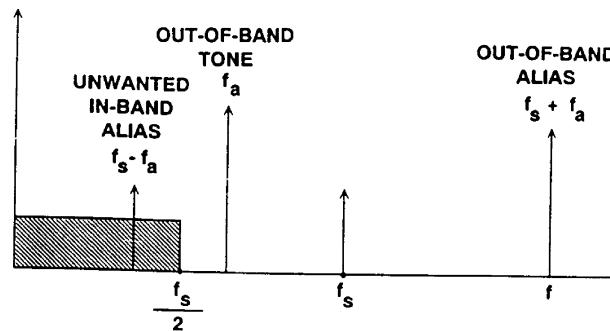

比较器输出的 0 和 1 的数据流随着环路平衡所需的电荷量而变化。电荷与电压和电容成比例。因为电压  $EXC$  和  $V_{REF}$  是固定值,所以 0 和 1 的密度代表输入电容  $C_{SENSOR}$  与参考电容

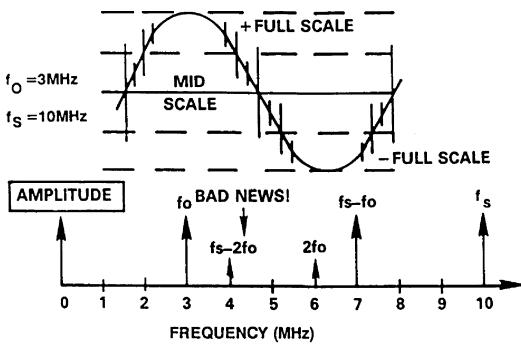

$C_{REF}$  的比值。片内数字滤波器从 0 和 1 组成的时域编码中提取信息形成数字结果。由于滤波是数字的, 直流附近的响应在采样频率及其倍频附近重复。因此, 片内数字滤波器在采样频率及其倍频附近没有提供抑制。

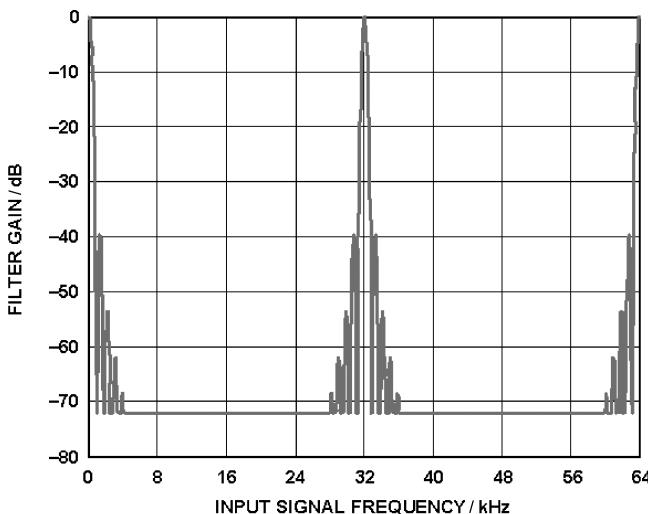

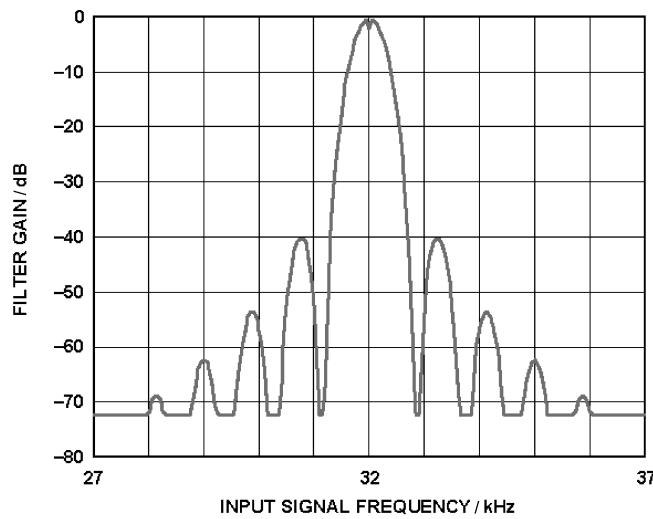

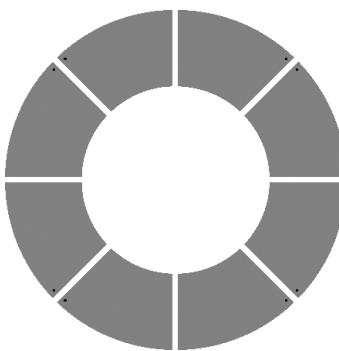

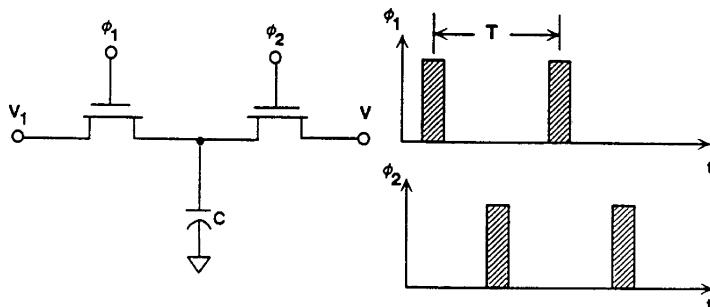

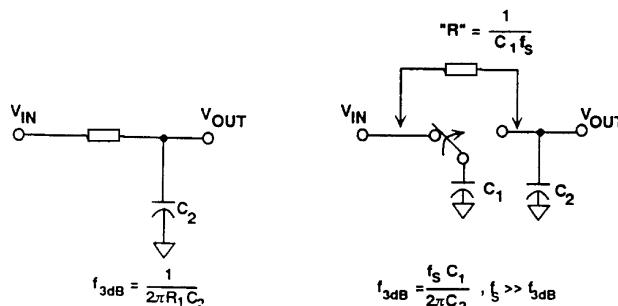

## AD7150

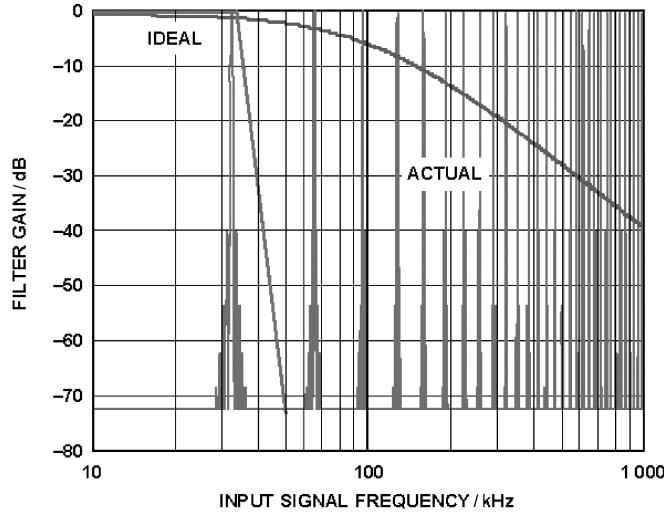

AD7150 使用二阶调制器和三阶 sinc 滤波器。激励频率即容性输入采样频率等于 32 kHz。因此, 片内滤波器响应在 32 kHz 及 32 kHz 的倍频处重复(见图 3)。在噪声环境中, 需要前端的一些附加滤波对 32 kHz 的倍频进行抑制。32 kHz 信号用于激励和测量电容。这样, 理想的外部滤波器应该允许 32 kHz 信号无衰减的通过并在 64 kHz 及其更高的频率进行滤波。

砖墙式滤波器能实现这一响应。然而, 因为 CDC 器件测量从激励引脚到容性输入引脚的电荷, 所以外部滤波器只能使用无源器件。

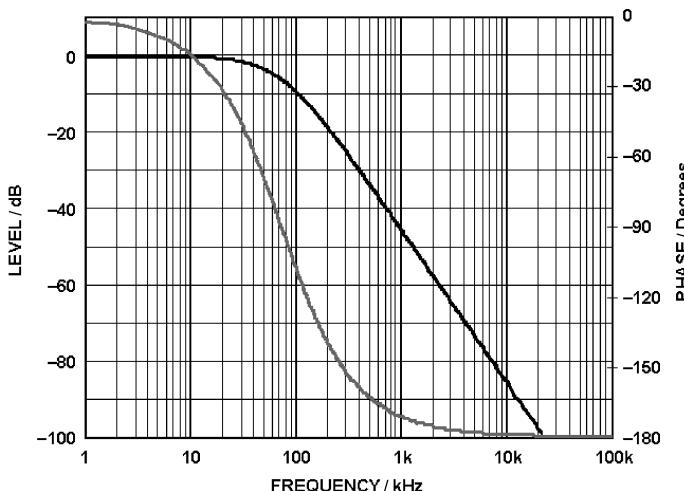

实际上, 无源滤波器有更慢的滚降。必须在 32 kHz 无衰减地通过与 32 kHz 倍频的衰减之间折中(见图 4)。

图 3 AD7150 滤波器响应

图 4 32 kHz 范围内的频率响应

图 5 抗混叠滤波器

## EMC 测试

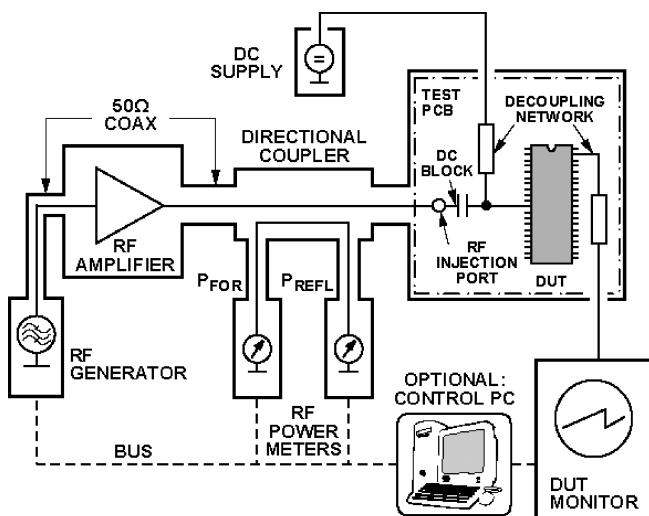

对于 EMC 测试, 使用图 4 所示 DPI 设置; 这个图摘自 IEC 62132 第一部分。DPI 测试设

[www.BDTIC.com/ADI](http://www.BDTIC.com/ADI)

置包括一个 RF 信号发生器,一个 RF 放大器,一个定向耦合器(耦合器通过探头与一个 RF 功率计连接来测量到 DUT 的前向功率)。测量反射功率是可选的,因为在 DPI 扫描时前向功率必须保持不变。

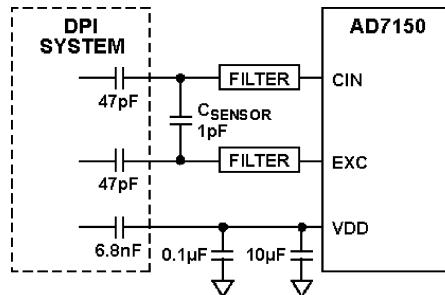

AD7150 的所有引脚必须进行 EMC 测试。EXC,CIN 和 VDD 引脚是最敏感的。因此,本应用笔记关注重点是这些引脚。根据 IEC 62132 第 4 部分,通过 AC 耦合(见图 7)对 CIN、EXC 和 VDD 引脚逐一施加连续的 RF 频率。测试方法推荐使用 6.8 nF 的 AC 耦合电容。这个电容用在 VDD 引脚。然而,EXC 和 CIN 引脚使用更小的电容(47 pF),因为 IEC 62132 第 4 部分中建议的电容值超过了 AD7150 允许的最大接地电容。

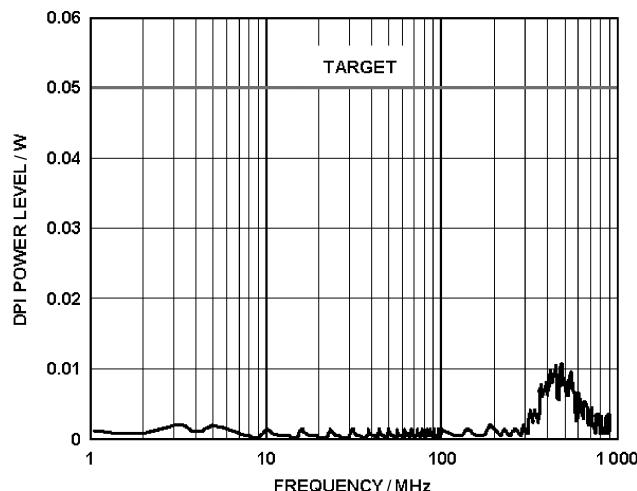

频率以 1 MHz 为步进从 1 MHz 增加到 100 MHz,以 10 MHz 为步进从 100 MHz 增加到 1 000 MHz。ADI 以 50 mW 为目标功率。如果在频率扫描时注入 50 mW 功率后 AD7150 没有误触发,就认为测试通过。如果注入 50 mW 功率后出现误触发,就认为测试失败。如果器件在任一频率没有通过 50 mW 目标功率测试,那么器件没有误触发的最大 RF 功率就确定了。

DPI 测试在更低频率范围从 1 MHz 到 3 MHz 以更小的 200 Hz 为步进重复进行。因为 AD7150 对 32 kHz 信号及其倍频信号敏感,所以进行这个测试,外部 EMC 滤波器在这个频率范围内效率较低。

对所有 EMC 测试,AD7150 的输入范围设置为 2 pF,灵敏度设为十进制的 10。

图 6 DPI 测试设置

图 7 AD7150 与 DPI 系统的连接

## 没有外部滤波器时 AD7150 的 EMC 性能

为了确定 AD7150 的 EMC 性能,先对 AD7150 在没有外部滤波器时进行 EMC 测试。由于 CIN 引脚是最敏感的,所以在 DPI 测试中使用这个引脚。如图 8 所示,引起误触发的功率远低于 50 mW 的目标。

请注意,以 50 mW 为目标功率时,AD7150 仍保持正常功能。尽管器件在这个功率测试时有误触发,但它不会被锁死。

图 8 没有外部滤波器时在引脚 CIN 以 1 MHz 为步进从 1 MHz 到 100 MHz,以 10 MHz 为步进从 100 MHz 到 1 000 MHz 的 DPI 测试

## 选择外部滤波器

砖墙式滤波器有最佳的滤波器响应——对 32 kHz 信号无衰减, 对 64 kHz 附近及更高的频率有抑制。因为 AD7150 不能与有源器件一起使用, 所以在 CIN 和 EXC 引脚上对不同种类的无源滤波器进行了评估。

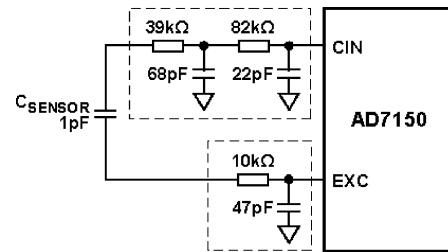

在对几个无源滤波器结构进行评估之后, 二阶滤波器被选来用在 CIN 引脚, 因为它使用合理的少量非精密器件提供了很好的频率响应和滚降性能。

对于 EXC 引脚, 用一阶滤波器足以达到期望的 EMC 性能。最后, VDD 引脚使用标准去耦电容(一个 0.1  $\mu$ F 陶瓷电容与一个 10  $\mu$ F 钨电容并联到 GND)。用这些去耦电容可以达到期望的 EMC 性能。

选择这些器件是 EMC 性能和 AD7150 近程检测精度最好的折中。虽然 AD7150 的精度降低了, 但它仍然能在近程应用中使用。

连接到 CIN 引脚的二阶滤波器和连接到 EXC 引脚的一阶滤波器的值如图 9 所示。一个 1 pF 陶瓷电容用在容性传感器的位置。二阶滤波器的截止频率是 72.76 kHz, 在 32 kHz 的相移是  $-48^\circ$ , 在 32 kHz 的衰减是  $-1.62$  dB。

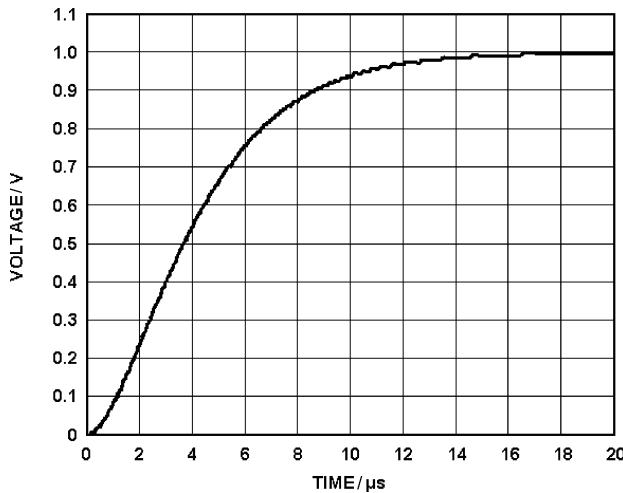

图 10 和图 11 分别为二阶无源滤波器的频率响应和阶跃响应。

图 9 AD7150 前端的无源滤波器

图 11 二阶无源滤波器的阶跃响应

## 有外部滤波器时 AD7150 的性能

24

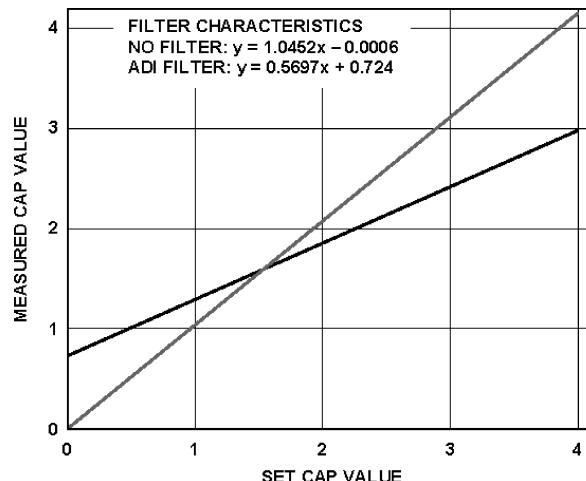

与 CIN 和 EXC 引脚连接的外部滤波器影响 AD7150 转换的精度。图 12 表明输入到输出传递函数的变化。有外部滤波器时，失调误差为 0.724 pF，当使用 2 pF 输入电容时增益误差为 -0.859 pF(相当于 -42.9%)。电源抑制降低到 40 fF/V。

图 12 有外部滤波器和无外部滤波器时 AD7150 的输入到输出传递函数

## 有外部滤波器时 AD7150 的 EMC 性能

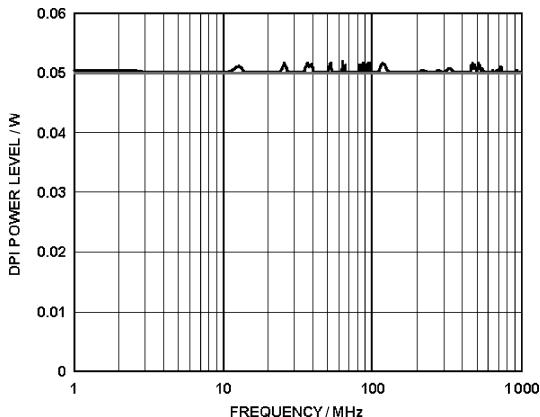

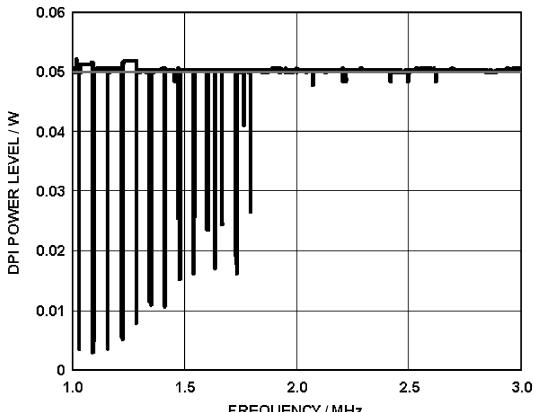

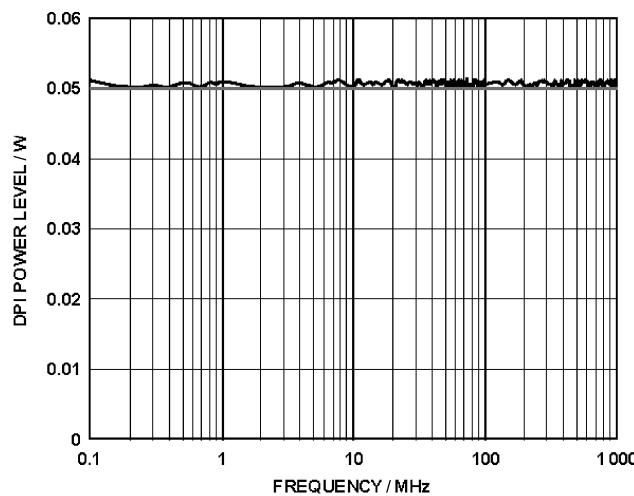

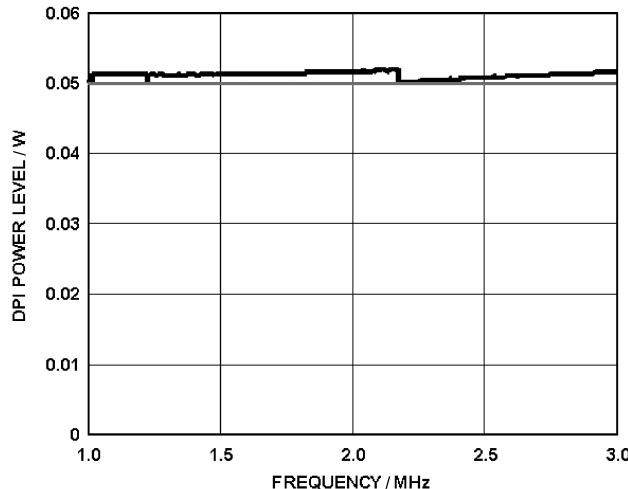

### 1. 在 CIN 引脚上的 DPI

当 RF 频率以 1 MHz 为步进从 1 MHz 扫描到 100 MHz 和以 10 MHz 为步进从 100 MHz 扫描到 1 000 MHz 时,如图 13 所示,AD7150 的输出端没有误触发出现。如图 14 所示,当以 200 Hz 为步进,从 1 MHz 到 3 MHz 重复 DPI 测试时,外部无源滤波器在 1.9 MHz 以上频率有全面的抗干扰性能。在低频时,外部滤波器不太有效——对 32 kHz 倍频附近的窄带频率仍然有一些敏感性。

图 13 CIN 引脚:从 1 MHz 到 1 000 MHz 扫描

图 14 CIN 引脚以 200 Hz 为步进从 1 MHz 到 3 MHz 的精细扫描

[www.BDTIC.com/ADI](http://www.BDTIC.com/ADI)

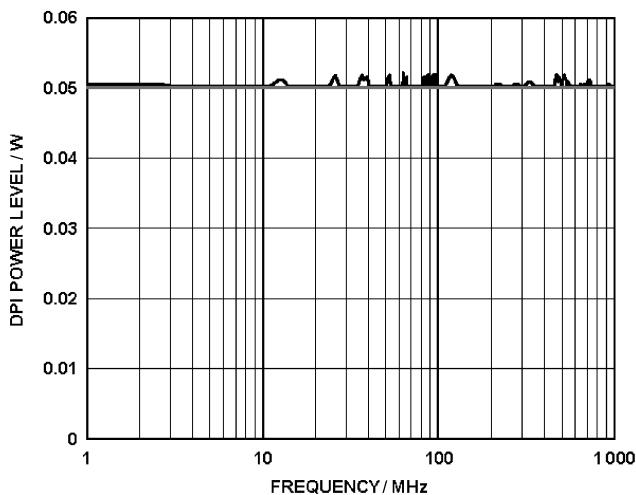

## 2. 在 EXC 引脚上的 DPI

在 EXC 引脚上 RF 频率以 1 MHz 为步进从 1 MHz 扫描到 100 MHz 并以 10 MHz 为步进从 100 MHz 扫描到 1 000 MHz 时,如图 15 所示,AD7150 的输出端没有误触发现。如图 16 所示,当以 200 Hz 为步进,从 1 MHz 到 3 MHz 重复 DPI 测试时,仍然没有误触发现。这样,当 EXC 引脚连接一阶滤波器时可以达到较高的 EMC 性能。

图 15 EXC 引脚:从 1 MHz 到 1 000 MHz 扫描

图 16 EXC 引脚:以 200 Hz 为步进从 1 MHz 到 3 MHz 扫描

www.BDTIC.com/ADI

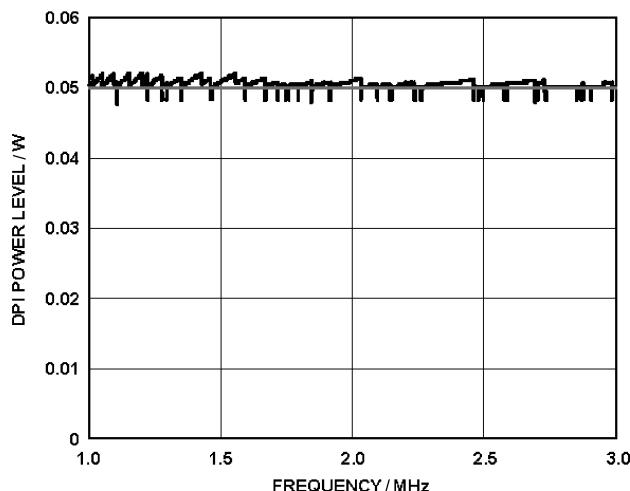

### 3. 在 VDD 引脚上的 DPI

在 VDD 引脚上也进行了 DPI 测试。当 RF 频率以 1 MHz 为步进从 1 MHz 扫描到 100 MHz 并以 10 MHz 为步进从 100 MHz 扫描到 1 000 MHz 时, 用标准去耦电容连接 VDD 引脚的 AD7150 没有误触发出现(见图 17)。当频率以 200 Hz 为步进从 1 MHz 扫描到 3 MHz 时, 仍然没有误触发出现(见图 18)。因此, 去耦电容提供了高水平的 EMC 性能。

图 17 VDD 引脚在 1 MHz 到 1 000 MHz 范围的 DPI 测试

图 18 VDD 引脚以 200 Hz 为步进从 1 MHz 到 3 MHz 扫描

www.BDTIC.com/ADI

## 结 论

以目标功率 50 mW 对 AD7150 进行 EMC 测试时，器件没有栓锁。在有 EMC 干扰时，器件继续进行转换，EMC 干扰取消后它能回到预期的精度。

在本应用笔记中，推荐用外部无源滤波器来提高 AD7150 的 EMC 性能。当 CIN 和 EXC 引脚连接外部滤波器并且 VDD 引脚使用标准去耦电容时，器件通过 1.9 MHz 以上频率的 EMC 测试。当频率小于 1.9 MHz 时，器件对 32 kHz 倍频附近范围的频率表现出一些敏感性。

没有外部滤波器并且以 50 mW 为目标功率水平时，AD7150 不能通过在 IEC 62132 第 4 部分中描述的 EMC 测试。然而，AD7150 总能保持正常功能。50 mW 功率水平不会引起 AD7150 的栓锁。

当使用外部 EMC 滤波器时，AD7150 仍能满足近程检测应用的需求。滤波器会导致 AD7150 精度的降低，然而其精度对于近程检测系统来说足够了。

本应用笔记中讨论的外部 EMC 滤波器优化了 AD7150 的 EMC 性能。如果使用不太标准的滤波器，AD7150 的精度会降低一点儿。这是 EMC 性能与 AD7150 精度的折中。

# AN - 1021 应用笔记

## 基于 MMSE 的触摸屏应用多点校准算法

作者: Ning Jia

### 简介

现代设备多以液晶屏及触摸屏技术作为用户界面。因其简单的构造和众所周知的操作原理, 电阻式触摸屏是讲求成本型设计的首选。然而, 电阻式触摸屏存在的机械对齐误差及缩放因子, 影响了触摸屏产生的 X、Y 坐标。因此, 很难将触摸屏的坐标与其后显示屏(液晶屏等)完全对齐。含有触摸屏的最终产品出厂时, 必须首先执行校准算法。

针对触摸屏的经典校准算法是一种基于三个参照点的三点校准算法。这种经典三点校准算法效率高、效果好, 但当触摸屏较大时, 性能较低。本应用笔记针对电阻式触摸屏, 提出了一种基于最小均方误差(MMSE)的多点校准算法, 采用三个以上的参照点。数学推导和实验均证明, 本算法的精度优于经典三点校准算法。

### 数学原理

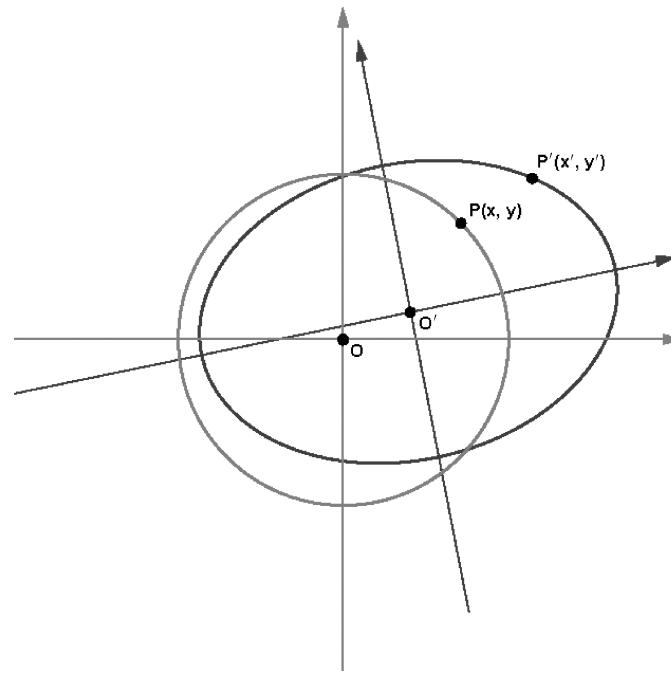

图 1 所示红色圆形的理想中心为 O(原点), 理想半径为 R。假定该红色圆形代表的是触摸屏下方液晶屏所显示的图像。蓝色椭圆表示用户沿着液晶屏所示红色圆形进行触摸时, 触摸屏产生的一组点(图中为夸张的显示)。因此, 受电阻式触摸屏本身机械对齐误差和缩放因子的影响, 重构后的图像在各坐标轴上均以不同的因子旋转、平移和缩放。校准算法面临的挑战是如何将触摸屏产生的坐标转换成精确代表所示图像的一组坐标。

设存在一点, 其理想坐标为  $P(x, y)$ , 且触摸屏产生的坐标为  $P'(x', y')$ 。(P 点位于红色圆形上, 与其对应的 P' 点则位于蓝色椭圆上。)设  $P'(x', y')$  旋转  $\theta$  角度, 然后在 X 和 Y 轴分别缩放  $K_x$  和  $K_y$ , 分别平移  $T_x$  和  $T_y$ , 可以回到其理想坐标  $P(x, y)$ 。标准算法的目的是计算系

## 第一部分 ADC 产品的应用

数  $\theta$ 、 $K_X$ 、 $K_Y$ 、 $T_X$  和  $T_Y$ 。然后可利用这些系数对触摸屏直接产生的坐标进行校准。

图 1 触摸屏误差

为了便于大家理解以上分析,不妨假设  $P'(x', y')$  为触摸屏直接产生的坐标,其等价极坐标表达式  $P'(R\cos\theta_0, R\sin\theta_0)$ 。另外假设,与  $P'(x', y')$  对应的理想坐标为  $P(x, y)$ 。鉴于  $P'(x', y')$  与  $P(x, y)$  的关系,可得:

$$P(x, y) = P(K_X R \cos(\theta_0 + \theta) + T_X, K_Y R \sin(\theta_0 + \theta) + T_Y)$$

根据三角函数,有

$$\cos(\theta_0 + \theta) = \cos\theta_0 \cos\theta - \sin\theta_0 \sin\theta$$

及

$$\sin(\theta_0 + \theta) = \sin\theta_0 \cos\theta + \cos\theta_0 \sin\theta$$

可得以下方程式:

$$\begin{cases} x' = R \cos\theta_0 \\ y' = R \sin\theta_0 \end{cases}$$

$$\begin{cases} x = K_X R \cos(\theta_0 + \theta) + T_X = K_X R (\cos\theta_0 \cos\theta - \sin\theta_0 \sin\theta) + T_X \\ y = K_Y R \sin(\theta_0 + \theta) + T_Y = K_Y R (\sin\theta_0 \cos\theta + \cos\theta_0 \sin\theta) + T_Y \end{cases}$$

则有

$$\begin{cases} x = \cos\theta K_x x' - \sin\theta K_y y' + T_x \\ y = \cos\theta K_y x' - \sin\theta K_x y' + T_y \end{cases}$$

其中：

$\theta$ 、 $K_x$ 、 $K_y$ 、 $T_x$  和  $T_y$  均为常数。

设：

$$\begin{aligned} \cos\theta K_x &= KX_1 \\ -\sin\theta K_x &= KX_2 \\ T_x &= KX_3 \\ \sin\theta K_y &= KY_1 \\ \cos\theta K_y &= KY_2 \\ T_y &= KY_3 \end{aligned}$$

则前述方程式可改写为：

$$\begin{cases} x = KX_1 x' + KX_2 y' + KX_3 \\ y = KY_1 y' + KY_2 y' + KY_3 \end{cases}$$

可利用以上方程式来校准  $P'(x', y')$ , 从而得到  $P(x, y)$ 。对于 X 轴和 Y 轴而言, 各方程式中均含有三个未知系数。

## 经典三点校准算法

通过上述分析, 我们得到了 X 轴或 Y 轴的校准方程式。对于 X 轴或 Y 轴, 各方程式均含有三个未知系数。因此, 如果可获得三个不相关参照点的信息, 则可构建出线性方程组, 通过解方程来获得未知系数的解。

设三个参照点的理想坐标为  $(x_0, y_0)$ 、 $(x_1, y_1)$  和  $(x_2, y_2)$ , 其对应的采样坐标分别为  $(x'_0, y'_0)$ 、 $(x'_1, y'_1)$  和  $(x'_2, y'_2)$ , 则 X 轴和 Y 轴的方程式分别为

$$\begin{cases} x_0 = KX_1 x'_0 + KX_2 y'_0 + KX_3 \\ x_1 = KX_1 x'_1 + KX_2 y'_1 + KX_3 \\ x_2 = KX_1 x'_2 + KX_2 y'_2 + KX_3 \end{cases}$$

及

$$\begin{cases} y_0 = KY_1 x'_0 + KY_2 y'_0 + KY_3 \\ y_1 = KY_1 x'_1 + KY_2 y'_1 + KY_3 \\ y_2 = KY_1 x'_2 + KY_2 y'_2 + KY_3 \end{cases}$$

基于此, 可将以上述方程改写为矩阵模式:

## 第一部分 ADC 产品的应用

$$\begin{bmatrix} x'_0 & y'_0 & 1 \\ x'_1 & y'_1 & 1 \\ x'_2 & y'_2 & 1 \end{bmatrix} \cdot \begin{bmatrix} KX_1 \\ KX_2 \\ KX_3 \end{bmatrix} = \begin{bmatrix} x_0 \\ x_1 \\ x_2 \end{bmatrix}$$

及

$$\begin{bmatrix} x'_0 & y'_0 & 1 \\ x'_1 & y'_1 & 1 \\ x'_2 & y'_2 & 1 \end{bmatrix} \cdot \begin{bmatrix} KY_1 \\ KY_2 \\ KY_3 \end{bmatrix} = \begin{bmatrix} y_0 \\ y_1 \\ y_2 \end{bmatrix}$$

在此基础上,可以通过解方程算出校准系数  $KX_1$ 、 $KX_2$ 、 $KX_3$ 、 $KY_1$ 、 $KY_2$  和  $KY_3$ 。

通过消元法求得的结果如下:

设  $k = (x'_0 - x'_2)(y'_1 - y'_2) - (x'_1 - x'_2)(y'_0 - y'_2)$ , 则

$$KX_1 = \frac{(x_0 - x_2)(y'_1 - y'_2) - (x_1 - x_2)(y'_0 - y'_2)}{k}$$

$$KX_2 = \frac{(x_1 - x_2)(x'_1 - x'_2) - (x_0 - x_2)(x'_1 - x'_2)}{k}$$

$$KX_3 = \frac{y'_0(x'_2 x_1 - x'_1 x_2) + y'_1(x'_0 x_2 - x'_2 x_0) + y'_2(x'_1 x_0 - x'_0 x_1)}{k}$$

$$KY_1 = \frac{(y_0 - y_2)(x'_1 - x'_2) - (y_1 - y_2)(y'_0 - y'_2)}{k}$$

$$KY_2 = \frac{(y_1 - y_2)(x'_0 - x'_2) - (y_0 - y_2)(x'_1 - x'_2)}{k}$$

$$KY_3 = \frac{y'_0(x'_2 y_1 - x'_1 y_2) + y'_1(x'_0 y_2 - x'_2 y_0) + y'_2(x'_1 y_0 - x'_0 y_1)}{k}$$

## 基于 MMSE 的多点校准算法

利用经典三点校准算法得到的系数,可以将三个参照点校准到理想位置。然而,对于不在参照点附近的其他点,校准性能不甚理想,当触摸屏相对较大时尤其如此。示例部分的实验结果同样证实了这个问题。因此,可考虑利用三个以上的参照点,以获得最佳校准系数。

设有  $N+1$  个参照点 ( $N+1 > 3$ ), 其理想坐标为  $(x_0, y_0)$ 、 $(x_1, y_1)$ 、 $\dots$ 、 $(x_N, y_N)$ , 且其对应的采样坐标为  $(x'_0, y'_0)$ 、 $(x'_1, y'_1)$ 、 $\dots$ 、 $(x'_N, y'_N)$ , 则相应的方程式如下:

$$\begin{cases} x_0 = KX_1 x'_0 + KX_2 y'_0 + KX_3 \\ x_1 = KX_1 x'_1 + KX_2 y'_1 + KX_3 \\ \vdots \\ x_N = KX_1 x'_N + KX_2 y'_N + KX_3 \end{cases}$$

及

$$\begin{cases} y_0 = KY_1 x'_0 + KY_2 y'_0 + KY_3 \\ y_1 = KY_1 x'_1 + KY_2 y'_1 + KY_3 \\ \vdots \\ y_N = KY_1 x'_N + KY_2 y'_N + KY_3 \end{cases}$$

注意,各方程组中的方程数(N+1)均大于未知系数的个数(3)。

可见,我们的目的是算出适合全部(N+1)个参照点的最佳校准系数。获得最佳系数的方法是遵循 MMSE 规则。这正是这种算法称为基于 MMSE 的多点校准算法的原因所在。

以 X 轴为例,定义一个目标函数:

$$FX = \sum_{i=0}^N (KX_1 x'_i + KX_2 y'_i + KX_3 - x_i)^2$$

其中,FX 为参照点的误差平方和。KX<sub>1</sub>、KX<sub>2</sub> 和 KX<sub>3</sub> 的最佳系数指使目标函数 FX 最小的那些系数。因此,可使用以下方程式:

$$\begin{cases} \frac{\partial FX}{\partial KX_1} = 0 \\ \frac{\partial FX}{\partial KX_2} = 0 \\ \frac{\partial FX}{\partial KX_3} = 0 \end{cases}$$

即

$$\begin{cases} \frac{\partial FX}{\partial KX_1} = \sum_{i=0}^N 2x'_i (KX_1 x'_i + KX_2 y'_i + KX_3 - x_i) = 0 \\ \frac{\partial FX}{\partial KX_2} = \sum_{i=0}^N 2y'_i (KX_1 x'_i + KX_2 y'_i + KX_3 - x_i) = 0 \\ \frac{\partial FX}{\partial KX_3} = \sum_{i=0}^N 2(KX_1 x'_i + KX_2 y'_i + KX_3 - x_i) = 0 \end{cases}$$

以上方程式可简化为

$$\begin{cases} (\sum_{i=0}^N x_i'^2) KX_1 + (\sum_{i=0}^N x'_i y'_i) KX_2 + (\sum_{i=0}^N x'_i) KX_3 = \sum_{i=0}^N x'_i x'_i \\ (\sum_{i=0}^N x'_i y'_i) KX_1 + (\sum_{i=0}^N y'_i) KX_2 + (\sum_{i=0}^N y'_i) KX_3 = \sum_{i=0}^N y'_i x'_i \\ (\sum_{i=0}^N x'_i) KX_1 + (\sum_{i=0}^N y'_i) KX_2 + N \cdot KX_3 = \sum_{i=0}^N x_i \end{cases}$$

设

# 第一部分 ADC 产品的应用

$$R = \begin{bmatrix} \sum_{i=0}^N x_i'^2 & \sum_{i=0}^N x_i' y_i' & \sum_{i=0}^N x_i' \\ \sum_{i=0}^N x_i' y_i' & \sum_{i=0}^N y_i'^2 & \sum_{i=0}^N y_i' \\ \sum_{i=0}^N x_i' & \sum_{i=0}^N y_i' & N \end{bmatrix}, \quad KX = \begin{bmatrix} KX_1 \\ KX_2 \\ KX_3 \end{bmatrix}, \quad BX = \begin{bmatrix} \sum_{i=0}^N x_i' x_i \\ \sum_{i=0}^N y_i' x_i \\ \sum_{i=0}^N x_i \end{bmatrix}$$

基于此,可将各方程式改写为矩阵模式  $R \cdot KX = BX$ ,并可通过求解前述方程组算出最佳系数  $KX = R^{-1} \cdot BX$ 。

与 X 轴类似,设

$$KY = \begin{bmatrix} KY_1 \\ KY_2 \\ KY_3 \end{bmatrix}, \quad BY = \begin{bmatrix} \sum_{i=0}^N x_i' y_i \\ \sum_{i=0}^N y_i' y_i \\ \sum_{i=0}^N y_i \end{bmatrix}$$

然后即可通过求解方程组  $R \cdot KY = BY$ ,算出 Y 轴的最佳系数  $KY = R^{-1} \cdot BY$ 。

通过消元法求得的结果如下:

设

$$\begin{aligned} a_0 &= \frac{\sum x_i'^2}{\sum x_i'}, a_1 = \frac{\sum x_i' y_i'}{\sum y_i'}, a_2 = \frac{\sum x_i'}{N} \\ b_0 &= \frac{\sum x_i' y_i'}{\sum x_i'}, b_1 = \frac{\sum y_i'^2}{\sum y_i'}, b_2 = \frac{\sum y_i'}{N}, \\ c_0 &= \frac{\sum x_i' x_i'}{\sum x_i'}, c_1 = \frac{\sum y_i' x_i}{\sum y_i'}, c_2 = \frac{\sum x_i'}{N}, \\ d_0 &= \frac{\sum x_i' y_i}{\sum x_i'}, d_1 = \frac{\sum y_i' x_i}{\sum y_i'}, d_2 = \frac{\sum y_i'}{N} \end{aligned}$$

其中,  $\sum \cdot$  表示  $\sum_{i=0}^N \cdot$ 。

基于此,可将方程组  $R \cdot KX = BX$  和  $R \cdot KY = BY$  分别改写为

$$\begin{bmatrix} a_0 & b_0 & 1 \\ a_1 & b_1 & 1 \\ a_2 & b_2 & 1 \end{bmatrix} \cdot \begin{bmatrix} KX_1 \\ KX_2 \\ KX_3 \end{bmatrix} = \begin{bmatrix} c_0 \\ c_1 \\ c_2 \end{bmatrix}$$

及

$$\begin{bmatrix} a_0 & b_0 & 1 \\ a_1 & b_1 & 1 \\ a_2 & b_2 & 1 \end{bmatrix} \cdot \begin{bmatrix} KY_1 \\ KY_2 \\ KY_3 \end{bmatrix} = \begin{bmatrix} d_0 \\ d_1 \\ d_2 \end{bmatrix}$$

不难发现,以上方程组的格式与前面经典三点算法的方程组相同:

$$\begin{bmatrix} x'_0 & y'_0 & 1 \\ x'_1 & y'_1 & 1 \\ x'_2 & y'_2 & 1 \end{bmatrix} \cdot \begin{bmatrix} KX_1 \\ KX_2 \\ KX_3 \end{bmatrix} = \begin{bmatrix} x_0 \\ x_1 \\ x_2 \end{bmatrix}$$

及

$$\begin{bmatrix} x'_0 & y'_0 & 1 \\ x'_1 & y'_1 & 1 \\ x'_2 & y'_2 & 1 \end{bmatrix} \cdot \begin{bmatrix} KY_1 \\ KY_2 \\ KY_3 \end{bmatrix} = \begin{bmatrix} y_0 \\ y_1 \\ y_2 \end{bmatrix}$$

在此基础上,可利用相同的公式计算系数的结果。

设

$$k = (a_0 - a_2)(b_1 - b_2) - (a_1 - a_2)(b_0 - b_2)$$

则

$$KX_1 = \frac{(c_0 - c_2)(b_1 - b_2) - (c_1 - c_2)(b_0 - b_2)}{k}$$

$$KX_2 = \frac{(c_1 - c_2)(a_0 - a_2) - (c_0 - c_2)(a_1 - a_2)}{k}$$

$$KX_3 = \frac{b_0(a_2c_1 - a_1c_2) + b_1(a_0c_2 - a_2c_0) + b_2(a_1c_0 - a_0c_1)}{k}$$

$$KY_1 = \frac{(d_0 - d_2)(b_1 - b_2) - (d_1 - d_2)(b_0 - b_2)}{k}$$

$$KY_2 = \frac{(d_1 - d_2)(a_0 - a_2) - (d_0 - d_2)(a_1 - a_2)}{k}$$

$$KY_3 = \frac{b_0(a_2d_1 - a_1d_2) + b_1(a_0d_2 - a_2d_0) + b_2(a_1d_0 - a_0d_1)}{k}$$

## 基于 MMSE 的多点校准算法的分析

通过计算  $a_0, a_1, a_2; b_0, b_1, b_2; c_0, c_1, c_2$  和  $d_0, d_1, d_2$  可以发现,可将  $a_0, a_1, a_2$  当作基于 3 种不同方法的  $x'_i$  的加权平均值,可将  $b_0, b_1, b_2$  看作基于 3 种不同方法的  $y'_i$  的加权平均值。类似地,可将  $c_0, c_1, c_2$  当作基于 3 种不同方法的  $x_i$  的加权平均值, $d_0, d_1, d_2$  则可视为基于三种不同方法的  $y_i$  的加权平均。

由于最终方程组与前面经典 3 点算法的方程组具有相同格式,因此,可将基于 MMSE 规则的算法视为另一种 3 点算法。然而,基于 MMSE 的算法的区别在于,其采用的不是任何参照点的直接信息,而是参照点的加权平均信息。换言之,先要算出  $N+1$  个直接采样点

## 第一部分 ADC 产品的应用

$(x'_0, y'_0)、(x'_1, y'_1)、\dots、(x'_N, y'_N)$  的三个加权平均点  $(a_0, b_0)、(a_1, b_1)、(a_2, b_2)$ 。这 3 个加权平均点对应的理想坐标为  $(c_0, d_0)、(c_1, d_1)$  和  $(c_2, d_2)$ 。可见, 基于 MMSE 的算法等效于对这三个加权平均点而言的经典 3 点算法。

### 基于 MMSE 的多点校准算法的步骤

完成基于 MMSE 的多点校准算法的下列步骤:

- ① 选择  $N+1(N+1>3)$  个参照点  $(x_0, y_0)、(x_1, y_1)、\dots、(x_N, y_N)$ 。

- ② 得到触摸屏产生的参照点的采样坐标  $(x'_0, y'_0)、(x'_1, y'_1)、\dots、(x'_N, y'_N)$ 。

- ③ 利用本应用笔记给出的公式, 算出校准系数 KX 和 KY。包括以下公式:

$$k = (a_0 - a_2)(b_1 - b_2) - (a_1 - a_2)(b_0 - b_2)$$

$$KX_1 = \frac{(c_0 - c_2)(b_1 - b_2) - (c_1 - c_2)(b_0 - b_2)}{k}$$

$$KX_2 = \frac{(c_1 - c_2)(a_0 - a_2) - (c_0 - c_2)(a_1 - a_2)}{k}$$

$$KX_3 = \frac{b_0(a_2c_1 - a_1c_2) + b_1(a_0c_2 - a_2c_0) + b_2(a_1c_0 - a_0c_1)}{k}$$

$$KY_1 = \frac{(d_0 - d_2)(b_1 - b_2) - (d_1 - d_2)(b_0 - b_2)}{k}$$

$$KY_2 = \frac{(d_1 - d_2)(a_0 - a_2) - (d_0 - d_2)(a_1 - a_2)}{k}$$

$$KY_3 = \frac{b_0(a_2d_1 - a_1d_2) + b_1(a_0d_2 - a_2d_0) + b_2(a_1d_0 - a_0d_1)}{k}$$

- ④ 在正常操作中, 利用校准系数(KX, KY)和下列方程式计算  $P'(x', y')$  的校准点。

$$\begin{cases} x = KX_1 x' + KX_2 y' + KX_3 \\ y = KY_1 x' + KY_2 y' + KY_3 \end{cases}$$

### 示例

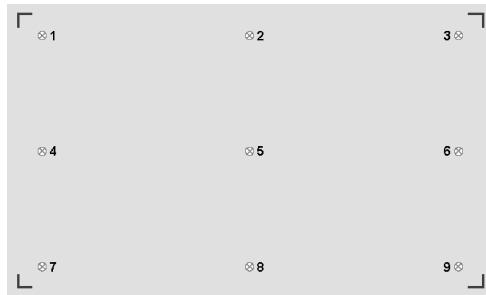

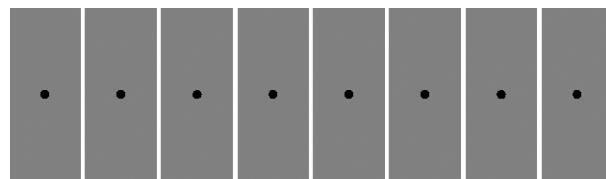

如图 2 所示, 从触摸屏上选择了 9 个点。其理想坐标为  $(3931, 3849)、(2047, 3849)、(164, 3849)、(3931, 2047)、(2047, 2047)、(164, 2047)、(3931, 246)、(2047, 246)$  和  $(164, 246)$ 。触摸屏产生的对应采样坐标为  $(3927, 3920)、(2054, 3936)、(193, 3943)、(3911, 2119)、(2054, 2127)、(195, 2164)、(3916, 355)、(2050, 351)$  和  $(189, 271)$ 。

www.BDTIC.com/ADI

之间存在极大的误差。

图 2 选择参照点

接下来的 3 个实验分别采用经典 3 点算法、基于 MMSE 的 5 点算法和基于 MMSE 的 9 点算法：

- 经典 3 点算法选择 3 个参照点，即图 2 中的点 1、点 6 和点 8。相应的校准系数为：

$$KX_1 = +1.011238, KX_2 = -0.003952, KX_3 = -24.638760$$

$$KY_1 = +0.009894, KY_2 = +1.005168, KY_3 = -130.112700$$

利用以上系数，校准后的结果列于表 1 中。

- 基于 MMSE 的 5 点算法选择 5 个参照点，即图 2 中的点 1、点 3、点 5、点 7 和点 9。相应的校准系数为：

$$KX_1 = +1.009899, KX_2 = -0.002260, KX_3 = -23.715720$$

$$KY_1 = +0.008494, KY_2 = +1.006247, KY_3 = -121.821000$$

利用以上系数，校准后的结果列于表 2 中。

- 基于 MMSE 的 9 点算法选择 9 个参照点，即图 2 中的点 1、点 2、点 3、点 4、点 5、点 6、点 7、点 8 和点 9。相应的校准系数为：

$$KX_1 = +1.011161, KX_2 = -0.001887, KX_3 = -25.777180$$

$$KY_1 = +0.009718, KY_2 = +1.006107, KY_3 = -126.258100$$

利用以上系数，校准后的结果列于表 3 中。

表 1 经典 3 点算法的结果

| 点(X, Y) | 1           | 2           | 3          | 4           | 5           | 6          | 7          | 8          | 9         |

|---------|-------------|-------------|------------|-------------|-------------|------------|------------|------------|-----------|

| 理想坐标    | (3931,3849) | (2047,3849) | (164,3849) | (3931,2047) | (2047,2047) | (164,2047) | (3931,246) | (2047,246) | (164,246) |

| 采样坐标    | (3927,3920) | (2054,3936) | (193,3943) | (3911,2119) | (2054,2127) | (195,2164) | (3915,331) | (2050,354) | (189,371) |

| 校准坐标    | (3931,3849) | (2037,3846) | (155,3835) | (3922,2039) | (2044,2028) | (164,2047) | (3933,242) | (2047,246) | (165,244) |

| 误差      | (0,0)       | (-10,-3)    | (-9,-14)   | (-9,-8)     | (-3,-19)    | (0,0)      | (+2,-4)    | (0,0)      | (+1,-2)   |

| 误差平方和   | (276,650)   |             |            |             |             |            |            |            |           |

# 第一部分 ADC 产品的应用

表 2 基于 MMSE 的 5 点算法的结果

| 点(X,Y) | 1           | 2           | 3          | 4           | 5           | 6          | 7          | 8          | 9         |

|--------|-------------|-------------|------------|-------------|-------------|------------|------------|------------|-----------|

| 理想坐标   | (3931,3849) | (2047,3849) | (164,3849) | (3931,2047) | (2047,2047) | (164,2047) | (3931,246) | (2047,246) | (164,246) |

| 采样坐标   | (3927,3920) | (2054,3936) | (193,3943) | (3911,2119) | (2054,2127) | (195,2164) | (3915,331) | (2050,354) | (189,371) |

| 校准坐标   | (3933,3856) | (2042,3856) | (162,3847) | (3921,2044) | (2046,2036) | (168,2057) | (3929,245) | (2046,252) | (166,253) |

| 误差     | (2,7)       | (-5,+7)     | (-2,-2)    | (-10,-3)    | (-1,-11)    | (4,10)     | (-2,-1)    | (-1,+6)    | (+2,+7)   |

| 误差平方和  | (159,418)   |             |            |             |             |            |            |            |           |

表 3 基于 MMSE 的 9 点算法的结果

| 点(X,Y) | 1           | 2           | 3          | 4           | 5           | 6          | 7          | 8          | 9         |

|--------|-------------|-------------|------------|-------------|-------------|------------|------------|------------|-----------|

| 理想坐标   | (3931,3849) | (2047,3849) | (164,3849) | (3931,2047) | (2047,2047) | (164,2047) | (3931,246) | (2047,246) | (164,246) |

| 采样坐标   | (3927,3920) | (2054,3936) | (193,3943) | (3911,2119) | (2054,2127) | (195,2164) | (3915,331) | (2050,354) | (189,371) |

| 校准坐标   | (3938,3856) | (2044,3854) | (162,3842) | (3925,2044) | (2047,2034) | (167,2053) | (3932,245) | (2046,250) | (165,249) |

| 误差     | (7,7)       | (-3,+5)     | (-2,-7)    | (-6,-3)     | (0,-13)     | (3,6)      | (+1,-1)    | (-1,+4)    | (+1,+3)   |

| 误差平方和  | (110,363)   |             |            |             |             |            |            |            |           |

## 结 论

如前述实验结果所示,无论采用哪种校准算法,校准坐标均远远优于直接采样坐标。另外,通过比较 3 种实验,可得出以下结论

- 经典 3 点校准算法有助于将 3 个参照点校准到理想位置。另外,对于靠近 3 个参照点的点,其性能表现非常好。然而,对于不在参照点附近的点,经典 3 点校准算法的表现不甚理想。这种算法的误差平方和是测试所用 3 种算法中最大的。因此,对于触摸屏尺寸相对较大的应用,经典 3 种校准算法并非好的选择。

- 对于某些点(接近参照点的点),基于 MMSE 的多点校准算法的表现不如经典 3 点校准算法。然而,就整个触摸屏来看,基于 MMSE 的多点校准算法的误差平方和小于经典 3 点算法,因为它利用了 3 个以上参照点的信息。因而,总体而言,其性能优于经典 3 点算法。

- 对于基于 MMSE 的多点校准算法,使用的参照点越多,性能越佳。

实验结果与数学推导相符合。

## 代码执行

以 C 语言编写的校准算法代码见“编码”部分。有 3 个参照点时，代码执行经典 3 点校准算法。有 3 个以上的参照点时，代码执行基于 MMSE 的多点校准算法。代码已通过 ADuC7026 测试(ADuC7026 是 ADI 公司出品的一款 MCU 产品)。3 个示例实验的结果均采用该代码计算得到。

## 编 码

```

#define N 9 // number of reference points for calibration algorithm

signed short int ReferencePoint[N][2]; // ideal position of reference points

signed short int SamplePoint[N][2]; // sampling position of reference points

double KX1, KX2, KX3, KY1, KY2, KY3; // coefficients for calibration algorithm

void Do_Calibration(signed short int * Px, signed short int * Py)// do calibration for point(Px, Py)

// using the calculated coefficients

{

* Px = (signed short int)(KX1 * (* Px) + KX2 * (* Py) + KX3 + 0.5);

* Py = (signed short int)(KY1 * (* Px) + KY2 * (* Py) + KY3 + 0.5);

}

int Get_Calibration_Coefficient() //calculate the coefficients for calibration algorithm;

//KX1, KX2, KX3, KY1, KY2, KY3

{

int i;

int Points = N;

double a[3], b[3], c[3], d[3], k;

if(Points < 3)

{

return 0;

}

else

{

if(Points == 3)

{

for(i=0; i<Points; i++)

```

# 第一部分 ADC 产品的应用

```

a[i] = (double)(SamplePoint[i][0]);

b[i] = (double)(SamplePoint[i][1]);

c[i] = (double)(ReferencePoint[i][0]);

d[i] = (double)(ReferencePoint[i][1]);

}

}

else if(Points>3)

{

for(i = 0; i<3; i++)

{

a[i] = 0;

b[i] = 0;

c[i] = 0;

d[i] = 0;

}

for(i = 0; i<Points; i++)

{

a[2] = a[2] + (double)(SamplePoint[i][0]);

b[2] = b[2] + (double)(SamplePoint[i][1]);

c[2] = c[2] + (double)(ReferencePoint[i][0]);

d[2] = d[2] + (double)(ReferencePoint[i][1]);

a[0] = a[0] + (double)(SamplePoint[i][0]) * (double)(Sample-

Point[i][0]);

a[1] = a[1] + (double)(SamplePoint[i][0]) * (double)(Sample-

Point[i][1]);

b[0] = a[1];

b[1] = b[1] + (double)(SamplePoint[i][1]) * (double)(Sample-

Point[i][1]);

c[0] = c[0] + (double)(SamplePoint[i][0]) * (double)(Referen-

cePoint[i][0]);

c[1] = c[1] + (double)(SamplePoint[i][1]) * (double)(Referen-

cePoint[i][0]);

d[0] = d[0] + (double)(SamplePoint[i][0]) * (double)(Referen-

cePoint[i][1]);

d[1] = d[1] + (double)(SamplePoint[i][1]) * (double)(Referen-

cePoint[i][1]);

}

a[0] = a[0]/a[2];

a[1] = a[1]/b[2];

b[0] = b[0]/a[2];

b[1] = b[1]/b[2];

c[0] = c[0]/a[2];

c[1] = c[1]/b[2];

d[0] = d[0]/a[2];

}

```

```

d[1] = d[1]/b[2];

a[2] = a[2]/Points;

b[2] = b[2]/Points;

c[2] = c[2]/Points;

d[2] = d[2]/Points;

}

k = (a[0] - a[2]) * (b[1] - b[2]) - (a[1] - a[2]) * (b[0] - b[2]);

KX1 = ((c[0] - c[2]) * (b[1] - b[2]) - (c[1] - c[2]) * (b[0] - b[2]))/k;

KX2 = ((c[1] - c[2]) * (a[0] - a[2]) - (c[0] - c[2]) * (a[1] - a[2]))/k;

KX3 = (b[0] * (a[2] * c[1] - a[1] * c[2]) + b[1] * (a[0] * c[2] - a[2] * c[0]) + b[2]

* (a[1] * c[0] - a[0] * c[1]))/k;

KY1 = ((d[0] - d[2]) * (b[1] - b[2]) - (d[1] - d[2]) * (b[0] - b[2]))/k;

KY2 = ((d[1] - d[2]) * (a[0] - a[2]) - (d[0] - d[2]) * (a[1] - a[2]))/k;

KY3 = (b[0] * (a[2] * d[1] - a[1] * d[2]) + b[1] * (a[0] * d[2] - a[2] * d[0]) + b[2]

* (a[1] * d[0] - a[0] * d[1]))/k;

return Points;

}

}

```

## 参考文献

Vidales, Carlos E. "How to Calibrate Touch Screens, Embedded Systems Design." Embedded.com, May 31, 2002. Embedded Systems Design. May 27, 2009.

## AN - 354 应用笔记 应用工程师问答(1)

作者:James Bryant

### 几个问题

问:我的多路复用 ADC 系统不太正常,是什么原因?

42

答:在进一步查找原因之前,你是否已经把多路复用器所有未使用的通道接地了?

问:没有。但是你怎么知道是这个问题呢?

答:因为悬空的引脚是导致含有 COMS 多路复用器的系统出现问题的最常见的原因之一。未使用的多路复用器的输入和输出引脚(无论是集成在多路复用 ADC 中的或者属于独立多路复用器一部分的)能将来自杂散场的信号引入器件的衬底,形成杂散衬底器件。此后,甚至在未使用的通道处于关闭状态时,开启状态的通道的性能也可能会严重下降(在可能性很小的极端情况下,杂散信号的注入会形成 4 层杂散器件并损坏某些芯片)。

每当使用多路复用器时,其输入和输出引脚必须连接到供电轨范围内的电位。处理未使用通道的最好办法是把它们接地,但是也许连接到供电轨范围内的电位更方便。

### 启动时的问题

问:为了降低功耗,我的 ADC 只有在进行测量时上电。系统在连续工作时很精确,但是电源接通时却不太稳定。为什么?

答:每当 ADC 的电源接通进行转换时,可能有 3 个原因导致其工作不正常:参考电压的慢开启、随机的初始逻辑状态和系统闩锁。

对于不同的原因——热稳定性、电容充电、使用 PNP 晶体管带隙基准电压源时再生电流镜的缓慢启动——上电后几个毫秒内一些参考电压有较大误差的情况并不罕见。在 ADC 进行转换时,外部和内部参考电压上的这种误差会导致不准确的转换结果。

在启动时,典型 ADC 的逻辑是一个随机状态;对于此时触发的转换,ADC 可能不会正常工作。在一个转换触发后,逻辑应该返回正确的预转换状态——但是在 ADC 达到稳定并进行有效转换前需要两个转换周期。因此,一个比较好的一般方法是在上电后获得可信的转换结果前先进行两次“假”转换。可以清楚记得,一些 ADC 在上一次转换完成前又被触发进行转换会很不稳定,在这种情况下发生时,需要一到两个“假”转换来让逻辑返回到一个已知状态。

如果 ADC 的外部逻辑使 ADC 的忙信号延长,这个忙信号只有在开始下一次转换时才结束,重要的是要认识到,如果转换器上电后处于忙状态,那么这个忙信号可能会保持闩锁,直到接收到转换启动脉冲后才结束。在这种情况下,系统不能自启动。如果忙信号总是在上电时出现,在进行系统设计时,这个问题肯定会被认识到并得到解决;但是如果忙信号只是在上电时偶尔出现,系统可能会难以预测闩锁。作为一项规则,在启动时 ADC 的控制信号不应该取决于逻辑忙状态。

## 关于对数补偿电阻

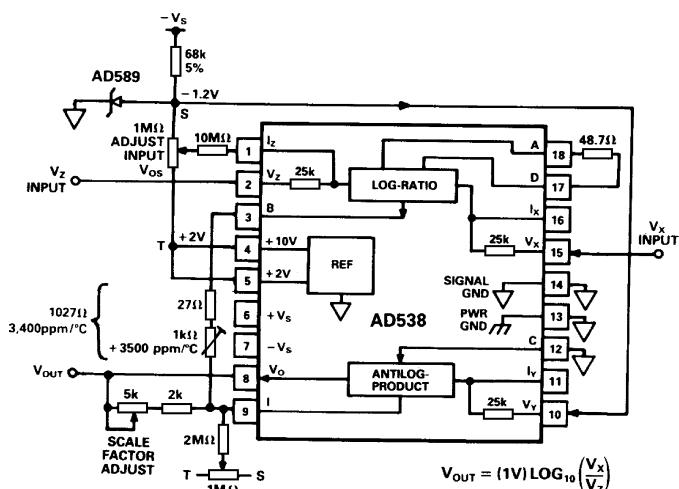

问:使用 AD538 Y[Z/X]m 类似的电路在内的对数电路设计:(例如,AD538 多功能单元数据手册中的图 6)需要“kT/q 补偿电阻”。这是什么?我从哪里能获得它们?

答:有两个相对的硅结,一个承载电流  $I$ ,另一个承载电流  $I_{REF}$ ,这两个硅结上的  $V_{BE}$  差值是  $(kT/q) \ln(I/I_{REF})$ 。这里,  $k/q$  表示玻耳兹曼常数与一个电子上的电荷(大约  $1/11605$  K/V)的比值,T 表示绝对温度(单位:开尔文)。

虽然在等温对中应用类似的结消除了反向饱和电流的温度灵敏度,但是  $kT/q$  仍与温度相关。为了在应用中消除这个相关性,必须在增益与结的绝对温度成反比例的电路中使用对数电压。在接近  $20^{\circ}\text{C}$  的合理温度范围,这可以通过使用具有约  $3\,400$  ppm/ $^{\circ}\text{C}$  正温度系数的  $1\,\text{k}\Omega$  增益设置电阻来实现,并使其与结保持相同温度。

## AN - 351 应用笔记 应用工程师问答(2)

作者:James Bryant

### 关于调整……

**问:** 我需要一些关于调整失调和增益的建议。

**答:** 不要调整! ——除非确有必要。尝试以下替代办法:(a)采用无须调整即符合规格要求的器件、元件和电路;(b)利用系统应用中的数字技术,通过软件进行调整。有时,如果考虑到电路设计、温度、振动以及性能和稳定性的持续寿命等因素的影响,还有随之而来的大量文档、复杂的调整细节等,采用调整电位计以及规格不达标的器件,虽然表面上节省了成本,但实际上得不偿失的。

**问:** 不过,如何调整模拟电路中的失调和增益误差呢?

**答:** 调整时顺序要正确,输入端也要正确。如果考虑到待调整电路的传输特性,方法一般都非常直观。

简单来说,线性模拟电路(如放大器、ADC、DAC)的理想传输特性通过以下公式得到:

$$OP = K \times IP \quad (1)$$

其中,OP 为输出,IP 为输入,K 为比例因子(请注意,这种简化表达式隐藏了多种问题:ADC 中的量化误差、当输入和输出采用不同形式时(如电压输入/电流输出)K 的量纲、意向失调等。)

在实际(非理想型)电路中,失调和增益误差,即 OS(折合至输入)和  $\Delta K$  同时分别出现在公式中,即:

$$OP = (K + \Delta K) \times (IP + OS) \quad (2)$$

$$OP = (K \times IP) + [(K \times OS) + (\Delta K \times IP) + (\Delta K \times OS)] \quad (3)$$

公式(2)和公式(3)并不完整,因为它们假定只有一种失调——即输入端的失调——但

这是最常见的情况。输入和输出失调相独立的系统,我们稍后再作探讨。

从公式(3)可知,当存在未知失调时,直接调整增益是无法做到的。必须首先调整失调。当 IP 设为 0 时,只有 OP 同为 0 时,才可调整失调。在此基础上,就可以调整增益了:当输入接近满量程(FS)时,则会调整增益,以使输出符合公式(1)的要求。

**问:双极性 ADC 和 DAC 又如何呢?**

**答:**许多 ADC 和 DAC 可以在单极性与双极性两种工作模式间来回切换,对于这类器件,应尽可能在单极性模式下调整其失调和增益。行不通时,或者当转换器仅工作于双极性模式下时,可以考虑其他方法。

可以将双极性转换器看作失调较大的单极性转换器(确切来说,其失调为 1 MSB——满量程范围的一半)。根据所用架构,该双极性失调(BOS)可能受到增益调整的影响,也可能不受其影响。受影响时,公式(1)成为:

$$OP = K \times (IP - BOS) \quad (4)$$

此时,在模拟零点处,失调进行调整,之后在接近 FS 时调整增益——无论 FS 为正还是负,但通常为正。这种方法通常用于双极性失调处于 DAC 范围内的 DAC。

若双极性失调不受增益调整影响,则有:

$$OP = K \times IP - BOS \quad (5)$$

此时,在负 FS 处调整失调,在(或接近,详见下文)正 FS 处调整增益。这种方法适用于多数 ADC 和 DAC,其中,双极性失调通过 DAC 之外的运算放大器和电阻来实现。

无疑,我们应该始终遵循数据手册中建议的方法,但是,当无数据手册可用时,一般而言,应在模拟零点处调整 DAC 失调,在负 FS 处调整 ADC 失调,并在接近正 FS 处调整二者的失调。

**问:为什么您一直提到“接近”满量程?**

**答:**放大器和 DAC 可以在零值和满量程时进行调整。对于 DAC 而言,全 1 时——最大的数字输入——对应产生低于“满量程”1 LSB 的输出,其中,“满量程”为基准电压的一定常数倍数;由于 DAC 的输出为基准电压与数字输入的归一化乘积,自然就得到上述结论。

ADC 不在零值和 FS 处进行调整。理想 ADC 的输出均经量化处理,第一个输出转换(从 00...00 至 00...01)发生于全“0”以上 1/2 LSB 时。此后,模拟输入每增加 1 LSB,就转换一次,直到最终转换发生于比 FS 低 1 个 1/2 LSB 时。非理想 ADC 的调整方法是,将其输入设为目标转换的标称值,然后进行调整,直到 ADC 输出在两个值之间均衡闪烁时。

可见,ADC 的失调是通过对第一个转换的输入进行调整的(即,比零值或负 FS 高 1/2 LSB 时,“接近”零或“接近”负 FS);增益则是在最后一个转换时进行调整的(即比负 FS 低 1 个 1/2 LSB,“接近”正 FS)。在失调调整过程中,以上程序会导致增益和失调误差相互影响,但可忽略不计。

**问:还有需要在“接近”满量程与非满量程处进行调整的其他异常现象吗?**

**www.BDTIC.com/ADI**

## 第一部分 ADC 产品的应用

答:同步电压频率转换器(SVFC),当其输出频率与其时钟频率存在谐波关系时,即当其输入非常接近时钟频率的 1/2、1/3 或 1/4 时,则很容易发生注入闭锁现象。SVFC 的 FS 为时钟频率的 1/2。使用调整工具可能会加重这个问题。因此,可以在 FS 的 95%左右调整 SVFC 的增益。

问:同时需要调整“输入”和“输出”失调的电路怎么办?

答:仪表放大器、隔离放大器等电路,一般有两个直流增益级,而且输入级增益可能是可变的。因此,对于二级放大器,若存在输入失调 IOS、输出失调 OOS、单位增益输入级,且第一级增益为 K,则其(零输入)输出 OP 为:

$$OP = OOS + K \times IOS \quad (6)$$

从公式(6)可以看出,如果增益保持不变,我们只需调整 IOS 或 OOS 二者之一即可使总失调归零(尽管在输入端采用长尾式双极性晶体管对时,如果同时调整 IOS 和 OOS,可以改善失调温度系数,但对于 FET 长尾对来说,情况不一定如此)。如果第一增益级可变,则必须同时调整两个失调。

这是通过迭代过程实现的。在零输入下,增益设为最大值,对输入失调进行调整,直到输出同样等于零为止。然后将增益减小至最小值,并对输出失调进行调整,直到输出再次为零为止。重复上述两步,直到无需进一步调整为止。增益必须在 IOS 和 OOS 都归零后进行调整;失调调整中使用的实际高增益值和低增益值并不重要。

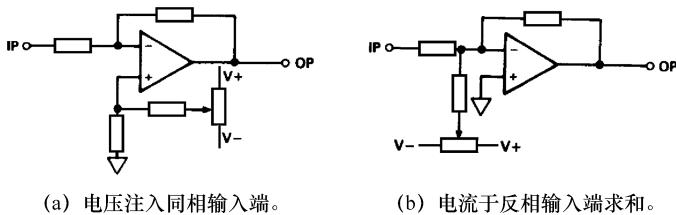

问:增益和失调调整应使用什么电路?

答:许多放大器(及部分转换器)配有专门的引脚,可用于调整增益和失调。更多的产品不存在这样的引脚。

一般情况下,失调是通过连接于两个指定引脚之间的电位计进行调整的,其游标(有时通过电阻)连接至任一电源。正确的连接方法和元件值,请参阅相应器件的数据手册。运算放大器之间最常见的差异之一在于失调校正电位计的值及其应连接的电源。

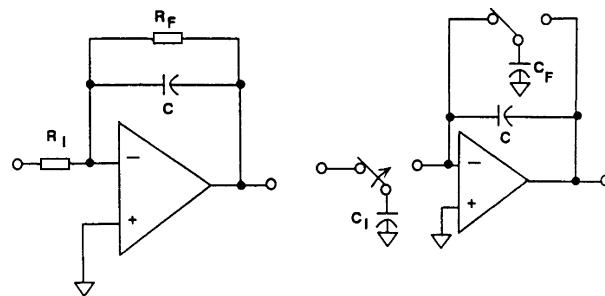

当放大器未提供独立的失调调整引脚时,通常可以向输入信号中添加一个失调调整常数。两种基本可能方法分别如图 1(a)和图 1(b)所示。对于差分输入运算放大器用作逆变器的情况(也是最常见的情况),如果需要对系统进行校正,图 1(a)所示方法最适合校正器件失调而非系统失调。对于单端连接,图 1(b)所示方法可用于系统失调,但是在小器件失调中应尽量避免这种方法,因为这种方法常用要求极大的求和电阻值(相对于信号输入电阻),才可:①避免求和点过载;②正确缩放校准电压并产生充分的衰减,以将差分电源电压漂移的影响降至最低限度。建议在电源与电位计之间设置电阻,以提高调整分辨率,降低功耗。

当电路中提供了增益调整引脚时,该引脚一般由一个可变电阻构成。关于其值和连接的详情,请参阅相应器件的数据手册。在不需要调整增益时,可以用其电阻值相当于建议调整电位计最大值一半的固定电阻替代该电阻。

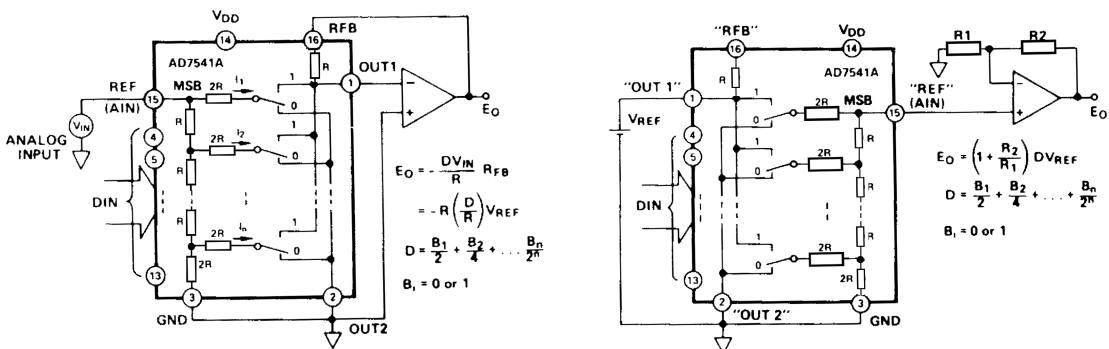

在未提供增益调整引脚时,一般需要添加外部可变增益级才可实现增益调整。在此以采用

图 1 用于失调调整的两种连接

梯形网络的 DAC 为例进行说明。如果梯形网络采用电流模式(图 2(a)),基准引脚的输入阻抗不随数字码而变动,且该 DAC 的增益可以通过与基准输入引脚或反馈电阻串联的小可变电阻进行调整。然而,如果该 DAC 采用电压模式(图 2(b)),则基准输入阻抗随数字码而变动,且只能通过改变基准电压——这种可能性并非始终都存在——或缓冲放大器的增益来调整增益。

可见,对于未搭载增益调整功能的电路,调整增益的可能性因具体情况而异,每种情况都需单独评估。

图 2 基本 DAC 电路比较

# AN - 586 应用笔记

## 高速模数转换器的 LVDS 数据输出

作者: Cindy Bloomingdale Gary Hendrickson

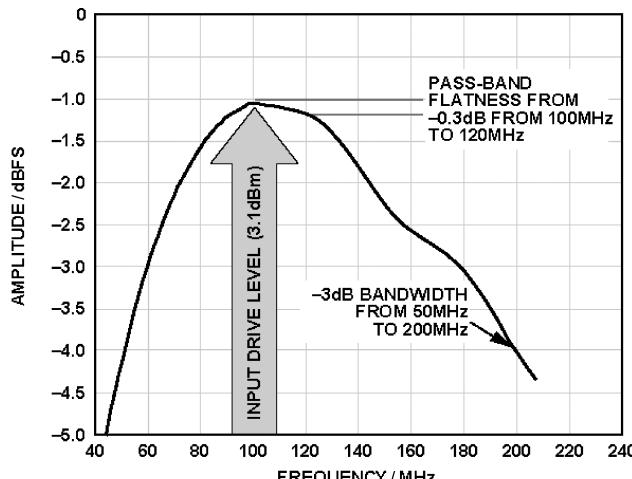

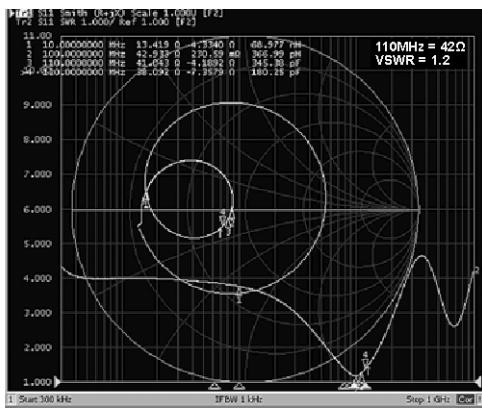

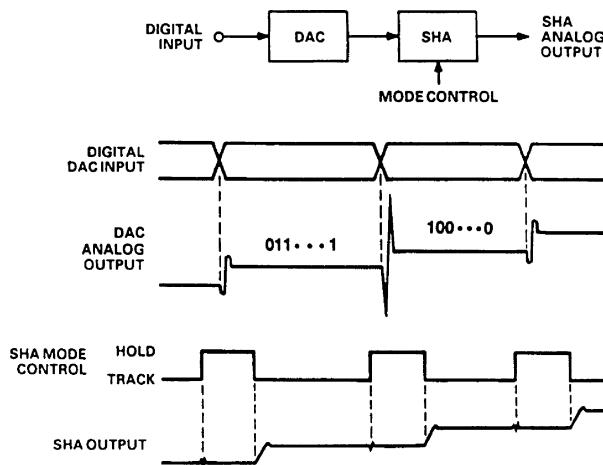

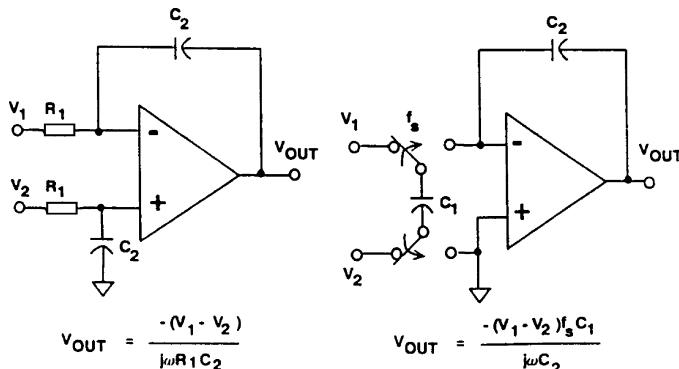

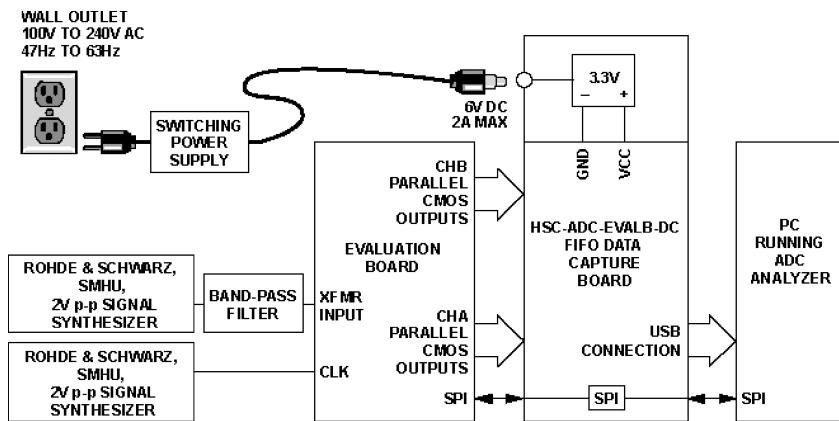

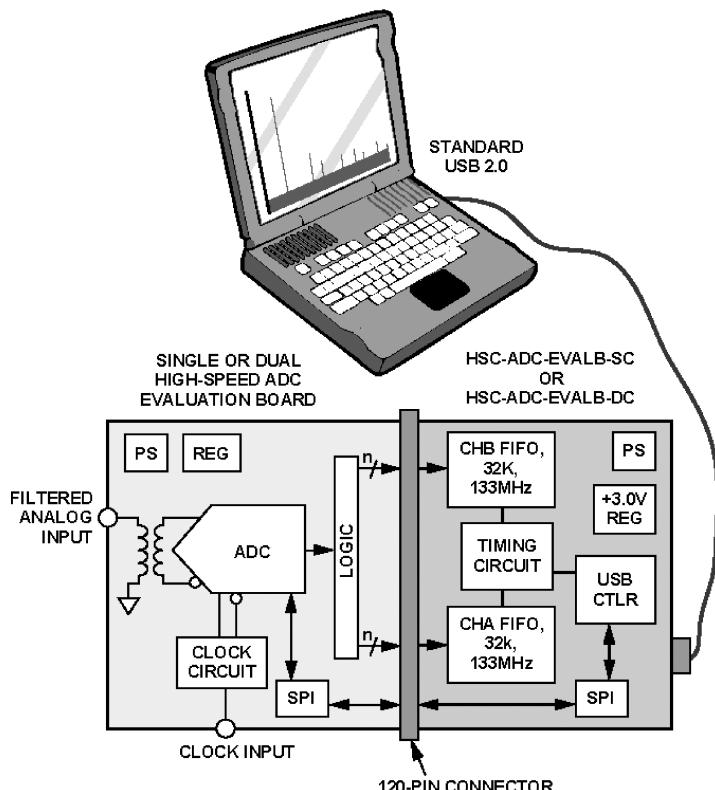

多年来,为了满足在通信、仪器仪表和消费市场的各种应用中新的带宽需求,模数转换器(ADC)的采样速率稳步提升。伴随在信号链前端对信号进行数字转换从而利用数字信号处理技术的需求,推动了高速 ADC 内核的开发,它们能够以 8 到 12 位分辨率在超过 100 MHz 到 200 MHz 时钟速率下进行数字转换。

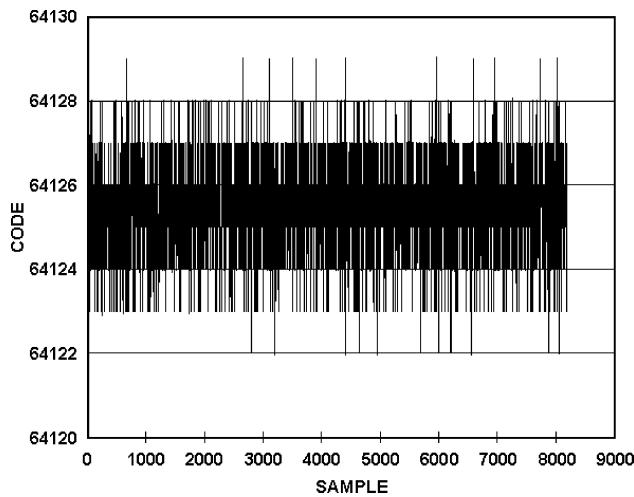

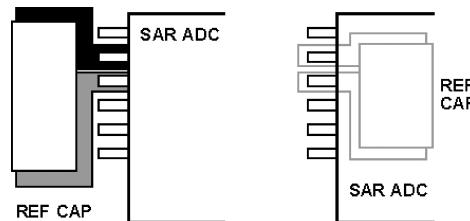

在独立的转换器中,ADC 需要能够驱动接收逻辑及其 PCB 走线所产生的电容。由于要驱动负载,电流开关瞬变会耦合到 ADC 的模拟前端电路,对性能造成负面影响。将这种影响降到最低的一种方法是复用两个输出端口,以时钟速率的一半速率来提供输出数据,这降低了信号边沿的速率,增加了开关瞬间的建立时间。AD9054A、AD9884、AD9410 和 AD9430 是最新的例子。

在 ADC 应用中,提供高速数据输出同时将性能限制降到最低的一种新方法是使用 LVDS(低电压差分信号传输)。ADI 正在将 LVDS 输出能力加到一个新的 170 MSPS、12 位 ADC 中——AD9430——并将会把 LVDS 引入到以后的高速 ADC 和 DAC 中。

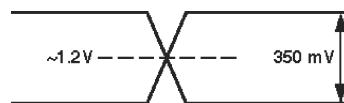

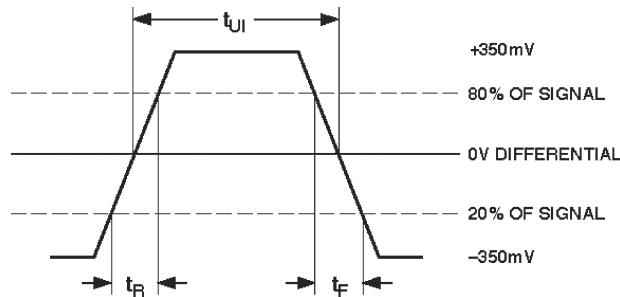

正如其名字所表述的,LVDS 是一种低电压差分信号传输方案。关键词是低电压( $\sim 350$  mV,见图 1)和差分。标准机构已经制定了规范,这些将稍后在这篇笔记中讨论。低电压信号摆幅具有更短开关时间的固有优势,这也降低了对 EMI 的考虑(相邻的差分走线会抵消相互之间的 EMI)。

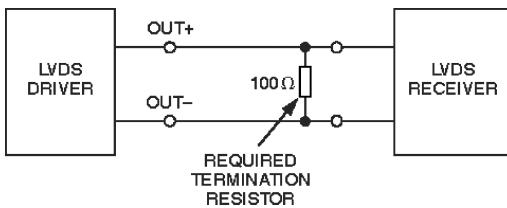

图 1 LVDS 输出电平

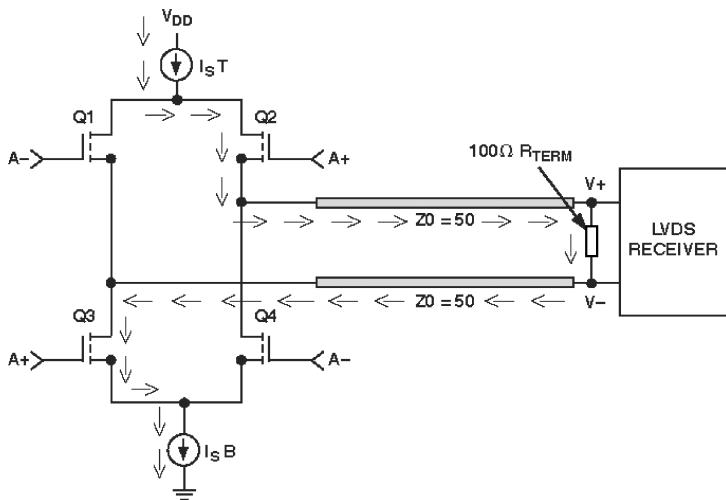

差分信号也有众所周知的共模抑制的优点。耦合到信号上的噪声往往在两个信号路径上都存在,这个噪声会被精心设计的差分接受器消除。LVDS 输出是电流输出级,在接收端需要  $100\ \Omega$  的端接电阻(见图 2),这与不需要端接的 CMOS 输出不同。电流输出导致输出供电电源上有固定直流负载电流,要避免供电电源的尖峰电流耦合到敏感的模拟前端。

图 2 LVDS 远端端接

## 标 准

有两个标准定义了 LVDS。一个是 ANSI/TIA/EIA - 644，其标题是《低电压差分信号(LVDS)接口电路的电气特性》。另外一个是 IEEE 标准 1596. 3，其标题是《可扩展一致性接口(SCI)的低电压差分信号(LVDS)IEEE 标准》。下面简单总结一下这两个标准。

### ANSI/TIA/EIA-644

ANSI/TIA/EIA 标准是在电信工业委员会(TIA)的 TR-30.2 小组委员会下开发的，它只包含 LVDS 的通用电气规范。它的目的是为点到点连接的数据通信设备之间建立一个通用高速接口标准。最大数据传输速率是 655 Mbps。TIA 小组委员会希望其他标准体系在发射器和接收器之间更完整的接口规范中引用 ANSI/TIA/EIA-644。

### IEEE 标准 1596. 3

IEEE 标准 1596. 3 是作为 1992 SCI 协议(IEEE 标准 1596 - 1992)的扩展开发的。原来的 SCI 协议适用于高端计算机中的高速包传输，使用 ECL 电平。然而，对于低端和功耗敏感的应用，需要一个新的标准。选用 LVDS 信号是因为电压摆幅比 ECL 输出小，在功耗敏感的设计中允许使用更低的供电电源。

### AD9430 的 LVDS 特性

如上所述，AD9430 是一系列高速模数转换器中第一个有 LVDS 输出选项的产品(同时也

# 第一部分 ADC 产品的应用

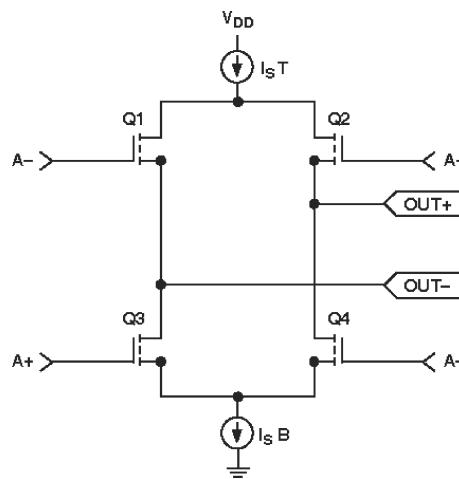

能提供 CMOS 输出)。它是一款 12 位、170 MSPS ADC, 针对宽带载波系统进行了优化, 具有卓越的动态性能。图 3 是 AD9430 LVDS 输出的简化等效电路。

图 3 LVDS 数据输出

50

图 3 中差分输出由 OUT+ 和 OUT- 表示, OUT+ 是正极或真数据输出, OUT- 为差分信号的补充数据输出。电路原理如下所述(见图 4)。片内电流源( $I_{sT}$ )由  $V_{DD}$  产生并流经 Q2。在这个例子中,发送的是逻辑 1( $V+ > V-$ )。 $100 \Omega$  接收端电阻为返回驱动器的电流提供了路径,电流通过 Q3 到更低的电流吸入端( $I_{sB}$ )再到地。额定的源/吸电流设置为大约 3.5 mA,对于  $100 \Omega$  外部端接电阻产生 350 mV 的摆幅。

假定有约 1.2 V 的输出共模电压(共模控制电路没有显示),输出电阻可以视为两个串联的  $50 \Omega$  电阻,它们的中心抽头的电压为 1.2 V。这与典型 PCB 走线的  $50 \Omega$  特性阻抗( $Z_0$ )相匹配并将反射降到最低。

AD9430 的 LVDS 输出与 ANSI/TIA/EIA-644 规范更为一致。表 1 对比了 ANSI/TIA/EIA-644 和 AD9430-170 的规格。

表 1 ANSI/TIA/EIA-644 和 AD9430 规格小结

| 规 格                                           | ANSI/TIA/EIA-644                                                       |         | AD9430-170            |

|-----------------------------------------------|------------------------------------------------------------------------|---------|-----------------------|

|                                               | 最 小 值                                                                  | 最 大 值   | 典 型 值                 |

| 输出电流                                          | 2.47 mA                                                                | 4.54 mA | 取决于 RSET(额定值为 3.5 mA) |

| 差分输出电压幅度                                      | 247 mV                                                                 | 454 mV  | 350 mV                |

| 输出失调电压(共模)                                    | 1.125 V                                                                | 1.375 V | 1.2 V                 |

| 转换时间上升时间 ( $t_R$ ) 和下降时间 ( $t_F$ ); 20% 至 80% | $\leq .3 \times t_{R/F} = .3 \times 5.88 \text{ ns} = 1.76 \text{ ns}$ |         | 0.5 ns                |

图 4 LVDS 输出电流

## 输出电流

COMS 是典型的电压输出,不同于 CMOS,LVDS 是电流输出型。AD9430 的输出电流根据一个电阻值来设置,其典型值为  $3.7\text{ k}\Omega$ 。这个  $3.7\text{ k}\Omega$  电阻设置输出电流为  $3.5\text{ mA}$ 。注意, $3.5\text{ mA}$  的额定输出电流( $I_s$ )在 AD9430 中是可调的,方便系统设计的灵活性。详情请参见 AD9430 数据手册。

## 差分输出电压与失调电压

ANSI 规范定义差分输出电压摆幅在  $247\text{ mV}$  和  $454\text{ mV}$  之间。假定 ADC 的输出电流设为  $3.5\text{ mA}$ ,接收端输入阻抗为  $100\Omega$ ,那么额定差分输出电压为  $350\text{ mV}$ 。

AD9430 的输出驱动器设计的额定共模电压为  $1.2\text{ V}$ ,这在 ANSI 规范的范围之内。共模电压的范围在  $1.1\text{ V}$  到  $1.375\text{ V}$  之间,在驱动和接收的地之间的电压差最多为  $\pm 1\text{ V}$ 。为了达到最好的性能,在同一块 PCB 上,ADC 的输出和接收端输入之间应该非常的靠近,在这种应用中就不用担心地平面的电压差。

## 转换时间

在表 1 中,对于数据信号速率小于或等于 200 MHz 的信号,ANSI/TIA/EIA - 644 规范规定其转换时间要小于或等于  $0.3 \times t_{UI}$ 。 $t_{UI}$  的值定义为数据信号速率的倒数。以 AD9430 为例,其最大信号速率为 170 MHz,那么  $t_{UI}$  等于 5.88 ns。用规范定义的公式换算  $t_{UI}$  的 5.88 ns 为  $0.3 \times 5.88 \text{ ns} = 1.76 \text{ ns}$ 。因此,差分信号上升时间和下降时间的总和应该小于 1.76 ns。AD9430 的上升和下降时间的额定值为 0.5 ns。LVDS 差分输出电压的上升和下降时间的定义如图 5 所示。LVDS 上升和下降时间定义为信号在其最大幅度的 20% 到 80% 之间变化所用的时间,CMOS 输出通常定义的范围是 10% 到 90%。

图 5 时序图

## LVDS 的 PCB 设计考虑

高性能 ADC 的 LVDS 输出应该与数字逻辑使用的标准 LVDS 输出区别对待。在高速数字应用中标准 LVDS 能驱动 1 到 10 米(取决于数据速率),不建议让高性能 ADC 驱动这么长的距离。建议输出走线的长度要短一些(小于 2 英寸),尽量降低任何噪声从相邻电路耦合到输出上的几率,噪声可能会返回到模拟输入。

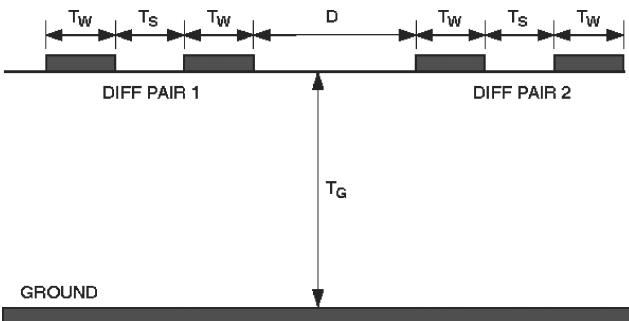

差分输出走线应该相互靠近,100  $\Omega$  端接电阻要靠近接收端来提高共模抑制能力。用户应该注意 PCB 走线长度,尽量减小延迟偏斜。

典型差分 PCB 微带线的截面如图 6 所示。

图 6 PCB 走线间距

## 布线指南

- 相对于走线长度的变化,保持  $T_w$ 、 $T_s$  和  $D$  为常量。

- 保持  $T_s \sim < 2 T_w$ 。

- 尽可能避免使用过孔。

- 保持  $D > 2 T_s$ 。

- 尽可能避免 90 °C 的拐弯。

- 控制  $T_w$  和  $T_g$ ,使阻抗约为  $50 \Omega$ 。

对于这些快速边沿( $< 0.5$  ns)速率的信号,电源的去耦是非常重要的。每一个电源和地引脚都要放置低电感的表面贴装电容,尽可能靠近 ADC 放置。不建议将去耦电容放在 PCB 的另外一面,因为过孔的电感会降低去耦的作用。由于邻近效应,差分  $Z_0$  会比每根导线的单端  $Z_0$  略低一些,每条线的  $Z_0$  应该设计得比  $50 \Omega$  高一些。可以对关键应用进行仿真来验证阻抗是否匹配。短期来看,这不是很关键。

## 其他的考虑

LVDS 也具有降低 EMI 的优点。相反方向的电流产生的 EMI 可以相互抵消(边沿速率相匹配时)。走线长度、偏斜和不连续将会降低这一优点,应该尽量避免。

在相近的数据速率下,相对于解复用的 CMOS 解决方案,LVDS 的时序约束更为简单。解复用的数据总线需要一个同步信号,LVDS 不需要这个信号。在解复用的 CMOS 总线中,需要一个速率为 ADC 采样速率一半的时钟,这增加了成本和复杂度。LVDS 不需要这些。通

## 第一部分 ADC 产品的应用

常, LVDS 更具有兼容性, 可以为客户提供更简单、干净的设计。

## 小 结

在转换器的应用中, LVDS 在高速信号转换中的优点可以为性能和整个系统带来好处。在 ADI 的众多 ADC 和 TxDAC 产品中, 这一技术响应了日益增长的高速转换器性能需求。

## 参考文献

- [1] ANSI/TIA/EIA-644, Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits, March 1996.

- [2] IEEE Std 1596.3-1996, IEEE Standard for Low-Voltage Differential Signals (LVDS) for Scalable Coherent Interface (SCI), March 1996.

# AN - 609 应用笔记 $\Sigma$ - $\Delta$ ADC 上的斩波

作者:Adrian Sherry

## 简介

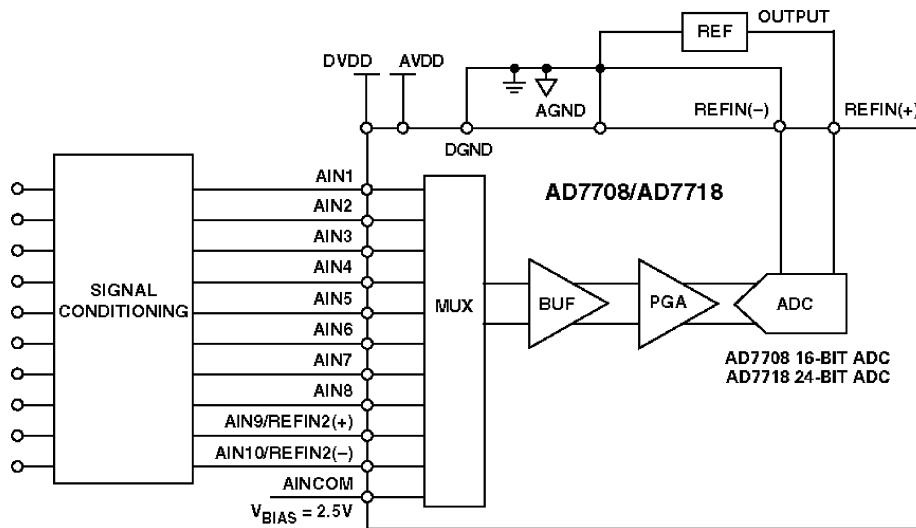

斩波是一项用于消除失调电压和其他低频误差的技术。本应用笔记简要介绍在 AD7708/AD7718、AD7709、AD7719 和 AD7782/AD7783 高分辨率  $\Sigma$ - $\Delta$  ADC 上是如何实现斩波的，及其带来的好处。

## 失调误差

在信号处理链路中的很多地方可能会有失调电压误差，例如，当两种不同金属连接时会产生与温度相关的热电偶电压。在集成电路例如 ADC 中，有许多内部失调误差源，例如，放大器输入器件之间的不匹配，采样开关关闭时采样电容上的电荷注入，或者 EMI 辐射的干扰等。如果这些不良失调随温度变化就会带来麻烦，因为一次校准不足以消除各种温度和电源条件下的失调误差。

## 斩 波

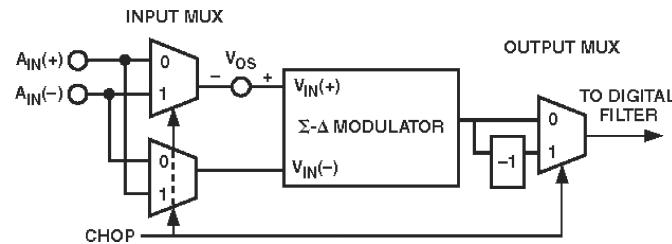

$\Sigma$ - $\Delta$  调制器中的各种放大器带来的失调可以通过本地斩波或自稳零放大器来清除。然而，其他类型的失调误差不能通过这些方法来消除。解决方案是对 ADC 内部的整个模拟信号链路进行斩波，这可以消除任何失调和低频误差，获得极低的失调误差和漂移。此方案如图 1 所示。

图 1 斩波

调制器的差分输入在输入多路复用器上被交替反相(或斩波),每个斩波相位都会进行ADC转换。调制器斩波在传递给数字滤波器前在输出多路复用器内被翻转。

如果我们把 $\Sigma\Delta$ 调制器的失调建模为叠加到输入信号的一项 $V_{OS}$ ,那么当斩波=0时的输出是:

$$(A_{IN}(+)-A_{IN}(-))+V_{OS}$$

当斩波=1的输出是:

$$-[(A_{IN}(-)-A_{IN}(+))+V_{OS}]$$

在数字滤波器中将这两个结果求平均值以后消除了误差电压,得到:

$$(A_{IN}(+)-A_{IN}(-))$$

这与没有任何失调项的差分输入电压相等。

## 结果 / 校准

这一结果几乎消除了ADC内部产生的任何失调误差,并且,更重要的是将任何随温度变化的失调漂移降到最低。这些ADC漂移的典型值是 $\pm 10 \text{ nV}/^\circ\text{C}$ 。实际上,这几乎是无法测量的。从输入多路复用器到调制器输出的整个模拟电路是经过斩波的。因此,不需要ADC失调校准。ADC失调误差典型值是 $\pm 3 \mu\text{V}$ 。这是插入PCB插座的器件在0V输入的时候测得的,由于不同的触点(PCB走线、焊锡、引线框、键合线和芯片金属化等)使用不同的金属,它包含了热电偶误差。

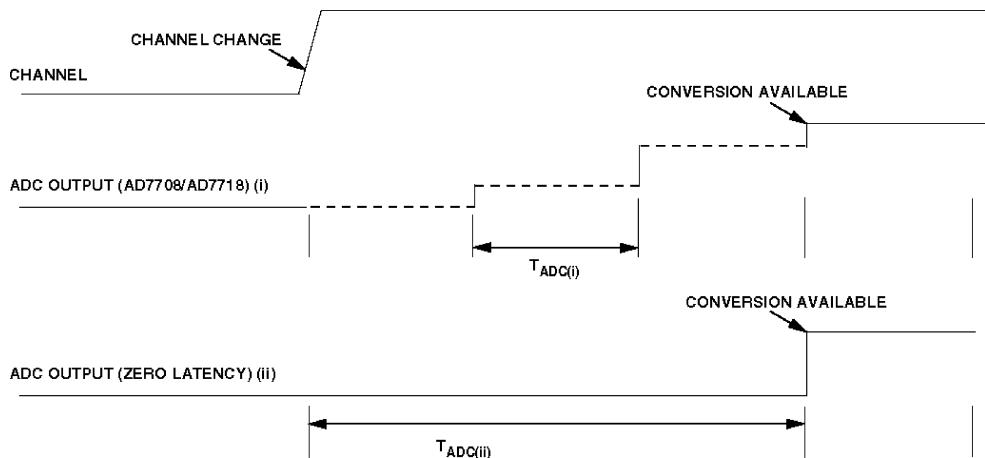

## 理解阶跃响应

由于ADC需要进行斩波=0和斩波=1的转换,ADC的第一个输出占用两个转换周期( $2 \times T_{ADC}$ ),因此第一个输出需要两个转换周期的建立时间,后续的输出发生在每个转换周期

( $T_{ADC}$ )。

在通道改变、PGA 增益改变或者 ADC 模式改变后会出现这样的两个转换周期的延迟。例如,电源掉电后,没有中间/无效输出产生——通道变化后的第一个输出是在新通道电压 100% 建立后。

如果 ADC 外部的模拟输入发生一个阶跃变化,例如,一个传感器的输出突然变化或者一个外部多路复用器进行开关,ADC 不会自动“知道”有改变发生,它会根据新输入和旧输入的加权平均来产生输出,除非当外部多路复用器开关后,ADC 中断当前的工作,直接开始新的转换,这时,重新启动 ADC 后它会经过  $2 \times T_{ADC}$  的延迟产生输出。

在输入信号发生变化后 ADC 产生一个中间值的情况很常见。这与模拟滤波器的特性相同。如果模拟低通滤波器的输入信号发生阶跃变化,在一段时间内,它的输出会反映旧模拟输入与新模拟输入结合后的值。只有在足够多个时间常数之后,它的输出才会完全反映新输入的值。

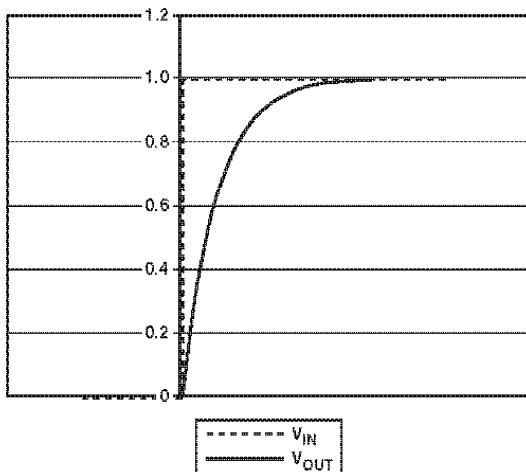

图 2 模拟滤波器的阶跃响应

这些  $\Sigma-\Delta$  ADC 包含一个给定的 3 dB 频率和建立时间的低通 FIR 滤波器,因此,虽然有有限脉冲/阶跃响应,但它的响应在离散时间上类似。

这些 ADC 唯一不定的特性就是在模拟输入发生改变后会有两个中间输出。这是斩波造成的结果。如上所述,具有斩波的 ADC 的输出是当前 ADC 转换和之前一个转换的平均值。如果模拟输入在 ADC 转换周期中发生改变,那么当前 ADC 转换是旧模拟输入和新模拟输入的综合反映,平均后的结果是一个中间值。下一个(非平均)转换会真正反映新的输入。然而,当与之前的转换平均时,它还不能产生最终的值,所以它产生第二个不稳定的输出。只有第三个输出才完全稳定(见图 3(1))。

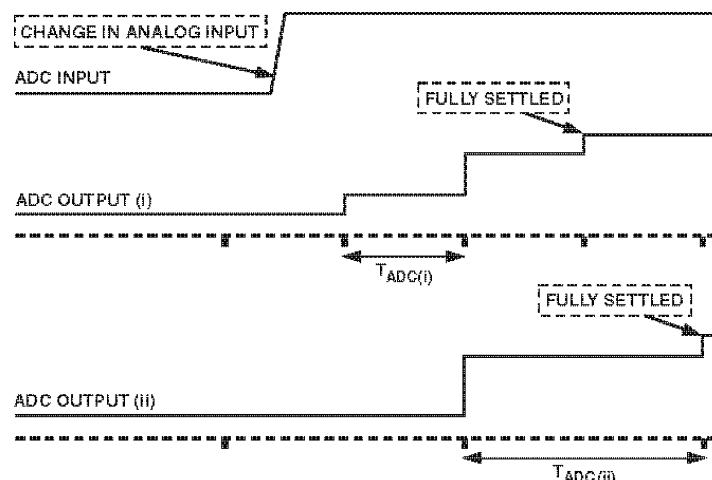

## 第一部分 ADC 产品的应用

一些其他的  $\Sigma\Delta$  ADC 将 ADC 转换输出限制在每  $2 \times T_{ADC}$  一次, 即最大吞吐量的一半。在这种情况下, 由于较慢的 ADC 转换速率, 模拟输入变化后最多只有一个中间结果(见图 3 (ii))。这种情况习惯以“无延迟”表示, 但实际上这样的 ADC 与 ADI 公司的 ADC 相比对于阶跃输入具有更大的延迟。

图 3 具有(i)和没有(ii)额外中间结果的 ADC 延迟的对比

那种方案是最好的? 在大多数应用中, 尽可能快地得到信息的需求是最重要的。例如, 在安全至关重要的控制系统中, 您得到一个反应即将过热的指示越快, 采取纠正的措施就越快。

在 ADC 有更快的输出时, 模拟输入发生变化后会比只有每  $2 \times T_{ADC}$  提供一次输出的 ADC 更早得到指示。这会减少 ADC 的有效延迟。

如果阶跃变化是由于外部多路复用器的变化引起的, 通常情况下最好同时中断 ADC 转换并在  $2 \times T_{ADC}$  之后获得稳定的结果。但是, 如果输入变化是由于传感器输出的突然改变所引起的, 尽快得到发生变化的指示更为重要, 因为这个变化可能很重要。

## 频率响应

斩波也会影响频率响应, 但是主要是在好的方面。用 2 平均的操作使陷波频率为  $f_{OUT}/2$  的奇数倍, 这可以提高 50 Hz/60 Hz 的抑制。请参考随附的有关 50 Hz/60 Hz 抑制的应用笔记。

## 小 结

斩波的主要目的是消除失调误差。在 ADI 公司的这些 ADC 上，斩波可以很好的消除失调。一次输出需要两次 ADC 转换可能不是很好，然而，在 ADC 中已经实现的方法在检测输入信号变化的时候会在响应时间上有些损失。关于  $\Sigma-\Delta$  ADC 的延迟响应有一些使人误解的信息，因此这篇应用笔记试图展示这一系列 ADC 能够提供的更理想的解决方案。

# AN - 614 应用笔记 在低功耗应用中使用 AD7782

作者 : Mary McCarthy

## 简介

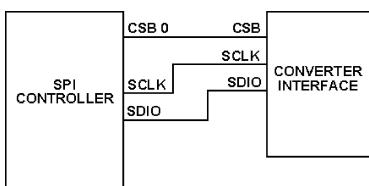

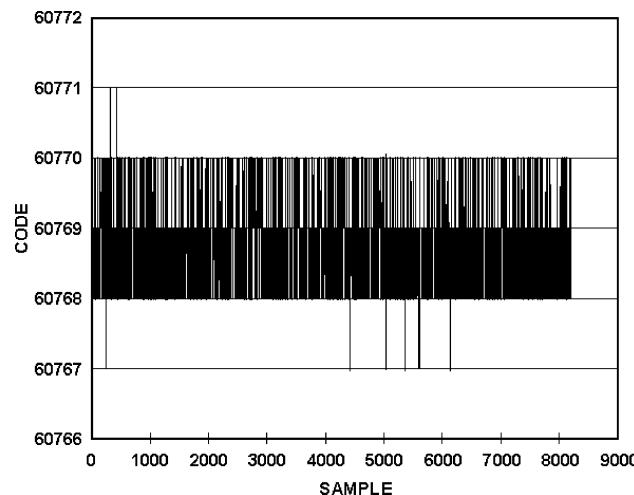

本应用笔记介绍在便携式或低功耗应用中如何使用 AD7782。该器件是一款引脚可配置的 24 位精度只读 ADC，具有 20 Hz 输出数据速率。它含有两个差分模拟输入通道，适用的模拟输入范围为  $\pm 160 \text{ mV}$  或  $\pm 2.56 \text{ V}$ 。输入信号范围和输入通道选择通过外部引脚进行配置。在两次转换之间，用户可以利用 AD7782 上的串行数据接口关断器件，以降低器件的平均功耗。

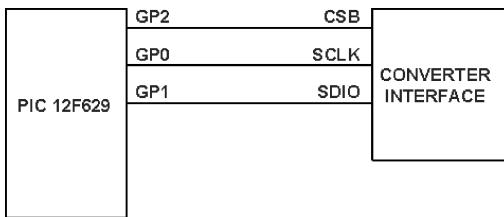

## 串行接口

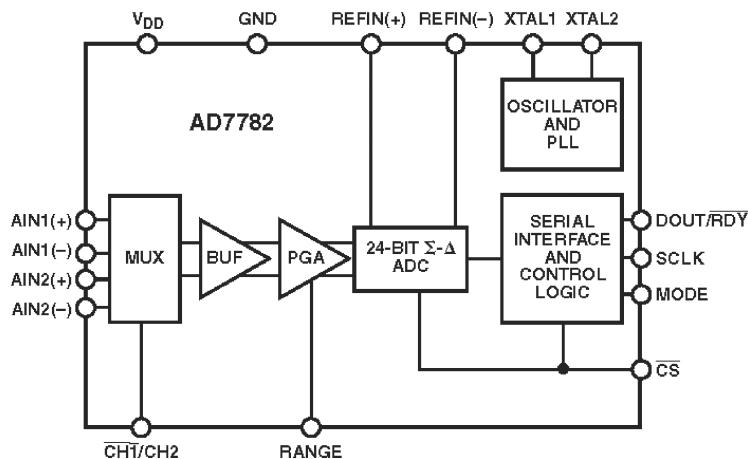

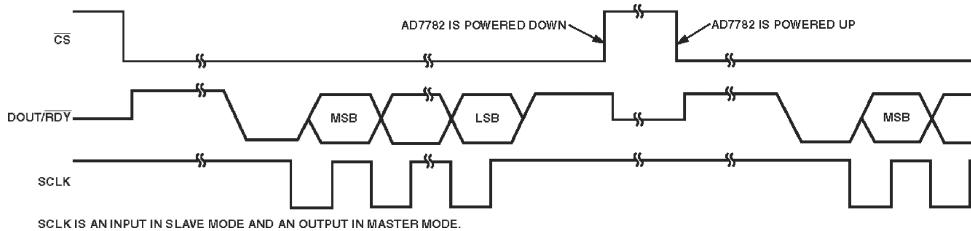

如图 1 所示，AD7782 具有一个三线式串行接口：DOUT/RDY、SCLK 和 CS。MODE 引脚用于设置器件的工作模式：从模式（SCLK 由外部提供）或主模式（AD7782 提供 SCLK）。器件上电后，将以 19.79 Hz 的更新速率连续转换。CS 引脚既可用作关断引脚，也可用作芯片选择引脚。当 CS 为高电平时，连续 ADC 转换中断，DOUT/RDY 变成三态，AD7782 进入待机模式，并且输出移位寄存器中的任何转换结果都会丢失。在主模式下，SCLK 也会呈三态。在节电模式下，AD7782 的片上晶体振荡器仍然保持工作状态。当 CS 变为低电平时，AD7782 的片上锁相环（PLL）建立锁定，然后器件开始转换选定的通道。

图 1 AD7782 功能框图

图 2 为 AD1782 时序图。

图 2 AD7782 时序图

## 功 耗

AD7782 上电后,3 V 时的典型功耗为 1.3 mA,5 V 时的典型功耗为 1.5 mA。在省电模式下,该器件 3 V 时的典型功耗为 6  $\mu$ A,5 V 时的典型功耗为 20  $\mu$ A。在两次转换之间使 AD7782 处于省电模式可以优化器件的功耗。例如,如果 AD7782 每秒执行一次转换,则首先可以使该器件上电以执行转换,然后利用 CS 将其关断,直到要求执行下一次转换时为止。

从图 2 可以看出,将 CS 拉低,AD7782 上电。上电之后,ADC 需要约为 1 ms 的建立时间。然后,器件开始执行转换。该  $\Sigma-\Delta$  ADC 采用斩波技术,因而在使器件离开省电模式之后,为产

## 第一部分 ADC 产品的应用

生正确的转换结果,需要使用两个转换周期。RDY仍将保持高电平,直到获得有效的转换结果为止。假设更新速率为 19.79 Hz,则转换周期为 50.5 ms,因此 AD7782 必须在  $(2 \times 50.5) + 1 = 102$  ms 内保持上电状态。转换结果被读取后,该器件便可关断。

如果某一应用要求每秒执行一次转换,则一秒钟内该器件处于上电模式的时间为 102 ms,处于关断模式的时间为  $(1000 - 102) = 898$  ms。假设采用 3 V 电源,则平均功耗等于  $(0.898 \times 6) + (0.102 \times 1300) = 138 \mu\text{A}$ 。

如果采用 5 V 电源,同样是每秒执行一次转换,则平均功耗等于  $(0.898 \times 20) + (0.102 \times 1500) = 171 \mu\text{A}$ 。

在某些应用中,AD7782 用于执行监控功能,每一小时执行一次转换。这种情况下,采用 3 V 电源时的平均功耗为  $(0.99997167 \times 6) + (0.00002833 \times 1300) = 6.04 \mu\text{A}$ ;

采用 5 V 电源时的平均功耗为  $(0.99997167 \times 20) + (0.00002833 \times 1500) = 20.04 \mu\text{A}$ 。

图 3 显示了平均功耗与转换速率之间的关系图,转换速率为 ADC 执行单次转换的周期,AD7782 在完成单次转换后被置于关断模式。从图中可以看出,当转换之间的时间间隔为 15 秒或更大时,平均功耗接近省电模式的额定值。

图 3 功耗与转换速率的关系曲线

## 小结

AD7782 ADC 上电后便会连续执行转换。但是,许多应用所需的更新速率可能低得多,因此许多转换结果不会被读取。对于这些应用,在两次转换之间关断 AD7782 将能降低功耗。由于 CS 同时充当芯片选择引脚和关断引脚,而无需微控制器提供额外数字引脚,因此在两次转换之间关断 ADC 会增加额外开销。

## AN - 639 应用笔记

### 常见问题解答: Analog Devices 电能计量(ADE)产品

作者: Rachel Kaplan

## 一般问题

### 如何索取预发布产品及评估板的样片?

请通过当地的授权代理商或销售代表索取预发布产品样片(带原始数据手册的产品)。有关我们的销售及经销商目录,请访问: [www.analog.com/salesdir/continent.asp](http://www.analog.com/salesdir/continent.asp)。请务必告诉他们产品已预发布。原始数据手册(若有)的“订购指南”部分会含有评估板产品型号。

## 计 量

### 为什么电子式电能表(固态电能表)优于机电式电能表或模拟式电能表?

电子式电能表能在较宽的电流动态范围内取得很高的精度,可以承受较高电流,功耗低、可靠、鲁棒性(稳定性不受时间和温度影响),而且不含易磨损的配件和易在直流电流下饱和的磁体。它们不需要精密机械,且温度容差变化不大。

电子式电能表更容易实现新的功能,如自动抄表(AMR)、多费率计价、防窃电、预付式电度表、限电、停电检测、功率因数检测等。电子式电能表在设计上更为灵活,可轻松进行重装配和升级(如软件升级)。校准简单、稳定,无需进行硬件调整,生产、运输和安装也更简单。电子式电能表为供电公司提供了更广泛的产品选择——而且激烈的竞争环境有助于降低这一解决方案的成本。

### 固态电能表的使用寿命如何?

我们通过加速寿命测试对 ADE IC 进行了测试。结果表明, ADE 的精度和可靠性可保持 60 年。这种电能表的使用寿命可能受电能表设计及元器件选择的影响。AN - 559 及 AN - 563 两篇应用笔记中描述的参考设计提供了一种有效的电能表解决方案, 是固态电能表设计的很好的参考。

### 有功功率、无功功率及视在功率三者之间有何区别?

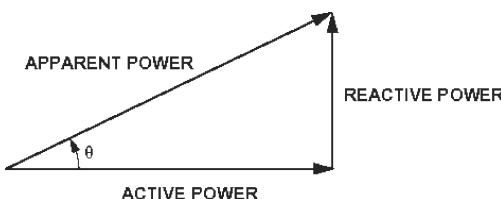

有功功率的计量单位是千瓦时, 无功功率和视在功率的计量单位分别是乏(VAR)时和伏安(VA)时。图 1 显示了有功功率、无功功率及视在功率三者间的关系。图中所示关系在纯正弦波下成立。存在谐波时, 这种关系将不成立。另见常见问题解答: 什么是功率因数?

图 1 功率三角关系

关系如下:

$$\text{有功功率} = VI \cos \theta$$

$$\text{无功功率} = VI \sin \theta$$

$$\text{视在功率} = VI$$

$$\text{功率因数} = \cos \theta$$

### 什么是功率因数?

$\cos \theta$  被称为功率因数, 其中,  $\theta$  为有功功率矢量与视在功率矢量之间的角度(无谐波)。可见, 功率因数为实际功率与视在功率之比。参见图 1。有的供电公司会对低功率因数罚款。造成低功率因数的常见原因为感应电机和变压器。当电流发生位移或与电压的相移角度达  $\theta$  时, 线路中会出现感抗。

## 电流传感器

### ADE IC 应与哪些电流传感器配合使用?

ADI 公司目前未与任何电流传感器制造商合作, 也不作相关推荐。电能表制造商和其他

客户必须自行评估和选择电流传感器。如要利用 ADE77xx 的全动态范围性能，则须使用能在这一

### 范围内实现所需精度的电流传感器。

### 不同电流传感器技术有哪些优势与不足？

| 传感器            | 优势                                  | 不足                              |

|----------------|-------------------------------------|---------------------------------|

| 低电阻分流器         | 极低的成本、良好的线性度                        | 较差的高电流性能、直流偏置、寄生电感              |

| 电流互感器          | 高电流性能、低功耗                           | 直流、相移导致的迟滞/饱和                   |

| 霍尔效应传感器        | 高电流性能、宽动态范围                         | 迟滞/饱和、高成本、温度漂移                  |

| 罗果夫斯基线圈(空芯 CT) | 低成本、无饱和限制、低功耗、不受直流偏置影响、宽动态范围、极低温度范围 | 输出为电压信号导数——要求模拟(或数字)积分器。EMI 灵敏度 |

ADE7753 和 ADE7759 内置数字积分器，与罗果夫斯基线圈很容易接口。各种情况下，均可关闭积分器，以与电流互感器(CT)或分流器接口。

### 选择分流器时有哪些考虑因素？

选择分流器时主要考虑以下因素：

功耗要求：据 IEC 61036，每个通道的功耗不能超过 2 W，更大的分流器功耗会消耗更多功率。

热管理因素：对于大(高电阻)分流器，当电流较大时，温度将大幅升高。

分流器品质：分流器的自热特性可能提高其电阻。结果可能导致输出信号发生变化，并由此影响到电能表的准确性。

窃电因素：分流器电阻应尽量接近导线，以减少通过外线分流产生的影响。

分流器应在电流工作范围内，为 IC 提供合理的信号水平。

### 选择电流互感器(CT)时有哪些考虑因素？

务必谨慎选择，确保特定电流互感器的动态电流感应范围足够大，能适应具体应用之需。在大直流或高电流下，电流互感器可能发生饱和，设计人员应选择额定值符合其需要的电流互感器。电流互感器有可能产生相移，选择时应考虑设计人员对此误差进行补偿的能力。

### 如何补偿电流传感器的相移(或通道间的相位不匹配)问题？

对于 ADE7751、ADE7755(单相)或 ADE7752(3 相)等产品，对相位不匹配进行补偿的唯一方式是硬件。可以通过调节 RC 滤波器用于输入通道抗混叠)的转折频率，产生相移以补

# 第一部分 ADC 产品的应用

偿电流互感器相位误差,由此纠正线路频率下的相位不匹配。应用笔记 AN-563 较为详细地讨论了调节相位不匹配的方法。

对于 ADE7753、ADE7756、ADE7759(单相)、ADE7754(3 相)等产品,您可以使用内部 PHCAL 寄存器来调节相位超前/滞后。调节相位不匹配只是简单的寄存器写操作过程。有关详情,请参阅相应产品的数据手册。如果补偿范围超出了 PHCAL 寄存器的范围,则可以结合使用硬件和软件相位调节方式。例如,您可以利用硬件法大致补偿默认情况下的相位不匹配问题,而通过 PHCAL 寄存器进行生产微调。

## 如何计算与电流互感器搭配的负载电阻?

负载电阻取决于最大电流( $I_{MAX}$ )、ADC 输入电平( $y$ )以及所用电流互感器中的匝数( $CTR_N$ )。在最大电流下,电流通道的输入信号应为满量程输入的一半<sup>\*</sup>,以获得裕量。

$$y = \frac{\text{Full Scale}}{2} = \frac{500 \text{ mV}_{\text{峰值}}}{2} = \frac{353.55 \text{ mV}_{\text{rms}}}{2} = 176.8 \text{ mV}_{\text{rms}}$$

应用以下等式:

$$\frac{I_{MAX}}{CTR_N} = x \quad \frac{y}{x} = 2R_B$$

求出  $R_B$  的值。例如,若  $I_{MAX}$  为 113.1 A 均方根值,则  $R_B = 4.5 \Omega$ 。

## 罗果夫斯基线圈的工作原理是什么?

罗果夫斯基线圈的基本工作原理是通过互感测量初级电流。

当电流通过导体时,导体周围会形成一个磁场。磁场强度与电流成正比。磁场的变化会在线圈中产生电动势(EMF)。EMF 是一种电压信号,与线圈中的磁场变化成比例。可见,线圈的输出电压与电流的时间微分( $di/dt$ )成比例。

罗果夫斯基线圈通常采用空芯设计,因而从理论上来说,不存在迟滞、饱和、非线性等问题。由于罗果夫斯基线圈依赖于磁场测量,这种性质使这类电流传感器比电流互感器更易受外部磁场的干扰。

有关详情及公式,请访问 ADI 网站上的技术文章“Current Sensing for Energy Metering”(面向电能计量的电流检测)。

## 从哪里可以买到罗果夫斯基线圈?

目前,ADE 产品开发小组正在寻找合适的罗果夫斯基线圈制造商。我们将向感兴趣的客户通知结果。如果您希望接收该通知,请将您的联系资料和请求发送至 energy.meter.an-

\* 满量程为 660 mV<sub>峰值</sub>、500 mV<sub>峰值</sub> 和 1 V<sub>峰值</sub>,视产品而定。有关规格详情,请参阅产品数据手册。

log.com。采用其专有传感器及 ADE 产品的电能表制造商对 ADI 数字积分器和传感器接口都很满意。

### 如何在单相、3 线配置中使用一个电流互感器或罗果夫斯基线圈(ANSI 2S)?

在美国(及部分其他地区),居民用电采用单相、3 线配置输送。L1 和 L2 两条线缆中的电压信号相互 180°反相,两个信号的参考是同样的。理论上,要求使用两个电能计量 IC 和两个传感器。然而,借助一种逼近法(通常极其接近真实情况),只需一个计量 IC 和一个电流传感器就够了。此时的前提假设是,两条相线的振幅相等(二者 180°反相)。只需用 L1 和 L2 间的电压差乘以 L1 中电流及 L2 的“反相值”之和即可。

数学公式为:

$$\begin{aligned} \text{L1 瞬时功率} &= V1N \times \text{L1 电流} \\ \text{L2 瞬时功率} &= V2N \times \text{L2 电流} \\ \text{总瞬时功率} &= \text{L1 功率} + \text{L2 功率} \\ &= V1N \times \text{L1 电流} + V2N \times \text{L2 电流} \end{aligned}$$

假设  $V1N = V2N = (V1N - V2N)/2$ , 则

$$\begin{aligned} \text{总瞬时功率} &= V1N \text{ L1 电流} + V2N \text{ L2 电流} \\ &= V1N \times \text{L1 电流} - V1N \times \text{L2 电流} \\ &= ((V1N - V2N)/2) \times (\text{L1 电流} - \text{L2 电流}) \end{aligned}$$

整除 2 是为了在校准过程中进行补偿。

在 AN-564 应用笔记中,使用的是电流互感器以正确求出电流和。用一个电流互感器并使 L1 和 L2 反向流动,以产生两个电流之和,也可用两个电流互感器来监控单个相位电流,并以外部方式(将两个电流互感器并联)求和。用单个电流互感器求和时务必小心;必须能在两种相位下承受总电流。例如,如果各相线的最大容量为 100 A,则电流互感器的容量需要达到 200 A。

## 全部 ADE 产品

### ADE 产品符合哪些计量标准?

ADE IC 的性能符合 IEC 1036、IEC 61036、ANSI 及其他衍生规范的要求。请参阅各产品数据手册中的规格部分,了解有关详情及与其他计量规范的合规情况。

ADE IC 是否可以在 50 Hz 及 60 Hz 环境中使用?

是的。ADE IC 的频率性能(45~70 Hz)可在各数据手册“典型性能特性”部分找到。

是否必须使用建议的 CLKIN 频率?

ADI 基于建议的 CLKIN 频率进行了广泛的测试。标定 CLKIN 频率是产品规格及器件性能得以保证的唯一频率。更改 3.5 MHz(ADE7751、ADE7753、ADE7755、ADE7756、ADE7759)或 10MHz(ADE7752、ADE7754)的 CLKIN 频率将改变数据手册所给等式中的常数以及寄存器分辨率、CF、F1 和 F2 脉冲宽度。

ADE775x 可以使用 3.3 V 数字电源吗?

不可以,数字电源无法工作于 3.3 V 的电压下。

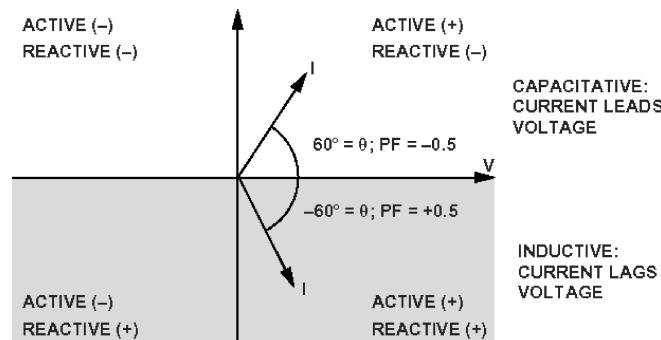

如何理解 ADE IC 中的无功功率或有功功率符号?

图 2 展示了电能寄存器符号的解读方法。

图 2 ADE IC 中的无功功率及有功功率

ADE 芯片测量的是功率还是电能?

ADE 电能计量产品的模拟输入通道采用 ADC, 可将交流电压和电流信号转换成数位流。然后在数字域对电压及电流位流进行乘法运算, 所得乘积为瞬时功率。在电能表内部, 该功率随时间累加。这就是电能。可见, ADE 芯片测量的是电能而非功率。需要时, 可利用波形采样寄存器读取位流, 从而在串行接口(SPI)器件(ADE7753、ADE7754、ADE7756 和 ADE7759)中求出瞬时功率。

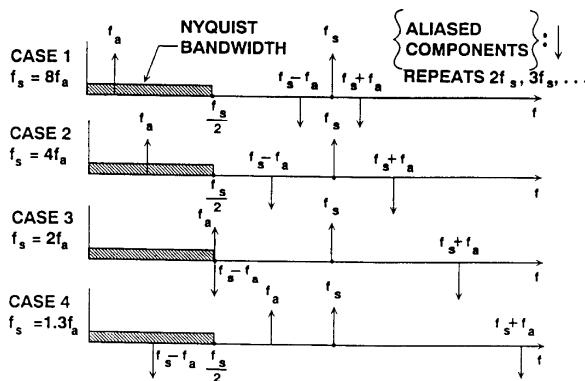

为什么要在输入通道中配置抗混叠滤波器?

ADE IC 输入端的 ADC 必须配置抗混叠滤波器以避免因 ADC 采样导致失真。ADE775x 系列

ADC 具有较高的采样速率(约 800 kHz)。如奈奎斯特理论所述,接近采样频率的镜像频率可能与采样频率(450 kHz)的一半左右混叠,从而与目标频带(50~60 Hz)重合,由此导致失真。简单的低通滤波器可以衰减高频率(近 900 kHz),不会与目标计量频带(低于 2 kHz)重合。

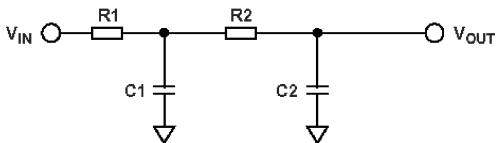

### 如何设计抗混叠滤波器?

本应用中,简单的 RC 低通滤波器足以满足对抗混叠滤波器的要求。AN - 559 应用笔记、ADE7755 参考设计文档解释了为 ADE77xx 产品设计简单的抗混叠滤波器的方法。

在关于两极串联 RC 滤波器(AN - 559,图 12)的公式  $H(s)=1/(S^2 \times R_2 \times C_2 + 3SRC + 1)$  中,3SRC 中的因子 3 是如何来的?

图 3 两个串联的 RC 滤波器

对于含有两个串联 RC 滤波器的滤波器网络,传函如下:

$$H(s)=1/((1+sR_1C_1)(1+sR_2C_2)+sR_1C_2)$$

其中,  $R_1=R_2$  且  $C_1=C_2$

两个串联滤波器的一种估算公式为  $H(s)=G(s) \times W(s)$ ,其中, $G(s)$  和  $W(s)$  表示各滤波器的传递函数。如果  $R_1=R_2$  且  $C_1=C_2$ ,估算结果的分母中就会包含  $2sRC$ 。

该估算忽略了精确等式中的“交越”项  $sR_1C_2$ 。可根据电路推算出传递函数,不进行估算,从而证明这一点。

AN - 559 解释了利用极点位置计算电阻及电容值以匹配相位和消除寄生并联电感的方法。

### 相位不匹配对电压和电流通道有何影响?

因电压与电流信号路径不匹配导致的有功功率测量误差百分比的近似值可通过以下公式计算:

$$\text{误差} \approx \text{不匹配(弧度)} \times \tan \theta \times 100\%$$

在该表达式中,  $\theta$  表示电压与电流间的相位角。显然,当功率因数为 0.5 时,0.1° 的相位不匹配将导致约 0.3% 的误差。可见,必须加倍小心,以确保内部信号路径在电压和电流相位上精确匹配。当功率因数较低时,即使是较小的相位不匹配也可能导致大误差。

### 如何校准 ADE 计量 IC?

对于 ADE7751、ADE7755(单相)或 ADE7752(3 相)等产品,校准通过硬件完成。这些产品需要在电压通道上配置电阻分压器网络。有关详情,请参阅相关应用笔记和产品数据手册。

对于 ADE7753、ADE7756、ADE7759(单相)或 ADE7754(3 相)等产品,校准则通过 SPI 接口写寄存器完成。有关详情,请参阅产品数据手册和应用笔记。

### 应以什么测试电流对电能表进行校准?

电能表一般以标定的基极电流( $I_B$ )进行校准。

该电流通常为最大电流( $I_{MAX}$ )的 10%。

### ADE775x DIP、SSOP 及 SOIC 几种封装在内部是否存在任何差异?

仅封装存在差异。器件性能不受封装方式影响。

ADE7755 和 ADE7751 上既有模拟地(AGND)也有数字地(DGND)。为什么在参考设计中,两个引脚都接到了模拟接地层上?

70 ADE7755 和 ADE7751 不会产生大量数字噪声。因此,可将整个 IC 接到平静的模拟接地层上,以减少来自其他源的噪声影响。此外,这种安排可以增大 PCB 上的接地层。这里的关键是将数字输出引脚(F1、F2、REVP 和 CF)接到数字接地层。

### 电流传感器应接到哪个接地层?

数字接地层。这样不但可以减少进入模拟接地层的电源线的噪声,而且可以在发生 ESD 事件时从 IC 分流电能。

### 晶体振荡器应接到哪个接地层?

数字接地层。

### 在设计电能表 PCB 上的接地层时,需要考虑哪些因素?

模拟接地层和数字接地层应相互物理隔离,且只能接一个点(星形接地配置)。最好用铁氧体磁珠连接两个接地层,以减小数字接地层进入模拟接地层的噪声。

### 对于电快速瞬变(EFT)突发脉冲测试,需要考虑哪些系统设计因素?

可参考以下实用技巧:

- 在电能表与线路的连接处使用铁氧体磁珠。**www.BDTIC.com/ADI**

- 在线路导线间使用金属氧化物压敏电阻(MOV)和分流电容。

- 尽可能增大与高压危险区域的物理距离,避免发生电火花。

对于电磁干扰(EFT)测试,需要考虑哪些系统设计因素?

可参考以下实用技巧:

- 接地层应尽可能大。

- 在 PCB 的模拟部分使用较短信号路径。

- 消除地环路。

- 使用短而紧实的双绞线。

- 考虑物理屏蔽。

## ADE775x:SPI 接口产品

ADE775x(ADE7753、ADE7754、ADE7756、ADE7759)能承受双向电能流吗?

是的,ADE775x(ADE7753、ADE7754、ADE7756、ADE7759)可以承受双向电能流。电能寄存器上会有相应标识。

ADE775x(ADE7753、ADE7754、ADE7756、ADE7759)能用于直流电能测量吗?

是的,在通道 1 中的 HPF 关闭时,ADE775x(ADE7753、ADE7754、ADE7756、ADE7759)可用于直流电能测量。但请注意,ADC 通道 1 和通道 2 中都有直流偏置,因此有必要进行直流校准以补偿该误差。可通过向 CH1OS、CH2OS 或 APOS 寄存器写入代码来补偿误差项 CH1\_OS1×CH2\_OS2。

哪些产品可以与罗果夫斯基线圈(空芯 CT、di/dt 传感器)配合使用?

ADE7753 和 ADE7759 为单相产品,可与 di/dt 传感器配合使用。所有情况下,使能该直接接口的积分器可被禁用(请参阅产品数据手册,了解寄存器配置图),以将电流互感器(或分流器)用作电流传感器。

在与 MCU 接口时,在 SPI 时序方面是否有任何特殊考虑?

在多字节数据传输过程中,字节间(产品数据手册中的  $t_7$  和  $t_{10}$ )至少须有 4  $\mu$ s 的间隔时间。其中包括通信寄存器写操作(启动 SPI 通信的命令字节),即 SCLK 的上升沿应发生在通信寄存器写操作的下降沿 4  $\mu$ s 之后。对于快速 MCU,传输时间可能会较快,从而违反以上时间要求。

哪些 ADE 产品会产生无功功率?

ADE7753。

ADE77xx VAR(无功功率)计算的工作原理是什么?

ADE 电能测量产品通过一个单极低通滤波器来计算 VAR, 其中, 频率相移常数为  $90^\circ$ , 衰减为  $20 \text{ dB}/10$  倍频程。低通滤波器的截止频率远低于基频, 因此, 在高于基频的任何频率下, 其相移均为  $90^\circ$ , 并使这些频率衰减  $20 \text{ dB}/10$  倍频程。这种解决方案受线路频率变化的影响。然而, 通过估算信号的线路周期, 就可以对线路频率增益衰减进行动态补偿。ADE 产品还有一个周期寄存器, 可供补偿使用(ADE7753)。有关各种 VAR 计算方法的全面说明和对比, 请参阅 ADI 网站上的技术文章“Measuring Reactive Power in Energy Meters”(测量电能表中的无功功率)。

要从 ADE775x 获得稳定的电能寄存器读数, 需要累加多少个线路周期?

虽然读数将在半个周期中稳定下来, 但问题在于精度。读数的精度为累加的 LSB 的  $1/n$ , 类似于 ADC 中的量化误差。

72

要获得有意义的电能读数, LINCYC 的最小数目是多少?

您可以调节半线路周期数, 在低电流精度和读出各相位所需时间之间作出权衡。

100 个半周期  $60 \text{ Hz} = 1.667 \text{ sec} \times 32 \text{ LSB/sec} = 53.333 = 53$ (舍入, 导致误差)。任何测量的误差均为  $\pm 0.5 \text{ LSB}$ 。

因此, 精度 = 1 LSB 误差 / 53 LSB = 1.875%。

因这种“量化”导致的误差在大电流下的影响较小(因为累加的 LSB 增加了)。可见, 最差情况发生在小电流时。

可以在 ADE77xx 中使用温度传感器来补偿基准电压漂移吗?

导致温度漂移的原因主要有两种: 内部电压基准和电流传感器自身发生漂移。即使内部电压基准漂移呈“平均”分布, 也不具可预测性, 不是单个器件性能的指标。除非温度漂移大到需要进行补偿的程度(通常并非如此), 不建议这样做。如果确有必要这样做, 则应在多个温度下进行校准。

如何处理不同的 3 相分布配置(3 线、4 线、 $\Delta$  和“Y”形)?

ADE7754 提供不同的电能计算模式, 应根据具体的服务配置选择相应的公式。有关 COMPMODE 寄存器的详情, 请参阅 ADE7754 数据手册。

**www.BDTIC.com/ADI**

### 我可以索取评估板(EVAL - ADE775xE)的驱动代码吗?

代码采用 LabVIEW 编写。如果没有 LabVIEW 软件,就无法查看。该软件随附的运行时引擎只能运行可执行文件。如果客户有 LabVIEW 软件,我们将十分乐意发送相关文件。

“read”(读)与“read with reset”(带重置读)(AENERGY 寄存器与 RAENERGY 寄存器[或 AENERGY 与 RVAENERGY])之间的区别是什么?

实际上,这两个寄存器(AENERGY 和 RAENERGY)读取的是同一个内部寄存器。读取 AENERGY 寄存器时,仅对内部寄存器进行读操作。当读取 RAENERGY 寄存器时,对内部寄存器进行读操作并将其重置为 0。半满中断表示内部寄存器处于半满状态。读取累加有功功率时,可以只读取内部寄存器而不进行重置,并在设定半满中断时进行重置,也可总是在读后进行重置。任何情况下,都需要在微处理器中配置一个累加器,用以跟踪电能表累加的总电能,而且必须将 AENERGY 寄存器值添加到累加器中。VAENERGY 和 RVAENERGY 两个寄存器的情况与此相同。

### 重置或上电后,ADE775x 内部寄存器的内容是什么?

重置后,寄存器的内容为数据手册中描述的默认值。必要时,应将校准寄存器的内容存储在非易失性存储器中,以便重新加载。另见常见问题解答:ADE775x 是否有停电(电压 SAG)保护?

### ADE775x 是否有停电(电压 SAG)保护?

ADE775x 中的寄存器均为易失性寄存器。因此,校准系数和电能寄存器读数应保存在电能表的非易失性存储器(如 EEPROM 或闪存)中。ADE7753、ADE7754、ADE7756 和 ADE7759 配有 SAG 检测功能,用于提前向 MCU 发出警告(当电源电压开始降低时)。SAG 检测功能的激活电平可通过器件寄存器进行配置。当 SAG 检测功能激活时,意味着 ADE775x 的 5 V 电源将中断。MCU 应备份电能数据,当线路电压(及 5 V 电源电压)恢复正常时,应从存储器中读取校准系数并传递至 ADE775x。有关详情,请参阅应用笔记 AN - 564。

### ADE7756、ADE7759 和 ADE7753 中的 ADC 的采样速率是多少?

ADE7756 中的 ADC 的采样速率为 890 kHz。然而,由于该 ADC 采用  $\Sigma - \Delta$  架构,因此输入频率带宽小于奈奎斯特频率(445 kHz)。因此,ADE775x 中的模拟输入带宽被限为 14 kHz。即是说,在 60 Hz 信号下,最多可以数字化 233 个谐波。同时还须考虑 ADC 之前的抗混叠滤波器的频率带宽,它们一般具有较低的截止频率。

IRMS/VRMS 寄存器(ADE7753、ADE7754)中的数据能保留多长时间,读取后会被擦除吗?

IRMS/VRMS 寄存器不断进行更新,因此,它们从不真正“保留”数据。在 ADE775x 中,均方根计算利用一个低通滤波器来提取均方根值,并有与之关联的建立时间(约 700 ms)。如此一来,实际中电流/电压事件对寄存器进行更新时会有一定的延迟。在 RMS 寄存器中,我们建议在电压输入信号在零交越之后对寄存器采样,以消除滤波带来的噪声。(您可以利用零交越中断来标示零交越事件。)

应如何对非 n 字节长的符号寄存器进行读写操作?

对于 SPI,必须按字节进行读写操作。以下举例说明如何处理非 n 字节长的寄存器:PHCAL 寄存器为 6 位寄存器,但经过符号扩展,如图 4 所示。在此必须进行符号扩展,将符号位于 MSB。对于 PHCAL 一类的寄存器,第 7 位实际为符号位。5 个 LSB 位为寄存器的数值。第 5 和第 6 位为“无关位”。在回读经符号扩展的寄存器时,这些无关位将与 MSB(符号位)匹配,与写入这些位的值无关。该方法适用于所有 6 位或 12 位符号寄存器。

|   |   |   |   |   |   |   |   |       |

|---|---|---|---|---|---|---|---|-------|

| 0 | X | X | 1 | 1 | 1 | 1 | 1 | = +1F |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |       |

|   |   |   |   |   |   |   |   |       |

|---|---|---|---|---|---|---|---|-------|

| 1 | X | X | 1 | 1 | 1 | 1 | 1 | = -1F |

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |       |

图 4 向符号扩展寄存器写入值

## ADE775x:模拟校准产品

在模拟校准器件中,可以将电位计用于电阻校准网络吗?

对于模拟校准器件(ADE7751、ADE7752、ADE7755、ADE7757),为了确保电能表在长时间和全温度下的精度,不建议使用电位计。

在为 ADE7751/ADE7755 参考设计选择电源单元内使用的电容时,需要考虑哪些因素?

由于 ADE7751/ADE7755 具有内部电源监控功能,因此,当模拟电源引脚( $AV_{DD}$ )处的电压降至 4 V 以下时,芯片会自动复位。为了确保电能表能在 SAG 电压下正常工作,应增大电容分压器网络所用电容的容量。对于噪声过滤,应选择较大的介质电容。分压器网络所用电

容的阻抗为  $X_C = 1/(2\pi fC)$ 。通过电容的电流为  $I_C = \text{线路电压} \times (2\pi fC)$ 。由于电源使用半波整流模式,因此电源电流为通过电容电流的一半  $I_P = I_C/2$ 。

## 单相产品

### 1. ADE7751/ADE7755

#### 如何确定增益校准范围?

衰减网络应至少允许±30%的校验范围,以支持分流器容差和±8%的片内基准容差。

利用数据手册中的频率输出计算等式,

$$F_{req} = \frac{\text{Const} \times V1 \times V2 \times \text{Gain} \times F_{1-4}}{V_{REF}^2}$$

可以基于所有参数估算总误差。 $F_{1-4}$  几乎不会带来误差,因为误差仅取决于晶体。

若要以这种方式估算总误差,可加上数据手册给出的典型增益误差(7%)、V1、V2 中的误差,再加上基准误差的两倍。设电阻公差为 1%,则有

$$\text{误差} \approx 1\% + 1\% + 7\% + 2(8\%) \approx 25\%$$

我们保守的估计 ADE7755 参考设计的误差,建议校验范围为 30%。

#### ADE7755 能与电流互感器配合使用吗?

能。请参阅 ADE7755 数据手册。

#### 基于 ADE7751 或 ADE7755 的电能表的起始电流是多少?

以下计算基于 F1、F2 输出设为 100 imp/kWh 且 F1-4 为 3.4 Hz(S1=0, S0=1)的电能表。还可用其他设置轻松进行类似计算:

#### 输出频率

$$F1, F2 = \frac{100 \frac{\text{imp}}{\text{kWh}}}{\frac{3600 \frac{\text{sec}}{\text{hr}}}{}} \approx 0.0277 \frac{\text{Hz}}{\text{kW}}$$

ADE7755 的最低输出频率为  $F_{1-4}$  的 0.0014%。F1、F2 的最低输出频率为:

$$0.0014\% (3.4 \text{ Hz}) \approx 0.0000476 \text{ Hz}$$

等效功率为:

$$\frac{0.0000476 \text{ Hz}}{0.0277 \frac{\text{Hz}}{\text{kW}}} \approx 1.72 \text{ W}$$

## 第一部分 ADC 产品的应用

对应的起始电流(220 V 线路电压下)为  $1.72 \text{ W}/220 \text{ V} = 7.8 \text{ mA}$ 。

### EVAL - ADE7755EB 有多大?

EVAL - ADE7755EB 的尺寸约为 6 英寸  $\times$  5 英寸。

### EVAL - ADE7755EB 可以使用 120 V 电源吗?

可以。虽然这种评估板设计用于 220 V 电源电压,但可按比例更改分压器的值,以支持 120 V 电源。请参阅相关应用笔记和评估板文档。如应用笔记中描述的那样,只需更改评估板上的 R53 和/或 R54 电阻的值,即可使转折频率匹配保持 4.8 kHz 不变。由于这里需要降低电源电压,因而应增大电阻 R53 或 R54 或同时增大它们的值。这种方法对其他 ADE775x 评估板同样适用。

### 如何计算 ADE7755 应用笔记(AN - 559)所述电路的功耗?

功耗基于最差情况进行计算。在电源端,主要负载为与  $470 \Omega$  电阻串联的  $470 \text{ nF}$  电容。50 Hz 下,阻抗大小约为  $6.8 \text{ k}\Omega$ 。若通过负载的标称电流为 32.4 mA,则视在功率为:

$$(220 \text{ V})(32.4 \text{ mA}) = 7 \text{ VA}$$

电源的实际功率(经电阻消耗)为:

$$(470 \Omega)(32.4 \text{ mA})^2 = 0.5 \text{ W}$$

其他主要有功功耗源为分流器。作为一个阻性元件,当有电流通过时,即会消耗功率。40 A 下,分流器的功耗为:

$$(350 \mu\Omega)(40 \text{ A})^2 = 0.56 \text{ W}$$

因此,总功耗为:

$$0.5 \text{ W} + 0.56 \text{ W} = 1.06 \text{ W}$$

### 在 AN - 559 参考设计中,用齐纳二极管代替 7805 稳压器有什么影响?

齐纳二极管的电源抑制性能(PSR)不如稳压器。也就是说,如果用齐纳二极管代替稳压器,受电源波纹的影响,轻负载下即可能产生较大误差。

### 据 ADE7751/ADE7755 参考设计建议,REFIN/OUT 引脚处的 $10 \mu\text{F}$ 钽电容的功能是什么?

这两个电容与介质电容一起用于稳定基准电压、确保高精度。

### ADE7755 中的 V1P 和 V1N 输入引脚的输入阻抗容差是多大?

输入阻抗标识的为最小值  $390 \text{ k}\Omega$ 。理论上这个值会更高,但最小值是设计必须考虑的最差情况。

## 2. ADE7757

**ADE7755 和 ADE7757 有何区别？**

ADE7757 是 ADE7755 的引脚简化版，集成了一个振荡器，可消除外部晶体振荡器的成本。EVAL-ADE7757EB 可供购买。鉴于 ADE7755 和 ADE7757 间的相似性，在开始设计时可以使用相同的应用笔记(AN-559)。ADE7757 在性能上与 ADE7755 极其相似。有关详情，请参阅产品数据手册。

**ADE7757 可以使用外部晶体振荡器吗？**

ADE7757 集成了振荡器，不能使用外部晶体振荡器。

**必须使用数据手册中指定的电阻吗？**

数据手册中的规格和常数针对的是所用电阻决定的某个 CLKIN 值。如果未在设计中使用建议电阻，我们无法保证器件的性能，另外，数据手册中的常数将发生变化。

**ADE7757 中的 F1、F2 和 CF 脉冲是否同步？**

在 ADE7757 中，CF 和 F1-F2 脉冲同步，与 ADE7755 一样。

## 3. ADE7753

**ADE7753 中的寄存器 AENERGY、VAENERGY 和 VARENERGY 之间是否存在固定的关系？**

是的。虽然 AENERGY、VARENERGY 和 VAENERGY 三个寄存器因信号路径差异而不会匹配，但三者之间存在固定的比例关系。它们应随输入而变化。

积分器关闭(线路频率 50 Hz)：

$$VA = 0.810 \times W, VA = 2.796 \times VAR, W = 3.453 \times VAR$$

积分器开启(线路频率 50 Hz)：

$$VA = 0.870 \times W, VA = 1.186 \times VAR, W = 1.363 \times VAR$$

**如何发现 VAENERGY、AENERGY 及 VARENERGY 三个寄存器之间的关系？**

在相移为 90°和 0°下，分别测量有功功率、VA 和 VAR，即可验证这三个电能寄存器之间的关系。VA 与瓦特数之比为 90°相移下的 LVAENERGY 除以 0°相移下的 LAENERGY。

**如何从 ADE7753 获取功率因数？**

功率因数为有功功率与视在功率之比。

**www.BDTIC.com/ADI**

## 第一部分 ADC 产品的应用

对于无谐波信号,有功功率通常表示为  $VI \cos(\theta)$ ,其中,V 和 I 分别指电压和电流均方根。视在功率为  $VI$ 。若要获得 ADE7753 中的这些信息,请使用 LAENERGY 和 LVAENERGY 寄存器。虽然它们是电能,但您可以假定功率保持不变。由于两种电能的累加时间相同,这一比例会带来相同的结果。

### 4. ADE7756

可以用 ADE7756 或 ADE7759 计算均方根电流或均方根电压吗?

可以。请参阅 AN - 578 应用笔记,了解用 ADE7756 和 ADE7759 计算均方根电流和电压的详细方法。ADE7753 直接在寄存器中提供 IRMS 和 VRMS。

如何用 ADE7756 检测掉电(电压 SAG)?

ADE7756 有一个十分有用模式,可以检测线路电压压差(SAG 检测)。您可以对该检测功能进行设置,以在线路电压低于可配置阈值超过一定半线路周期数(可配置)时输出中断。该功能可提前通知您,电源的 5 V 电压可能很快就会下降,需要立即备份数据。

SAG 引脚无法可靠地捕捉掉电事件。应该用 IRQ 引脚来检测掉电。为了让 IRQ 引脚显示 SAG 事件,应将中断使能寄存器中的 SAG 位(第 1 位)设置为高电平。该位的默认值为逻辑低电平。

设置: MODE=0x0000; IRQEN=0x02

ADE7756 在挂起模式下的功耗是多少?如果在 CLK 输入端有一个 3.57 MHz 的晶体,应如何中断数字电路?此时的功耗是多少?

在挂起模式(模式寄存器的第 4 位设为 1)下,模拟部分被关闭,AV<sub>DD</sub>上的功耗低于 0.3 mA。数字电源功耗只能通过关闭时钟输入并将 CLKIN 连接至 GND 或 V<sub>DD</sub>(CLKOUT 开路)来降低。此时,DV<sub>DD</sub>上的功耗接近 0 mA。

如果利用微处理器驱动 ADE7756,可以在待机模式将 CLK 输入保持为逻辑 1 或 0。如果微处理器的时钟频率为 8 MHz,则可在 4 MHz 下运行 ADE7756,而不会产生任何问题。否则,需要部署一种晶体断开机制,以降低 DV<sub>DD</sub> 电流。

如何用 ADE7756 或 ADE7759 检测反相有功功率?

对于 ADE7756 或 ADE7759,您可以通过从波形寄存器中读取乘法器波形来检测反相功率。平均值符号可通过 MCU 进行解释。

如何用 ADE7756 检测有功功率?

当两个输入端(电流和电压)均为满量程交流信号( $\pm 1$  V 峰值差分)时,在乘法运算之后(平均有功功率),LPF 输出端的信号应为 0xCCCC 左右。在选定乘法器输出的情况下,通过读取波形寄存器即可访问该信号(MODE 寄存器的 WAVESEL 位 = 00)。

## 如何用 ADE7756 计算功率因数或获取无功功率符号?

在 ADE7756 中,无从得知无功功率是电容性的还是电感性的。需要使用 ADE7753 才能达此目的。要用 ADE7756 确定功率因数,您需要处理来自波形采样的 VRMS 和 IRMS,详见 AN - 578 应用笔记。在此基础上,即可得到功率因数,即有功功率与( $VRMS \times IRMS$ )之比。用 ADE7753 计算功率因数要简单得多,因为这种产品直接提供了有功功率和视在功率。

### 5. ADE7759

IRQEN(ADE7753、ADE7756、ADE7759)的全部 8 个位都可写吗?当向 IRQEN 写入 0x00 时,返回值为 0x40。

您的读数是正确的。IRQEN 寄存器的默认值为 0x40,重置位(6)为高电平。该使能位在中断使能寄存器中不起作用,意即该状态位在重置结束时设置,但无法通过启用它来产生中断。IRQEN 寄存器中的其余位默认值为 0。设为逻辑高电平时,如果 STATUS 寄存器中检测到对应事件,IRQ 引脚上将产生一个中断。IRQEN 中的重置位不可写,因为它不起作用。

## 如何计算将有功功率寄存器关联至千瓦时的常数?

您可以通过校准 kW:

$$kW = \frac{(Volts_{CAL})(Current_{CAL})}{1000}$$

以及在累加时间中累加的电量  $t_{ACC}$  来计算 kWh/LSB 常数,其中,累加时间为

$$t_{ACC} = \frac{LINECYC}{(2)(Line Freq)}$$

2 源自 LINECYC 寄存器计量的是半线路周期这一事实。等式为:

$$\frac{kWh}{LSB} = \frac{\frac{(t_{ACC})(kW)}{3600}}{Energy}$$

其中,Energy 为在校准周期中累加的电量。

## 多相产品

在三相系统中,如果已知各相位的电压,应如何计算相位间电压?

$$V_1 = V_{\text{相位 B}} \times \cos 60^\circ$$

$$V_2 = V_{\text{相位 B}} \times \sin 60^\circ$$

$$(V_{\text{相位 A}} - V_{\text{相位 B}})^2 = (V_{\text{相位 A}} - V_{\text{相位 B}})^2 + V_2^2$$

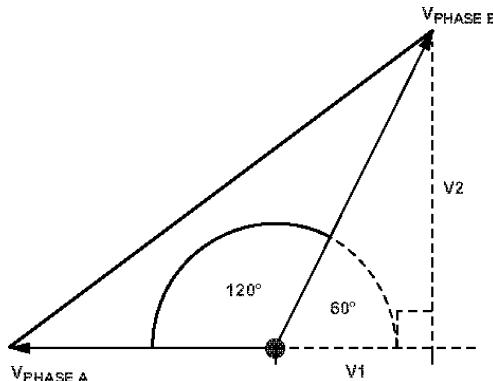

若假定三个电压相互平衡(相间 120°),则图 5 展示了相间电压的计算方法。

图 5 三相电压

您可以通过相到相的相位差来微调等式。该相位差可以根据各相位的零交越检测值(和中断)以及 ADE7754 的周期测量值推算出来。

### 1. ADE7752

**空载阈值与电流输入信号之间有何关系?**

ADE7752 空载阈值额定为满量程输出频率的 0.005%, 或最大功率的 0.005%。由于输出频率与输入信号(见数据手册)之间存在固定的关系, 因而可以据此推算出电流输入。以下等式假定:  $V = V_A = V_B = V_C$  且  $I = I_A = I_B = I_C$ :

$$\text{Freq} = \frac{3.922 \times 3(VI) \times F_{1-7}}{V_{\text{REF}}^2}$$

空载阈值为输出频率的 0.005%。这表示, 如果电压通道为满量程的 100%, 则空载阈值为电流通道的 0.005%。但是, 如果电压通道仅为满量程的 50%, 则阈值为电流通道输入的 0.01%。

### 2. ADE7754

**ADE7754 中为什么有三个有功功率寄存器?**

实际上, AENERGY 和 RAENERGY 读取的是同一个内部寄存器。读取 AENERGY 寄存器时, 仅对内部寄存器进行读操作。读取 RAENERGY 时, 对内部寄存器进行读操作并将其重置为 0。

要读取累加的有功功率, 可在半满中断被置位时读取和重置内部寄存器。需要在微处理器中配置一个累加器, 用以跟踪电能表累加的总电能, 而且必须在发生半满中断时将 AENERGY 寄存器值添加到累加器中。

第三个有功功率寄存器是 LANERGY 寄存器,可在指定的(LINECYC)线路周期数内累加有功功率。该寄存器可用于校准。详见 AN-624 应用笔记。

VAENERGY 和 RVAENERGY 寄存器具有相同的工作原理。

#### 如何连接 ADE7754 与电流互感器,要求的电流互感器精度是多少?

ADE7754 与电流互感器的连接非常简单。电流互感器的两条线缆可直接连接至 ADE7754 的电流输入端。同时应将两个负载电阻连接至电流互感器的两个输出端以及模拟地。负载电阻的值应根据 ADE7754 的模拟输入满量程(0.5 V 峰值差分,PGA=1)进行选择。

另见常见问题解答:如何计算电流互感器的负载电阻?

电流互感器的精度决定电能表精度本身,因此,应选择精度等于或高于目标电能表精度的电流互感器。

另见常见问题解答:选择电流互感器(CT)时有哪些考虑因素?

#### 如何在 ADE7754(ADE7753)评估板软件窗口中向器件写入值?

在该软件的多数窗口中,仅当单击“Write configuration”(写入配置)按钮时才会将窗口配置写入器件。

#### 可以从 ADE7754 中读取每相信息吗?

可以。可通过 LINECYC 模式及 WATMODE 寄存器选择累加相位,从而得到每相信息。

##### (1) 设 置

配置器件:

- 选择线路累加模式。

- 屏蔽线路累加中断(0x0F,第 10 位)。

- WATMODE 寄存器(0x0D,第 0 - 2 位)——选择相位 A。

- MMODE 寄存器(0x0B,第 4 - 6 位)——选择零交越相位。

##### (2) 环 路

- ① 等待 LAENERGY 中断。

- ② 将 LINECYC (0x13) 配置为较小值。

- ③ 写 WATMODE 选择相位 B。

- ④ 写 MMODE, 为零交越(ZX)选择相位 B。

- ⑤ 读 LAENERGY 寄存器(相位 A 的值)。

- ⑥ 重置中断(0x11)。

- ⑦ 等待 LAENERGY 中断。

- ⑧ 将 LINECYC 写为正常值。(必须在第一个 ZX 前执行。)

⑨重置中断(0x11)。

注意:没有必要去读 LAENERGY 寄存器,因为值是根据相位 A(第 1 步与第 3 步之间的时间)和相位 B(第 3 步与第 7 步之间的时间)累加出来的。

⑩ 对每个相位从第 1 步开始重复。

第②步中 LINECYC 的值必须足够长,以允许 LAENERGY 寄存器至少累加 1 位,并有足够的时问来执行所有寄存器读写操作(第③至第⑤步)。

#### 如何从 ADE7754 中获得有功功率信息?

ADE7754 在寄存器中提供有功功率信息,即平均有功功率的累加值。对于 ADE7754,不能像在 ADE7756 中一样,从波形寄存器读取有功功率波形。为了估算有功功率,您可以读取 LAENERGY 寄存器并用 LAENERGY 寄存器值除以累加时间,从而求出有功功率。在累加有功功率前,无法取得该信息。

#### 如何从 ADE7754 获取功率因数?

功率因数为有功功率与视在功率之比。

对于无谐波信号,有功功率通常表示为  $VI \cos(\theta)$ ,其中,V 和 I 分别指电压和电流的均方根值。视在功率为 VI。若要获得 ADE7754 中的这些信息,可使用 LAENERGY 和 LVAENERGY 寄存器。虽然它们是电能,但您可以假定功率保持不变。由于两种电能的累加时间相同,这一比例会给出相同的结果。

#### 如何获得功率因数的符号?

对于功率因数的符号,请使用配置为无功测量的 LAENERGY 寄存器(第 5 位, WAVMODE 寄存器)。对实际无功功率测量来说,虽然该测量值不精确,但可为您提供无功功率以及功率因数的符号。

#### 能否制作一种可同时用于 3 线“△”配置以及 4 线“Y”形配置的电能表?

您的设计需要针对两种配置进行校准,且微处理器在两种情况下应加载不同的校准参数(如增益)。检测栅格配置有两种实现方法。您可以将微处理器配置为软件自动检测模式(检测各相位的零交越,查找存在的相位,查看波形采样的电平),并禁用空闲相位的输入。或者,为了提高精度,您也可以使用硬件开关。

#### 如何用 ADE7754 监控 4 线系统中的中性接地电压以及全部三个相位?

在 4 线系统中,您可以假设  $VA + VB + VC = VN$ ,通过切换各个相位并利用波形采样,即可求出  $VA + VB + VC$ 。更精确的方法是在系统中添加一个专用的 ADC 或单相计量 IC。

当不存在电流和电压时,为什么 VAENERGY 寄存器中仍有累加值? VAENERGY 寄存器存在空载阈值吗?

我们未在 VA 中配置空载阈值。当电压和电流为零时,您需要忽略微处理器中该寄存器中存在的任何累加值。利用 SAG 中断或通过监控 AENERGY 寄存器中的累加运算即可知道何时电压为零。

#### 为什么无法使用 ADE7754 中的无功功率寄存器?

ADE7753 和 ADE7754 配有无功功率寄存器。但 ADE7754 存在一个设计误差:在无功功率运算中,电流的内部相移为  $89^\circ$  而非  $90^\circ$ 。当 PF 为 1 时,该误差会使无功功率为非零值,当 PF = 0.5 时,误差更大。这表示,ADE7754 中的无功功率寄存器无法直接用于计价,甚至无法直接用于提供信息。在 ADE7754 中,我们建议通过有功功率和视在功率来计算无功功率。功率三角法可给出无功功率:

$$\text{无功功率} = \sqrt{(\text{视在功率})^2 - (\text{有功功率})^2}$$

ADE7754 的无功功率寄存器可用于确定无功功率的符号,因为功率三角计算法得到的结果没有符号信息。

ADE7753 中的无功功率寄存器可直接用于精确计算可计价量。

83

#### ADE7754 的周期寄存器似乎无法正常工作。该寄存器有何不同?

如果禁用 MMODE 寄存器 ZXSEL 部分的某个相位,周期寄存器对该相位将不起作用。周期寄存器的工作原理是对所选相位 ZX 间的时间进行计数。ZXSEL 寄存器控制位于数据路径开始部分的 MUX。可见如果禁用 ZXSEL 寄存器中的某个相位,然后禁用 PERIOD 模块中的某个相位,则在周期间,该相位将无 ZX 可数。

可能出现的另一个问题是,当不存在 ZX 时,周期寄存器不会进行更新。在 PERDSEL 寄存器中切换相位时,周期寄存器也不会被清除。如果在测试时,相位 A 输入为 60 Hz,相位 B 无输入,则当相位 A 测试完毕切换到相位 B 时,将继续读取周期寄存器中的最后一个值(为来自相位 A 的值)。

在我们的仿真测试中,周期寄存器的精度在 1 秒钟后约为 5% 误差率,由于周期寄存器数据路径中滤波器的作用,在大约 2.5 秒后,误差将稳定为  $<2$  LSB。仿真中,先是无输入,最后是 60 Hz 的正弦波输入。

#### 对输出 CF 是否定义有电能表常数?

ADE7754 CF 频率并未定义电能表常数。如果全部 6 个模拟输入均为满量程交流电平,则 CF 频率约为 96 kHz。

www.BDTIC.com/ADI

# 第一部分 ADC 产品的应用

表常数及输入值(例如 220 V, 10 A)对应的值。

ADE7754 中的寄存器 AENERGY 和 VAENERGY 之间是否存在固定的关系?

是的。虽然 AENERGY 和 VARENERGY 两个寄存器因信号路径差异而不会匹配,但它们之间存在固定的关系。它们应随输入而变化。

在 50 Hz 线路频率下:

$$VA = W / 3.657$$

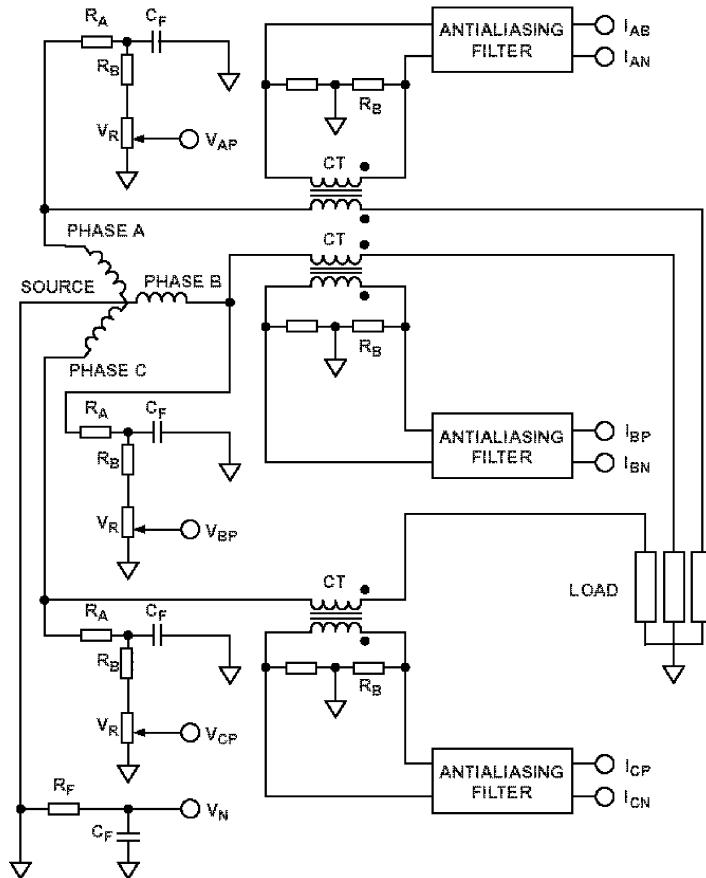

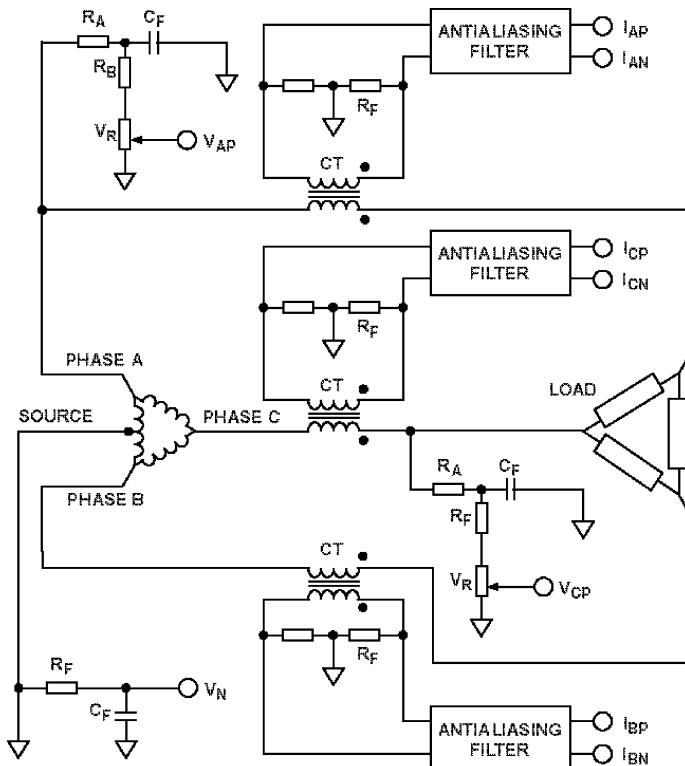

3 相 4 线“Y”形模式连接(见图 6)有哪些(含 3 个电压传感器)?

图 6 4 线“Y”形模式连接(含 3 个电压传感器)

$$\begin{aligned} \text{有功功率} &= (V_{AP} - V_N) \times (I_{AP} - I_{AN}) + (V_{BP} - V_N) \times (I_{BP} - I_{BN}) + (V_{CP} - V_N) \times (I_{CP} - I_{CN}) \\ &= (V_{\Phi A} \times I_{\Phi A}) + (V_{\Phi B} \times I_{\Phi B}) + (V_{\Phi C} \times I_{\Phi C}) \end{aligned}$$

据 ADE7754 数据手册,若要在 ADE7754 中选择该计算模式,则 WATMOD 寄存器应为 00x00,且 WATTSEL=0x00。

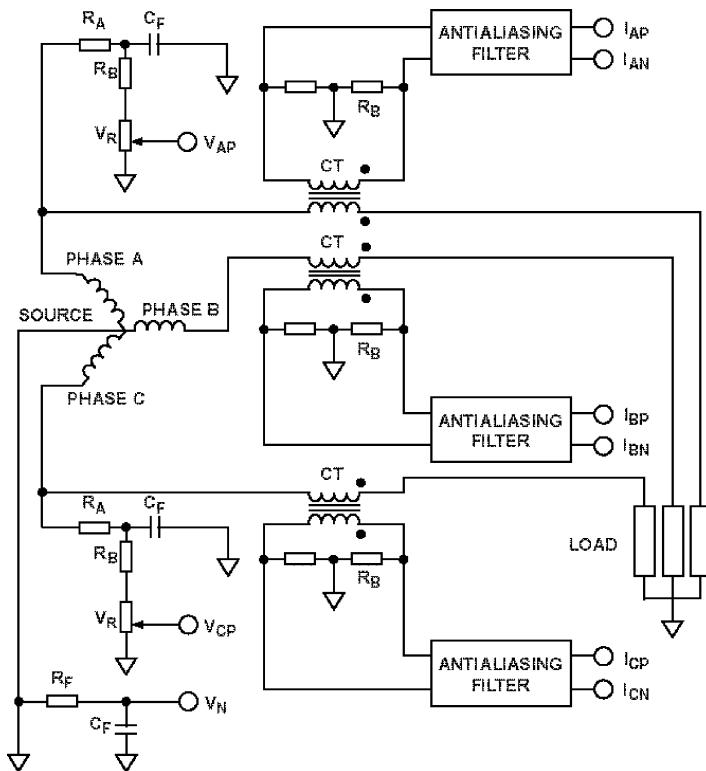

3 相 4 线“Y”形模式连接(见图 7)有哪些(含两个电压传感器)?

图 7 4 线“Y”形连接(含 2 个电压传感器)

$$\begin{aligned} \text{有功功率} &= (V_{AP} - V_N) \times ((I_{AP} - I_{AN}) - (I_{BP} - I_{BN})) + \\ &\quad (V_{CP} - V_N) \times ((I_{CP} - I_{CN}) - (I_{BP} - I_{BN})) \\ &= V_{\Phi A} \times (I_{\Phi A} - I_{\Phi B}) + V_{\Phi C} \times (I_{\Phi C} - I_{\Phi B}) \end{aligned}$$

若要在 ADE7754 中选择该计算模式,则 WATMOD 寄存器应为 0x01 且 WATTSEL = 0x07。

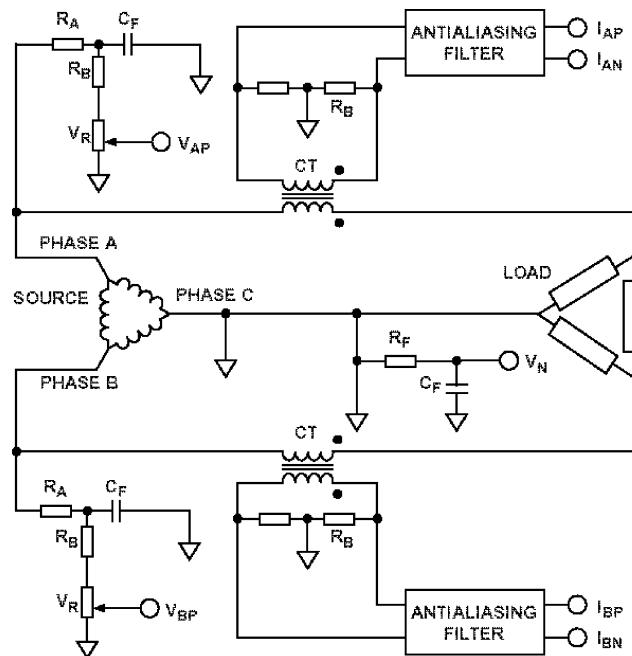

### 3 相 3 线 $\Delta$ 模式中(见图 8)有哪些模拟输入连接?

对于 3 相 3 线系统, 只有两个电压输入连接至 ADE7754。一个相位用作基准相位(连接至 ADE7754 的  $V_N$  引脚), 另外两个相位以其为参考。在 3 相 3 线连接中, 无法直接得到  $V_{AB}$  和  $I_C$ 。若要测量  $I_C$ , 需要添加一个电流互感器。对于  $V_{AB}$ , ADE7754 实际上测量的是  $V_{BC}$  和  $V_{AC}$ 。 $V_{AB}$  可根据这两个值算出, 假设 3 个相位间的相位差不变( $120^\circ$ )。

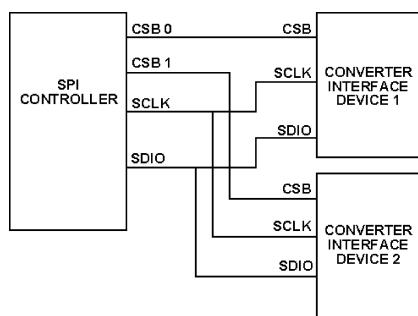

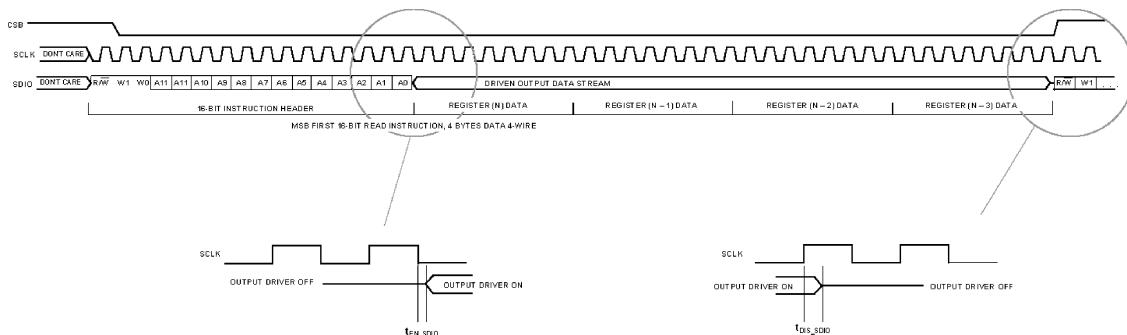

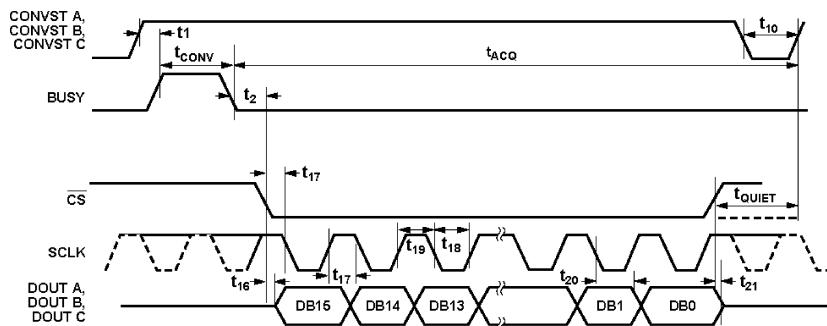

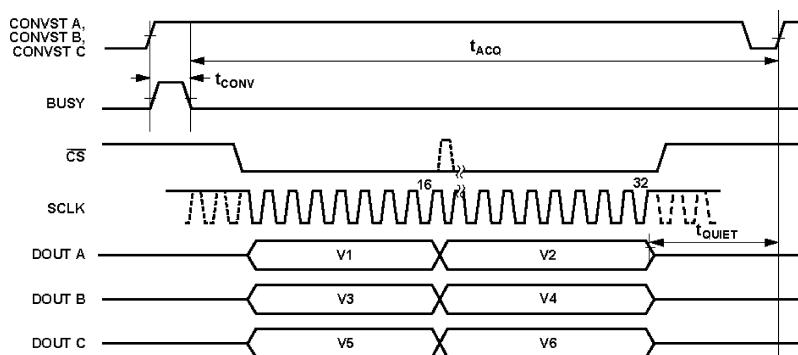

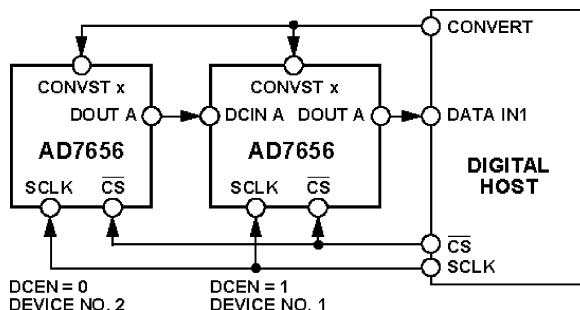

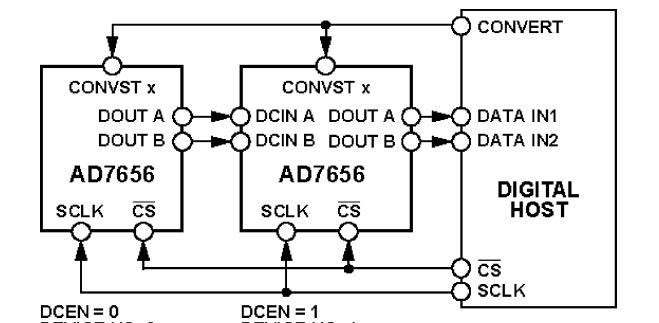

若要在 ADE7754 中选择该计算模式, 则 WATTMOD 寄存器应为 0x00 且 WATTSEL = 0x3、0x5 或 0x6。