HMC794LP3E 2 GHz Low Noise Programmable Divider (N = 1 to 4) SMT

The HMC794LP3E is a SiGe BiCMOS low noise programmable frequency divider in a 3x3mm leadless surface mount package. The circuit can be programmed to divide from N = 1 to N = 4 in the 200 MHz to 2 GHz input frequency range. The high level output power (up to 10 dBm) with a very low SSB phase noise and 50% duty cycle makes this device ideal for low noise clock generation, LO generation and LO drive applications. Configurable bias controls allow power minimization of up to 20%. .

技术特性

- Low Noise Floor:

-163 dBc/Hz at 10 MHz offset &

-160 dBc/Hz at 100 kHz offset

- Programmable Frequency

Divider, N = 1, 2, 3 or 4

- 200 MHz to 2 GHz

Input Frequency Range

- 50% Duty Cycle Outputs

- Up to +10 dBm Output Power

- Sleep Mode: Consumes <1 μA

- 16 Lead 3x3mm SMT Package: 9mm²

订购信息 Ordering Information

应用领域 APPLICATION

- LO Generation with Low Noise Floor

- Clock Generators

- Mixer LO Drive

- Military Applications

- Test Equipment

- Sensors

|

技术指标

| Input Freq. (GHz) |

Function |

Input Power (dBm) |

Output

Power (dBm) |

100 kHz SSB Phase Noise (dBc/Hz) |

Bias Supply |

Package |

| 0.2 - 2.0 |

Programmable Divider (N = 1 to 4) |

-2 to +10 |

10 |

-160 |

+5V @ 135mA |

LP3 |

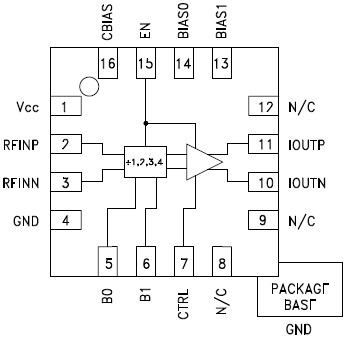

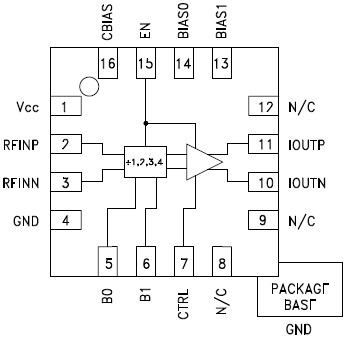

功能框图 Functional Block Diagram

|